Äîêóìåíòàöèÿ è îïèñàíèÿ www.docs.chipfind.ru

a

Preliminary Technical Data

Blackfin and the Blackfin logo are registered trademarks of Analog Devices, Inc.

Blackfin

®

Embedded

Symmetric Multi-Processor

ADSP-BF561

Rev. PrC

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O.Box 9106, Norwood, MA 02062-9106 U.S.A.

Tel:781/329-4700

www.analog.com

Fax:781/326-8703

© 2004 Analog Devices, Inc. All rights reserved.

FEATURES

Dual Symmetric 600 Mhz High Performance Blackfin Core

328 KBytes of On-chip Memory (See Memory Info

on Page 3

)

Each Blackfin Core Includes:

Two 16-Bit MACs, Two 40-Bit ALUs, Four 8-Bit Video ALUs,

40-Bit Shifter

RISC-Like Register and Instruction Model for Ease of Pro-

gramming and Compiler-Friendly Support

Advanced Debug, Trace, and Performance- Monitoring

0.8 - 1.2V core V

DD

with On-Chip Voltage Regulation

3.3V and 2.5V Tolerant I/O

256-Ball Mini BGA and 297-Ball PBGA Package Options

PERIPHERALS

Two Parallel Input/Output Peripheral Interface Units Sup-

porting ITU-R 656 Video and Glueless Interface to ADI

Analog Front End ADCs

Two Dual Channel, Full Duplex Synchronous Serial Ports Sup-

porting Eight Stereo I

2

S Channels

Dual 16 Channel DMA Controllers and one internal memory

DMA controller

12 General Purpose 32-bit Timer/Counters, with PWM

Capability

SPI-Compatible Port

UART with Support for IrDA®

Dual Watchdog Timers

48 Programable Flags

On-Chip Phase Locked Loop Capable of 1x to 63x Frequency

Multiplication

Figure 1. Functional Block Diagram

DMA

EXTERNAL PORT

FLASH/SDRAM CONTROL

32

16

32

16

BOOT ROM

PAB

EAB

DAB

DAB

PPI

PPI

VOLTAGE

REGULATOR

JTAG TEST

EMULATION

GPIO

SPI

UART

IRDA®

SPORT0

TIMERS

SPORT1

IMDMA

CONTROLLER

L1

INSTRUCTION

MEMORY

L1

DATA

MEMORY

MMU

B

L2 SRAM

128 KBYTES

CORE SYSTEM / BUS INTERFACE

L1

INSTRUCTION

MEMORY

L1

DATA

MEMORY

MMU

B

IRQ CTRL/

TIMER

IRQ CTRL/

TIMER

CONTROLLER2

DMA

CONTROLLER1

Rev. PrC

|

Page 2 of 52

|

April 2004

ADSP-BF561

Preliminary Technical Data

TABLE OF CONTENTS

General Description ................................................. 3

Portable Low-Power Architecture ............................. 3

Blackfin Processor Core .......................................... 3

Memory Architecture ............................................ 4

Internal (On-chip) Memory ................................. 4

External (Off-Chip) Memory ................................ 5

I/O Memory Space ............................................. 6

Booting ........................................................... 6

Event Handling ................................................. 6

Core Event Controller (CEC) ................................ 6

System Interrupt Controller (SIC) .......................... 6

Event Control ................................................... 7

DMA Controllers .................................................. 8

WatchDog Timers ................................................ 8

Serial Ports (SPORTs) ............................................ 9

Serial Peripheral Interface (SPI) Ports ........................ 9

UART Port .......................................................... 9

Programmable Flags (PFx) .................................... 10

Timers ............................................................. 10

Parallel Peripheral Interface ................................... 10

General Purpose Mode Descriptions .................... 10

Input Mode .................................................... 10

ITU -R 656 Mode Descriptions ........................... 10

Active Video Only Mode ................................... 10

Vertical Blanking Interval Mode .......................... 11

Entire Field Mode ............................................ 11

Dynamic Power Management ................................ 11

Full-On Operating Mode Maximum Performance . 11

Active Operating Mode Moderate Power Savings .. 11

Hibernate Operating Mode--Maximum Static Power

Savings ....................................................... 11

Sleep Operating Mode High Power Savings ......... 11

Deep Sleep Operating Mode Max. Power Savings .. 11

Power Savings ................................................. 12

Voltage Regulation .............................................. 12

Clock Signals ..................................................... 13

Booting Modes ................................................... 13

Instruction Set Description ................................... 14

Development Tools .............................................. 14

Designing an Emulator-Compatible

Processor Board (Target) ................................... 15

Additional Information ........................................ 15

Pin Descriptions .................................................... 16

Specifications ........................................................ 20

Recommended Operating Conditions ...................... 20

Electrical Characteristics ....................................... 20

Absolute Maximum Ratings ................................... 21

ESD Sensitivity ................................................... 21

Timing Specifications ........................................... 22

Clock and Reset Timing ..................................... 23

Asynchronous Memory Read Cycle Timing ............ 24

Asynchronous Memory Write Cycle Timing ........... 25

SDRAM Interface Timing .................................. 26

External Port Bus Request and Grant Cycle Timing .. 27

Parallel Peripheral Interface Timing ..................... 28

Serial Ports ..................................................... 29

Serial Peripheral Interface (SPI) Port--Master Timing 34

Serial Peripheral Interface (SPI) Port--Slave Timing . 36

Universal Asynchronous Receiver-Transmitter (UART)

Port--Receive and Transmit Timing .................. 38

Timer Cycle Timing .......................................... 39

Programmable Flags Cycle Timing ....................... 40

JTAG Test And Emulation Port Timing ................. 41

Power Dissipation ............................................... 42

Output Drive Currents ......................................... 42

Test Conditions .................................................. 42

Output Enable Time ......................................... 43

Output Disable Time ......................................... 43

Example System Hold Time Calculation ................... 43

Capacitive Loading .............................................. 44

256-ball MBGA Pin Configurations ............................ 45

297-ball PBGA Pin Configurations ............................. 47

Outline Dimensions ................................................ 50

Outline Dimensions ................................................ 51

Ordering Guide ..................................................... 51

REVISION HISTORY

Revision PrC:

· Edits made to pinlists and timing specification.

ADSP-BF561

Preliminary Technical Data

Rev. PrC

|

Page 3 of 52

|

April 2004

GENERAL DESCRIPTION

The ADSP-BF561 processor is a high-performance member of

the Blackfin family of products targeting a variety of multimedia

and telecommunications applications. At the heart of this device

are two independent Analog Devices Blackfin processors. These

Blackfin processors combine a dual-MAC state-of-the-art signal

processing engine, the advantage of a clean, orthogonal RISC-

like microprocessor instruction set, and single-instruction, mul-

tiple-data (SIMD) multimedia capabilities into a single

instruction-set architecture. The ADSP-BF561 device integrates

a general purpose set of digital imaging peripherals creating a

complete system on-chip solution for digital imaging and multi-

media applications.

The ADSP-BF561 processor has 328 KBytes of on-chip mem-

ory. Each Blackfin core includes:

· 16K Bytes of Instruction SRAM/Cache

· 16K Bytes of Instruction SRAM

· 32K Bytes of Data SRAM/Cache

· 32K Bytes of Data SRAM

· 4K Bytes of Scratchpad SRAM

Additional on-chip memory peripherals include:

· 128 KBytes of Low Latency On-chip SRAM

· Four Channel Internal Memory DMA Controller

· External Memory controller with glueless support for

SDRAM, SRAM, and Flash

PORTABLE LOW-POWER ARCHITECTURE

Blackfin processors provide world-class power management

and performance for embedded signal processing applications.

Blackfin processors are designed in a low power and low voltage

design methodology and feature Dynamic Power Management.

Dynamic Power Management is the ability to vary both the volt-

age and frequency of operation to significantly lower the overall

power dissipation. This translates into an exponential reduction

in power dissipation providing longer battery life to portable

applications.

BLACKFIN PROCESSOR CORE

As shown in

Figure 2

, each Blackfin core contains two multi-

plier/accumulators (MACs), two 40-bit ALUs, four video ALUs,

and a single shifter. The computational units process 8-bit, 16-

bit, or 32-bit data from the register file.

Figure 2. Blackfin Processor Core

SP

SEQUENCER

ALIGN

DECODE

LOOP BUFFER

DAG0

DAG1

16

16

8

8

8

8

40

40

A0

A1

BARREL

SHIFTER

DATA ARITHMETIC UNIT

CONTROL

UNIT

ADDRESS ARITHMETIC UNIT

FP

P5

P4

P3

P2

P1

P0

R7

R6

R5

R4

R3

R2

R1

R0

I3

I2

I1

I0

L3

L2

L1

L0

B3

B2

B1

B0

M3

M2

M1

M0

Rev. PrC

|

Page 4 of 52

|

April 2004

ADSP-BF561

Preliminary Technical Data

Each MAC performs a 16-bit by 16-bit multiply in every cycle,

with an accumulation to a 40-bit result, providing 8 bits of

extended precision. The ALUs perform a standard set of arith-

metic and logical operations. With two ALUs capable of

operating on 16- or 32-bit data, the flexibility of the computa-

tion units covers the signal processing requirements of a varied

set of application needs.

Each of the two 32-bit input registers can be regarded as two 16-

bit halves, so each ALU can accomplish very flexible single 16-

bit arithmetic operations. By viewing the registers as pairs of 16-

bit operands, dual 16-bit or single 32-bit operations can be

accomplished in a single cycle. By further taking advantage of

the second ALU, quad 16-bit operations can be accomplished

simply, accelerating the per cycle throughput.

The powerful 40-bit shifter has extensive capabilities for per-

forming shifting, rotating, normalization, extraction, and

depositing of data. The data for the computational units is

found in a multi-ported register file of sixteen 16-bit entries or

eight 32-bit entries.

A powerful program sequencer controls the flow of instruction

execution, including instruction alignment and decoding. The

sequencer supports conditional jumps and subroutine calls, as

well as zero-overhead looping. A loop buffer stores instructions

locally, eliminating instruction memory accesses for tight

looped code.

Two data address generators (DAGs) provide addresses for

simultaneous dual operand fetches from memory. The DAGs

share a register file containing four sets of 32-bit Index, Modify,

Length, and Base registers. Eight additional 32-bit registers pro-

vide pointers for general indexing of variables and stack

locations.

Blackfin processors support a modified Harvard architecture in

combination with a hierarchical memory structure. Level 1 (L1)

memories are those that typically operate at the full processor

speed with little or no latency. Level 2 (L2) memories are other

memories, on-chip or off-chip, that may take multiple processor

cycles to access. At the L1 level, the instruction memory holds

instructions only. The two data memories hold data, and a dedi-

cated scratchpad data memory stores stack and local variable

information. At the L2 level, there is a single unified memory

space, holding both instructions and data.

In addition, half of L1 instruction memory and half of L1 data

memories may be configured as either Static RAMs (SRAMs) or

caches. The Memory Management Unit (MMU) provides mem-

ory protection for individual tasks that may be operating on the

core and may protect system registers from unintended access.

The architecture provides three modes of operation: User mode,

Supervisor mode, and Emulation mode. User mode has

restricted access to certain system resources, thus providing a

protected software environment, while supervisor mode has

unrestricted access to the system and core resources.

The Blackfin instruction set has been optimized so that 16-bit

op-codes represent the most frequently used instructions,

resulting in excellent compiled code density. Complex DSP

instructions are encoded into 32-bit op-codes, representing fully

featured multifunction instructions. Blackfin processors sup-

port a limited multi-issue capability, where a 32-bit instruction

can be issued in parallel with two 16-bit instructions, allowing

the programmer to use many of the core resources in a single

instruction cycle.

The Blackfin assembly language uses an algebraic syntax for

ease of coding and readability. The architecture has been opti-

mized for use in conjunction with the VisualDSP C/C++

compiler, resulting in fast and efficient software

implementations.

MEMORY ARCHITECTURE

The ADSP-BF561 views memory as a single unified 4G-byte

address space, using 32-bit addresses. All resources including

internal memory, external memory, and I/O control registers

occupy separate sections of this common address space. The

memory portions of this address space are arranged in a hierar-

chical structure to provide a good cost/performance balance of

some very fast, low-latency memory as cache or SRAM very

close to the processor, and larger, lower-cost and performance-

memory systems farther away from the processor. The ADSP-

BF561 memory map is shown in

Figure 3

.

The L1 memory system in each core is the highest-performance

memory available to each Blackfin core. The L2 memory pro-

vides additional capacity with lower performance. Lastly, the

off-chip memory system, accessed through the External Bus

Interface Unit (EBIU), provides expansion with SDRAM, flash

memory, and SRAM, optionally accessing more than 768M

bytes of physical memory. The memory DMA controllers pro-

vide high-bandwidth data-movement capability. They can

perform block transfers of code or data between the internal

L1/L2 memories and the external memory spaces.

Internal (On-chip) Memory

The ADSP-BF561 has four blocks of on-chip memory providing

high-bandwidth access to the core.

The first is the L1 instruction memory of each Blackfin core

consisting of 16K bytes of 4-way set-associative cache memory

and 16K bytes of SRAM. The cache memory may also be config-

ured as an SRAM. This memory is accessed at full processor

speed. When configured as SRAM, each of the two 16K banks of

memory is broken into 4K sub-banks which can be indepen-

dently accessed by the processor and DMA.

The second on-chip memory block is the L1 data memory of

each Blackfin core which consists of four banks of 16K bytes

each. Two of the L1 data memory banks can be configured as

one way of a two-way set associative cache or as an SRAM. The

other two banks are configured as SRAM. All banks are accessed

at full processor speed. When configured as SRAM, each of the

four 16K banks of memory is broken into 4K sub-banks which

can be independently accessed by the processor and DMA.

The third memory block associated with each core is a 4K-byte

scratchpad SRAM which runs at the same speed as the L1 mem-

ories, but is only accessible as data SRAM (it cannot be

configured as cache memory and is not accessible via DMA).

ADSP-BF561

Preliminary Technical Data

Rev. PrC

|

Page 5 of 52

|

April 2004

The fourth on-chip memory system is the L2 SRAM memory

array which provides 128K bytes of high speed SRAM operating

at one half the bandwidth of the core, and slightly longer latency

than the L1 memory banks. The L2 memory is a unified instruc-

tion and data memory and can hold any mixture of code and

data required by the system design. The Blackfin cores share a

dedicated low-latency 64-bit wide data path port into the L2

SRAM memory.

Each Blackfin core processor has its own set of core Memory

Mapped Registers (MMRs) but share the same system MMR

registers and 128 KB L2 SRAM memory.

External (Off-Chip) Memory

The ADSP-BF561 external memory is accessed via the External

Bus Interface Unit (EBIU). This interface provides a glueless

connection to up to four banks of synchronous DRAM

(SDRAM) as well as up to four banks of asynchronous memory

devices including flash, EPROM, ROM, SRAM, and memory

mapped I/O devices.

The PC133-compliant SDRAM controller can be programmed

to interface to up to four banks of SDRAM, with each bank con-

taining between 16M bytes and 128M bytes providing access to

up to 512M bytes of SDRAM. Each bank is independently pro-

grammable and is contiguous with adjacent banks regardless of

the sizes of the different banks or their placement. This allows

flexible configuration and upgradability of system memory

while allowing the core to view all SDRAM as a single, contigu-

ous, physical address space.

The asynchronous memory controller can also be programmed

to control up to four banks of devices with very flexible timing

parameters for a wide variety of devices. Each bank occupies a

Figure 3. Memory Map

RESERVED

ASYNCMEMORYBANK3

ASYNCMEMORYBANK2

ASYNCMEMORYBANK1

ASYNCMEMORYBANK0

0xFF800000

0xFF701000

0xFF700000

0xFF614000

0xFF504000

0xFF500000

0xFF408000

0xFF404000

0xFF610000

0xFF604000

0xFF600000

0xFF508000

0xFF400000

L1SCRATCHPADSRAM(4K)

L1INSTRUCTIONSRAM/CACHE(16K)

L1INSTRUCTIONSRAM(16K)

L1DATABANKBSRAM/CACHE(16K)

L1DATABANKBSRAM(16K)

L1DATABANKASRAM/CACHE(16K)

L1DATABANKASRAM(16K)

COREAMEMORYMAP

COREBMEMORYMAP

COREMMRREGISTERS

COREMMRREGISTERS

SYSTEMMMRREGISTERS

L1SCRATCHPADSRAM(4K)

RESERVED

L1INSTRUCTIONSRAM/CACHE(16K)

L1INSTRUCTIONSRAM(16K)

L1DATABANKBSRAM/CACHE(16K)

L1DATABANKBSRAM(16K)

L1DATABANKASRAM/CACHE(16K)

L1DATABANKASRAM(16K)

L2SRAM(128K)

BOOTROM

SDRAMBANK3

SDRAMBANK2

SDRAMBANK1

SDRAMBANK0

0xFFE00000

0xFFC00000

0xFFB01000

0xFFB00000

0xFFA14000

0xFFA10000

0xFFA04000

0xFFA00000

0xFF908000

0xFF904000

0xFF900000

0xFF808000

0xFF804000

0xFEB20000

0xFEB00000

0xEF004000

0xEF000000

0x30000000

0x2C000000

0x28000000

0x24000000

0x20000000

0x00000000

RESERVED

INTERNALMEMORY

EXTERNALMEMORY

0xFFFFFFFF

Topof last SDRAMpage

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

0xFF800000

Rev. PrC

|

Page 6 of 52

|

April 2004

ADSP-BF561

Preliminary Technical Data

64M-byte segment regardless of the size of the devices used so

that these banks will only be contiguous if fully populated with

64M bytes of memory.

I/O Memory Space

Blackfin processors do not define a separate I/O space. All

resources are mapped through the flat 32-bit address space. On-

chip I/O devices have their control registers mapped into mem-

ory-mapped registers (MMRs) at addresses near the top of the

4G-byte address space. These are separated into two smaller

blocks, one which contains the control MMRs for all core func-

tions, and the other which contains the registers needed for

setup and control of the on-chip peripherals outside of the core.

The core MMRs are accessible only by the core and only in

supervisor mode and appear as reserved space by on-chip

peripherals. The system MMRs are accessible by the core in

supervisor mode and can be mapped as either visible or reserved

to other devices, depending on the system protection model

desired.

Booting

The ADSP-BF561 contains a small boot kernel, which config-

ures the appropriate peripheral for booting. If the ADSP-BF561

is configured to boot from boot ROM memory space, the pro-

cessor starts executing from the on-chip boot ROM.

Event Handling

The event controller on the ADSP-BF561 handles all asynchro-

nous and synchronous events to the processor. The ADSP-

BF561 provides event handling that supports both nesting and

prioritization. Nesting allows multiple event service routines to

be active simultaneously. Prioritization ensures that servicing of

a higher-priority event takes precedence over servicing of a

lower-priority event. The controller provides support for five

different types of events:

· Emulation An emulation event causes the processor to

enter emulation mode, allowing command and control of

the processor via the JTAG interface.

· Reset This event resets the processor.

· Non-Maskable Interrupt (NMI) The NMI event can be

generated by the software watchdog timer or by the NMI

input signal to the processor. The NMI event is frequently

used as a power-down indicator to initiate an orderly shut

down of the system.

· Exceptions Events that occur synchronously to program

flow, i.e., the exception will be taken before the instruction

is allowed to complete. Conditions such as data alignment

violations, undefined instructions, etc. cause exceptions.

· Interrupts Events that occur asynchronously to program

flow. They are caused by timers, peripherals, input pins,

and an explicit software instruction.

Each event has an associated register to hold the return address

and an associated return-from-event instruction. When an

event is triggered, the state of the processor is saved on the

supervisor stack.

The ADSP-BF561 event controller consists of two stages, the

Core Event Controller (CEC) and the System Interrupt Control-

ler (SIC). The Core Event Controller works with the System

Interrupt Controller to prioritize and control all system events.

Conceptually, interrupts from the peripherals enter into the

SIC, and are then routed directly into the general-purpose inter-

rupts of the CEC.

Core Event Controller (CEC)

The CEC supports nine general-purpose interrupts (IVG157),

in addition to the dedicated interrupt and exception events. Of

these general-purpose interrupts, the two lowest-priority inter-

rupts (IVG1514) are recommended to be reserved for software

interrupt handlers, leaving seven prioritized interrupt inputs to

support the peripherals of the ADSP-BF561.

Table 1

describes

the inputs to the CEC, identifies their names in the Event Vector

Table (EVT), and lists their priorities.

System Interrupt Controller (SIC)

The System Interrupt Controller provides the mapping and

routing of events from the many peripheral interrupt sources, to

the prioritized general-purpose interrupt inputs of the CEC.

Although the ADSP-BF561 provides a default mapping, the user

can alter the mappings and priorities of interrupt events by writ-

ing the appropriate values into the Interrupt Assignment

Registers (IAR).

Table 2

describes the inputs into the SIC and

the default mappings into the CEC.

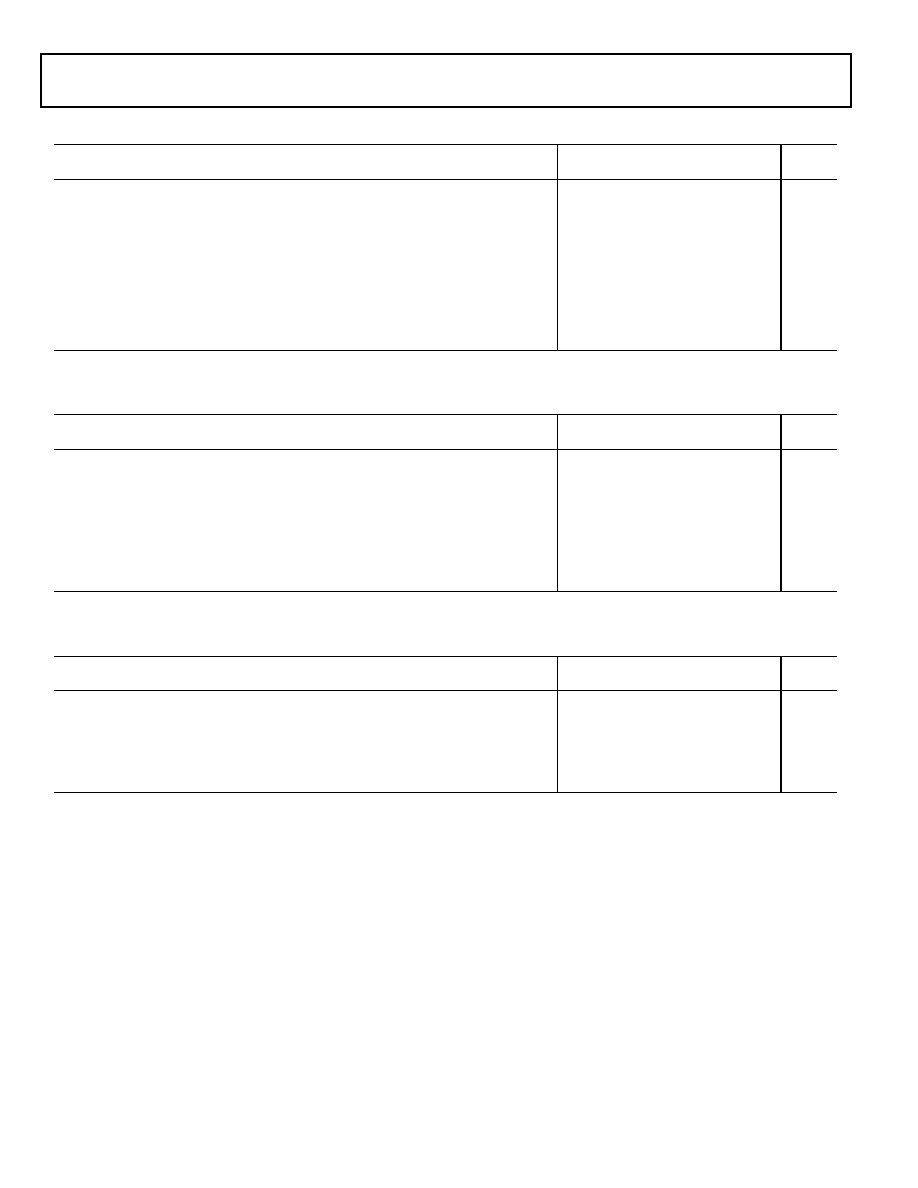

Table 1. Core Event Controller (CEC)

Priority

(0 is Highest)

Event Class

EVT Entry

0

Emulation/Test

EMU

1

Reset

RST

2

Non-Maskable NMI

3

Exceptions

EVX

4

Global Enable

-

5

Hardware Error

IVHW

6

Core Timer

IVTMR

7

General Interrupt 7

IVG7

8

General Interrupt 8

IVG8

9

General Interrupt 9

IVG9

10

General Interrupt 10

IVG10

11

General Interrupt 11

IVG11

12

General Interrupt 12

IVG12

13

General Interrupt 13

IVG13

14

General Interrupt 14

IVG14

15

General Interrupt 15

IVG15

ADSP-BF561

Preliminary Technical Data

Rev. PrC

|

Page 7 of 52

|

April 2004

Event Control

The ADSP-BF561 provides the user with a very flexible mecha-

nism to control the processing of events. In the CEC, three

registers are used to coordinate and control events. Each of the

registers, as follows, is 16-bits wide, while each bit represents a

particular event class:

· CEC Interrupt Latch Register (ILAT) The ILAT register

indicates when events have been latched. The appropriate

bit is set when the processor has latched the event and

cleared when the event has been accepted into the system.

This register is updated automatically by the controller, but

may be written only when its corresponding IMASK bit is

cleared.

· CEC Interrupt Mask Register (IMASK) The IMASK reg-

ister controls the masking and unmasking of individual

events. When a bit is set in the IMASK register, that event is

unmasked and will be processed by the CEC when asserted.

A cleared bit in the IMASK register masks the event

thereby preventing the processor from servicing the event

even though the event may be latched in the ILAT register.

This register may be read from or written to while in super-

visor mode. (Note that general-purpose interrupts can be

globally enabled and disabled with the STI and CLI instruc-

tions, respectively.)

· CEC Interrupt Pending Register (IPEND) The IPEND

register keeps track of all nested events. A set bit in the

IPEND register indicates the event is currently active or

nested at some level. This register is updated automatically

by the controller but may be read while in supervisor mode.

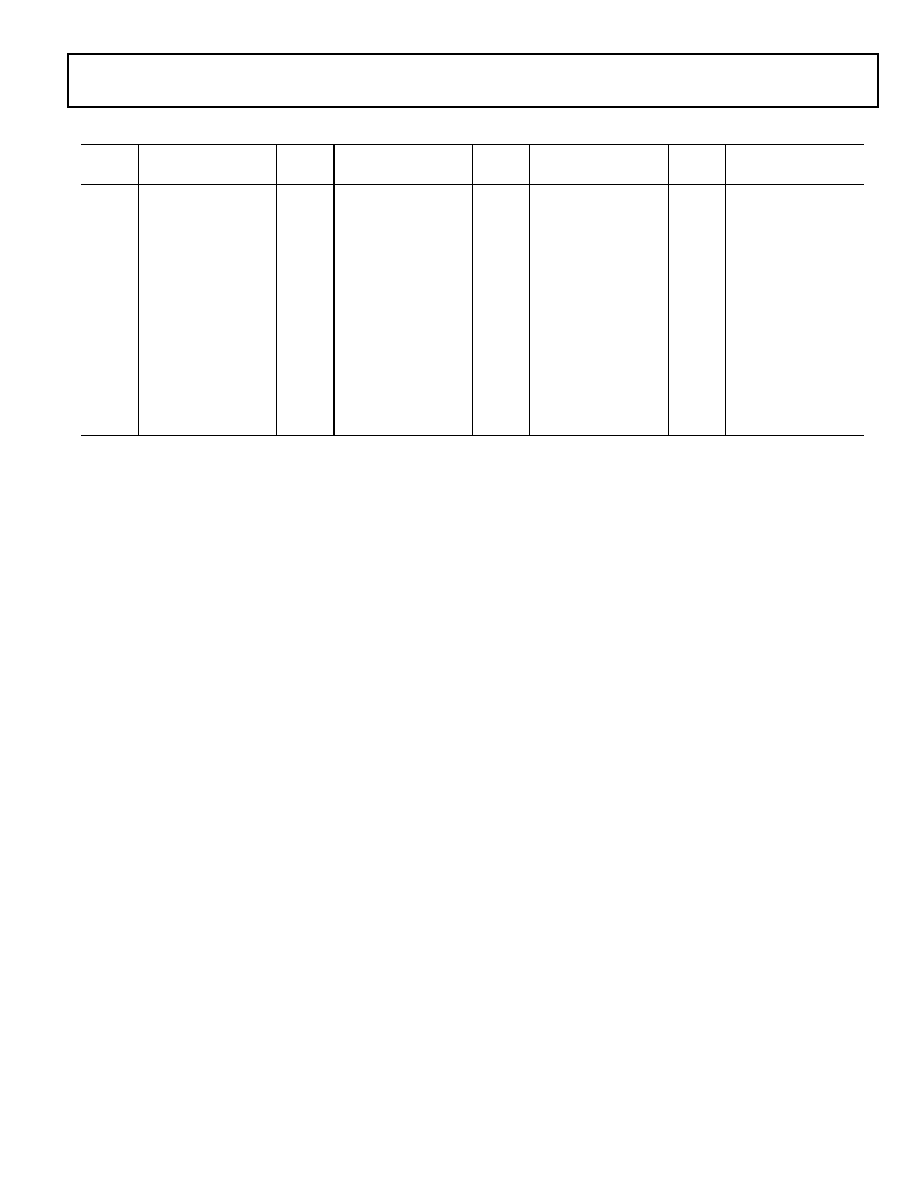

Table 2. Peripheral Interrupt Source Reset State

Peripheral Interrupt Source

Chan

1

IVG

2

PLL wakeup

0

IVG07

DMA1 Error

1

IVG07

DMA2 Error

2

IVG07

IMDMA Error

3

IVG07

PPI1 Error

4

IVG07

PPI2 Error

5

IVG07

SPORT0 Error

6

IVG07

SPORT1 Error

7

IVG07

SPI Error

8

IVG07

UART Error

9

IVG07

Reserved

10

IVG07

DMA1 0 interrupt

11

IVG08

DMA1 1 interrupt

12

IVG08

DMA1 2 interrupt

13

IVG08

DMA1 3 interrupt

14

IVG08

DMA1 4 interrupt

15

IVG08

DMA1 5 interrupt

16

IVG08

DMA1 6 interrupt

17

IVG08

DMA1 7 interrupt

18

IVG08

DMA1 8 interrupt

19

IVG08

DMA1 9 interrupt

20

IVG08

DMA1 10 interrupt

21

IVG08

DMA1 11 interrupt

22

IVG08

DMA2 0 interrupt

23

IVG09

DMA2 1 interrupt

24

IVG09

DMA2 2 interrupt

25

IVG09

DMA2 3 interrupt

26

IVG09

DMA2 4 interrupt

27

IVG09

DMA2 5 interrupt

28

IVG09

DMA2 6 interrupt

29

IVG09

DMA2 7 interrupt

30

IVG09

DMA2 8 interrupt

31

IVG09

DMA2 9 interrupt

32

IVG09

DMA2 10 interrupt

33

IVG09

DMA2 11 interrupt

34

IVG09

Timer0 interrupt

35

IVG10

Timer1 interrupt

36

IVG10

Timer2 interrupt

37

IVG10

Timer3 interrupt

38

IVG10

Timer4 interrupt

39

IVG10

Timer5 interrupt

40

IVG10

Timer6 interrupt

41

IVG10

Timer7 interrupt

42

IVG10

Timer8 interrupt

43

IVG10

Timer9 interrupt

44

IVG10

Timer10 interrupt

45

IVG10

Timer11 interrupt

46

IVG10

FIO0 interrupt A

47

IVG11

FIO0 interrupt B

48

IVG11

FIO1 interrupt A

49

IVG11

FIO1 interrupt B

50

IVG11

FIO2 interrupt A

51

IVG11

FIO2 interrupt B

52

IVG11

DMA1 write/read 0 interrupt

53

IVG08

DMA1 write/read1 interrupt

54

IVG08

DMA2 write/read 0 interrupt

55

IVG09

DMA2 write/read 1 interrupt

56

IVG09

IMDMA write/read 0 interrupt

57

IVG12

IMDMA write/read 1 interrupt

58

IVG12

Watchdog Timer

59

IVG13

Reserved

60

IVG07

Reserved

61

IVG07

Supplemental 0

62

IVG07

Supplemental 1

63

IVG07

1

Peripheral Interrupt Channel Number

2

Default User IVG Interrupt

Table 2. Peripheral Interrupt Source Reset State (Continued)

Peripheral Interrupt Source

Chan

1

IVG

2

Rev. PrC

|

Page 8 of 52

|

April 2004

ADSP-BF561

Preliminary Technical Data

The SIC allows further control of event processing by providing

six 32-bit interrupt control and status registers. Each register

contains a bit corresponding to each of the peripheral interrupt

events shown in

Table 2

.

· SIC Interrupt Mask Register (SIC_IMASK0, SIC_IMASK1)

This register controls the masking and unmasking of

each peripheral interrupt event. When a bit is set in the reg-

ister, that peripheral event is unmasked and will be

processed by the system when asserted. A cleared bit in the

register masks the peripheral event thereby preventing the

processor from servicing the event.

· SIC Interrupt Status Register (SIC_ISTAT0, SIC_ISTAT1)

As multiple peripherals can be mapped to a single event,

this register allows the software to determine which periph-

eral event source triggered the interrupt. A set bit indicates

the peripheral is asserting the interrupt, a cleared bit indi-

cates the peripheral is not asserting the event.

· SIC Interrupt Wakeup Enable Register (SIC_IWR0,

SIC_IWR1) By enabling the corresponding bit in this reg-

ister, each peripheral can be configured to wake up the

processor, should the processor be in a powered down

mode when the event is generated. (

For more information,

see Dynamic Power Management on Page 11.

)

Because multiple interrupt sources can map to a single general-

purpose interrupt, multiple pulse assertions can occur simulta-

neously, before or during interrupt processing for an interrupt

event already detected on this interrupt input. The IPEND reg-

ister contents are monitored by the SIC as the interrupt

acknowledgement.

The appropriate ILAT register bit is set when an interrupt rising

edge is detected (detection requires two core clock cycles). The

bit is cleared when the respective IPEND register bit is set. The

IPEND bit indicates that the event has entered into the proces-

sor pipeline. At this point the CEC will recognize and queue the

next rising edge event on the corresponding event input. The

minimum latency from the rising edge transition of the general-

purpose interrupt to the IPEND output asserted is three core

clock cycles; however, the latency can be much higher, depend-

ing on the activity within and the mode of the processor.

DMA CONTROLLERS

The ADSP-BF561 has multiple, independent DMA controllers

that support automated data transfers with minimal overhead

for the DSP core. DMA transfers can occur between the ADSP-

BF561's internal memories and any of its DMA-capable periph-

erals. Additionally, DMA transfers can be accomplished

between any of the DMA-capable peripherals and external

devices connected to the external memory interfaces, including

the SDRAM controller and the asynchronous memory control-

ler. DMA-capable peripherals include the SPORTs, SPI port,

UART, and PPI. Each individual DMA-capable peripheral has

at least one dedicated DMA channel.

The ADSP-BF561 DMA controllers support both 1-dimen-

sional (1D) and 2-dimensional (2D) DMA transfers. DMA

transfer initialization can be implemented from registers or

from sets of parameters called descriptor blocks.

The 2D DMA capability supports arbitrary row and column

sizes up to 64K elements by 64K elements, and arbitrary row

and column step sizes up to +/- 32K elements. Furthermore, the

column step size can be less than the row step size, allowing

implementation of interleaved data streams. This feature is

especially useful in video applications where data can be de-

interleaved on the fly.

Examples of DMA types supported by the ADSP-BF561 DMA

controllers include:

· A single, linear buffer that stops upon completion

· A circular, auto-refreshing buffer that interrupts on each

full or fractionally full buffer

· 1-D or 2-D DMA using a linked list of descriptors

· 2-D DMA using an array of descriptors, specifying only the

base DMA address within a common page

In addition to the dedicated peripheral DMA channels, each

DMA Controller has four memory DMA channels provided for

transfers between the various memories of the ADSP-BF561

system. These enable transfers of blocks of data between any of

the memories--including external SDRAM, ROM, SRAM, and

flash memory--with minimal processor intervention. Memory

DMA transfers can be controlled by a very flexible descriptor-

based methodology or by a standard register-based autobuffer

mechanism.

Further, the ADSP-BF561 has a four channel Internal Memory

DMA (IMDMA) Controller. The IMDMA Controller allows

data transfers between any of the internal L1 and L2 memories.

WATCHDOG TIMERS

Each ADSP-BF561 core includes a 32-bit timer, which can be

used to implement a software watchdog function. A software

watchdog can improve system availability by forcing the proces-

sor to a known state, via generation of a hardware reset, non-

maskable interrupt (NMI), or general- purpose interrupt, if the

timer expires before being reset by software. The programmer

initializes the count value of the timer, enables the appropriate

interrupt, then enables the timer. Thereafter, the software must

reload the counter before it counts to zero from the pro-

grammed value. This protects the system from remaining in an

unknown state where software, which would normally reset the

timer, has stopped running due to an external noise condition

or software error.

After a reset, software can determine if the watchdog was the

source of the hardware reset by interrogating a status bit in the

timer control register, which is set only upon a watchdog gener-

ated reset.

The timer is clocked by the system clock (SCLK), at a maximum

frequency of SCLK.

ADSP-BF561

Preliminary Technical Data

Rev. PrC

|

Page 9 of 52

|

April 2004

SERIAL PORTS (SPORTS)

The ADSP-BF561 incorporates two dual-channel synchronous

serial ports (SPORT0 and SPORT1) for serial and multiproces-

sor communications. The SPORTs support the following

features:

· I

2

S capable operation.

· Bidirectional operation Each SPORT has two sets of inde-

pendent transmit and receive pins, enabling eight channels

of I

2

S stereo audio.

· Buffered (8-deep) transmit and receive ports Each port

has a data register for transferring data words to and from

other DSP components and shift registers for shifting data

in and out of the data registers.

· Clocking Each transmit and receive port can either use an

external serial clock or generate its own, in frequencies

ranging from (f

SCLK

/131,070) Hz to (f

SCLK

/2) Hz.

· Word length Each SPORT supports serial data words

from 3 to 32 bits in length, transferred most-significant-bit

first or least-significant-bit first.

· Framing Each transmit and receive port can run with or

without frame sync signals for each data word. Frame sync

signals can be generated internally or externally, active high

or low, and with either of two pulsewidths and early or late

frame sync.

· Companding in hardware Each SPORT can perform

A-law or µ-law companding according to ITU recommen-

dation G.711. Companding can be selected on the transmit

and/or receive channel of the SPORT without additional

latencies.

· DMA operations with single-cycle overhead Each SPORT

can automatically receive and transmit multiple buffers of

memory data. The DSP can link or chain sequences of

DMA transfers between a SPORT and memory.

· Interrupts Each transmit and receive port generates an

interrupt upon completing the transfer of a data word or

after transferring an entire data buffer or buffers through

DMA.

· Multichannel capability Each SPORT supports 128 chan-

nels out of a 1024-channel window and is compatible with

the H.100, H.110, MVIP-90, and HMVIP standards.

SERIAL PERIPHERAL INTERFACE (SPI) PORTS

The ADSP-BF561 has one SPI-compatible ports that enable the

processor to communicate with multiple SPI-compatible

devices.

The SPI interface uses three pins for transferring data: two data

pins (Master Output-Slave Input, MOSIx, and Master Input-

Slave Output, MISO) and a clock pin (Serial Clock, SCK). One

SPI chip select input pin (SPISS) let other SPI devices select the

DSP, and seven SPI chip select output pins (SPISEL71) let the

DSP select other SPI devices. The SPI select pins are reconfig-

ured Programmable Flag pins. Using these pins, the SPI ports

provide a full duplex, synchronous serial interface, which sup-

ports both master and slave modes and multimaster

environments.

Each SPI port's baud rate and clock phase/polarities are pro-

grammable (see SPI Clock Rate equation), and each has an

integrated DMA controller, configurable to support transmit or

receive data streams. The SPI's DMA controller can only service

unidirectional accesses at any given time.

During transfers, the SPI ports simultaneously transmit and

receive by serially shifting data in and out on their two serial

data lines. The serial clock line synchronizes the shifting and

sampling of data on the two serial data lines.

UART PORT

The ADSP-BF561 provides a full duplex Universal Asynchro-

nous Receiver/Transmitter (UART) ports (UART0 and

UART1) fully compatible with PC-standard UARTs. The UART

ports provide a simplified UART interface to other peripherals

or hosts, supporting full duplex, DMA supported, asynchronous

transfers of serial data. Each UART port includes support for 5

to 8 data bits; 1 or 2 stop bits; and none, even, or odd parity. The

UART ports support two modes of operation, as follows:

· PIO (Programmed I/O) The processor sends or receives

data by writing or reading I/O-mapped UATX or UARX

registers, respectively. The data is double-buffered on both

transmit and receive.

· DMA (Direct Memory Access) The DMA controller

transfers both transmit and receive data. This reduces the

number and frequency of interrupts required to transfer

data to and from memory. Each UART has two dedicated

DMA channels, one for transmit and one for receive. These

DMA channels have lower priority than most DMA chan-

nels because of their relatively low service rates.

Each UART port's baud rate (see UART Clock Rate equation),

serial data format, error code generation and status, and inter-

rupts are programmable. In the UART Clock Rate equation, the

divisor (D) can be 1 to 65536.

The UART programmable features include:

· Supporting bit rates ranging from (f

SCLK

/ 1048576) to

(f

SCLK

/16) bits per second.

· Supporting data formats from 7 to12 bits per frame.

· Both transmit and receive operations can be configured to

generate maskable interrupts to the processor.

In conjunction with the general-purpose timer functions, auto-

baud detection is supported.

SPI Clock Rate

f

SCLK

2 SPIBAUD

×

-----------------------------------

=

UART Clock Rate

f

SCLK

16 D

×

----------------

=

Rev. PrC

|

Page 10 of 52

|

April 2004

ADSP-BF561

Preliminary Technical Data

The capabilities of UART0 are further extended with support

for the InfraRed Data Association (IrDA®) Serial InfraRed Phys-

ical Layer Link Specification (SIR) protocol.

PROGRAMMABLE FLAGS (PFX)

The ADSP-BF561 has 48 bi-directional, general-purpose I/O,

Programmable Flag (PF470) pins. The Programmable Flag

pins have special functions for SPI port operation. Each pro-

grammable flag can be individually controlled as follows by

manipulation of the flag control, status, and interrupt registers:

· Flag Direction Control Register Specifies the direction of

each individual PFx pin as input or output.

· Flag Control and Status Registers Rather than forcing the

software to use a read-modify-write process to control the

setting of individual flags, the ADSP-BF561 employs a

"write one to set" and "write one to clear" mechanism that

allows any combination of individual flags to be set or

cleared in a single instruction, without affecting the level of

any other flags. Two control registers are provided, one

register is written to in order to set flag values while

another register is written to in order to clear flag values.

Reading the flag status register allows software to interro-

gate the sense of the flags.

· Flag Interrupt Mask Registers The Flag Interrupt Mask

Registers allow each individual PFx pin to function as an

interrupt to the processor. Similar to the Flag Control Reg-

isters that are used to set and clear individual flag values,

one Flag Interrupt Mask Register sets bits to enable inter-

rupt function, and the other Flag Interrupt Mask register

clears bits to disable interrupt function. PFx pins defined as

inputs can be configured to generate hardware interrupts,

while output PFx pins can be configured to generate soft-

ware interrupts.

· Flag Interrupt Sensitivity Registers The Flag Interrupt

Sensitivity Registers specify whether individual PFx pins

are level- or edge-sensitive and specify-if edge-sensitive-

whether just the rising edge or both the rising and falling

edges of the signal are significant. One register selects the

type of sensitivity, and one register selects which edges are

significant for edge-sensitivity.

TIMERS

There are fourteen (14) programmable timer units in the ADSP-

BF561. Twelve general-purpose timers have an external pin that

can be configured either as a Pulse Width Modulator (PWM) or

timer output, as an input to lock the timer, or for measuring

pulse widths of external events. Each of the twelve general-pur-

pose timer units can be independently programmed as a PWM,

internally or externally clocked timer, or pulse width counter.

The general-purpose timer units can be used in conjunction

with the UART to measure the width of the pulses in the data

stream to provide an auto-baud detect function for a serial

channel.

The general-purpose timers can generate interrupts to the pro-

cessor core providing periodic events for synchronization,

either to the processor clock or to a count of external signals. In

addition to the twelve general-purpose programmable timers,

another timer is also provided for each core. These extra timers

are clocked by the internal processor clock (CCLK) and is typi-

cally used as a system tick clock for generation of operating

system periodic interrupts.

PARALLEL PERIPHERAL INTERFACE

The processor provides two Parallel Peripheral Interfaces (PPI)

that can connect directly to parallel A/D and D/A converters,

ITU-R-601/656 video encoders and decoders, and other general

purpose peripherals. Each PPI consists of a dedicated input

clock pin, up to 3 frame synchronization pins, and up to 16 data

pins.

In ITU-R 656 mode, the PPI receives and parses a data stream of

8- bit or 10-bit data elements. On-chip decode of embedded

preamble control and synchronization information is

supported.

General Purpose Mode Descriptions

The general-purpose modes of the PPI are intended to suit a

wide variety of data capture and transmission applications. The

modes are divided into four main categories, each allowing up

to 16 bits of data transfer per PPI_CLK cycle:

· Data Receive with Internally Generated Frame Syncs.

· Data Receive with Externally Generated Frame Syncs.

· Data Transmit with Internally Generated Frame Syncs.

· Data Transmit with Externally Generated Frame Syncs.

Input Mode

These modes support ADC/DAC connections, as well as video

communication with hardware signaling. Many of the modes

support more than one level of frame synchronization. If

desired, a programmable delay can be inserted between asser-

tion of a frame sync and reception / transmission of data.

ITU -R 656 Mode Descriptions

Three distinct ITU-R 656 modes are supported:

· Active Video Only Mode

· Vertical Blanking Only Mode

· Entire Field Mode

Active Video Only Mode

In this mode, the PPI does not read in any data between the End

of Active Video (EAV) and Start of Active Video (SAV) pream-

ble symbols, or any data present during the vertical blanking

intervals. In this mode, the control byte sequences are not stored

to memory; they are filtered by the PPI.

Vertical Blanking Interval Mode

In this mode, the PPI only transfers vertical blanking interval

(VBI) data, as well as horizontal blanking information and con-

trol byte sequences on VBI lines.

ADSP-BF561

Preliminary Technical Data

Rev. PrC

|

Page 11 of 52

|

April 2004

Entire Field Mode

In this mode, the entire incoming bitstream is read in through

the PPI. This includes active video, control preamble sequences,

and ancillary data that may be embedded in horizontal and ver-

tical blanking intervals.

Though not explicitly supported, ITU,-656 output functionality

can be achieved by setting up the entire frame structure (includ-

ing active video, blanking and control information) in memory

and streaming the data out of the PPI in a frame sync-less mode.

The processor's 2D DMA features facilitate this transfer by

allowing the static frame buffer (blanking and control codes) to

be placed in memory once, and simply updating the active video

information on per-frame basis.

These modes support ADC/DAC connections, as well as video

communication with hardware signaling. Many of the modes

support more than one level of frame synchronization. If

desired, a programmable delay can be inserted between asser-

tion of a frame sync and reception/transmission of data.

DYNAMIC POWER MANAGEMENT

The ADSP-BF561 provides four operating modes, each with a

different performance/power profile. In addition, Dynamic

Power Management provides the control functions to dynami-

cally alter the processor core supply voltage, further reducing

power dissipation. Control of clocking to each of the ADSP-

BF561 peripherals also reduces power consumption. See

Table 3

for a summary of the power settings for each mode.

Full-On Operating Mode Maximum Performance

In the Full-On mode, the PLL is enabled and is not bypassed,

providing capability for maximum operational frequency. This

is the default execution state in which maximum performance

can be achieved. The processor cores and all enabled peripherals

run at full speed.

Active Operating Mode Moderate Power Savings

In the Active mode, the PLL is enabled but bypassed. Because

the PLL is bypassed, the processor's core clock (CCLK) and sys-

tem clock (SCLK) run at the input clock (CLKIN) frequency. In

this mode, the CLKIN to CCLK multiplier ratio can be changed,

although the changes are not realized until the Full-On mode is

entered. DMA access is available to appropriately configured L1

memories.

In the Active mode, it is possible to disable the PLL through the

PLL Control register (PLL_CTL). If disabled, the PLL must be

re-enabled before transitioning to the Full-On or Sleep modes.

Hibernate Operating Mode--Maximum Static Power

Savings

The Hibernate mode maximizes static power savings by dis-

abling the voltage and clocks to the processor core (CCLK) and

to all the synchronous peripherals (SCLK). The internal voltage

regulator for the processor can be shut off by writing b#00 to the

FREQ bits of the VR_CTL register. This disables both CCLK

and SCLK. Furthermore, it sets the internal power supply volt-

age (V

DDINT

) to 0 V to provide the lowest static power

dissipation. Any critical information stored internally (memory

contents, register contents, etc.) must be written to a non-vola-

tile storage device prior to removing power if the processor state

is to be preserved. Since V

DDEXT

is still supplied in this mode, all

of the external pins tri-state, unless otherwise specified. This

allows other devices that may be connected to the processor to

have power still applied without drawing unwanted current.

The internal supply regulator can be woken up by asserting the

RESET pin.

Sleep Operating Mode--High Dynamic Power Savings

The Sleep mode reduces power dissipation by disabling the

clock to the processor core (CCLK). The PLL and system clock

(SCLK), however, continue to operate in this mode. Typically an

external event will wake up the processor. When in the Sleep

mode, assertion of wakeup will cause the processor to sense the

value of the BYPASS bit in the PLL Control register (PLL_CTL).

When in the Sleep mode, system DMA access to L1 memory is

not supported.

Deep Sleep Operating Mode--Maximum Dynamic Power

Savings

The Deep Sleep mode maximizes power savings by disabling the

clocks to the processor cores (CCLK) and to all synchronous

peripherals (SCLK). Asynchronous peripherals will not be able

to access internal resources or external memory. This powered-

down mode can only be exited by assertion of the reset interrupt

(RESET). If BYPASS is disabled, the processor will transition to

the Full On mode. If BYPASS is enabled, the processor will tran-

sition to the Active mode.

Power Savings

As shown in

Table 4

, the ADSP-BF561 supports two different

power domains. The use of multiple power domains maximizes

flexibility, while maintaining compliance with industry stan-

dards and conventions. By isolating the internal logic of the

ADSP-BF561 into its own power domain, separate from the I/O,

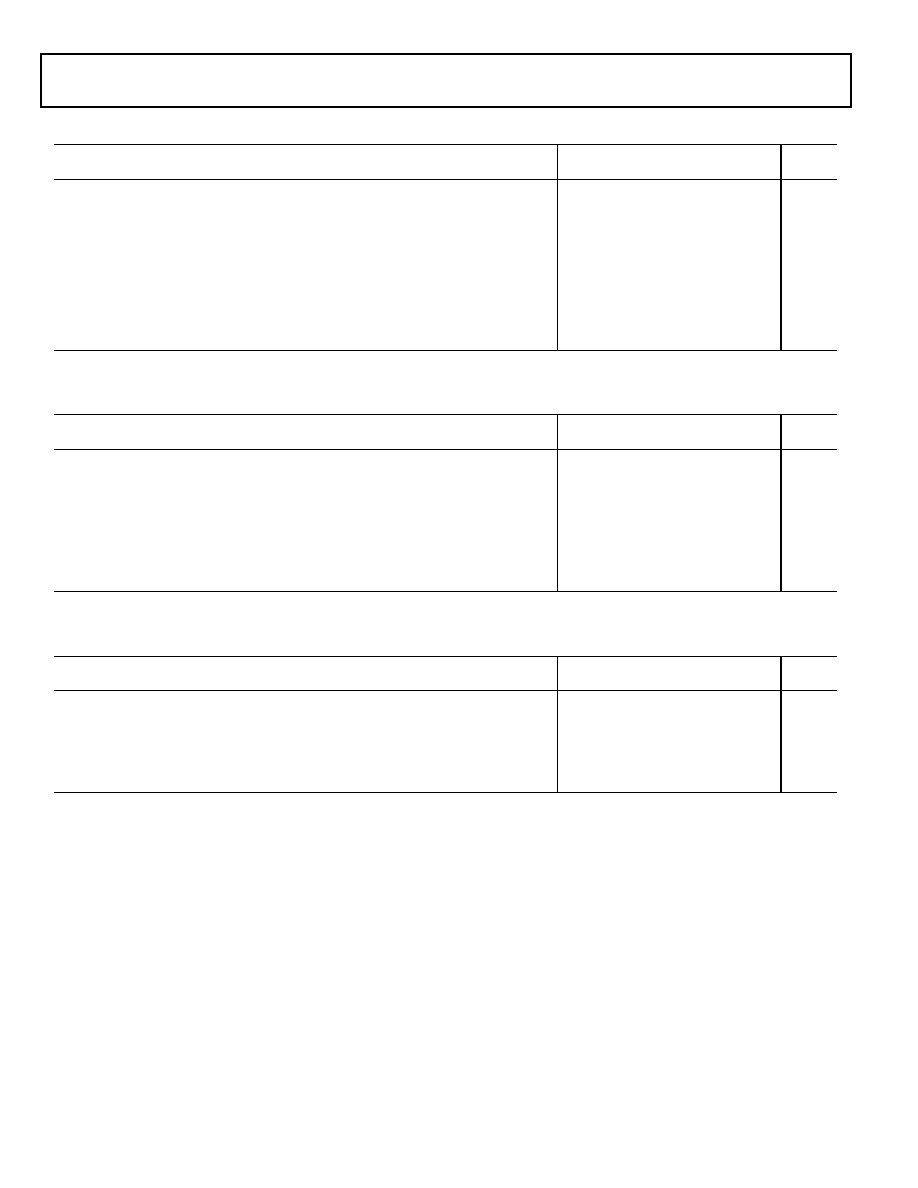

Table 3. Power Settings

Mode

PLL

PLL

Bypassed

Core

Clock

(CCLK)

System

Clock

(SCLK)

Core

Power

Full On

Enabled

No

Enabled Enabled On

Active

Enabled/

Disabled

Yes

Enabled Enabled On

Sleep

Enabled

Disabled Enabled On

Deep Sleep Disabled

Disabled Disabled On

Hibernate

Disabled

Disabled Disabled Off

Table 3. Power Settings (Continued)

Mode

PLL

PLL

Bypassed

Core

Clock

(CCLK)

System

Clock

(SCLK)

Core

Power

Rev. PrC

|

Page 12 of 52

|

April 2004

ADSP-BF561

Preliminary Technical Data

the processor can take advantage of Dynamic Power Manage-

ment, without affecting the I/O devices. There are no

sequencing requirements for the various power domains.

The power dissipated by a processor is largely a function of the

clock frequency of the processor and the square of the operating

voltage. For example, reducing the clock frequency by 25%

results in a 25% reduction in dynamic power dissipation, while

reducing the voltage by 25% reduces dynamic power dissipation

by more than 40%. Further, these power savings are additive, in

that if the clock frequency and supply voltage are both reduced,

the power savings can be dramatic.

The Dynamic Power Management feature of the ADSP-BF561

allows both the processor's input voltage (V

DDINT

) and clock

frequency (f

CCLK

) to be dynamically controlled.

The savings in power dissipation can be modeled using the

Power Savings Factor and % Power Savings calculations.

The Power Savings Factor is calculated as:

where the variables in the equations are:

· f

CCLKNOM

is the nominal core clock frequency

· f

CCLKRED

is the reduced core clock frequency

· V

DDINTNOM

is the nominal internal supply voltage

· V

DDINTRED

is the reduced internal supply voltage

· T

NOM

is the duration running at f

CCLKNOM

· T

RED

is the duration running at f

CCLKRED

The percent power savings is calculated as:

VOLTAGE REGULATION

The ADSP-BF561 processor provides an on-chip voltage regula-

tor that can generate processor core voltage levels 0.85V(-5% /

+10%) to 1.2V(-5% / +10%) from an external 2.25 V to 3.6 V

supply.

Figure 4

shows the typical external components

required to complete the power management system. The regu-

lator controls the internal logic voltage levels and is

programmable with the Voltage Regulator Control Register

(VR_CTL) in increments of 50 mV. To reduce standby power

consumption, the internal voltage regulator can be programmed

to remove power to the processor core while keeping I/O power

(V

DDEXT

) supplied. While in hibernation, V

DDEXT

can still be

applied, eliminating the need for external buffers. The voltage

regulator can be activated from this powerdown state by assert-

ing RESET, which will then initiate a boot sequence. The

regulator can also be disabled and bypassed at the user's

discretion.

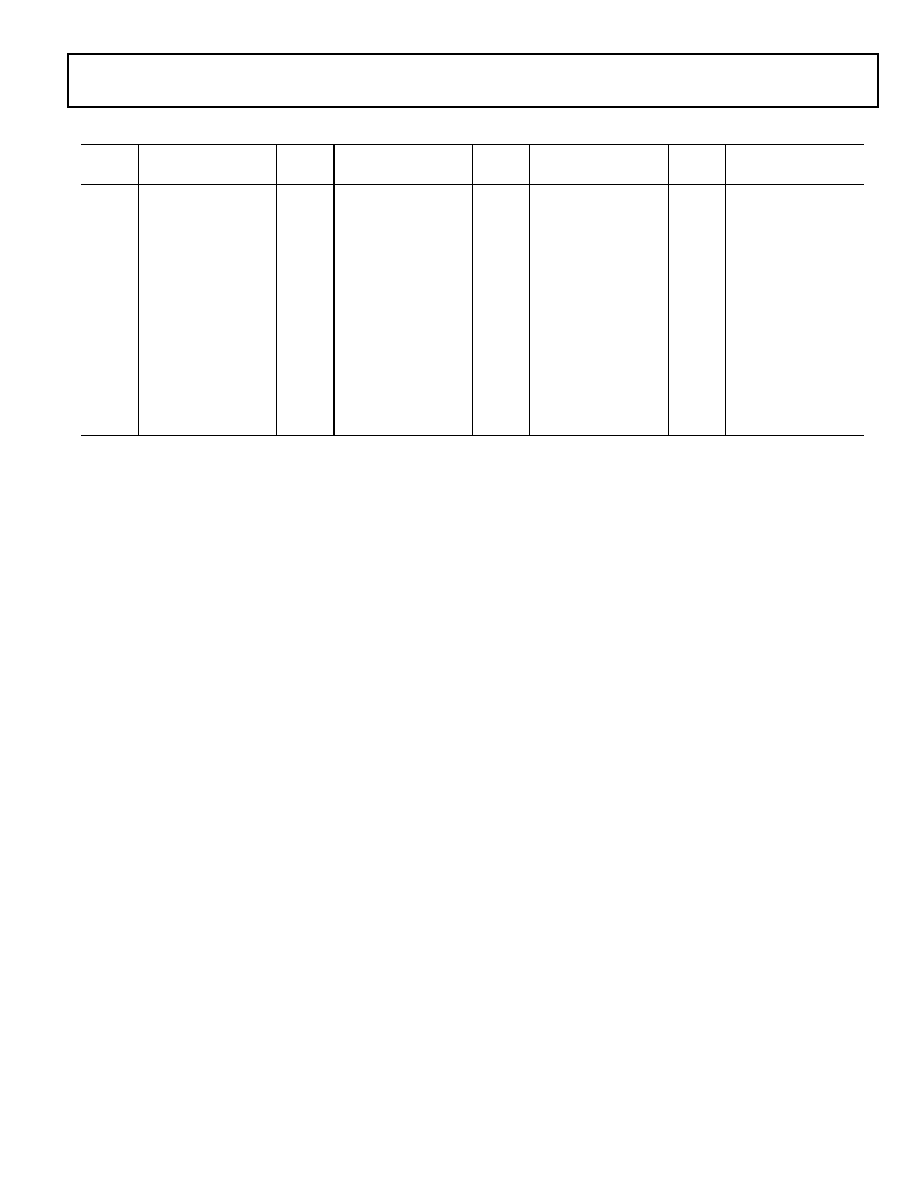

Table 4. ADSP-BF561 Power Domains

Power Domain

VDD Range

All internal logic

V

DDINT

I/O

V

DDEXT

Figure 4. Voltage Regulator Circuit

Power Savings Factor

f

CCLKRED

f

CCLKNOM

---------------------

V

DDINTRED

V

DDINTNOM

--------------------------

2

×

T

RED

T

NOM

-------------

×

=

% Power Savings

1 Power Savings Factor

(

) 100%

×

=

ADSP-BF561

Preliminary Technical Data

Rev. PrC

|

Page 13 of 52

|

April 2004

CLOCK SIGNALS

The ADSP-BF561 can be clocked by an external crystal, a sine

wave input, or a buffered, shaped clock derived from an external

clock oscillator.

If an external clock is used, it should be a TTL compatible signal

and must not be halted, changed, or operated below the speci-

fied frequency during normal operation. This signal is

connected to the processor's CLKIN pin. When an external

clock is used, the XTAL pin must be left unconnected.

Alternatively, because the ADSP-BF561 includes an on-chip

oscillator circuit, an external crystal may be used. The crystal

should be connected across the CLKIN and XTAL pins, with

two capacitors connected as shown in

Figure 5

Capacitor values are dependent on crystal type and should be

specified by the crystal manufacturer. A parallel-resonant, fun-

damental frequency, microprocessor-grade crystal should be

used.

As shown in

Figure 6

, the core clock (CCLK) and system

peripheral clock (SCLK) are derived from the input clock

(CLKIN) signal. An on-chip PLL is capable of multiplying the

CLKIN signal by a user programmable 1x to 63x multiplication

factor. The default multiplier is 10x, but it can be modified by a

software instruction sequence. On-the-fly frequency changes

can be effected by simply writing to the PLL_DIV register.

All on-chip peripherals are clocked by the system clock (SCLK).

The system clock frequency is programmable by means of the

SSEL30 bits of the PLL_DIV register. The values programmed

into the SSEL fields define a divide ratio between the PLL output

(VCO) and the system clock. SCLK divider values are 1 through

15.

Table 5

illustrates typical system clock ratios:

The maximum frequency of the system clock is f

SCLK

. Note that

the divisor ratio must be chosen to limit the system clock fre-

quency to its maximum of f

SCLK

. The SSEL value can be changed

dynamically without any PLL lock latencies by writing the

appropriate values to the PLL divisor register (PLL_DIV).

The core clock (CCLK) frequency can also be dynamically

changed by means of the CSEL[10] bits of the PLL_DIV regis-

ter. Supported CCLK divider ratios are 1, 2, 4, and 8, as shown

in

Table 6

. This programmable core clock capability is useful for

fast core frequency modifications.

BOOTING MODES

The ADSP-BF561 has three mechanisms (listed in

Table 7

) for

automatically loading internal L1 instruction memory after a

reset. A fourth mode is provided to execute from external mem-

ory, bypassing the boot sequence.

Figure 5. External Crystal Connections

Figure 6. Frequency Modification Methods

CLKIN

CLKOUT

XTAL

PLL

1

× - 63×

× 1:15

× 1, 2, 4, 8

VCO

SCLK

CCLK

SCLK

133 MHZ

CLKI N

"FI NE" ADJUSTMENT

REQUI RES PLL SEQ UENCING

"CO ARSE" ADJUSTMENT

ON-THE-FLY

CCLK

SCLK

Table 5. Example System Clock Ratios

Signal Name

SSEL[30]

Divider Ratio

VCO/SCLK

Example Frequency Ratios

(MHz)

VCO

SCLK

0001

1:1

100

100

0110

6:1

300

50

1010

10:1

500

50

Table 6. Core Clock Ratios

Signal Name

CSEL[10]

Divider Ratio

VCO/CCLK

Example Frequency Ratios

VCO

CCLK

00

1:1

500

500

01

2:1

500

250

10

4:1

200

50

11

8:1

200

25

Table 7. Booting Modes

BMODE10

Description

00

Execute from 16-bit external memory (Bypass

Boot ROM)

01

Boot from 8/16-bit flash

10

Reserved

11

Boot from SPI serial ROM (16-bit address

range)

Rev. PrC

|

Page 14 of 52

|

April 2004

ADSP-BF561

Preliminary Technical Data

The BMODE pins of the Reset Configuration Register, sampled

during power-on resets and software-initiated resets, imple-

ment the following modes:

· Execute from 16-bit external memory - Execution starts

from address 0x2000 0000 with 16-bit packing. The boot

ROM is bypassed in this mode. All configuration settings

are set for the slowest device possible (3-cycle hold time,

15-cycle R/W access times, 4-cycle setup).

· Boot from 8/16-bit external FLASH memory The 8/16-bit

FLASH boot routine located in boot ROM memory space is

set up using Asynchronous Memory Bank 0. All configura-

tion settings are set for the slowest device possible (3-cycle

hold time; 15-cycle R/W access times; 4-cycle setup).

· Boot from SPI serial EEPROM (16-bit addressable) The

SPI uses the PF2 output pin to select a single SPI EPROM

device, submits a read command at address 0x0000, and

begins clocking data into the beginning of L1 instruction

memory. A 16-bit addressable SPI-compatible EPROM

must be used.

For each of the boot modes, a boot loading protocol is used to

transfer program and data blocks, from an external memory

device, to their specified memory locations. Multiple memory

blocks may be loaded by any boot sequence. Once all blocks are

loaded, Core A program execution commences from the start of

L1 instruction SRAM (0xFFA0 0000). Core B remains in a held-

off state until a certain register bit is cleared. After that, Core B

will start execution at address 0xFF60 0000.

In addition, bit 4 of the Reset Configuration Register can be set

by application code to bypass the normal boot sequence during

a software reset. For this case, the processor jumps directly to

the beginning of L1 instruction memory.

INSTRUCTION SET DESCRIPTION

The Blackfin processor family assembly language instruction set

employs an algebraic syntax that was designed for ease of coding

and readability. The instructions have been specifically tuned to

provide a flexible, densely encoded instruction set that compiles

to a very small final memory size. The instruction set also pro-

vides fully featured multifunction instructions that allow the

programmer to use many of the processor core resources in a

single instruction. Coupled with many features more often seen

on microcontrollers, this instruction set is very efficient when

compiling C and C++ source code. In addition, the architecture

supports both a user (algorithm/application code) and a super-

visor (O/S kernel, device drivers, debuggers, ISRs) mode of

operations, allowing multiple levels of access to core processor

resources.

The assembly language, which takes advantage of the proces-

sor's unique architecture, offers the following advantages:

· Seamlessly integrated DSP/CPU features are optimized for

both 8-bit and 16-bit operations.

· A multi-issue load/store modified-Harvard architecture,

which supports two 16-bit MAC or four 8-bit ALU + two

load/store + two pointer updates per cycle.

· All registers, I/O, and memory are mapped into a unified

4G-byte memory space providing a simplified program-

ming model.

· Microcontroller features, such as arbitrary bit and bit-field

manipulation, insertion, and extraction; integer operations

on 8-, 16-, and 32-bit data-types; and separate user and ker-

nel stack pointers.

· Code density enhancements, which include intermixing of

16- and 32-bit instructions (no mode switching, no code

segregation). Frequently used instructions are encoded as

16-bits.

DEVELOPMENT TOOLS

The ADSP-BF561 is supported with a complete set of

CROSSCORE

TM

software and hardware development tools,

including Analog Devices emulators and the VisualDSP++®

development environment. The same emulator hardware that

supports other Analog Devices processors also fully emulates

the ADSP-BF561.

The VisualDSP++ project management environment lets pro-

grammers develop and debug an application. This environment

includes an easy-to-use assembler that is based on an algebraic

syntax, an archiver (librarian/library builder), a linker, a loader,

a cycle-accurate instruction-level simulator, a C/C++ compiler,

and a C/C++ run-time library that includes DSP and mathemat-

ical functions. A key point for these tools is C/C++ code

efficiency. The compiler has been developed for efficient trans-

lation of C/C++ code to Blackfin assembly. The Blackfin

processor has architectural features that improve the efficiency

of compiled C/C++ code.

The VisualDSP++ debugger has a number of important fea-

tures. Data visualization is enhanced by a plotting package that

offers a significant level of flexibility. This graphical representa-

tion of user data enables the programmer to quickly determine

the performance of an algorithm. As algorithms grow in com-

plexity, this capability can have increasing significance on the

designer's development schedule, increasing productivity. Sta-

tistical profiling enables the programmer to non intrusively poll

the processor as it is running the program. This feature, unique

to VisualDSP++, enables the software developer to passively

gather important code execution metrics without interrupting

the real-time characteristics of the program. Essentially, the

developer can identify bottlenecks in software quickly and effi-

ciently. By using the profiler, the programmer can focus on

those areas in the program that impact performance and take

corrective action.

Debugging both C/C++ and assembly programs with the Visu-

alDSP++ debugger, programmers can:

· View mixed C/C++ and assembly code (interleaved source

and object information)

· Insert breakpoints

· Set conditional breakpoints on registers, memory, and

stacks

· Trace instruction execution

· Perform linear or statistical profiling of program execution

ADSP-BF561

Preliminary Technical Data

Rev. PrC

|

Page 15 of 52

|

April 2004

· Fill, dump, and graphically plot the contents of memory

· Perform source level debugging

· Create custom debugger windows

The VisualDSP++ IDE lets programmers define and manage

software development. Its dialog boxes and property pages let

programmers configure and manage all development tools,

including Color Syntax Highlighting in the VisualDSP++ edi-

tor. These capabilities permit programmers to:

· Control how the development tools process inputs and

generate outputs.

· Maintain a one-to-one correspondence with the tool's

command line switches.

The VisualDSP++ Kernel (VDK) incorporates scheduling and

resource management tailored specifically to address the mem-

ory and timing constraints of embedded, real-time

programming. These capabilities enable engineers to develop

code more effectively, eliminating the need to start from the

very beginning, when Developing new application code. The

VDK features include Threads, Critical and Unscheduled

regions, Semaphores, Events, and Device flags. The VDK also

supports Priority-based, Pre-emptive, Cooperative and Time-

Sliced scheduling approaches. In addition, the VDK was

designed to be scalable. If the application does not use a specific

feature, the support code for that feature is excluded from the

target system.

Because the VDK is a library, a developer can decide whether to

use it or not. The VDK is integrated into the VisualDSP++

development environment, but can also be used with standard

command-line tools. When the VDK is used, the development

environment assists the developer with many error-prone tasks

and assists in managing system resources, automating the gen-

eration of various VDK based objects, and visualizing the

system state, when debugging an application that uses the VDK.

VCSE is Analog Devices technology for creating, using, and

reusing software components (independent modules of sub-

stantial functionality) to quickly and reliably assemble software

applications. Download components from the Web and drop

them into the application. Publish component archives from

within VisualDSP++. VCSE supports component implementa-

tion in C/C++ or assembly language.

Use the Expert Linker to visually manipulate the placement of

code and data on the embedded system. View memory utiliza-

tion in a color-coded graphical form, easily move code and data

to different areas of the processor or external memory with the

drag of the mouse, examine run time stack and heap usage. The

Expert Linker is fully compatible with existing Linker Definition

File (LDF), allowing the developer to move between the graphi-

cal and textual environments.

Analog Devices' emulators use the IEEE 1149.1 JTAG test access

port of the ADSP-BF561 to monitor and control the target

board processor during emulation. The emulator provides full-

speed emulation, allowing inspection and modification of mem-

ory, registers, and processor stacks. Non intrusive in-circuit

emulation is assured by the use of the processor's JTAG inter-

face--the emulator does not affect target system loading or

timing.

In addition to the software and hardware development tools

available from Analog Devices, third parties provide a wide

range of tools supporting the Blackfin processor family. Third

Party software tools include DSP libraries, real-time operating

systems, and block diagram design tools.

DESIGNING AN EMULATOR-COMPATIBLE

PROCESSOR BOARD (TARGET)

The Analog Devices family of emulators are tools that every sys-

tem developer needs to test and debug hardware and software

systems. Analog Devices has supplied an IEEE 1149.1 JTAG

Test Access Port (TAP) on the ADSP-BF561. The emulator uses

the TAP to access the internal features of the processor, allow-

ing the developer to load code, set breakpoints, observe

variables, observe memory, and examine registers. The proces-

sor must be halted to send data and commands, but once an

operation has been completed by the emulator, the processor is

set running at full speed with no impact on system timing.

To use these emulators, the target board must include a header

that connects the processor's JTAG port to the emulator.

For details on target board design issues including mechanical

layout, single processor connections, multiprocessor scan

chains, signal buffering, signal termination, and emulator pod

logic, see the EE-68: Analog Devices JTAG Emulation Technical

Reference on the Analog Devices web site (

www.analog.com

)--

use site search on "EE-68." This document is updated regularly

to keep pace with improvements to emulator support.

To use these emulators, the target board must include a header

that includes a header that connects the processor's JTAG port

to the emulation.

ADDITIONAL INFORMATION

This data sheet provides a general overview of the ADSP-BF561

architecture and functionality. For detailed information on the

Blackfin DSP family core architecture and instruction set, refer

to the ADSP-BF561 Hardware Reference and the Blackfin Family

Instruction Set Reference.

Rev. PrC

|

Page 16 of 52

|

April 2004

ADSP-BF561

Preliminary Technical Data

PIN DESCRIPTIONS

ADSP-BF561 pin definitions are listed in

Table 8

. Unused

inputs should be tied or pulled to V

DDEXT

or GND.

Table 8. Pin Descriptions

Block

Pin Name

Type Signals Function

Driver

Type

Pull-up/down requirement

EBIU

ADDR[25:2]

O

24

Address Bus for Async/Sync Access

A

none

DATA[31:0]

I/O

32

Data Bus for Async/Sync Access

A

none

ABE[3:0]/SDQM[3:0]

O

4

Byte Enables/Data Masks for Async

/Sync Access

A

none

BG

O

1

Bus Grant

A

none

BR

I

1

Bus Request

-

pull-up required if function not used

BGH

O

1

Bus Grant Hang

A

none

EBIU

(SDRAM)

SRAS

O

1

Row Address Strobe

A

none

SCAS

O

1

Column Address Strobe

A

none

SWE

O

1

Write Enable

A

none

SCKE

O

1

Clock Enable

A

none

SCLK0/CLKOUT

O

1

Clock Output Pin 0

B

none

SCLK1

O

1

Clock Output Pin 1

B

none

SA10

O

1

SDRAM A10 Pin

A

none

SMS[3:0]

O

4

Bank Select

A

none

EBIU

(ASYNC)

AMS[3:0]

O

4

Bank Select

A

none

ARDY

I

1

Hardware Ready Control

-

pull-up required if function not used

AOE

O

1

Output Enable

A

none

AWE

O

1

Write Enable

A

none

ARE

O

1

Read Enable

A

none

PPI1

PPI1D[15:8] /PF[47:40]

I/O

8

PPI Data / Programmable Flag Pins

C

software configurable, none

PPI1D[7:0]

I/O

8

PPI Data Pins

C

software configurable, none

PPI1CLK

I

1

PPI Clock

-

software configurable, none

PPI1SYNC1/ TMR8

I/O

1

PPI Sync / Timer

C

software configurable, none

PPI1SYNC2/ TMR9

I/O

1

PPI Sync / Timer

C

software configurable, none

PPI1SYNC3

I/O

1

PPI Sync

C

software configurable, none

PPI2

PPI2D[15:8] /PF[39:32]

I/O

8

PPI Data / Programmable Flag Pins

C

software configurable, none

PPI2D[7:0]

I/O

8

PPI Data Pins

C