### **Features**

- Maximum data rate: 43 Gb/s

- Output amplitude: 0.9 Vpp

- Single-ended clock/data input

- 50 Gb/s option available

## **General Description**

The CI0085B is a dynamic D-type Flip Flop (D-FF) operating at data rates up to 43 Gb/s. The I/O levels are SCFL (VH: 0.0 V, VL: -0.9 V). The IC is fabricated using a 0.1- $\mu$ m InP HEMT process. The CI0085B is provided in a hermetically-sealed package with V-connectors.

## **Applications**

- Waveform Shaping

- Data Retiming

- Decision Circuit

## **Truth Table**

| Din                 | CKin | QT | QC |  |  |

|---------------------|------|----|----|--|--|

| L                   |      | L  | Н  |  |  |

| Н                   |      | Н  | L  |  |  |

| Otherwise No Change |      |    |    |  |  |

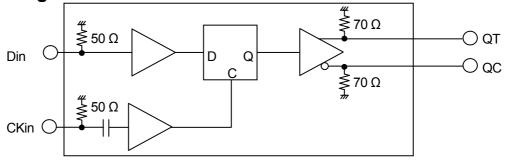

# **Functional Diagram**

## **Connection Table**

| No. | NAME | FUNCTION               | No. | NAME                 | FUNCTION                    |

|-----|------|------------------------|-----|----------------------|-----------------------------|

| 1   | NC   | No Internal Connection | 8   | QT <sup>(1)</sup>    | Data Output (True)          |

| 2   | Din  | Data Input             | 9   | QC <sup>(1)</sup>    | Data Output (Complementary) |

| 3   | GND  | Ground (0.0 V)         | 10  | GND                  | Ground (0.0 V)              |

| 4   | NC   | No Internal Connection | 11  | Vss                  | Power Supply (-4.5 V)       |

| 5   | NC   | No Internal Connection | 12  | CKin                 | Clock Input                 |

| 6   | NC   | No Internal Connection | 13  | Vrefd <sup>(2)</sup> | Data Input Reference        |

| 7   | GND  | Ground (0.0 V)         | 14  | GND                  | Ground (0.0 V)              |

Notes

- (1) Terminate unused output connectors to GND through 50-ohm resistors.

- (2) Internally generated reference voltage that determines the data input threshold level. By Applying -0.75V to -0.2V externally to this pin an arbitrary threshold voltage can be established.

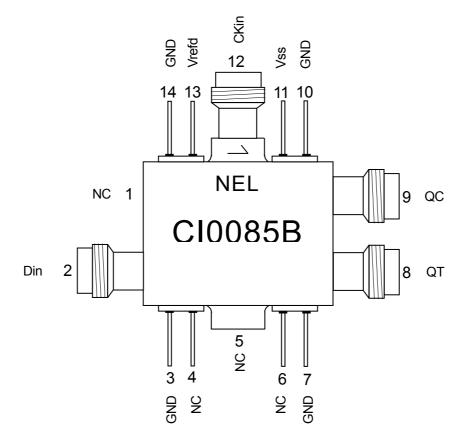

# **Connection Diagram (Top View)**

| SYMBOL            | PARAMETER                                       | RATING       | UNIT |

|-------------------|-------------------------------------------------|--------------|------|

| VSS               | Power Supply Voltage                            | -5.0 to +0.1 | V    |

| Vin               | Applied Voltage Amplitude at Clock Input (CKin) | 1.2          | Vpp  |

| Vind              | Applied Voltage at Data Input (Din)             | -1.2 to +0.1 | V    |

| Vinck             | Applied Voltage at Clock Input (CKin)           | -1.2 to +1.2 | V    |

| Vout              | Applied Voltage at Data Outputs (QT, QC)        | TBD          | V    |

| Vrefd             | Applied Voltage at Vrefd pin                    | -1.2 to +0.1 | V    |

| Tstor             | Storage Temperature                             | TBD          | °C   |

| Tc <sup>(1)</sup> | Case Temperature under Bias                     | TBD          | °C   |

# **Absolute Maximum Ratings**

TBD: To Be Determined

# **Recommended Operating Conditions**

| SYMBOL | PARAMETER                    | MIN.                                                                            | TYP. | MAX. | UNIT |

|--------|------------------------------|---------------------------------------------------------------------------------|------|------|------|

| VSS    | Power Supply                 | -4.7                                                                            | -4.5 | -4.3 | V    |

| Vrefd  | Data Input Reference Voltage | Open or adjust in the range from -0.75 V to -0.2 V                              |      |      |      |

| Din    | Data Input Interface         | DC coupling (see DC Characteristics)                                            |      |      |      |

| CKin   | Clock Input Interface        | DC coupling (see DC Characteristics) or<br>AC coupling (see AC Characteristics) |      |      |      |

| QT,QC  | Data Output Interface        | DC coupling (see DC Characteristics) ,<br>Terminate to GND through $50 \Omega$  |      |      |      |

# **DC Characteristics**

$(V_{ss} = -4.5 V, GND = 0.0 V, Tc^{(1)} = 30 °C)$

| SYMBOL | PARAMETER                       | MIN. | TYP. | MAX. | UNIT |

|--------|---------------------------------|------|------|------|------|

| ISS    | Power Supply Current            |      | 330  | TBD  | mA   |

| VOH    | Output Voltage, High (QT, QC)   | TBD  | 0.0  |      | V    |

| VOL    | Output Voltage, Low (QT, QC)    |      | -0.9 | TBD  | V    |

| VIH    | Input Voltage, High (Din, CKin) | TBD  | 0.0  |      | V    |

| VIL    | Input Voltage, Low (Din, CKin)  |      | -0.9 | TBD  | V    |

TBD: To Be Determined

Note

(1) Tc: Temperature at package base.

| 55 – -4.5 V, UN  | D = 0.0  V, PIN = 31, IVIR = 1/2,  VfeId:  A | ujust in the fa | ange nom -0 | .75 V 10 -0.2 V | )    | -       |

|------------------|----------------------------------------------|-----------------|-------------|-----------------|------|---------|

| SYMBOL           | PARAMETER                                    | Tc=30 °C        |             |                 | UNIT |         |

| STINDOL          | PARAIVIETER                                  | MIN.            | TYP.        | MAX.            | UNIT |         |

| Vin              | Clock Input Voltage Amplitude                | TBD             | 0.9         |                 | Vpp  |         |

| Vcenter          | Clock Input Center Voltage                   | -0.5            |             | 0.5             | V    |         |

| <b>f</b> MAX     | Maximum Clock Frequency                      | 43              |             |                 | GHz  | (1)     |

| f <sub>MIN</sub> | Minimum Clock Frequency                      |                 | 35          |                 | GHz  |         |

| Vamp             | Output Voltage Amplitude<br>(QT, QC)         | TBD             | 0.9         |                 | Vpp  |         |

| tr               | Output Rise Time (QT, QC)<br>20 - 80%        |                 | 10          | TBD             | ps   |         |

| tf               | Output Fall Time (QT, QC)<br>20 - 80%        |                 | 10          | TBD             | ps   |         |

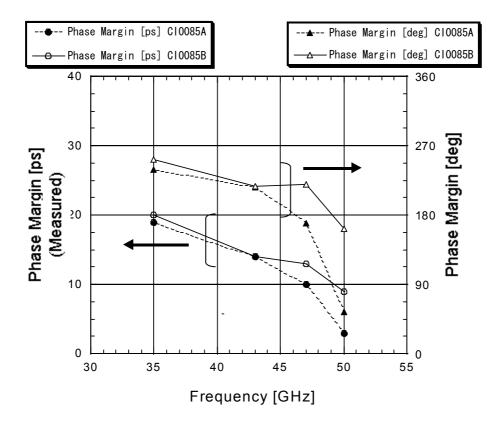

| PM               | Phase Margin                                 |                 | 200         |                 | deg. | (1), (2 |

AC Characteristics (43 Gb/s) (Vss = -4.5 V, GND = 0.0 V, PN = 31, MR = 1/2, Vrefd: Adjust in the range from -0.75 V to -0.2 V)

TBD: To Be Determined

Notes

(1) Confirmed by error-free operation using pseudo-random pattern with a word length of  $2^{31}$ -1 bits at 43 Gb/s

PM (measured) [ps] - X 360 [deg.] (2) Calculated as follows: PM [deg.] = -23.3 [ps]

where, 23.3 ps =

$$\frac{1}{43 \text{Gb/s}}$$

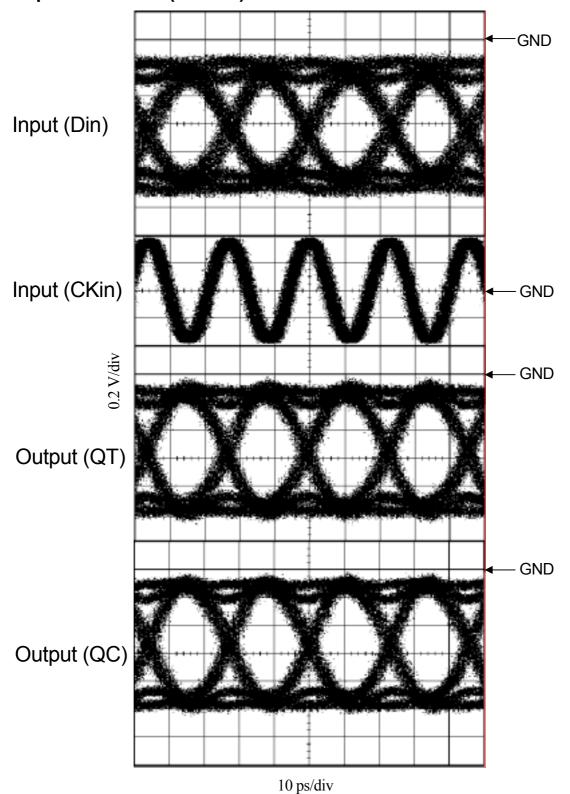

Sample Waveforms (43 Gb/s)

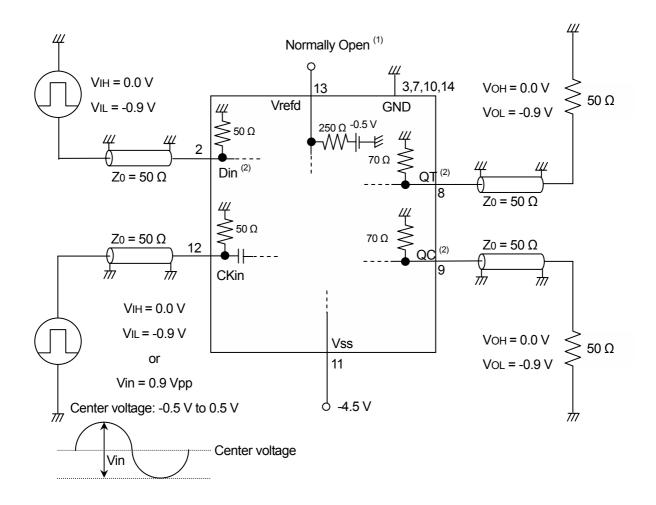

## **Measurement Conditions**

Vss = -4.5 V, Vrefd = -0.62 V, Input Data: 43 Gb/s, Input Clock: 43 GHz

# **Sample Phase Margin Characteristics**

## Measurement Conditions

Vss = -4.5 V, Vrefd = Optimum, Input Data: SCFL, Input Clock: 0.7 Vpp

#### **Sample Implementation**

Note: Each number corresponds to a pin or a connector as shown in Connection Diagram

#### Note

- (1) Open or adjust in the range from -0.75 V to -0.2 V.

- (2) DC coupling only.

## **Power Supply Sequence**

- (1) Set power supply voltages Vss, and GND to 0 V.

- (2) Apply -4.5 V to Vss.

- (3) Input data and clock signals.

#### Note

Use power supplies that do not generate glitches. Many power supplies generate glitches when their outputs are turned on or turned off. To avoid these glitches, connect power supplies to Vss and Vrefd after the power supply outputs are turned on and set to 0 V. Disconnect power supplies from Vss and Vrefd after the power supply outputs are set to 0 V but before the outputs are turned off.

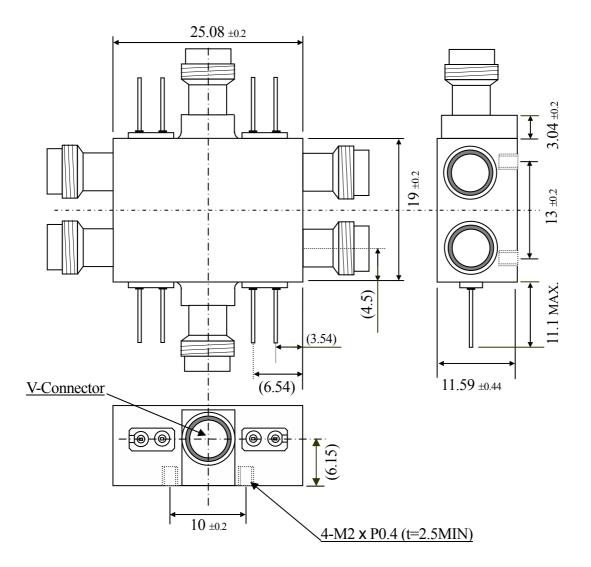

# SCMD Package Dimension (mm)

# **Handling Instructions**

Since the IC is fabricated using InP HEMT process, users are recommended to follow the instructions below to prevent damage to the chip from electro-static discharge.

- 1) Use a conductive working desk connected to the ground (or, a conductive table top connected to the ground).

- 2) Require all handling personnel to wear a conductive bracelet or wrist-strap connected to the ground through a 1 M $\Omega$  resistor.

- 3) Ground all test equipment.

- 4) Ground all soldering iron tops.

- 5) Store IC's and other devices such as chip capacitors in their conductive carriers until they are soldered.

# **Ordering Information**

| Part #:      | Description:               |

|--------------|----------------------------|

| CI0085B - 43 | $f_{MAX} = 43 \text{ GHz}$ |

| CI0085B - 47 | $f_{MAX} = 47 \text{ GHz}$ |

| CI0085B - 50 | $f_{MAX} = 50 \text{ GHz}$ |

# Caution

- 1. In order to improve products and technology, specifications are subject to change without notice.

- 2. When using the products, be sure the latest information and specifications are used.

- 3. Circuit drawings etc. shall be provided for the purpose of information only on application examples not for actual installation of equipment. NTT Electronics Corp. shall not assume any liability for damage that may result from the use of these circuit drawings etc. NTT Electronics Corp. shall not assent to or guarantee any rights of execution for patent rights of the third parties and other rights that may be raised for use of these circuit drawings.

- 4. To make a design, the products shall be used within the assured ranges with respect to maximum ratings, voltage, and radiation. NTT Electronics Corp. shall not take any responsibility for damage caused by neglecting the assured values or improper usage.

- 5. Though NTT Electronics Corp. makes every effort to improve quality and reliability, there is a risk that failure or malfunction may occur in semiconductors. It is therefore necessary that the purchasers should take responsibility for making a design that allows the products to operate safely on equipment and systems without any direct threat to the human body and/or property, should such failures or malfunction occur.

- 6. NTT Electronics Corp.'s semiconductor device products are designed to be used with multimedia networks communication equipment and related measuring equipment. They have not been developed for such equipment that may affect people's lives. Those who intend to use the products for special purposes that may affect human life as a result of failure or malfunction in the equipment using the products or that require extremely high reliability (e.g. life support, aircraft and space rockets, control in nuclear power facilities, submarine relays, control of operations, etc.) shall contact NTT Electronics Corp. before using the products. NTT Electronics Corp. shall not assume any liability for damage that may occur during operation of the products without prior consultation.

- 7. The product is controlled under the 'Foreign Exchange and Foreign Trade Law'. In the case of exporting this product, it is requested that you take necessary procedures to obtain prior approval from the Minister of Economy, Trade and Industry.

- 8. The product uses GaAs (gallium arsenide). GaAs powder and vapor are dangerous for humans. Do not break, cut, crush or chemically destroy the products. To dispose of the products, follow the relevant regulations and laws; do not mix with general industrial waste and domestic garbage.

- 9. Any questions should be directed to the Sales Department of NTT Electronics Corp.

Copyright 2002 NTT Electronics Corp.