ADVANCE INFORMATION

This document contains information on a product under development at Advanced Micro Devices. The information

is intended to help you evaluate this product. AMD reserves the right to change or discontinue work on this proposed

product without notice.

Publication# 25692

Rev: A Amendment+1

Issue Date: November 9, 2001

Refer to AMD's Website (www.amd.com) for the latest information.

Am29BDS643G

64 Megabit (4 M x 16-Bit)

CMOS 1.8 Volt-only Simultaneous Read/Write, Burst Mode Flash Memory

DISTINCTIVE CHARACTERISTICS

s

Single 1.8 volt read, program and erase (1.7 to

1.9 volt)

s

Multiplexed Data and Address for reduced I/O

count

-- A0≠A15 multiplexed as D0≠D15

-- Addresses are latched by AVD# control input

when CE# low

s

Simultaneous Read/Write operation

-- Data can be continuously read from one bank

while executing erase/program functions in

other bank

-- Zero latency between read and write operations

s

Read access times at 66/54/40 MHz

-- Burst access times of 11/13.5/20 ns @ 30 pF

at industrial temperature range

-- Asynchronous random access times

of 55/70/70 ns @ 30 pF

-- Synchronous random access times

of 71/87.5/95 ns @ 30 pF

s

Burst length

-- Continuous linear burst

-- 8/16/32 word linear burst with wrap around

s

Power dissipation (typical values, 8 bits

switching, C

L

= 30 pF)

-- Burst Mode Read: 25 mA

-- Simultaneous Operation: 40 mA

-- Program/Erase: 15 mA

-- Standby mode: 0.2 µA

s

Sector Architecture

-- Eight 8 Kword sectors and one hundred

twenty-six 32 Kword sectors

-- Banks A and B each contain four 8 Kword

sectors and thirty-one 32 Kword sectors; Banks

C and D each contain thirty-two 32 Kword

sectors

s

Sector Protection

-- Software command sector locking

-- WP# protects the last two boot sectors

-- All sectors locked when V

PP

= V

IL

s

Handshaking feature

-- Provides host system with minimum possible

latency by monitoring RDY

s

Supports Common Flash Memory

Interface (CFI)

s

Software command set compatible with JEDEC

42.4 standards

-- Backwards compatible with Am29F and

Am29LV families

s

Manufactured on 0.17 µm process technology

s

Minimum 1 million erase cycle guarantee

per sector

s

20-year data retention at 125

∞

C

-- Reliable operation for the life of the system

s

Embedded Algorithms

-- Embedded Erase algorithm automatically

preprograms and erases the entire chip or any

combination of designated sectors

-- Embedded Program algorithm automatically

writes and verifies data at specified addresses

s

Data# Polling and toggle bits

-- Provides a software method of detecting

program and erase operation completion

s

Erase Suspend/Resume

-- Suspends an erase operation to read data from,

or program data to, a sector that is not being

erased, then resumes the erase operation

s

Hardware reset input (RESET#)

-- Hardware method to reset the device for reading

array data

s

CMOS compatible inputs and outputs

s

Package

-- 44-ball Very Thin FBGA

2

Am29BDS643G

November 9, 2001

A D V A N C E I N F O R M A T I O N

GENERAL DESCRIPTION

The Am29BDS643G is a 64 Mbit, 1.8 Volt-only, simul-

taneous Read/Write, Burst Mode Flash memory

device, organized as 4,194,304 words of 16 bits each.

This device uses a single V

CC

of 1.7 to 1.9 V to read,

program, and erase the memory array. A 12.0-volt V

PP

may be used for faster program performance if desired.

The device can also be programmed in standard

EPROM programmers.

At 66 MHz, the Am29N643 provides a burst access of

11 ns at 30 pF with initial access times of 71 ns at 30

pF. At 54 MHz, the device provides a burst access of

13.5 ns at 30 pF with initial access times of 87.5 ns at

30 pF. At 40 MHz, the device provides a burst access

of 20 ns at 30 pF with initial access times of 95 ns at 30

pF. The device operates within the industrial tempera-

ture range of ≠40

∞

C to +85

∞

C. The device is offered in

the 44-ball Very Thin FBGA package.

Simultaneous Read/Write Operations with

Zero Latency

The Simultaneous Read/Write architecture provides

simultaneous operation by dividing the memory

space into four banks. The device allows a host sys-

t e m t o p r o g r a m o r e r a s e i n o n e b a n k , t h e n

immediately and simultaneously read from another

bank, with zero latency. This releases the system from

waiting for the c ompletion of program or er as e

operations.

The device is divided as shown in the following table:

The device uses Chip Enable (CE#), Write Enable

(WE#), Address Valid (AVD#) and Output Enable

(OE#) to control asynchronous read and write opera-

tions. For burst operations, the device additionally

requires Power Saving (PS), Ready (RDY), and Clock

(CLK). This implementation allows easy interface with

minimal glue logic to microprocessors/microcontrollers

for high performance read operations.

The device offers complete compatibility with the

JEDEC 42.4 single-power-supply Flash command

set standard. Commands are written to the command

register using standard microprocessor write timings.

Reading data out of the device is similar to reading

from other Flash or EPROM devices.

The host system can detect whether a program or

erase operation is complete by using the device sta-

tus bit DQ7 (Data# Polling) and DQ6/DQ2 (toggle

bits). After a program or erase cycle has been com-

pleted, the device automatically returns to reading

array data.

The sector erase architecture allows memory sec-

tors to be erased and reprogrammed without affecting

the data contents of other sectors. The device is fully

erased when shipped from the factory.

Hardware data protection measures include a low

V

CC

detector that automatically inhibits write opera-

tions during power transitions. The device also offers

three types of data protection at the sector level. The

sector lock/unlock command sequence disables or

re-enables both program and erase operations in any

sector. When at V

IL

, WP# locks the outermost sectors.

Finally, when V

PP

is at V

IL

, all sectors are locked.

The device offers two power-saving features. When

addresses have been stable for a specified amount of

time, the device enters the automatic sleep mode.

Th e s ys tem can al so plac e the de vi ce into the

standby mode. Power consumption is greatly re-

duced in both modes.

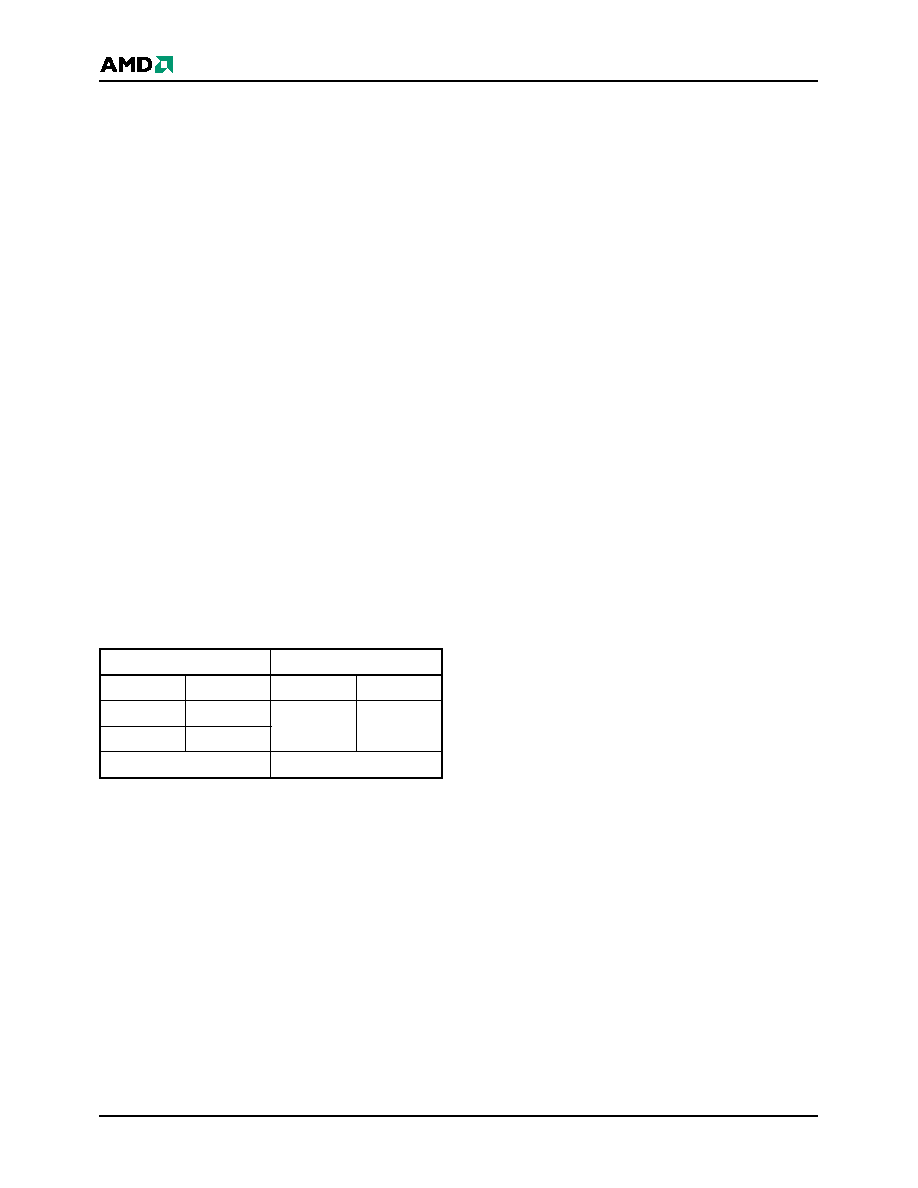

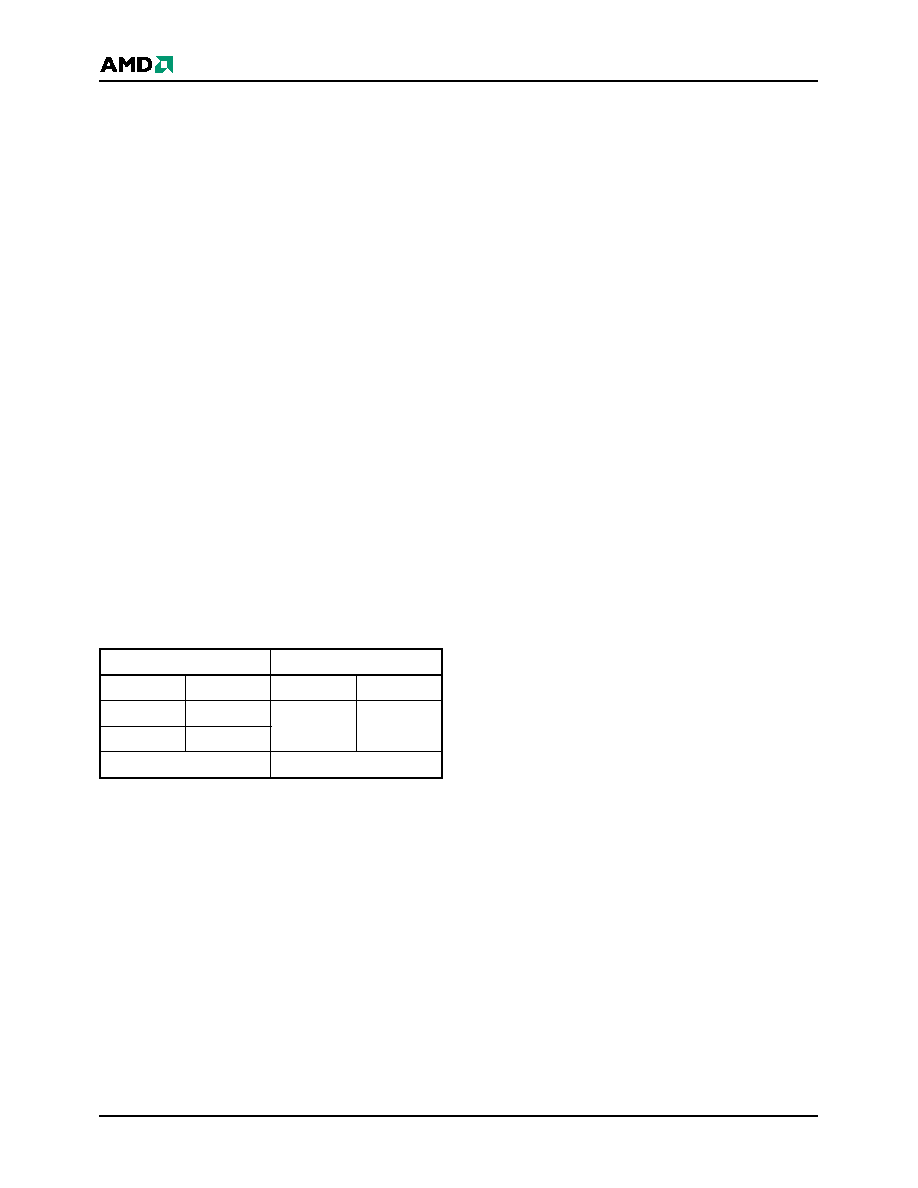

Bank A & B Sectors

Bank C & D Sectors

Quantity

Size

Quantity

Size

4

8 Kwords

32

32 Kwords

31

32 Kwords

32 Mbits total

32 Mbits total

November 9, 2001

Am29BDS643G

3

A D V A N C E I N F O R M A T I O N

TABLE OF CONTENTS

Product Selector Guide . . . . . . . . . . . . . . . . . . . . . 4

Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Block Diagram of

Simultaneous Operation Circuit . . . . . . . . . . . . . . 5

Connection Diagram . . . . . . . . . . . . . . . . . . . . . . . . 6

Special Handling Instructions for FBGA Package .................... 6

Input/Output Descriptions . . . . . . . . . . . . . . . . . . . 7

Logic Symbol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Ordering Information . . . . . . . . . . . . . . . . . . . . . . . 8

Device Bus Operations . . . . . . . . . . . . . . . . . . . . . . 9

Table 1. Device Bus Operations .......................................................9

Requirements for Asynchronous Read Operation (Non-Burst) 9

Requirements for Synchronous (Burst) Read Operation .......... 9

Continuous Burst ...................................................................... 9

8-, 16-, and 32-Word Linear Burst with Wrap Around ............ 10

Table 2. Burst Address Groups .......................................................10

Programmable Wait State ...................................................... 10

Handshaking Feature ............................................................. 10

Power Saving Function ........................................................... 11

Simultaneous Read/Write Operations with Zero Latency ....... 11

Writing Commands/Command Sequences ............................ 11

Accelerated Program Operation ............................................. 11

Autoselect Functions .............................................................. 11

Automatic Sleep Mode ........................................................... 12

RESET#: Hardware Reset Input ............................................. 12

Output Disable Mode .............................................................. 12

Hardware Data Protection ...................................................... 12

Low VCC Write Inhibit ............................................................ 12

Write Pulse "Glitch" Protection ............................................... 12

Logical Inhibit .......................................................................... 12

Common Flash Memory Interface (CFI) . . . . . . . 13

Table 3. CFI Query Identification String ..........................................13

Table 4. System Interface String .....................................................14

Table 5. Device Geometry Definition ..............................................14

Table 6. Primary Vendor-Specific Extended Query ........................15

Table 7. Sector Address Table ........................................................16

Command Definitions . . . . . . . . . . . . . . . . . . . . . . 20

Reading Array Data ................................................................ 20

Set Configuration Register Command Sequence ................... 20

Table 8. Burst Modes ......................................................................20

Handshaking Feature ............................................................. 20

Table 9. Wait States for Handshaking .............................................21

Enable PS (Power Saving) Mode Command Sequence ........ 21

Sector Lock/Unlock Command Sequence .............................. 21

Reset Command ..................................................................... 21

Autoselect Command Sequence ............................................ 21

Program Command Sequence ............................................... 22

Unlock Bypass Command Sequence ..................................... 22

Figure 1. Program Operation .......................................................... 23

Chip Erase Command Sequence ........................................... 23

Sector Erase Command Sequence ........................................ 23

Erase Suspend/Erase Resume Commands ........................... 24

Figure 2. Erase Operation.............................................................. 24

Table 10. Command Definitions .................................................... 25

Write Operation Status . . . . . . . . . . . . . . . . . . . . 26

DQ7: Data# Polling ................................................................. 26

Figure 3. Data# Polling Algorithm .................................................. 26

DQ6: Toggle Bit I .................................................................... 27

Figure 4. Toggle Bit Algorithm........................................................ 27

DQ2: Toggle Bit II ................................................................... 28

Table 11. DQ6 and DQ2 Indications .............................................. 28

Reading Toggle Bits DQ6/DQ2 ............................................... 28

DQ5: Exceeded Timing Limits ................................................ 28

DQ3: Sector Erase Timer ....................................................... 29

Table 12. Write Operation Status ................................................... 29

Absolute Maximum Ratings . . . . . . . . . . . . . . . . 30

Figure 5. Maximum Negative Overshoot Waveform ...................... 30

Figure 6. Maximum Positive Overshoot Waveform ........................ 30

Operating Ranges . . . . . . . . . . . . . . . . . . . . . . . . . 30

DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . 31

Test Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Figure 7. Test Setup....................................................................... 32

Table 13. Test Specifications ......................................................... 32

Key to Switching Waveforms. . . . . . . . . . . . . . . . 32

Switching Waveforms. . . . . . . . . . . . . . . . . . . . . . 32

Figure 8. Input Waveforms and

Measurement Levels...................................................................... 32

AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . 33

Synchronous/Burst Read ........................................................ 33

Figure 9. Burst Mode Read (66 and 54 MHz) ................................ 33

Figure 10. Burst Mode Read (40 MHz) .......................................... 34

Asynchronous Read ............................................................... 35

Figure 11. Asynchronous Mode Read............................................ 35

Figure 12. Reset Timings ............................................................... 36

Erase/Program Operations ..................................................... 37

Figure 13. Program Operation Timings.......................................... 38

Figure 14. Chip/Sector Erase Operations ...................................... 39

Figure 15. Accelerated Unlock Bypass Programming Timing........ 40

Figure 16. Data# Polling Timings (During Embedded Algorithm) .. 41

Figure 17. Toggle Bit Timings (During Embedded Algorithm)........ 41

Figure 18. 8-, 16-, and 32-Word Linear Burst

Address Wrap Around.................................................................... 42

Figure 19. Latency with Boundary Crossing (54 MHz and 66 MHz) 42

Figure 20. Initial Access with Power Saving (PS)

Function and Address Boundary Latency ...................................... 43

Figure 21. Example of Extended Valid Address Reducing Wait State

Usage............................................................................................. 43

Figure 22. Back-to-Back Read/Write Cycle Timings ...................... 44

Erase and Programming Performance . . . . . . . 45

Data Retention. . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Physical Dimensions* . . . . . . . . . . . . . . . . . . . . . 46

VDA044--44-Ball Very Thin Fine-Pitch Ball Grid Array

(FBGA) 9.2 x 8.0 mm Package ............................................... 46

Revision Summary . . . . . . . . . . . . . . . . . . . . . . . . 47

4

Am29BDS643G

November 9, 2001

A D V A N C E I N F O R M A T I O N

PRODUCT SELECTOR GUIDE

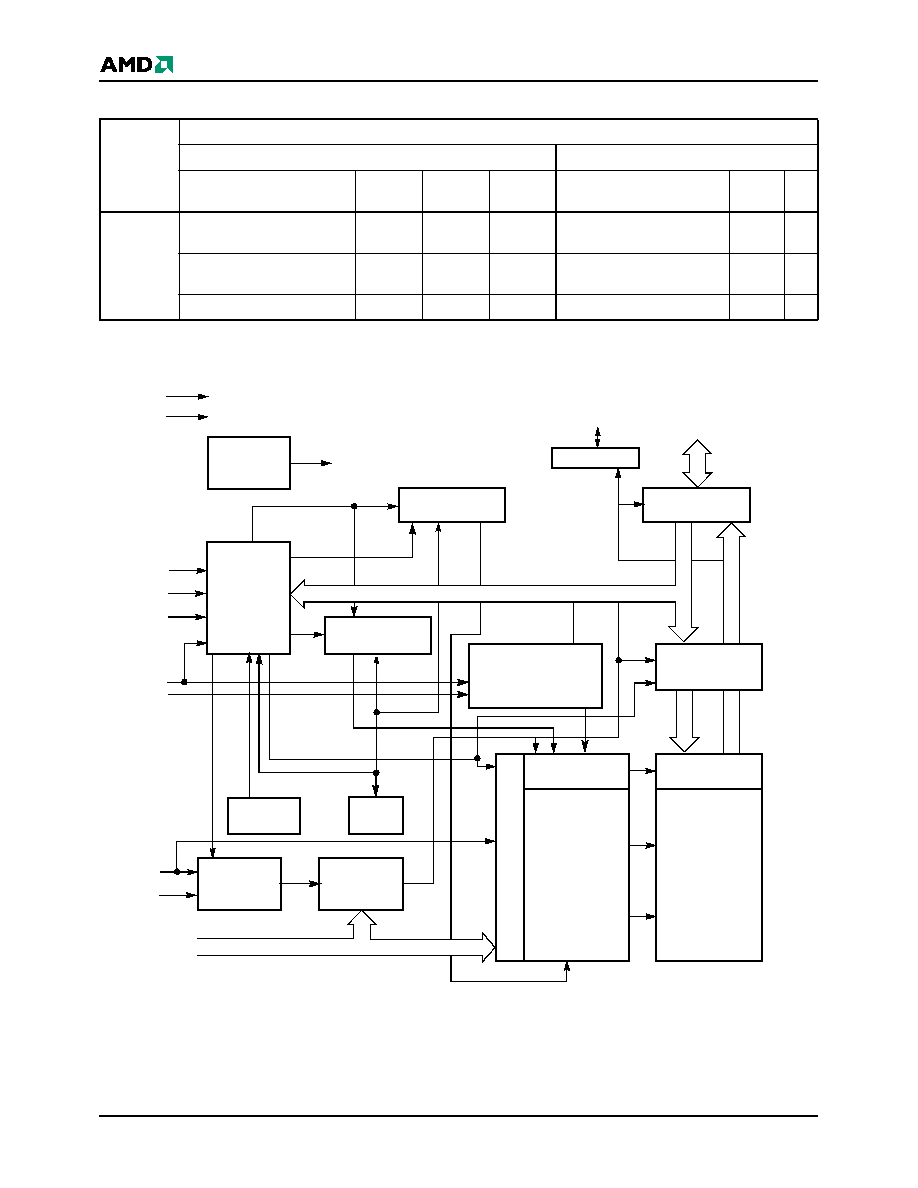

BLOCK DIAGRAM

Part

Number

Am29BDS643G

Synchronous/Burst

Asynchronous

Speed Option

7G

(40 MHz)

7M

(54 MHz)

5K

(66 MHz)

Speed Option

7G/7M

5K

V

CC

=

1.7 ≠ 1.9 V

Max Initial Access Time, ns

(t

IACC

)

95

87.5

71

Max Access Time, ns (t

ACC

)

70

55

Max Burst Access Time, ns

(t

BACC

)

20

13.5

11

Max CE# Access, ns (t

CE

)

70

55

Max OE# Access, ns (t

OE

)

20

13.5

11

Max OE# Access, ns (t

OE

)

20

11

Input/Output

Buffers

X-Decoder

Y-Decoder

Chip Enable

Output Enable

Logic

Erase Voltage

Generator

PGM Voltage

Generator

Timer

V

CC

Detector

State

Control

Command

Register

V

CC

V

SS

WE#

RESET#

V

PP

CE#

OE#

A/DQ0

≠

A/DQ15

Data

Latch

Y-Gating

Cell Matrix

A

ddr

es

s

Lat

c

h

A/DQ0≠A/DQ15

A16≠A21

RDY

Buffer

RDY

Burst

State

Control

Burst

Address

Counter

PS Buffer

PS

AVD#

CLK

A0≠A21

November 9, 2001

Am29BDS643G

5

A D V A N C E I N F O R M A T I O N

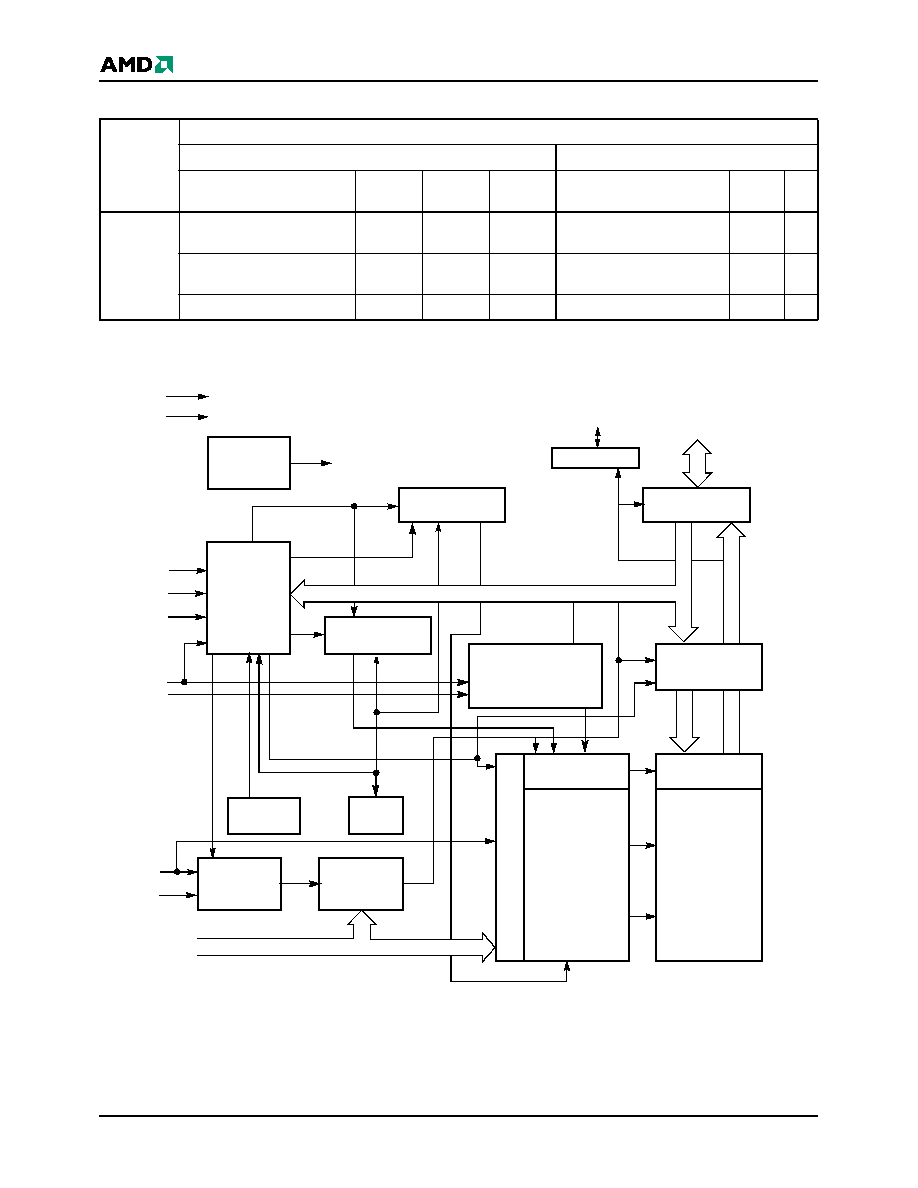

BLOCK DIAGRAM OF

SIMULTANEOUS OPERATION CIRCUIT

Note: A0≠A15 are multiplexed with DQ0≠DQ15.

V

CC

V

SS

Bank B Address

RESET#

WE#

CE#

AVD#

DQ0≠DQ15

STATE

CONTROL

&

COMMAND

REGISTER

Bank B

X-Decoder

Y-Decoder

Latches and

Control Logic

Bank A

X-Decoder

Y-Decoder

Latches and

Control Logic

DQ0≠DQ15

DQ0≠DQ15

DQ0≠DQ15

DQ0≠DQ15

DQ0≠

DQ15

Bank C

Y-Decoder

X-Decoder

Latches and

Control Logic

Bank D

Y-Decoder

X-Decoder

Latches and

Control Logic

OE#

OE#

OE#

OE#

Status

Control

A0≠A21

A0≠A21

A0≠A21

A0≠A21

A0≠A21

Bank C Address

Bank D Address

Bank A Address

PS

RDY