PRELIMINARY

1M x 36/2M x 18/512K x 72 Pipelined SRAM

with NoBLTM Architecture

CY7C1460V25

CY7C1462V25

CY7C1464V25

Cypress Semiconductor Corporation

·

3901 North First Street

·

San Jose, CA 95134

·

408-943-2600

Document #: 38-05191 Rev. *B

Revised November 14, 2002

Features

· Zero Bus Latency

, no dead cycles between write and

read cycles

· Fast clock speed: 250, 200, and 167 MHz

· Fast access time: 2.7, 3.0 and 3.5 ns

· Internally synchronized registered outputs eliminate

the need to control OE

· Single 2.5V ±5% power supply V

DD

· Separate V

DDQ

for 2.5V or 1.8V I/O

· Single WE (Read/Write) control pin

· Positive clock-edge triggered, address, data, and

control signal registers for fully pipelined applications

· Interleaved or linear four-word burst capability

· Individual byte write (BWS

a

BWS

h

) control (may be tied

LOW)

· CEN pin to enable clock and suspend operations

· Three chip enables for simple depth expansion

· JTAG boundary scan for BGA packaging version

· Available in 119-ball bump BGA, 165-ball FBGA

package and 100-pin TQFP packages (CY7C1460V25

and CY7C1462V25). 209 FBGA package for

CY7C1464V25

Functional Description

The CY7C1460V25,CY7C1462V25 and CY7C1464V25

SRAMs are designed to eliminate dead cycles when transi-

tions from READ to WRITE or vice versa. These SRAMs are

optimized for 100 percent bus utilization and achieves Zero

Bus Latency. They integrate 1,048,576 x 36/2,097,152 x 18/

524,288 x 72 SRAM cells, respectively, with advanced

synchronous peripheral circuitry and a two-bit counter for

internal burst operation. The Synchronous Burst SRAM family

employs high-speed, low-power CMOS designs using

advanced single layer polysilicon, three-layer metal

technology. Each memory cell consists of six transistors.

All synchronous inputs are gated by registers controlled by a

positive-edge-triggered Clock Input (CLK). The synchronous

inputs include all addresses, all data inputs, depth-expansion

Chip Enables (CE

1

, CE

2

, and CE

3

), cycle start input (ADV/LD),

Clock Enable (CEN), Byte Write Selects (BWS

a

, BWS

b

,

BWS

c

,BWS

d,

BWS

e

, BWS

f

, BWS

g

, BWS

h

), and read-write

control (WE). BWS

c

and BWS

d

apply to CY7C1460V25 and

CY7C1464V25 only.BWS

e

, BWS

f,

BWS

g

, and BWS

h

apply to

CY7C1464V25 only

Address and control signals are applied to the SRAM during

one clock cycle, and two cycles later, its associated data

occurs, either read or write.

A Clock Enable (CEN) pin allows operation of the

CY7C1460V25,CY7C1462V25 and CY7C1464V25 to be

suspended as long as necessary. All synchronous inputs are

ignored when (CEN) is high and the internal device registers

will hold their previous values.

There are three Chip Enable (CE

1

, CE

2

, CE

3

) pins that allow

the user to deselect the device when desired. If any one of

these three are not active when ADV/LD is low, no new

memory operation can be initiated and any burst cycle in

progress is stopped. However, any pending data transfers

(read or write) will be completed. The data bus will be in high

impedance state two cycles after chip is deselected or a write

cycle is initiated.

The CY7C1460V25,CY7C1462V25 and CY7C1464V25 have

an on-chip two-bit burst counter. In the burst mode,

CY7C1460V25,CY7C1462V25 and CY7C1464V25 provide

four cycles of data for a single address presented to the

SRAM. The order of the burst sequence is defined by the

MODE input pin. The MODE pin selects between linear and

interleaved burst sequence. The ADV/LD signal is used to load

a new external address (ADV/LD = LOW) or increment the

internal burst counter (ADV/LD = HIGH)

Output Enable (OE) and burst sequence select (MODE) are

the asynchronous signals. OE can be used to disable the

outputs at any given time. ZZ may be tied to LOW if it is not

used.

Four pins are used to implement JTAG test capabilities. The

JTAG circuitry is used to serially shift data to and from the

device. JTAG inputs use LVTTL/LVCMOS levels to shift data

during this testing mode of operation.

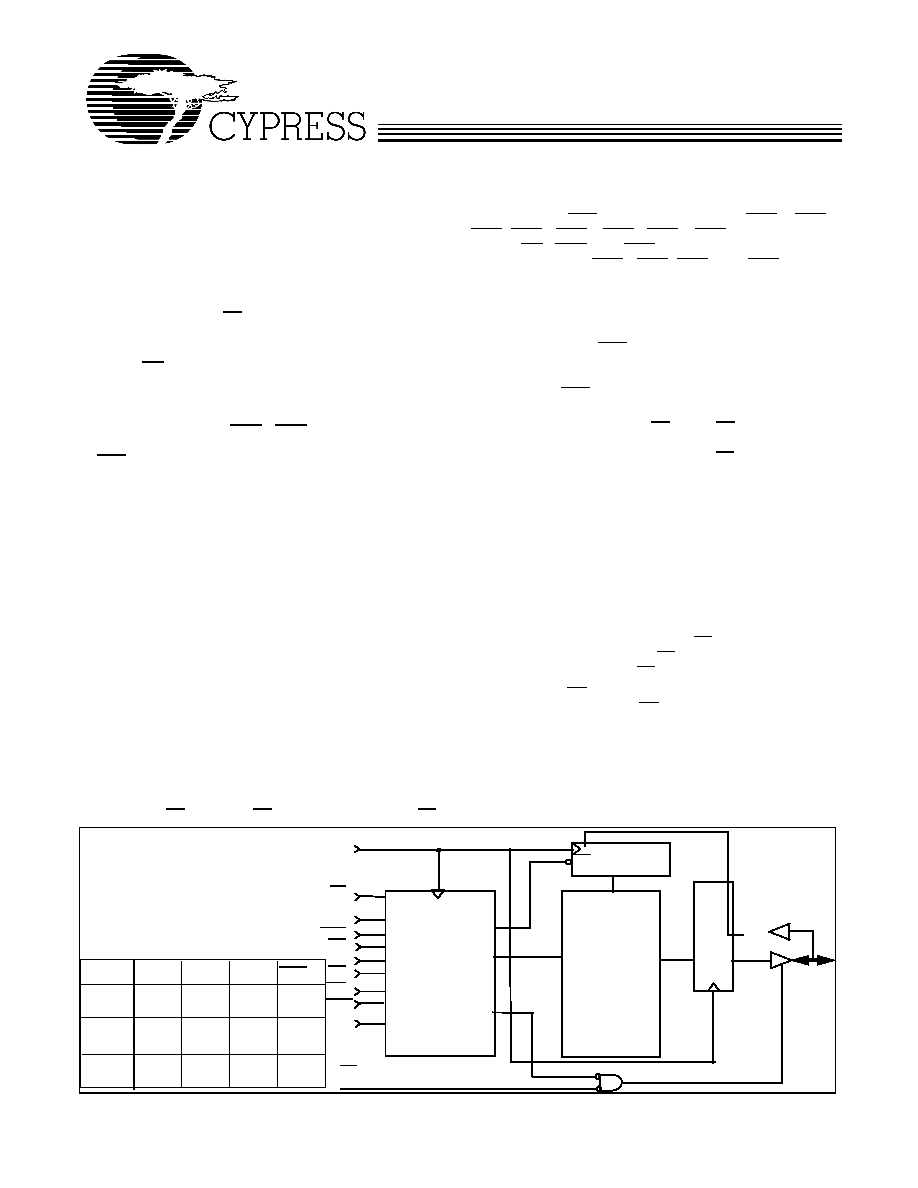

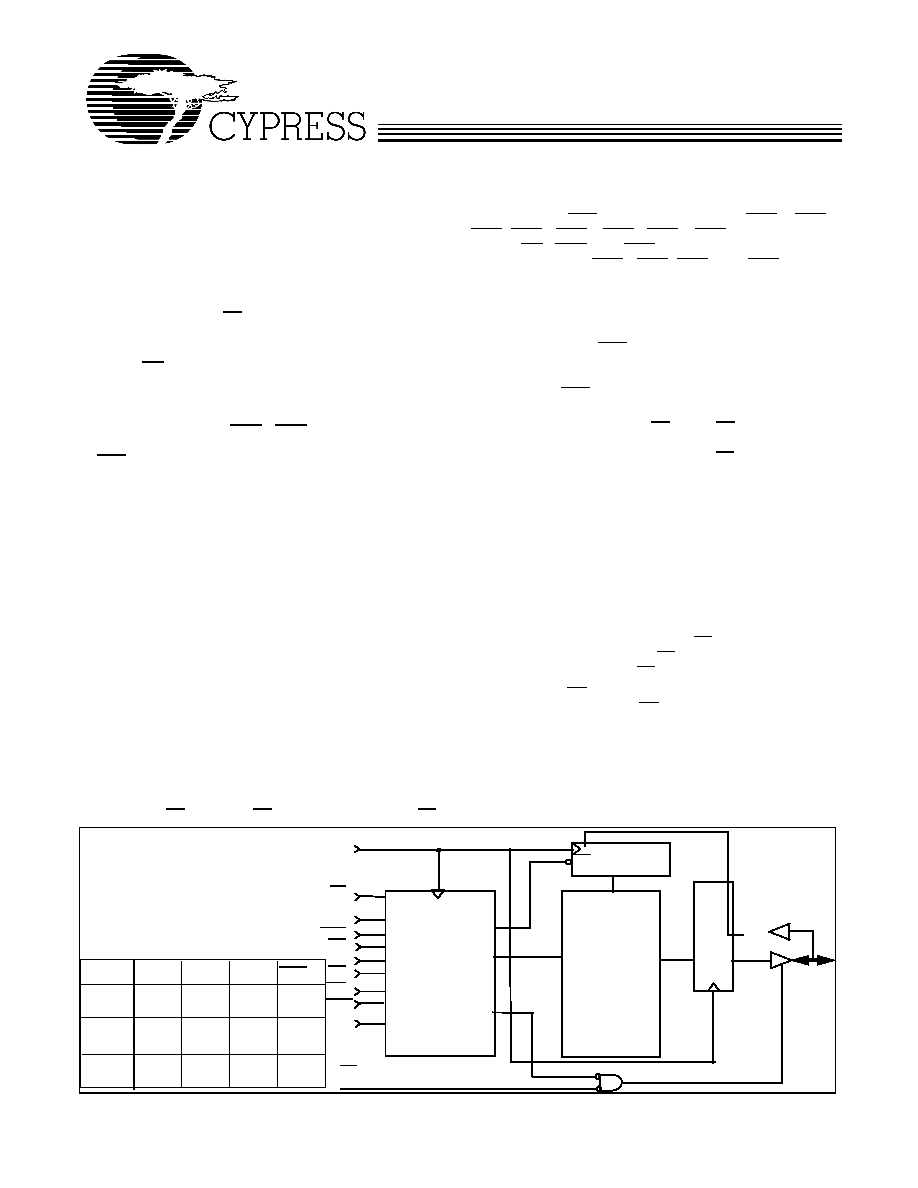

CLK

A

x

CEN

WE

BWS

x

CE

1

CE

CE

2

OE

1Mx36

MEMORY

ARRAY

Logic Block Diagram

DQ

x

Data-In REG.

Q

D

CE

CONTROL

and WRITE

LOGIC

3

ADV/LD

Mode

DP

x

2Mx18

OU

T

O

U

T

RE

GIS

TE

RS

and LOGIC

1Mx36

2Mx18

A

X

DQ

X

DP

X

BWS

X

X = 19:0

X = 20:0 X = a, b

X= a, b,

512Kx72

X = 18:0

X = a, b,

c, d

X = a, b

c, d

, c, d

X = a, b

X = a, b

X = a, b,

c,d,e,f,g,h

X = a, b,

c,d,e,f,g,h c,d,e,f,g,h

X = a, b

512Kx72

PRELIMINARY

CY7C1460V25

CY7C1462V25

CY7C1464V25

Document #: 38-05191 Rev. *B

Page 2 of 26

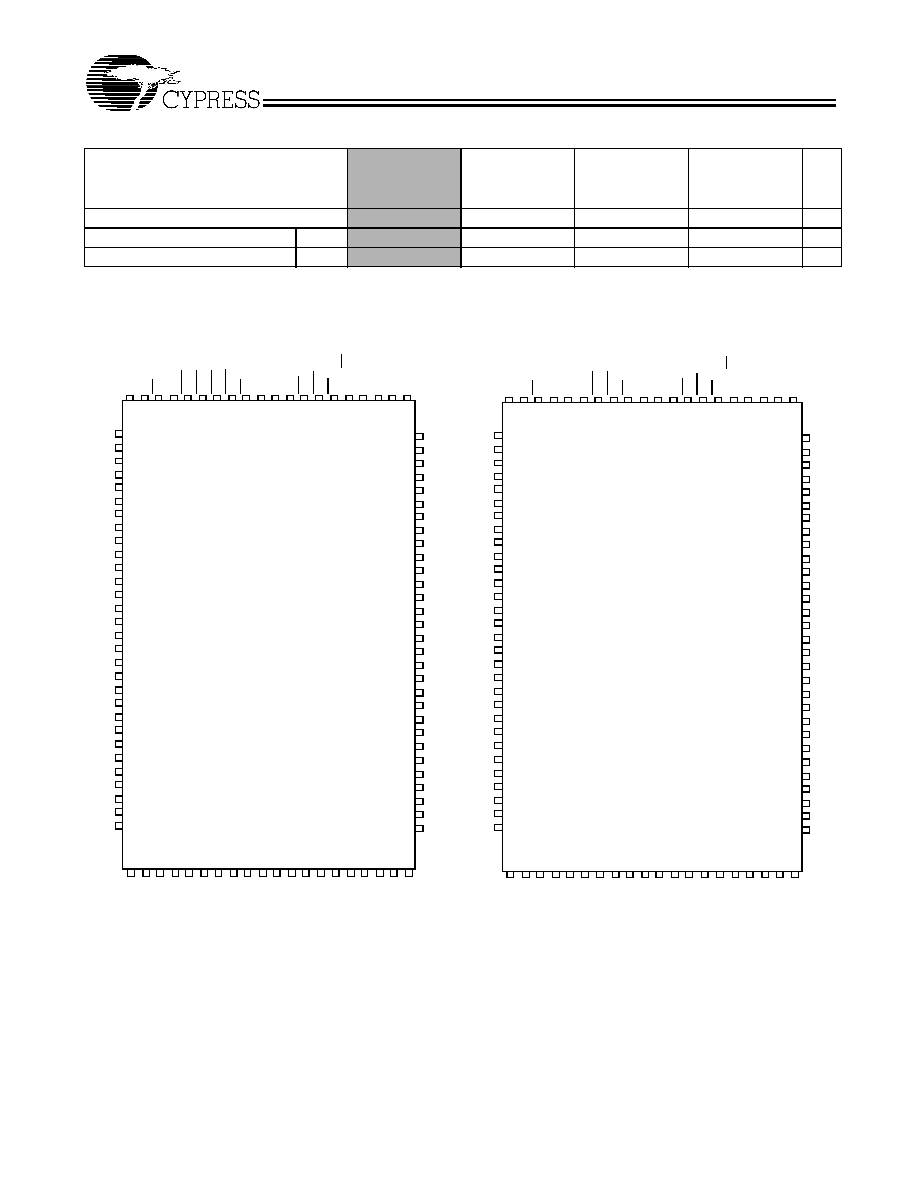

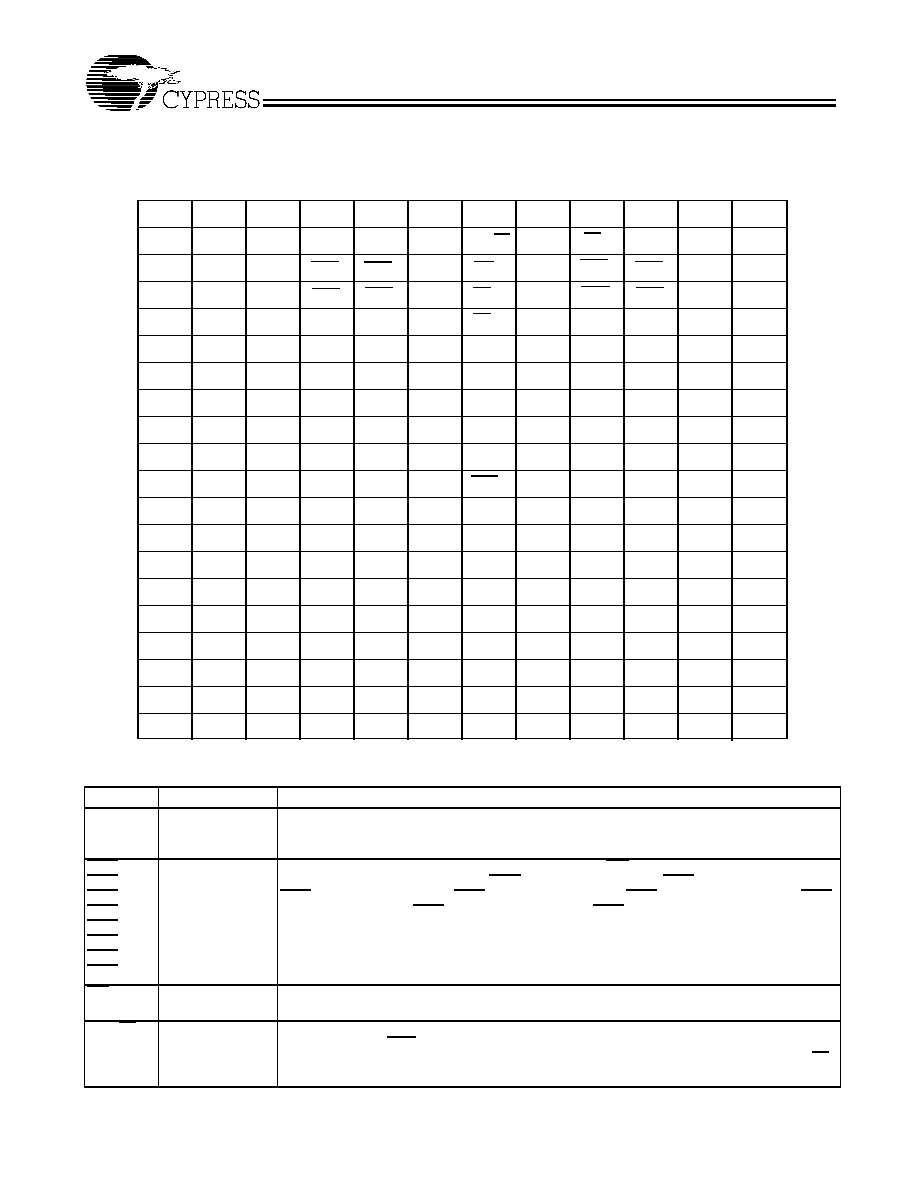

Selection Guide

CY7C1460V25C

Y7C1462V25

CY7C1464V25

-300

CY7C1460V25C

Y7C1462V25

CY7C1464V25

-250

CY7C1460V25C

Y7C1462V25CY7

C1464V25

-200

CY7C1460V25C

Y7C1462V25

CY7C1464V25

-167

Unit

Maximum Access Time

2.3

2.7

3.0

3.5

ns

Maximum Operating Current

Com'l

TBD

TBD

TBD

TBD

mA

Maximum CMOS Standby Current

TBD

TBD

TBD

TBD

mA

Shaded areas contain advance information.

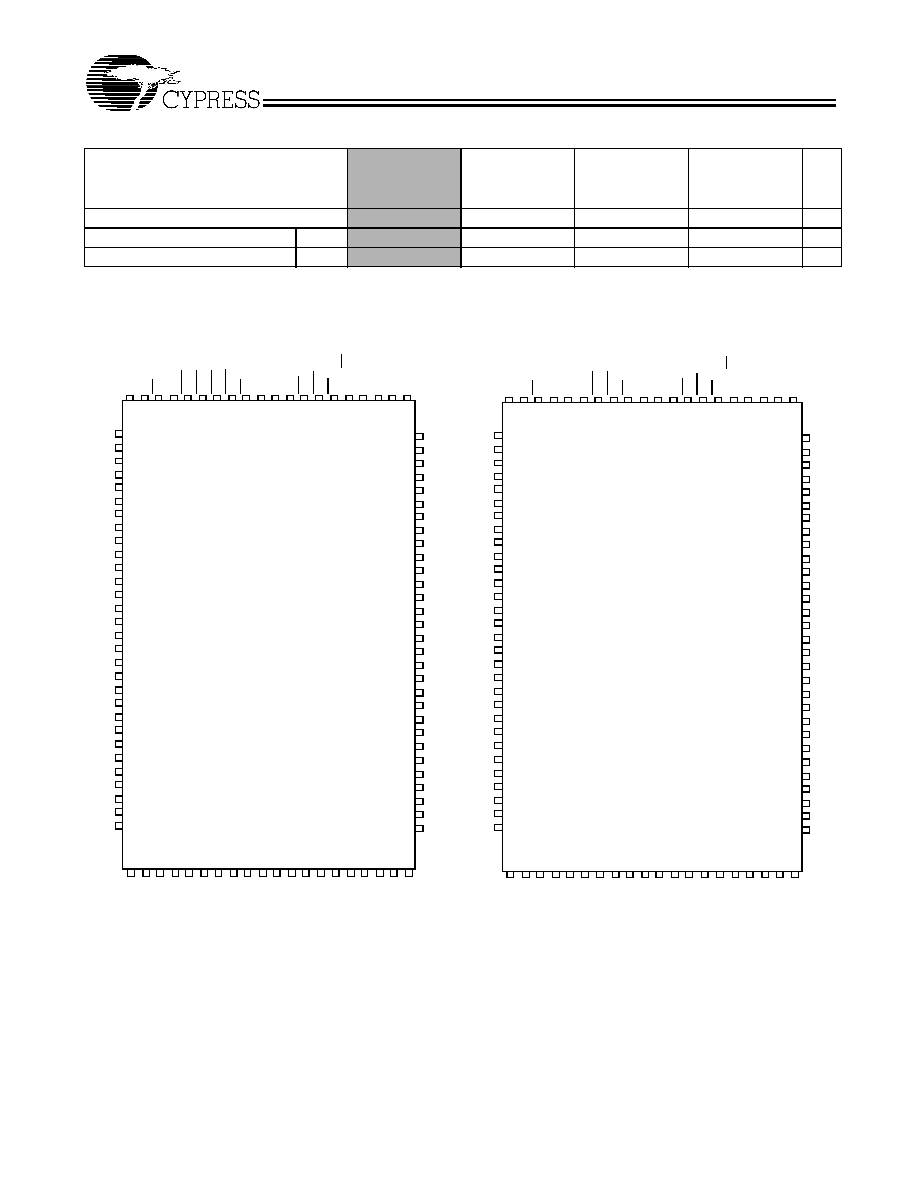

Pin Configurations

A

A

A

A

A

1

A

0

NC

NC

V

SS

V

DD

A

A

A

A

A

A

V

DDQ

V

SS

DQb

DQb

DQb

V

SS

V

DDQ

DQb

DQb

V

SS

NC

V

DD

DQa

DQa

V

DDQ

V

SS

DQa

DQa

V

SS

V

DDQ

V

DDQ

V

SS

DQc

DQc

V

SS

V

DDQ

DQc

DQc

V

DD

V

SS

DQd

DQd

V

DDQ

V

SS

DQd

DQd

DQd

V

SS

V

DDQ

A

A

CE

1

CE

2

BW

S

a

CE

3

V

DD

V

SS

CLK

WE

CEN

OE

A

A

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

A

A

ADV/L

D

ZZ

CY7C1460V25

100-pin TQFP Packages

A

A

A

A

A

1

A

0

NC

NC

V

SS

V

DD

A

A

A

A

A

A

A

NC

NC

V

DDQ

V

SS

NC

DPa

DQa

DQa

V

SS

V

DDQ

DQa

DQa

V

SS

NC

V

DD

DQa

DQa

V

DDQ

V

SS

DQa

DQa

NC

NC

V

SS

V

DDQ

NC

NC

NC

NC

NC

NC

V

DDQ

V

SS

NC

NC

DQb

DQb

V

SS

V

DDQ

DQb

DQb

NC

V

DD

V

SS

DQb

DQb

V

DDQ

V

SS

DQb

DQb

DPb

NC

V

SS

V

DDQ

NC

NC

NC

A

A

CE

1

CE

2

NC

NC

BW

S

b

BW

S

a

CE

3

V

DD

V

SS

CLK

WE

CEN

OE

A

A

A

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

10

0

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

A

A

ADV/L

D

ZZ

MO

D

E

NC

BW

S

d

MO

D

E

BW

S

c

DQc

DQc

DQc

DQc

DPc

DQd

DQd

DPd

DQd

NC

DPb

DQb

DQa

DQa

DQa

DQa

DPa

DQb

DQb

(1M x 36)

CY7C1462V25

BW

S

b

NC

NC

A

A

NC

A

(2M x 18)

PRELIMINARY

CY7C1460V25

CY7C1462V25

CY7C1464V25

Document #: 38-05191 Rev. *B

Page 5 of 26

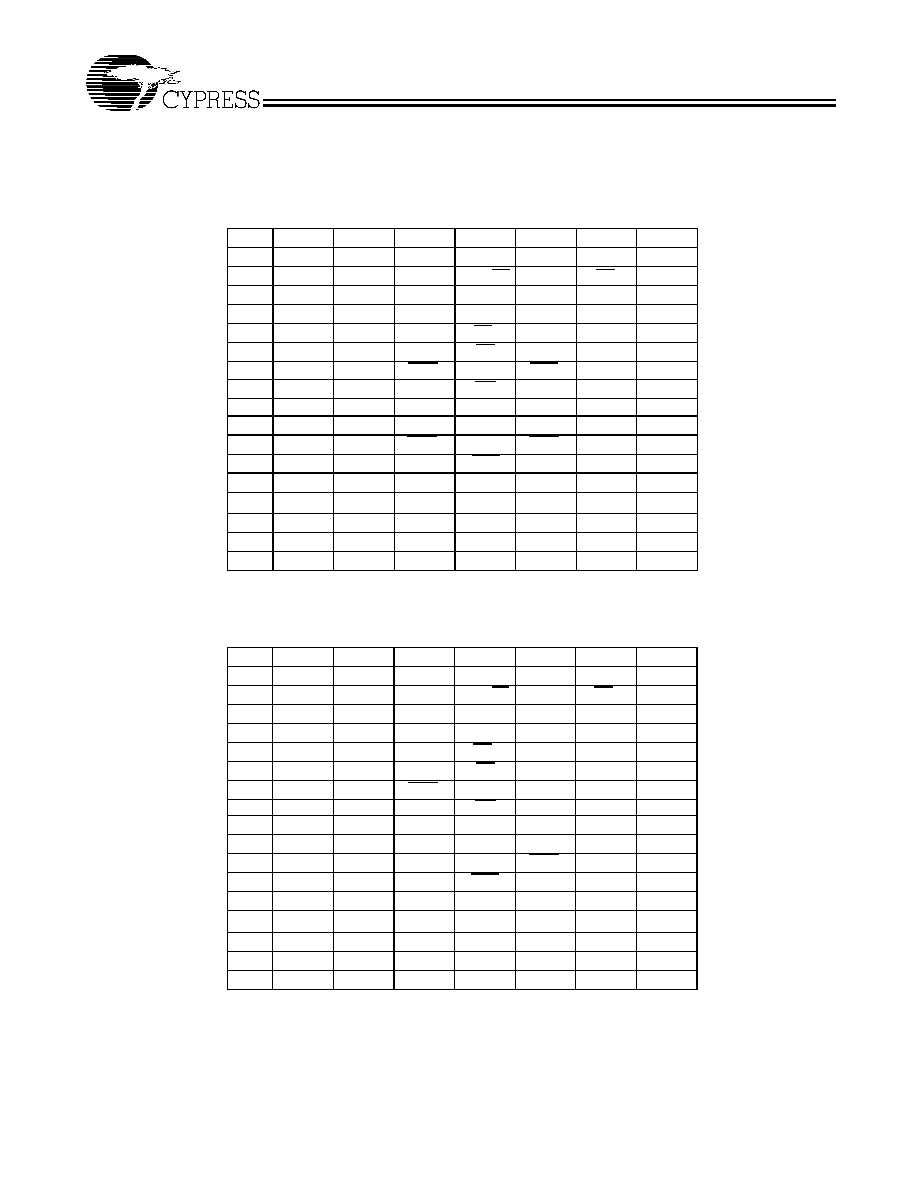

Pin Configurations

(continued)

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

1

2

3

4

5

6

7

8

9

11

10

DQg

DQg

DQg

DQg

DQg

DQg

DQg

DQg

DQc

DQc

DQc

DQc

NC

DPg

DQh

DQh

DQh

DQh

DQd

DQd

DQd

DQd

DPd

DPc

DQc

DQc

DQc

DQc

NC

DQh

DQh

DQh

DQh

DPh

DQd

DQd

DQd

DQd

DQb

DQb

DQb

DQb

DQb

DQb

DQb

DQb

DQf

DQf

DQf

DQf

NC

DPf

DQa

DQa

DQa

DQa

DQe

DQe

DQe

DQe

DPa

DPb

DQf

DQf

DQf

DQf

NC

DQa

DQa

DQa

DQa

DPe

DQe

DQe

DQe

DQe

A

A

A

A

NC

NC

NC

72M

A

NC

A

A

A

A

A

A

A1

A0

A

A

A

A

A

A

NC

NC

NC

NC

NC

NC

BWS

b

BWS

f

BWS

e

BWS

a

BWS

c

BWS

g

BWS

d

BWS

h

TMS

TDI

TDO

TCK

NC

NC

MODE

NC

CEN

V

SS

NC

CLK

NC

V

SS

V

DD

V

DD

V

DD

V

DD

V

DD

V

DD

V

DD

V

DD

V

DD

V

DD

V

DD

V

DD

V

DD

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

NC

V

DD

NC

OE

CE

3

CE

1

CE

2

ADV/LD

WE

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

ZZ

V

SS

V

SS

V

SS

V

SS

NC

V

DDQ

V

SS

V

SS

NC

V

SS

V

SSQ

V

SS

V

SS

V

SS

V

SS

NC

V

SS

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

NC

V

DDQ

V

DDQ

V

DDQ

V

DDQ

NC

V

DDQ

V

DDQ

V

DDQ

V

DDQ

NC

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

209-ball Bump BGA

CY7C1464V25 (512K x72)

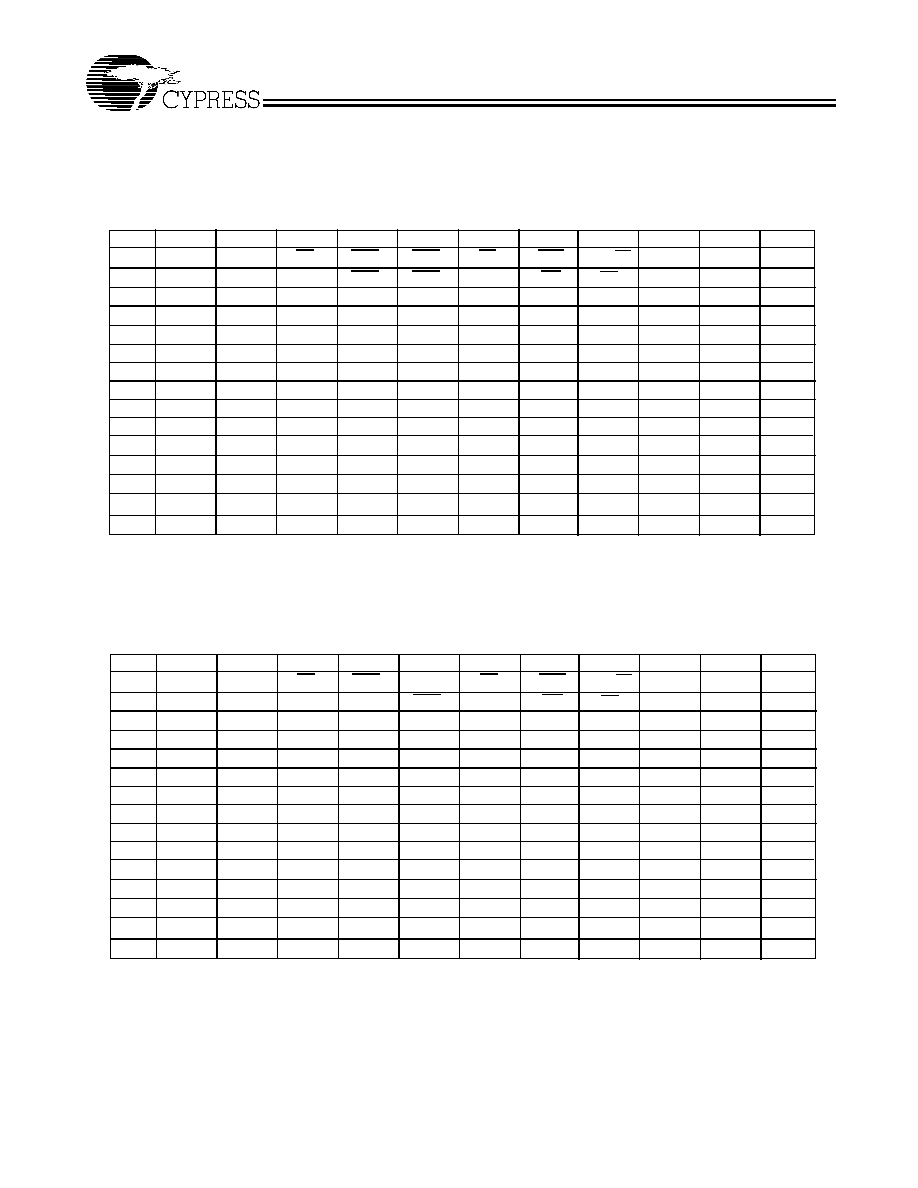

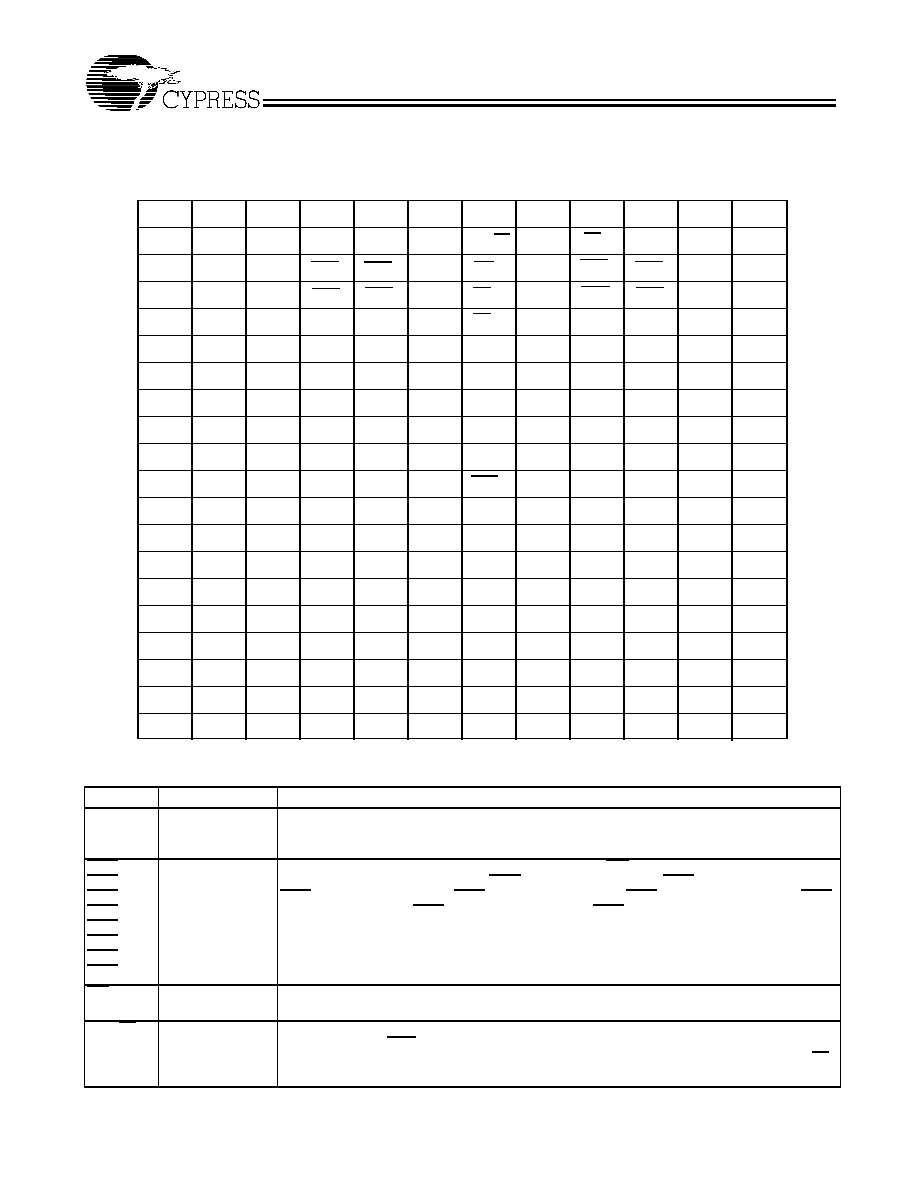

Pin Definitions

Pin Name

I/O Type

Pin Description

A0

A1

A

Input-

Synchronous

Address Inputs used to select one of the 1048576/2097152/524,288 address locations.

Sampled at the rising edge of the CLK.

BWS

a

BWS

b

BWS

c

BWS

d

BWS

e

BWS

f

BWS

g

BWS

h

Input-

Synchronous

Byte Write Select Inputs, active LOW. Qualified with WE to conduct writes to the SRAM.

Sampled on the rising edge of CLK. BWS

a

controls DQ

a

and DP

a

, BWS

b

controls DQ

b

and DP

b

,

BWS

c

controls DQ

c

and DP

c

, BWS

d

controls DQ

d

and DP

d

.BWS

e

controls DQ

e

and DP

e

, BWS

f

controls DQ

f

and DP

f

, BWS

g

controls DQ

g

and DP

g

, BWS

h

controls DQ

h

and DP

h

.

WE

Input-

Synchronous

Write Enable Input, active LOW. Sampled on the rising edge of CLK if CEN is active LOW.

This signal must be asserted LOW to initiate a write sequence.

ADV/LD

Input-

Synchronous

Advance/Load Input used to advance the on-chip address counter or load a new address.

When HIGH (and CEN is asserted LOW) the internal burst counter is advanced. When LOW,

a new address can be loaded into the device for an access. After being deselected, ADV/LD

should be driven LOW in order to load a new address.