| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: HI5728 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

1

File Number

4321.4

HI5728

10-Bit, 125/60MSPS, Dual High Speed

CMOS D/A Converter

The HI5728 is a 10-bit, dual 125MSPS D/A converter which

is implemented in an advanced CMOS process. It is

designed for high speed applications where integration,

bandwidth and accuracy are essential. Operating from a

single +5V or +3V supply, the converter provides 20.48mA of

full scale output current and includes an input data register.

Low glitch energy and excellent frequency domain

performance are achieved using a segmented architecture.

A 60MSPS version and an 8-bit (HI5628) version are also

available. Comparable single DAC solutions are the HI5760

(10-bit) and the HI5660 (8-bit). This DAC is a member of the

CommLinkTM family of communication devices.

Features

∑ Throughput Rate . . . . . . . . . . . . . . . . . . . . . . . .125MSPS

∑ Low Power . . . . . . . . . . . . . . . 330mW at 5V, 54mW at 3V

∑ Integral Linearity Error . . . . . . . . . . . . . . . . . . . . .

±

1 LSB

∑ Differential Linearity . . . . . . . . . . . . . . . . . . . . . .

±

0.5 LSB

∑ Gain Matching (Typ) . . . . . . . . . . . . . . . . . . . . . . . . . .0.5%

∑ SFDR at 5MHz Output . . . . . . . . . . . . . . . . . . . . . . .68dBc

∑ Single Power Supply from +5V to +3V

∑ CMOS Compatible Inputs

∑ Excellent Spurious Free Dynamic Range

∑ Internal Voltage Reference

∑ Dual 10-Bit D/A Converters on a Monolithic Chip

Applications

∑ Wireless Local Loop

∑ Direct Digital Frequency Synthesis

∑ Wireless Communications

∑ Signal Reconstruction

∑ Arbitrary Waveform Generators

∑ Test Equipment/Instrumentation

∑ High Resolution Imaging Systems

Pinout

HI5728

(LQFP)

TOP VIEW

Ordering Information

PART

NUMBER

TEMP.

RANGE

(

o

C)

PACKAGE

PKG. NO.

MAX

CLOCK

SPEED

HI5728IN

-40 to 85 48 Ld LQFP

Q48.7x7A

125MHz

HI5728/6IN

-40 to 85 48 Ld LQFP

Q48.7x7A

60MHz

HI5728EVAL1

25

Evaluation Platform

125MHz

1

2

3

4

5

6

7

8

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

9

10

11

12

13 14 15 16

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

QD6

QD5

QD4

QD3

QD2

QD1

QD0 (LSB)

DV

DD

DGND

NC

AV

DD

AGND

ID6

ID5

ID4

ID3

ID2

SLEEP

DV

DD

DGND

NC

AV

DD

ID1

ID0 (LSB)

ID7

ID8

ID9 (MSB)

DV

DD

DGND

QCLK

DGND

DV

DD

QD9 (MSB)

QD8

QD7

ICLK

A

GND

ICOMP1

REFLO

IOUT

A

IOUTB

A

GND

A

GND

QOUTB

QOUT

A

FSADJ

REFIO

QCOMP1

Data Sheet

July 1999

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143

|

Copyright

©

Intersil Corporation 1999

CommLinkTM is a trademark of Intersil Corporation.

2

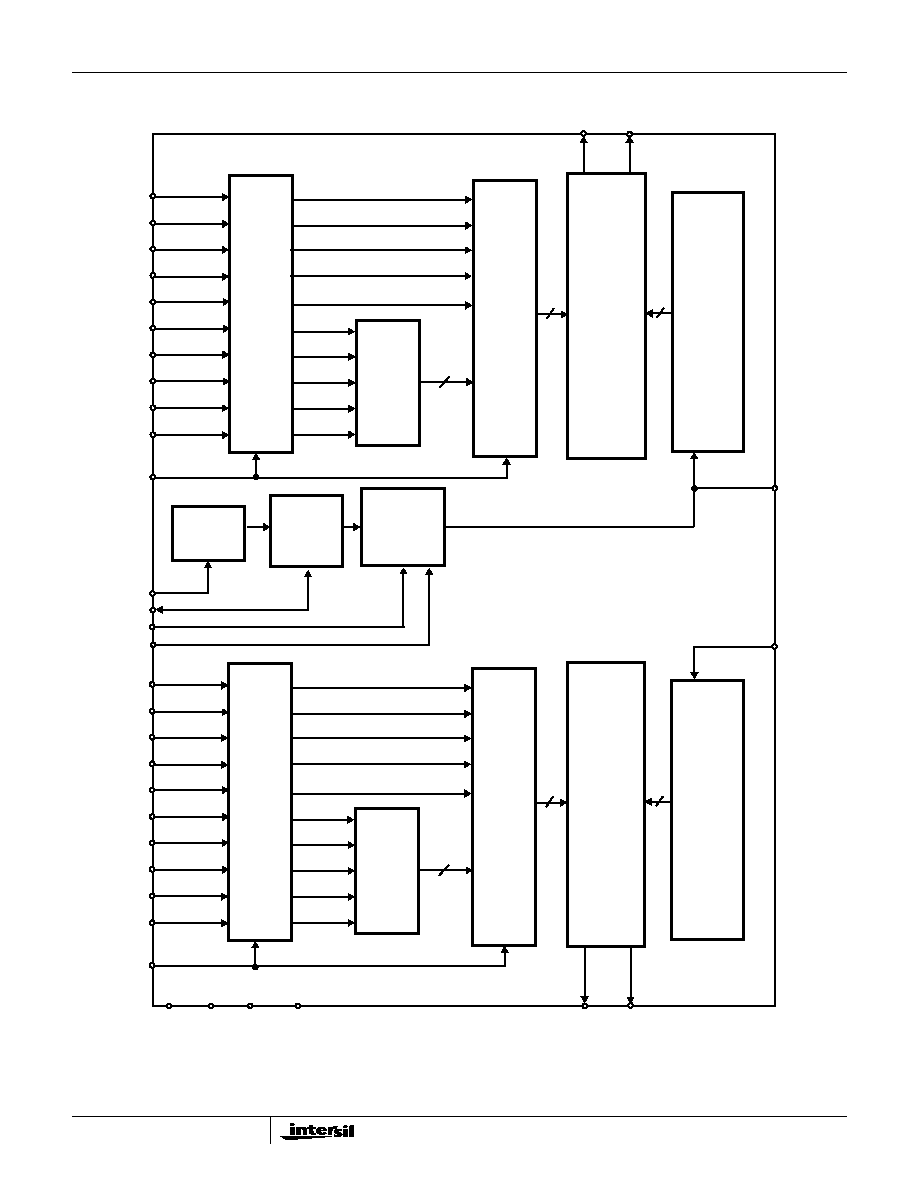

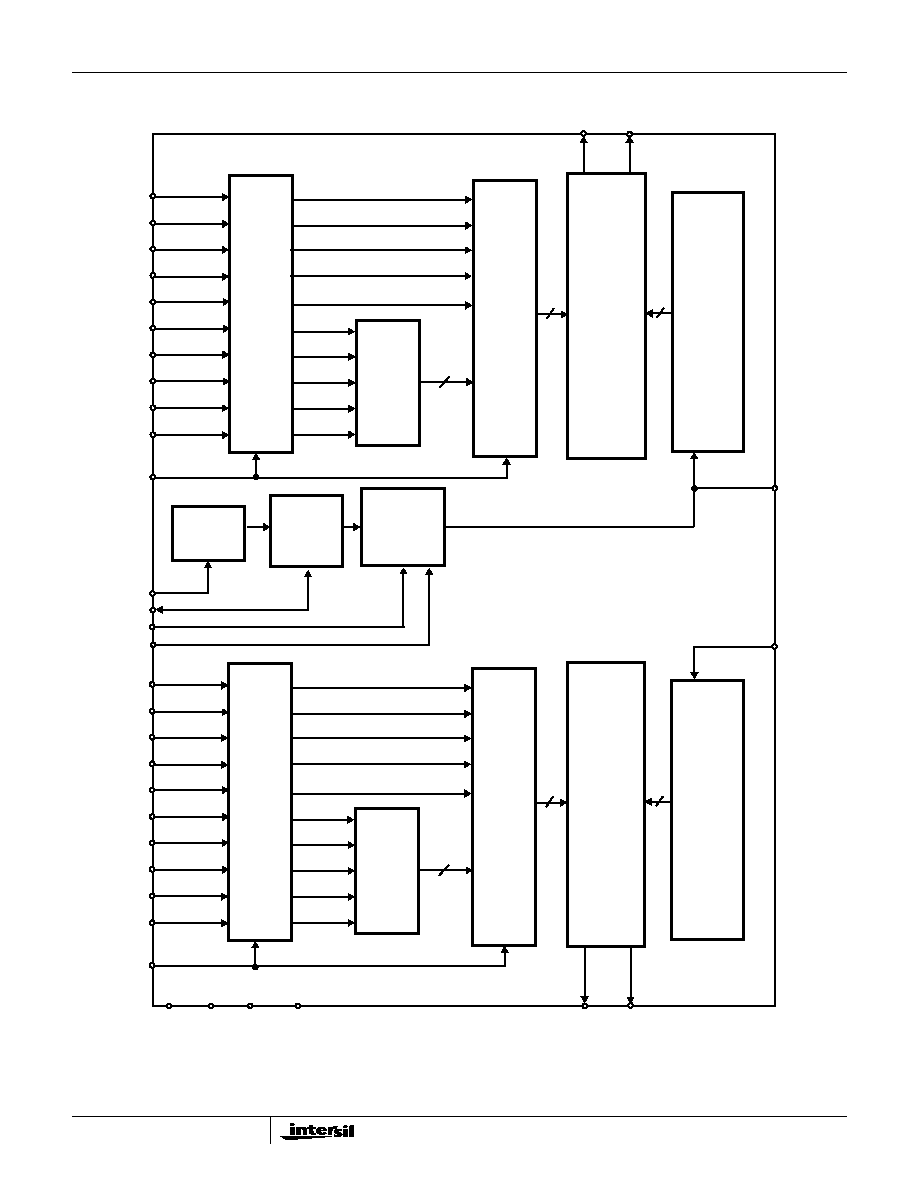

Functional Block Diagram

UPPER

VOLTAGE

REFERENCE

(LSB) ID0

ID1

ID2

ID3

ID4

ID5

ID6

(MSB) ID9

ICLK

ID7

ID8

5-BIT

DECODER

REFIO

LATCH

AV

DD

AGND

DV

DD

DGND

LATCH

CASCODE

CURRENT

SOURCE

SWITCH

MATRIX

BIAS

GENERATION

INT/EXT

FSADJ

REFERENCE

INT/EXT

SELECT

REFLO

31

36

36

31 MSB

SEGMENTS

5 LSBs

+

ICOMP1

SLEEP

IOUTA

IOUTB

UPPER

(LSB) QD0

QD1

QD2

QD3

QD4

QD5

QD6

QCLK

QD7

QD8

5-BIT

DECODER

LATCH

LATCH

CASCODE

CURRENT

SOURCE

SWITCH

MATRIX

31

36

36

31 MSB

SEGMENTS

5 LSBs

+

QCOMP1

QOUTA QOUTB

HI5728

3

Typical Applications Circuit

IOUTB

IOUTA

50

+5V OR +3V SUPPLY

0.1

µ

F

50

10

µ

F

50

0.1

µ

F

2k

FERRITE

10

µ

H

+

BEAD

R

SET

1

2

3

4

5

6

7

8

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

9

10

11

12

13 14 15 16

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

AV

DD

(POWER PLANE)

ID7

ID6

ID5

ID8

ID9 (MSB)

QD9 (MSB)

ID4

ID3

ID2

ID1

ID0 (LSB)

QD8

QD7

QD6

QD5

QD4

QD3

QD2

QD1

QD0 (LSB)

I

CLK

/Q

CLK

DV

DD

0.1

µ

F

DV

DD

SLEEP

DV

DD

0.1

µ

F

DV

DD

DGND

NC (GROUND)

AV

DD

AGND

ICOMP1

0.1

µ

F

0.1

µ

F

AV

DD

A

GND

QOUTA

QOUTB

50

50

0.1

µ

F

REFIO

QCOMP1

0.1

µ

F

AV

DD

0.1

µ

F

AV

DD

AGND

AV

DD

0.1

µ

F

DV

DD

DGND

DV

DD

NC (GROUND)

+5V OR +3V SUPPLY

0.1

µ

F

10

µ

F

FERRITE

10

µ

H

+

BEAD

DV

DD

(POWER PLANE)

ANALOG

GROUND

PLANE

DIGITAL

GROUND

PLANE

NOTE: ICOMP1 AND QCOMP1

PINS (24, 14) MUST BE TIED

TOGETHER EXTERNALLY

HI5728

4

Pin Descriptions

PIN NO.

PIN NAME

PIN DESCRIPTION

39-30

QD9 (MSB) Through

QD0 (LSB)

Digital Data Bit 9, the Most Significant Bit through Digital Data Bit 0, the Least Significant Bit, of the Q

channel.

1-6, 48-46

ID9 (MSB) Through

ID0 (LSB)

Digital Data Bit 9, the Most Significant Bit through Digital Data Bit 0, the Least Significant Bit, of the I chan-

nel.

8

SLEEP

Control Pin for Power-Down mode. Sleep Mode is active high; Connect to ground for Normal Mode. Sleep

pin has internal 20

µ

A active pull-down current.

15

REFLO

Connect to analog ground to enable internal 1.2V reference or connect to AV

DD

to disable.

23

REFIO

Reference voltage input if internal reference is disabled and reference voltage output if internal reference is

enabled. Use 0.1

µ

F cap to ground when internal reference is enabled.

22

FSADJ

Full Scale Current Adjust. Use a resistor to ground to adjust full scale output current. Full Scale Output

Current Per Channel = 32 x I

FSADJ

.

14, 24

ICOMP1, QCOMP1

Reduces noise. Connect each to AV

DD

with 0.1

µ

F capacitor near each pin. The ICOMP1 and QCOMP1

pins MUST be tied together externally.

13, 18, 19, 25

AGND

Analog Ground Connections.

17

IOUTB

The complimentary current output of the I channel. Bits set to all 0s gives full scale current.

16

IOUTA

Current output of the I channel. Bits set to all 1s gives full scale current.

20

QOUTB

The complimentary current output of the Q channel. Bits set to all 0s gives full scale current.

21

QOUTA

Current output of the Q channel. Bits set to all 1s gives full scale current.

11, 27

NC

No Connect. Recommended: connect to ground.

12, 26

AV

DD

Analog Supply (+2.7V to +5.5V).

10, 28, 41, 44

DGND

Digital Ground.

9, 29, 40, 45

DV

DD

Supply voltage for digital circuitry (+2.7V to +5.5V).

43

ICLK

Clock input for I channel. Positive edge of clock latches data.

42

QCLK

Clock input for Q channel. Positive edge of clock latches data.

HI5728

5

Absolute Maximum Ratings

Thermal Information

Digital Supply Voltage DV

DD

to DCOM . . . . . . . . . . . . . . . . . +5.5V

Analog Supply Voltage AV

DD

to ACOM . . . . . . . . . . . . . . . . . +5.5V

Grounds, ACOM TO DCOM . . . . . . . . . . . . . . . . . . . -0.3V to +0.3V

Digital Input Voltages (D9-D0, CLK, SLEEP) . . . . . . . . . DV

DD

+0.3V

Internal Reference Output Current. . . . . . . . . . . . . . . . . . . . .

±

50

µ

A

Reference Input Voltage Range . . . . . . . . . . . . . . . . . . AV

DD

+0.3V

Analog Output Current (I

OUT

) . . . . . . . . . . . . . . . . . . . . . . . . . 24mA

Operating Conditions

Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . . . -40

o

C to 85

o

C

Thermal Resistance (Typical, Note 1)

JA

(

o

C/W)

TQFP Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

75

Maximum Power Dissipation

TQFP Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .930mW

Maximum Junction Temperature . . . . . . . . . . . . . . . . . . . . . . .150

o

C

Maximum Storage Temperature Range . . . . . . . . . . -65

o

C to 150

o

C

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . .300

o

C

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1.

JA

is measured with the component mounted on an evaluation PC board in free air.

Electrical Specifications

AV

DD

= DV

DD

=

+

5V, V

REF

= Internal 1.2V, IOUTFS = 20mA, T

A

= 25

o

C for All Typical Values. Data given is

per channel except for `Power Supply Characteristics.'

PARAMETER

TEST CONDITIONS

HI5728IN

T

A

= -40

o

C TO 85

o

C

UNITS

MIN

TYP

MAX

SYSTEM PERFORMANCE (Per Channel)

Resolution

10

-

-

Bits

Integral Linearity Error, INL

"Best Fit" Straight Line (Note 7)

-1

±

0.5

+1

LSB

Differential Linearity Error, DNL

(Note 7)

-0.5

±

0.25

+0.5

LSB

Offset Error, I

OS

(Note 7)

-0.025

+0.025

% FSR

Offset Drift Coefficient

(Note 7)

-

0.1

-

ppm

FSR/

o

C

Full Scale Gain Error, FSE

With External Reference (Notes 2, 7)

-10

±

2

+10

% FSR

With Internal Reference (Notes 2, 7)

-10

±

1

+10

% FSR

Full Scale Gain Drift

With External Reference (Note 7)

-

±

50

-

ppm

FSR/

o

C

With Internal Reference (Note 7)

-

±

100

-

ppm

FSR/

o

C

Gain Matching Between Channels

-0.5

0.1

0.5

dB

I/Q Channel Isolation

F

OUT

= 10MHz

-

80

-

dB

Output Voltage Compliance Range

(Note 3)

-0.3

-

1.25

V

Full Scale Output Current, I

FS

2

-

20

mA

DYNAMIC CHARACTERISTICS (Per Channel)

Maximum Clock Rate, f

CLK

(Note 3)

125

-

-

MHz

Output Settling Time, (t

SETT

)

0.1% (

±

1 LSB, equivalent to 9 Bits) (Note 7)

-

20

-

ns

0.05% (

±

1/2 LSB, equivalent to 10 Bits) (Note 7)

-

35

-

ns

Singlet Glitch Area (Peak Glitch)

R

L

= 25

(Note 7)

-

35

-

pV∑s

Output Rise Time

Full Scale Step

-

1.5

-

ns

Output Fall Time

Full Scale Step

-

1.5

-

ns

Output Capacitance

-

10

-

pF

Output Noise

IOUTFS = 20mA

-

50

-

pA/

Hz

IOUTFS = 2mA

-

30

-

pA/

Hz

HI5728