| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: HIP2100 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

|

Copyright

©

Intersil Corporation 1999

HIP2100

100V/2A Peak, Low Cost, High Frequency

Half Bridge Driver

The HIP2100 is a high frequency, 100V Half Bridge

N-Channel MOSFET driver IC, available in 8 lead plastic

SOIC. The low-side and high-side gate drivers are

independently controlled and matched to 8ns. This gives the

user maximum flexibility in dead-time selection and driver

protocol. Undervoltage protection on both the low-side and

high-side supplies force the outputs low. An on-chip diode

eliminates the discrete diode required with other driver ICs.

A new level-shifter topology yields the low-power benefits of

pulsed operation with the safety of DC operation. Unlike

some competitors, the high-side output returns to its correct

state after a momentary undervoltage of the high-side

supply.

Features

∑ Drives N-Channel MOSFET Half Bridge

∑ Space Saving SO8 Package

∑ Bootstrap Supply Max Voltage to 116VDC

∑ On-Chip 1

Bootstrap Diode

∑ Fast Propagation Times Needed for Multi-MHz Circuits

∑ Drives 1000pF Load at 1MHz with Rise and Fall Times of

Typically 10ns

∑ CMOS Input Thresholds for Improved Noise Immunity

∑ Independent Inputs for Non-Half Bridge Topologies

∑ No Start-Up Problems

∑ Outputs Unaffected by Supply Glitches, HS Ringing Below

Ground, or HS Slewing at High dv/dt

∑ Low Power Consumption

∑ Wide Supply Range

∑ Supply Undervoltage Protection

∑ 3

Output Resistance

Applications

∑ Telecom Half Bridge Power Supplies

∑ Avionic DC-DC Converters

∑ Two-Switch Forward Converters

∑ Active Clamp Forward Converters

Ordering Information

PART NUMBER

TEMP.

RANGE (

o

C)

PACKAGE

PKG. NO.

HIP2100IB

-40

o

C to 85

o

C

8 Ld SOIC (N)

M8.15

Pinout

HIP2100 (SOIC)

TOP VIEW

Application Block Diagram

5

6

8

7

4

3

2

1

V

DD

HB

HO

HS

LO

LI

HI

V

SS

SECONDARY

CIRCUIT

+100V

CONTR

OL

CONTROLLER

PWM

LI

HI

HO

LO

V

DD

HS

HB

+12V

V

SS

HIP2100

REFERENCE

AND

ISOLATION

DRIVE

LO

DRIVE

HI

Data Sheet

October 1998

File Number

4022.2

2

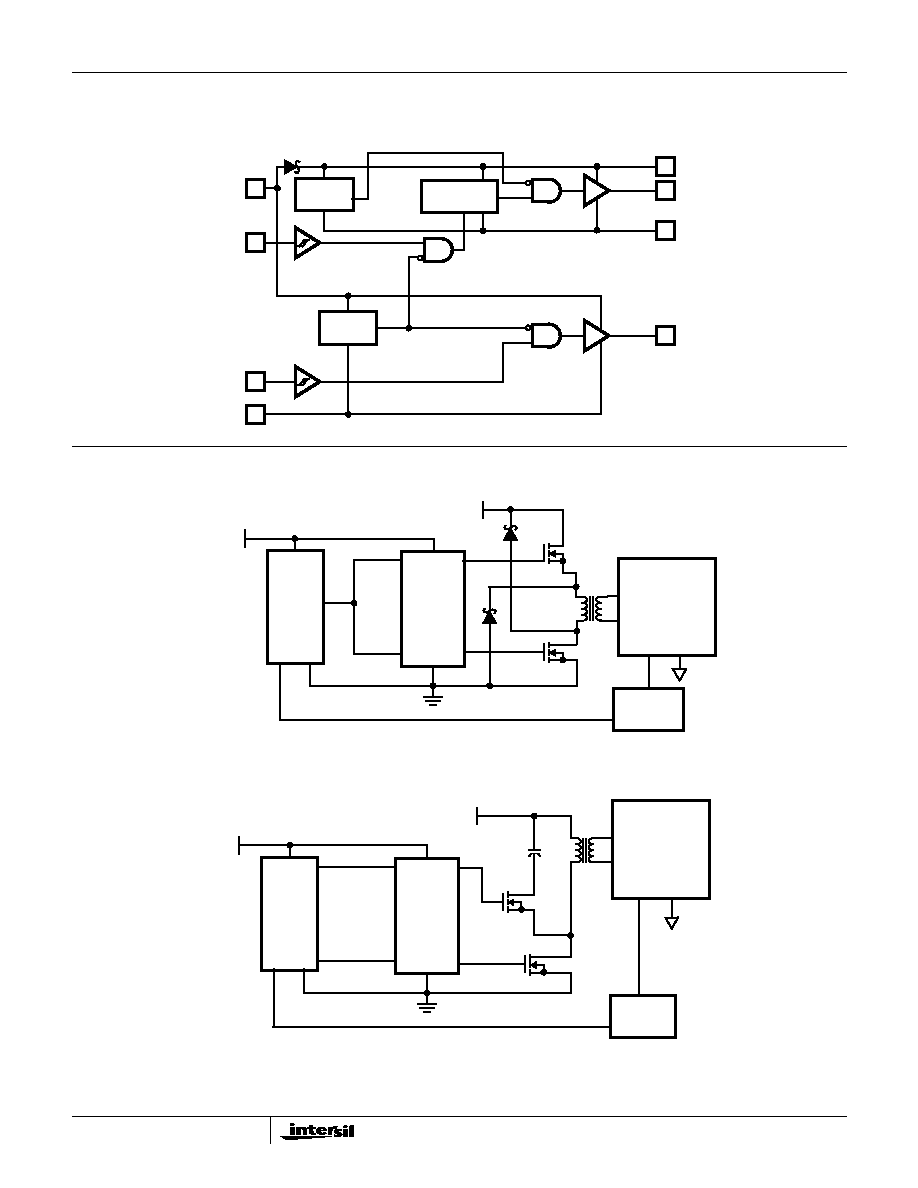

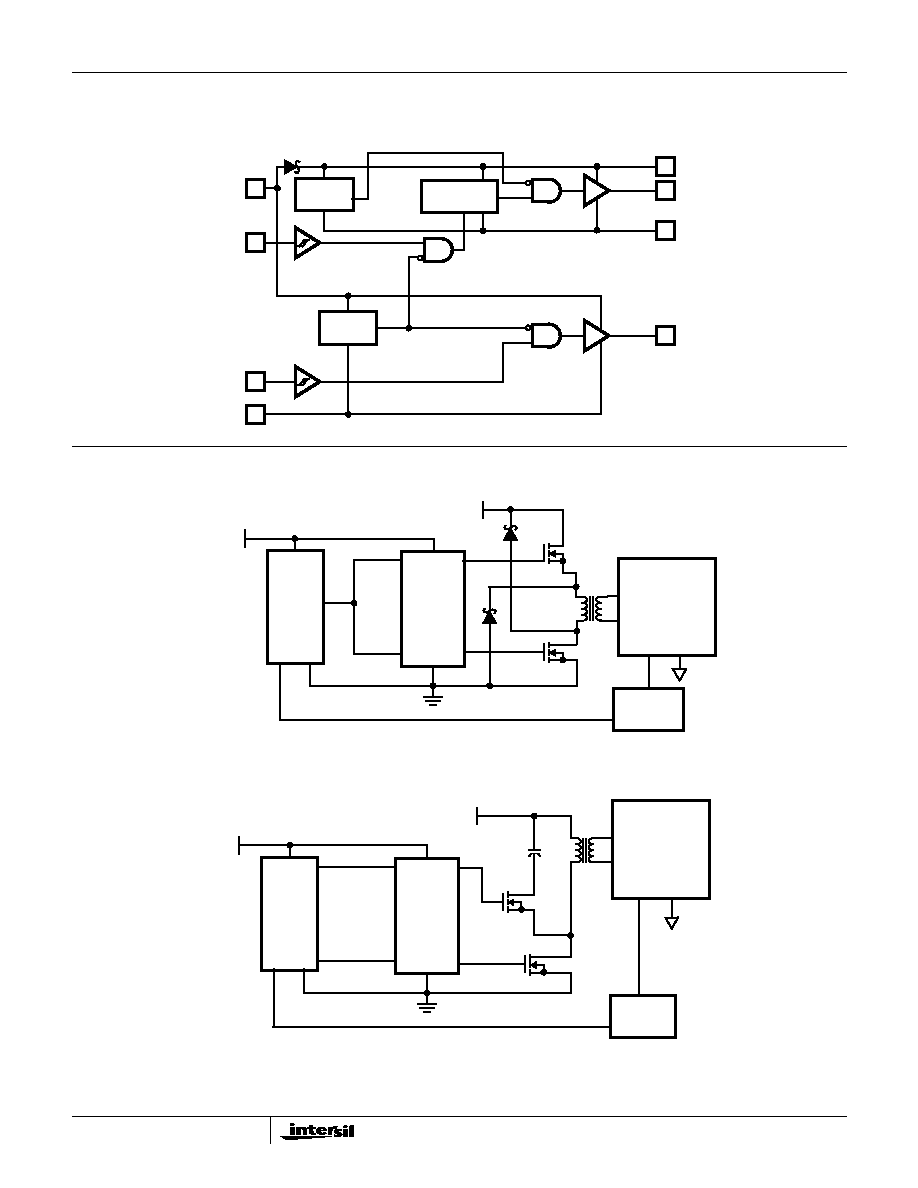

Functional Block Diagram

Other Applications

FIGURE 1. TWO-SWITCH FORWARD CONVERTER

FIGURE 2. FORWARD CONVERTER WITH AN ACTIVE CLAMP

UNDER

VOLTAGE

V

DD

HI

LI

V

SS

1

5

6

7

DRIVER

DRIVER

2

3

4

HB

HO

HS

8

LO

LEVEL SHIFT

UNDER

VOLTAGE

SECONDARY

HIP

2100

ISOLATION

PWM

+48V

+12V

CIRCUIT

SECONDARY

CIRCUIT

HIP

2100

ISOLATION

PWM

+48V

+12V

HIP2100

3

Absolute Maximum Ratings

Thermal Information

Supply Voltage, V

DD,

V

HB

-V

HS

. . . . . . . . . . . . . . . . . . -0.3V to 18V

LI and HI Voltages . . . . . . . . . . . . . . . . . . . . . . . . -3V to V

DD

+0.3V

Voltage on LO . . . . . . . . . . . . . . . . . . . . . . . . . . -0.3V to V

DD

+0.3V

Voltage on HO . . . . . . . . . . . . . . . . . . . . . . V

HS

-0.3V to V

HB

+0.3V

Voltage on HS (Continuous) . . . . . . . . . . . . . . . . . . . . . -1V to 110V

Voltage on HB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +118V

Average Current in V

DD

to HB diode . . . . . . . . . . . . . . . . . . . 100mA

ESD Classification . . . . . . . . . . . . . . . . . . . . . . . . . . . Class 1 (1kV)

NOTE: All Voltages Relative to Pin 7, V

SS

Unless Otherwise Specified

Thermal Resistance

JA

JC

SOIC . . . . . . . . . . . . . . . . . . . . . . . . . . . .

160

o

C/W

N/A

SOIC in Thermal Conductive Media. . . . . . . . . . . . . . . . . 70

o

C/W

HS Slew Rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10V/ns

Storage Temperature Range . . . . . . . . . . . . . . . . . . -65

o

C to 150

o

C

Junction Temperature Range. . . . . . . . . . . . . . . . . . -55

o

C to 150

o

C

Lead Temperature (Soldering 10s - Lead Tips Only) . . . . . . . 300

o

C

Maximum Power Dissipation at +25

o

C in Free Air. . . . . . . . 780mW

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the recommended operating conditions of this specification is not implied.

Recommended Operating Conditions

Supply Voltage, V

DD

. . . . . . . . . . . . . . . . . . . . . . . . . +9V to +16.5V

Voltage on HS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -1V to 100V

Voltage on HS . . . . . . . . . . . . . . . (Repetitive Transient) -5V to 105V

Voltage on HB V

HS

+8V to V

HS

+16.5V and V

DD

-1V to V

DD

+100V

Electrical Specifications

V

DD

= V

HB

= 12V, V

SS

= V

HS

= 0V, No Load on LO or HO, Unless Otherwise Specified

PARAMETERS

SYMBOL

TEST CONDITIONS

T

J

= 25

o

C

T

J

= - 40

o

C

TO 125

o

C

UNITS

MIN

TYP

MAX

MIN

MAX

SUPPLY CURRENTS

V

DD

Quiescent Current

I

DD

LI = HI = 0V

-

0.1

0.15

-

0.2

mA

V

DD

Operating Current

I

DDO

f = 500kHz

-

1.5

2.5

-

3

mA

Total HB Quiescent Current

I

HB

LI = HI = 0V

-

0.1

0.15

-

0.2

mA

Total HB Operating Current

I

HBO

f = 500kHz

-

1.5

2.5

-

3

mA

HB to V

SS

Current, Quiescent

I

HBS

V

HS

= V

HB

= 116.5V

-

0.05

1

-

10

µ

A

HB to V

SS

Current, Operating

I

HBSO

f = 500kHz

-

0.7

-

-

-

mA

INPUT PINS

Low Level Input Voltage Threshold

V

IL

4

5.4

-

3

-

V

High Level Input Voltage Threshold

V

IH

-

5.8

7

-

8

V

Input Voltage Hysteresis

V

IHYS

-

0.4

-

-

-

V

Input Pulldown Resistance

R

I

-

200

-

100

500

k

UNDER VOLTAGE PROTECTION

V

DD

Rising Threshold

V

DDR

7

7.3

7.8

6.5

8

V

V

DD

Threshold Hysteresis

V

DDH

-

0.5

-

-

-

V

HB Rising Threshold

V

HBR

6.5

6.9

7.5

6

8

V

HB Threshold Hysteresis

V

HBH

-

0.4

-

-

-

V

BOOT STRAP DIODE

Low-Current Forward Voltage

V

DL

I

VDD-HB

= 100

µ

A

-

0.45

0.55

-

0.7

V

High-Current Forward Voltage

V

DH

I

VDD-HB

= 100mA

-

0.7

0.8

-

1

V

Dynamic Resistance

R

D

I

VDD-HB

= 100mA

-

0.8

1

-

1.5

LO GATE DRIVER

Low Level Output Voltage

V

OLL

I

LO

= 100mA

-

0.25

0.3

-

0.4

V

High Level Output Voltage

V

OHL

I

LO

= -100mA, V

OHL

= V

DD

-V

LO

-

0.25

0.3

-

0.4

V

Peak Pullup Current

I

OHL

V

LO

= 0V

-

2

-

-

-

A

Peak Pulldown Current

I

OLL

V

LO

= 12V

-

2

-

-

-

A

HO GATE DRIVER

Low Level Output Voltage

V

OLH

I

HO

= 100mA

-

0.25

0.3

-

0.4

V

High Level Output Voltage

V

OHH

I

HO

= -100mA, V

OHH

= V

HB

-V

HO

-

0.25

0.3

-

0.4

V

Peak Pullup Current

I

OHH

V

HO

= 0V

-

2

-

-

-

A

Peak Pulldown Current

I

OLH

V

HO

= 12V

-

2

-

-

-

A

HIP2100

4

Pin Descriptions

Timing Diagrams

Switching Specifications

V

DD

= V

HB

= 12V, V

SS

= V

HS

= 0V, No Load on LO or HO, Unless Otherwise Specified

PARAMETERS

SYMBOL

TEST

CONDITIONS

T

J

= 25

o

C

T

J

= - 40

o

C

TO 125

o

C

UNITS

MIN

TYP

MAX

MIN

MAX

Lower Turn-Off Propagation Delay (LI Falling to LO Falling)

t

LPHL

-

20

35

-

45

ns

Upper Turn-Off Propagation Delay (HI Falling to HO Falling)

t

HPHL

-

20

35

-

45

ns

Lower Turn-On Propagation Delay (LI Rising to LO Rising)

t

LPLH

-

20

35

-

45

ns

Upper Turn-On Propagation Delay (HI Rising to HO Rising)

t

HPLH

-

20

35

-

45

ns

Delay Matching: Lower Turn-On and Upper Turn-Off

t

MON

-

2

8

-

10

ns

Delay Matching: Lower Turn-Off and Upper Turn-On

t

MOFF

-

2

8

-

10

ns

Either Output Rise/Fall Time

t

RC,

t

FC

C

L

= 1000pF

-

10

-

-

-

ns

Either Output Rise/Fall Time (3V to 9V)

t

R,

t

F

C

L

= 0.1

µ

F

-

0.5

0.6

-

0.8

us

Either Output Rise Time Driving DMOS

t

RD

C

L

= IRFR120

-

20

-

-

-

ns

Either Output Fall Time Driving DMOS

t

FD

C

L

= IRFR120

-

10

-

-

-

ns

Minimum Input Pulse Width that Changes the Output

t

PW

-

-

-

-

50

ns

Bootstrap Diode Turn-On or Turn-Off Time

t

BS

-

10

-

-

-

ns

PIN

NUMBER

SYMBOL

DESCRIPTION

1

V

DD

Positive Supply to lower gate drivers. De-couple this pin to V

SS

(Pin 7). Bootstrap diode connected to HB (pin 2).

2

HB

High-Side Bootstrap supply. External bootstrap capacitor is required. Connect positive side of bootstrap capacitor to

this pin. Bootstrap diode is on-chip.

3

HO

High-Side Output. Connect to gate of High-Side power MOSFET.

4

HS

High-Side Source connection. Connect to source of High-Side power MOSFET. Connect negative side of bootstrap

capacitor to this pin.

5

HI

High-Side input.

6

LI

Low-Side input.

7

V

SS

Chip negative supply, generally will be ground.

8

LO

Low-Side Output. Connect to gate of Low-Side power MOSFET.

FIGURE 3.

FIGURE 4.

t

HPLH

,

t

LPLH

t

HPHL

,

t

LPHL

HI,

LI

HO,

LO

t

MON

t

MOFF

LI

HI

LO

HO

HIP2100

5

Typical Performance Curves

FIGURE 5. OPERATING CURRENT vs FREQUENCY

FIGURE 6. LEVEL SHIFTER CURRENT vs FREQUENCY

FIGURE 7. HIGH LEVEL OUTPUT VOLTAGE vs TEMPERATURE

FIGURE 8. LOW LEVEL OUTPUT VOLTAGE vs TEMPERATURE

FIGURE 9. UNDERVOLTAGE LOCKOUT THRESHOLD vs

TEMPERATURE

FIGURE 10. UNDERVOLTAGE LOCKOUT HYSTERESIS vs

TEMPERATURE

T = 125

o

C

T = 25

o

C

T = -40

o

C

T = 150

o

C

10

100

1000

10

1

0.1

0.01

FREQUENCY (kHz)

I

DDO

, I

HBO

(mA)

T = -40

o

C

T = 125

o

C

T = 25

o

C

T = 150

o

C

10

1

0.1

0.01

I

HBSO

(mA)

10

100

1000

FREQUENCY (kHz)

TEMPERATURE (

o

C)

V

OHL

, V

OHH

(mV)

500

400

300

200

100

-50

0

50

100

150

V

HB

= V

DD

= 9V

V

HB

= V

DD

= 12V

V

HB

= V

DD

= 14V

V

HB

= V

DD

= 16.5V

TEMPERATURE (

o

C)

V

OLL

, V

OLH

(mV)

500

400

300

200

100

-50

0

50

100

150

V

HB

= V

DD

= 9V

V

HB

= V

DD

= 12V

V

HB

= V

DD

= 14V

V

HB

= V

DD

= 16.5V

TEMPERATURE (

o

C)

-50

0

50

100

150

7.6

7.4

7.2

7.0

6.8

6.6

V

DDR

V

HBR

V

HBR

, V

DDR

(mV)

TEMPERATURE (

o

C)

-50

0

50

100

150

0.54

0.5

0.46

0.42

0.38

0.3

V

DDH

V

HBH

V

HBH

, V

DDH

(mV)

0.34

HIP2100

6

FIGURE 11. PROPAGATION DELAYS vs TEMPERATURE

FIGURE 12. PULLUP CURRENT vs OUTPUT VOLTAGE

FIGURE 13. PULLDOWN CURRENT vs OUTPUT VOLTAGE

FIGURE 14. BOOTSTRAP DIODE I-V CHARACTERISTICS

FIGURE 15. BIAS CURRENT vs VOLTAGE

Typical Performance Curves

(Continued)

t

HPHL

t

HPLH

t

LPHL

t

LPLH

TEMPERATURE (

o

C)

-50

0

50

100

150

30

25

20

15

t

LPLH

, t

LPHL

, t

HPLH

, t

HPHL

(ns)

6

2.0

I

HO

, I

LO

(A)

12

10

8

4

2

0

2.5

1.5

1.0

0.5

0

V

HO

, V

LO

(V)

6

2.0

I

LO

, I

HO

(A)

12

10

8

4

2

0

2.5

1.5

1.0

0.5

0

V

LO

, V

HO

(V)

0.8

1

0.1

0.01

0.001

1

∑

10

-4

1

∑

10

-5

1

∑

10

-6

0.7

0.6

0.5

0.4

0.3

FORWARD VOLTAGE (V)

FOR

W

ARD CURRENT (A)

V

DD

, V

HB

(V)

0

5

10

15

60

50

40

0

I

DD

, I

HB

(

µ

A)

30

20

10

I

DD

vs V

DD

I

HB

vs V

HB

HIP2100

7

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time with-

out notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and

reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result

from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com

Sales Office Headquarters

NORTH AMERICA

Intersil Corporation

P. O. Box 883, Mail Stop 53-204

Melbourne, FL 32902

TEL: (407) 724-7000

FAX: (407) 724-7240

EUROPE

Intersil SA

Mercure Center

100, Rue de la Fusee

1130 Brussels, Belgium

TEL: (32) 2.724.2111

FAX: (32) 2.724.22.05

ASIA

Intersil (Taiwan) Ltd.

7F-6, No. 101 Fu Hsing North Road

Taipei, Taiwan

Republic of China

TEL: (886) 2 2716 9310

FAX: (886) 2 2715 3029

HIP2100