Integrated Silicon Solution, Inc.

2231 Lawson Lane ∑ Santa Clara, CA. 95054-3311 ∑ Tel: (408) 588-0800 ∑ Fax: (408) 588-0806

E-mail: sales@issi.com ∑ www.issi.com

IS51

IS51

IS51

IS51

IS51V

V

V

V

V V4064

V4064

V4064

V4064

V4064

PP

PPParallel Sear

arallel Sear

arallel Sear

arallel Sear

arallel Search P

ch P

ch P

ch P

ch Processor P

rocessor P

rocessor P

rocessor P

rocessor Product Brief

roduct Brief

roduct Brief

roduct Brief

roduct Brief

APRIL 2002

DESCRIPTION

The IS51V V4064 Parallel Search Processor is the most flexible and

highest-performing CAM-based (Content Addressable Memory) search

processor on the market today.

The patent-pending architecture of IS51V V4064 features multiple

CAMtiles

TM

, which can be flexibly configured to accommodate databases of

any width and depth efficiently. In addition, the IS51V V4064 contains an

instruction table, which stores user-programmable instructions that can be

changed dynamically when needed.

The IS51V V4064 is the only CAM-based search processor capable of

performing four simultaneous table lookups per cycle and achieving a

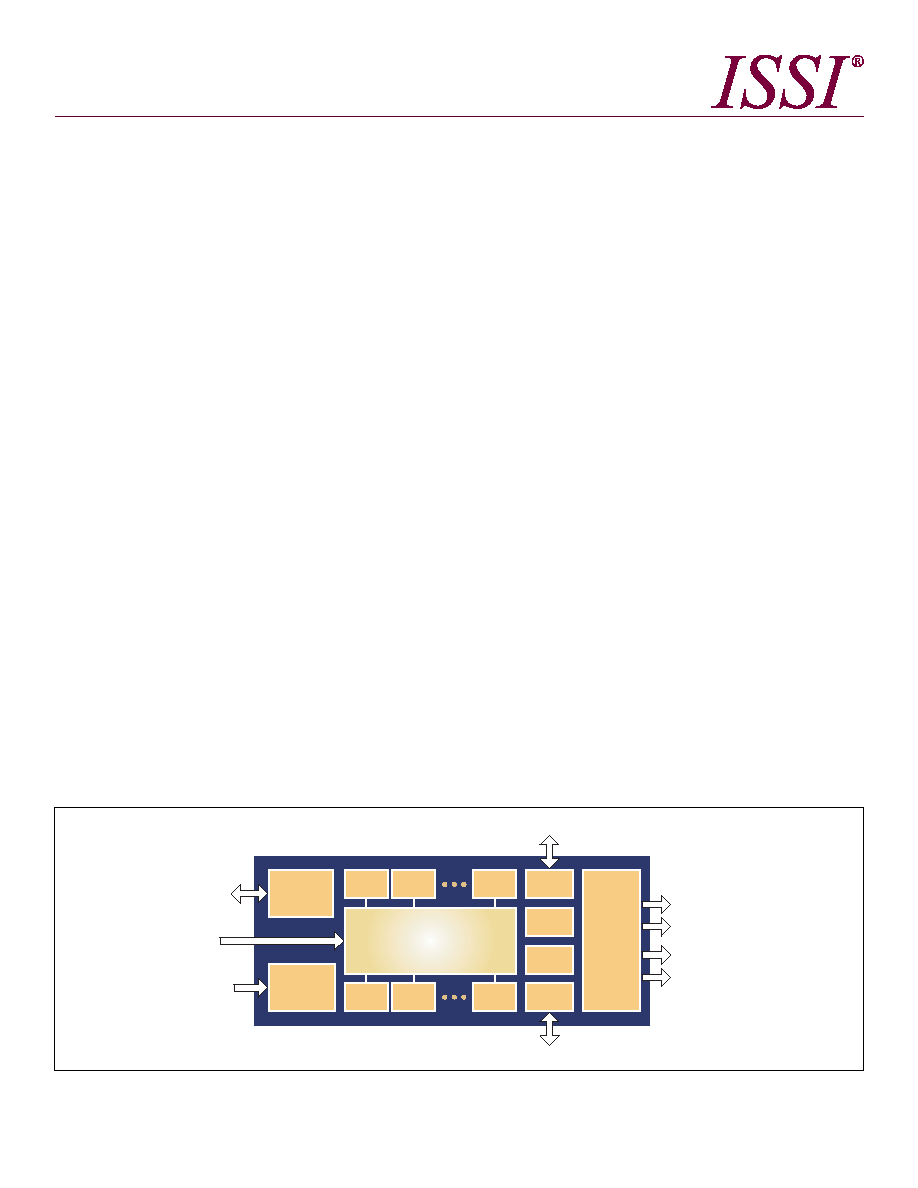

BLOCK DIAGRAM

C

C

A

A

M

M

T

T

ile

ile

0

0

A

A

g

g

in

in

g

g

U

U

n

n

it

it

CAMBI

CAMBI

S

S

T

T

C

C

h

h

i

i

p

p

C

C

a

a

s

s

c

c

a

a

de I

de I

n

n

t

t

e

e

r

r

f

f

a

a

c

c

e (

e (

C

C

C

C

I

I

)

)

JT

JT

A

A

G

G

C

C

A

A

M

M

T

T

ile

ile

32

32

Re

Re

s

s

u

u

l

l

t

t

P

P

r

r

oc

oc

e

e

s

s

s

s

i

i

ng

ng

an

an

d

d

Ad

Ad

d

d

r

r

e

e

s

s

s

s

Re

Re

l

l

o

o

ca

ca

t

t

i

i

o

o

n

n

Un

Un

i

i

t

t

C

C

A

A

M

M

T

T

ile

ile

33

33

C

C

A

A

M

M

T

T

ile

ile

63

63

C

C

A

A

M

M

T

T

ile

ile

1

1

C

C

A

A

M

M

T

T

ile

ile

31

31

P

P

r

r

ogr

ogr

am

am

m

ma

bl

bl

e

e

I

I

n

n

st

st

r

r

u

u

ct

ct

i

i

o

o

n

n

Tab

Tab

l

l

e

e

C

C

onf

onf

i

i

gur

gur

at

at

i

i

o

o

n

n

I/F

I/F

C

C

a

a

s

s

c

c

ade

ade

Un

Un

i

i

t

t

J

J

T

T

A

A

G

G

In

In

te

te

r

r

f

f

a

a

c

c

e

e

Configuration

I/F (CIF)

SearchData

Interface (SDI)

Search Instruction

Interface (SII)

Configuration

I/F (CIF)

SearchData

Interface (SDI)

Search Instruction

Interface (SII)

Simultaneous Search

Result Buses

Simultaneous Search

Result Buses

IS51VV4064

IS51VV4064

Sear

arch D

Data S

ta Selection F

n Fabr

abric (

(SDSF)

maximum of 533 million lookups per second at 133MHz. To maintain this

high throughput, the IS51V V4064 provides a separate configuration bus,

which allows database updates without suspending normal search

operations.

The IS51V V4064 enables networking equipment to satisfy present and

future network bandwidth requirements by alleviating the common

bottlenecks found in present network systems. It is a general-purpose

parallel search processor targeting multi-Gigabit/Terabit, OC768, OC192

core and edge routers, multi-layer enterprise switches, advanced server

load balancing switches, advanced content switches, and next generation

SAN (storage area network) switches.

FEATURES

∑ Flexible and configurable BTCAM

TM

technology.

∑ 64 blocks of CAM (CAMTiles

TM

); each configurable as either 1Kx64

binary CAM or 1Kx32 ternary CAM.

∑ Maximum 4Mbits (binary) or 2Mbits (ternary) per chip

∑ Both width and depth of up to 16 databases are individually

configurable.

∑ Four independent searches per cycle; up to 533 million searches per

second with 133MHz clock.

∑ Flexible search key sizes: 32, 64, 96, 128, 192, up to 2K/1K-bit for

binary/ternary operations.

∑ Flexible search key distribution via SDSF (search data selection fabric);

programmable distribution of non-contiguous search data to multiple

databases.

∑ 128-bit double-sample rate (256-bit effective) search data input port

(34Gbps @ 133MHz).

∑ 7-bit search instruction input port, supporting 64 user-programmable

search instructions (up to four search operations per search instruction).

∑ Support for "search-miss auto-learn" operation.

∑ Four 25-bit search result output ports.

∑ 16 independent programmable relocation circuits for flexible match

address output generation.

∑ Standard 32-bit configuration port for status and data updates.

∑ Simultaneous search and data/status updates.

∑ 3 aging bits per entry. Aging bits auto-refresh when entry matches. 16

independent configurable aging timers

∑ Static entry support.

∑ Invalid entry and "invalid entry search" operation support.

∑ Two chip-cascading methodologies, one of which allows an unlimited

number of chips to support large databases.

∑ User-accessible CAMBIST (CAMTile

TM

Built-In Self-Test).

∑ Parity checking on CAM cells to identify soft errors.

∑ IEEE 1149.1 JTAG test access port.

∑ High performance-to-power ratio.

∑ 480-ball BGA package.

∑ 0.18 micron CMOS process, 1.8V core, 2.5V/3.3V I/O.

Another Advanced Memory Solution from ISSI