| ÐлекÑÑоннÑй компоненÑ: LTC1749 | СкаÑаÑÑ:  PDF PDF  ZIP ZIP |

1749f.pm6

1

LTC1749

1749f

12-Bit, 80Msps

Wide Bandwidth ADC

s

Sample Rate: 80Msps

s

PGA Front End (2.25V

P-P

or 1.35V

P-P

Input Range)

s

71.8dB SNR and 87dB SFDR (PGA = 0)

s

70.2dB SNR and 87dB SFDR (PGA = 1)

s

500MHz Full Power Bandwidth S/H

s

No Missing Codes

s

Single 5V Supply

s

Power Dissipation: 1.45W

s

Two Pin Selectable Reference Values

s

Data Ready Output Clock

s

Pin Compatible 14-Bit 80Msps Device (LTC1750)

s

48-Pin TSSOP Package

s

Direct IF Sampling

s

Telecommunications

s

Receivers

s

Cellular Base Stations

s

Spectrum Analysis

s

Communications Test Equipment

s

Undersampling

, LTC and LT are registered trademarks of Linear Technology Corporation.

The LTC

®

1749 is an 80Msps, 12-bit A/D converter de-

signed for digitizing wide dynamic range signals up to

frequencies of 500MHz. The input range of the ADC can be

optimized with the on-chip PGA sample-and-hold circuit

and flexible reference circuitry.

The LTC1749 has a highly linear sample-and-hold circuit

with a bandwidth of 500MHz. The SFDR is 80dB with an

input frequency of 250MHz. Ultralow jitter of 0.15ps

RMS

allows undersampling of IF frequencies with minimal

degradation in SNR. DC specs include

±

1LSB INL and no

missing codes.

The digital interface is compatible with 5V, 3V, 2V and

LVDS logic systems. The ENC and ENC inputs may be

driven differentially from PECL, GTL and other low swing

logic families or from single-ended TTL or CMOS. The low

noise, high gain ENC and ENC inputs may also be driven

by a sinusoidal signal without degrading performance. A

separate output power supply can be operated from 0.5V

to 5V, making it easy to connect directly to low voltage

DSPs or FIFOs.

The 48-pin TSSOP package with a flow-through pinout

simplifies the board layout.

80Msps, 12-Bit ADC with a 2.25V Differential Input Range

DESCRIPTIO

U

FEATURES

APPLICATIO S

U

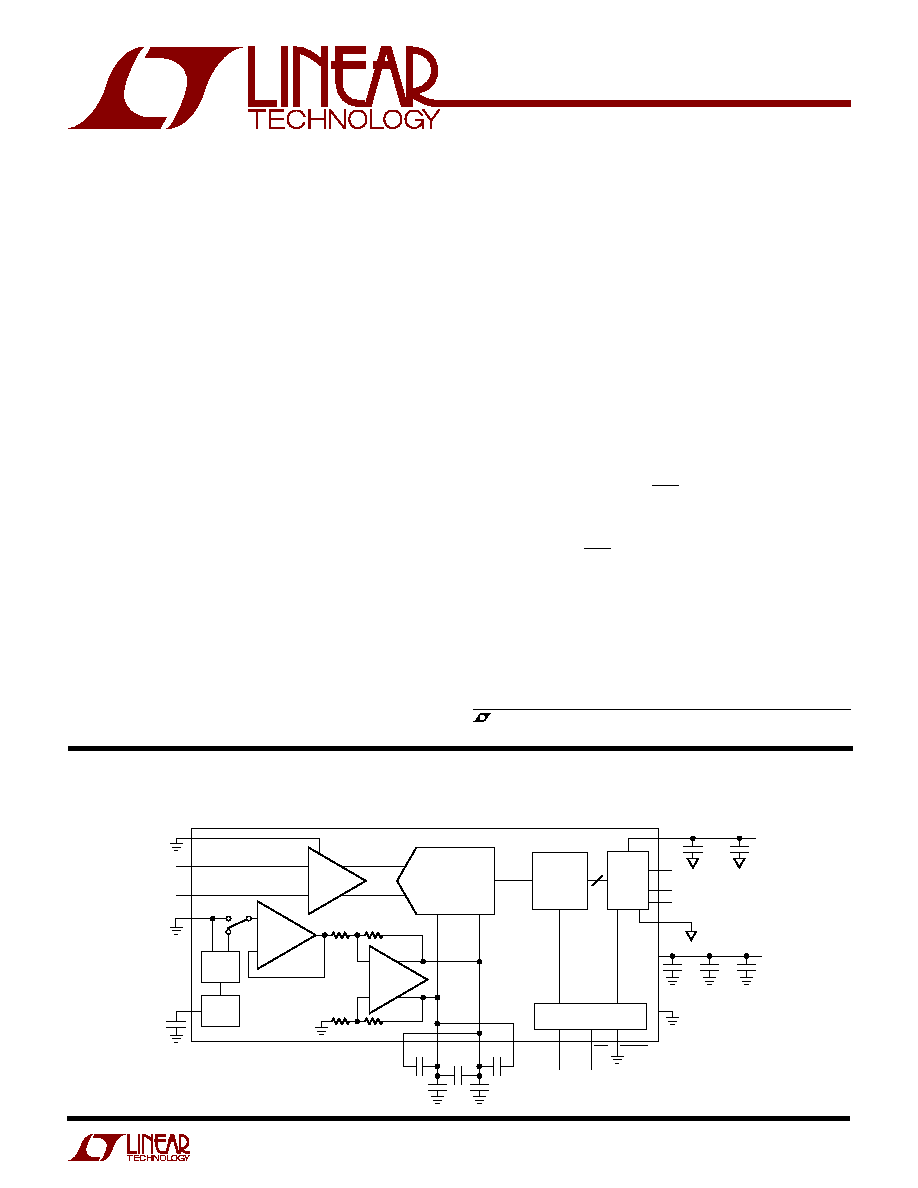

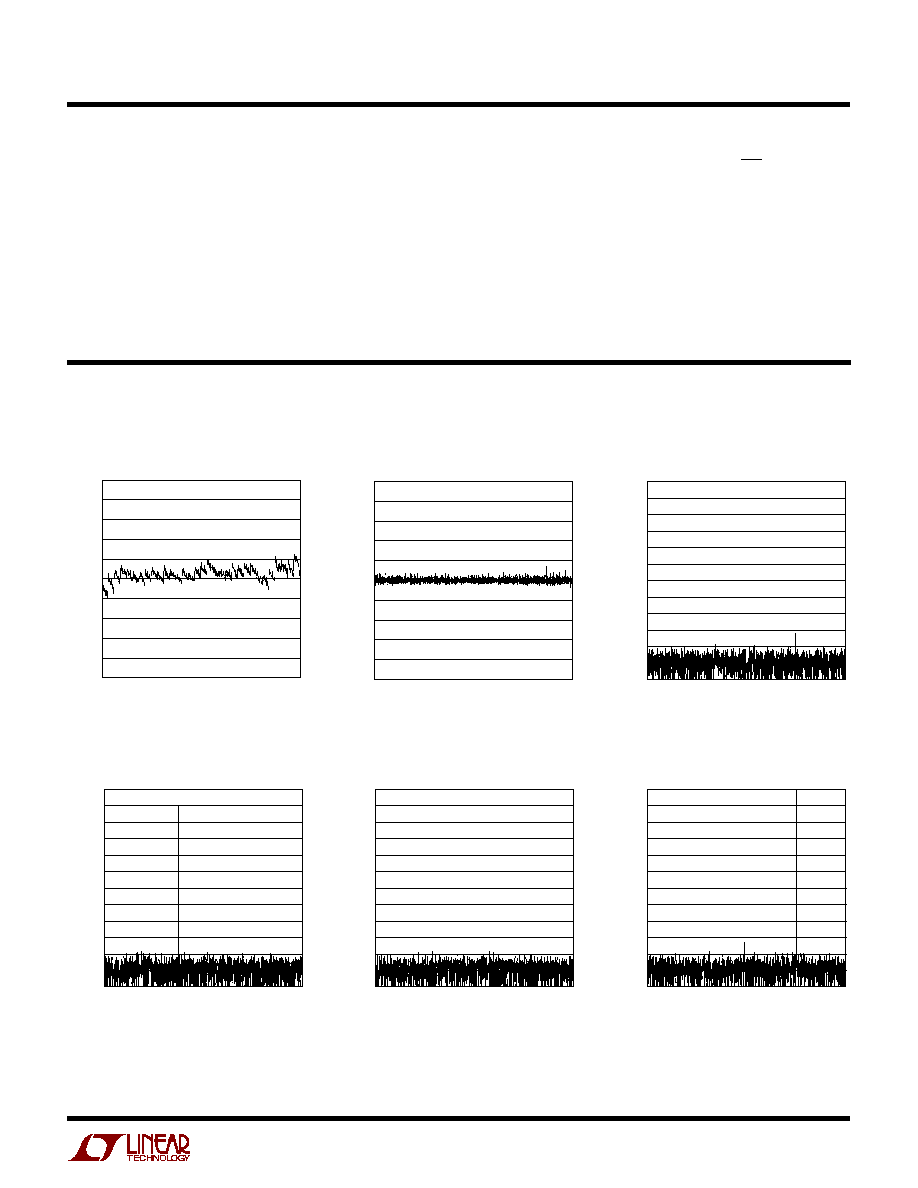

BLOCK DIAGRA

W

12-BIT

PIPELINED ADC

12

S/H

CIRCUIT

±

1.125V

DIFFERENTIAL

ANALOG INPUT

A

IN

+

PGA

A

IN

SENSE

V

CM

4.7

µ

F

DIFF AMP

REFLA

REFHB

GND

1749 BD

ENC

4.7

µ

F

1

µ

F

1

µ

F

0.1

µ

F

0.1

µ

F

REFHA

REFLB

BUFFER

RANGE

SELECT

2V

REF

CORRECTION

LOGIC AND

SHIFT

REGISTER

OUTPUT

LATCHES

CONTROL LOGIC

OV

DD

V

DD

OGND

0.5V TO 5V

5V

0.1

µ

F

1

µ

F

1

µ

F

1

µ

F

D11

D0

CLKOUT

·

·

·

ENC

DIFFERENTIAL

ENCODE INPUT

MSBINV

0.1

µ

F

2

LTC1749

1749f

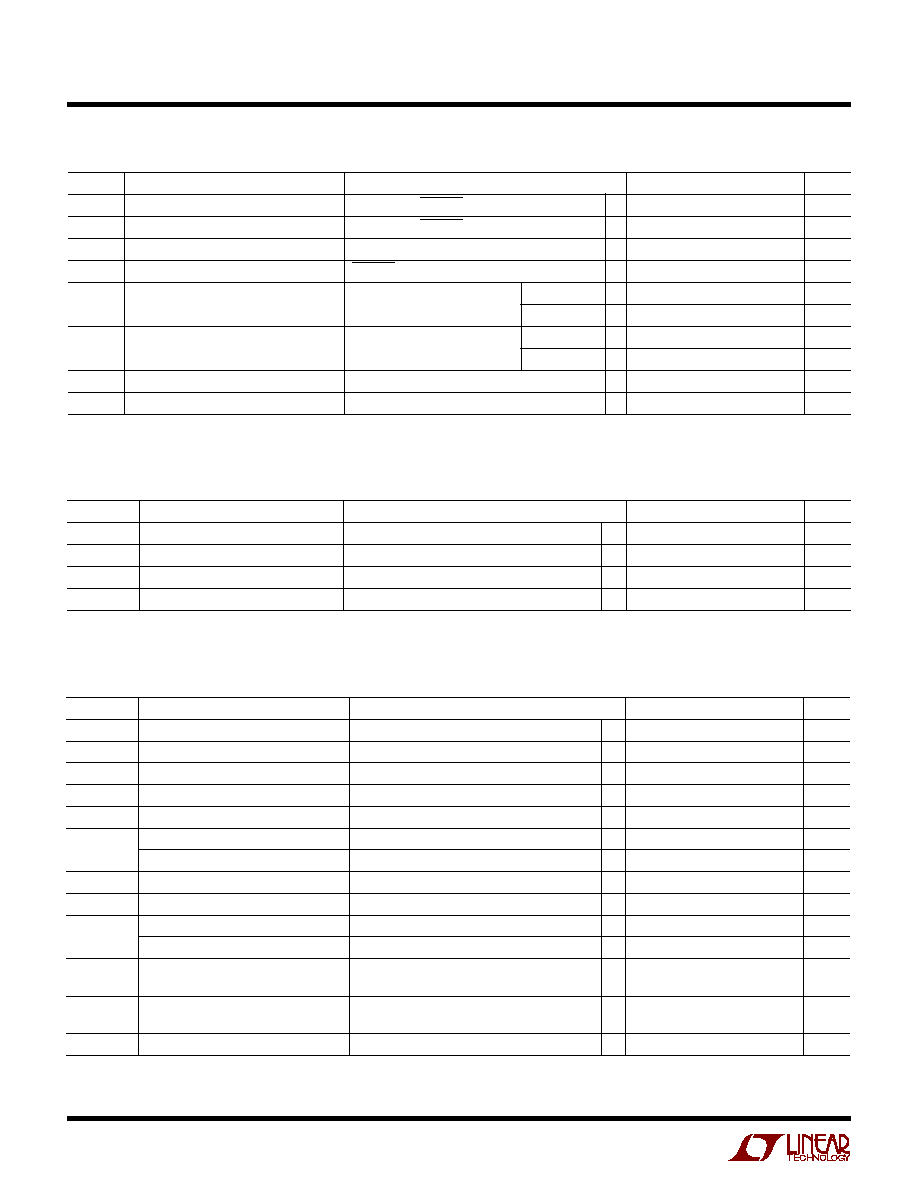

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

Resolution (No Missing Codes)

q

12

Bits

Integral Linearity Error

(Note 6)

1.0

±

0.4

1.0

LSB

q

1.5

1.5

LSB

Differential Linearity Error

q

0.8

±

0.2

0.8

LSB

Offset Error

(Note 7) External Reference (V

SENSE

= 1.125V, PGA = 0)

35

±

8

35

mV

Gain Error

External Reference (V

SENSE

= 1.125V, PGA = 0)

3.5

±

1

3.5

%FS

Full-Scale Tempco

Internal Reference

±

40

ppm/

°

C

External Reference (V

SENSE

= 1.125V)

±

20

ppm/

°

C

Offset Tempco

±

20

µ

V/

°

C

Input Referred Noise (Transition Noise)

V

SENSE

= 1.125V, PGA = 0

0.23

LSB

RMS

ORDER PART

NUMBER

OV

DD

= V

DD

(Notes 1, 2)

Supply Voltage (V

DD

) ............................................. 5.5V

Analog Input Voltage (Note 3) .... 0.3V to (V

DD

+ 0.3V)

Digital Input Voltage (Note 4) ..... 0.3V to (V

DD

+ 0.3V)

Digital Output Voltage ................. 0.3V to (V

DD

+ 0.3V)

OGND Voltage .............................................. 0.3V to 1V

Power Dissipation ............................................ 2000mW

Operating Temperature Range

LTC1749C ............................................... 0

°

C to 70

°

C

LTC1749I ............................................ 40

°

C to 85

°

C

Storage Temperature Range ................. 65

°

C to 150

°

C

Lead Temperature (Soldering, 10 sec).................. 300

°

C

LTC1749CFW

LTC1749IFW

T

JMAX

= 150

°

C,

JA

= 35

°

C/W

The

q

indicates specifications which apply over the full operating

temperature range, otherwise specifications are at T

A

= 25

°

C. (Note 5)

ABSOLUTE

M

AXI

M

U

M

RATINGS

W

W

W

U

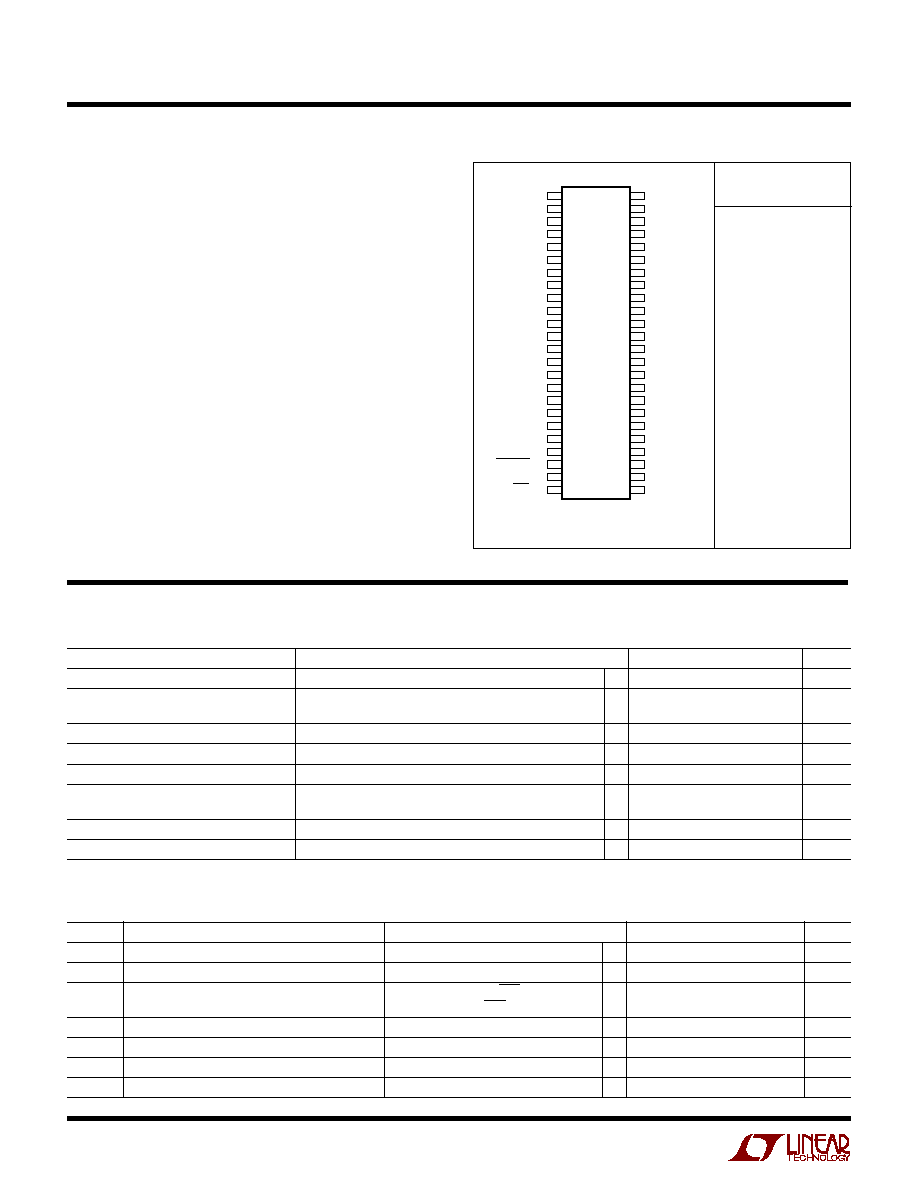

PACKAGE/ORDER I

N

FOR

M

ATIO

N

W

U

U

CO VERTER CHARACTERISTICS

U

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

V

IN

Analog Input Range (Note 8)

4.75V

V

DD

5.25V

q

±

0.7 to

±

1.125

V

I

IN

Analog Input Leakage Current

0 < A

IN

+

, A

IN

< V

DD

q

1

1

µ

A

C

IN

Analog Input Capacitance

Sample Mode ENC < ENC

6.9

pF

Hold Mode ENC > ENC

2.4

pF

t

ACQ

Sample-and-Hold Acquisition Time

q

5

6

ns

t

AP

Sample-and-Hold Acquisition Delay Time

0

ns

t

JITTER

Sample-and-Hold Acquisition Delay Time Jitter

0.15

ps

RMS

CMRR

Analog Input Common Mode Rejection Ratio

1.5V < (A

IN

= A

IN

+

) < 3V

80

dB

The

q

indicates specifications which apply over the full operating temperature range, otherwise

specifications are at T

A

= 25

°

C. (Note 5)

A ALOG I PUT

U

U

Consult LTC Marketing for parts specified with wider operating temperature ranges.

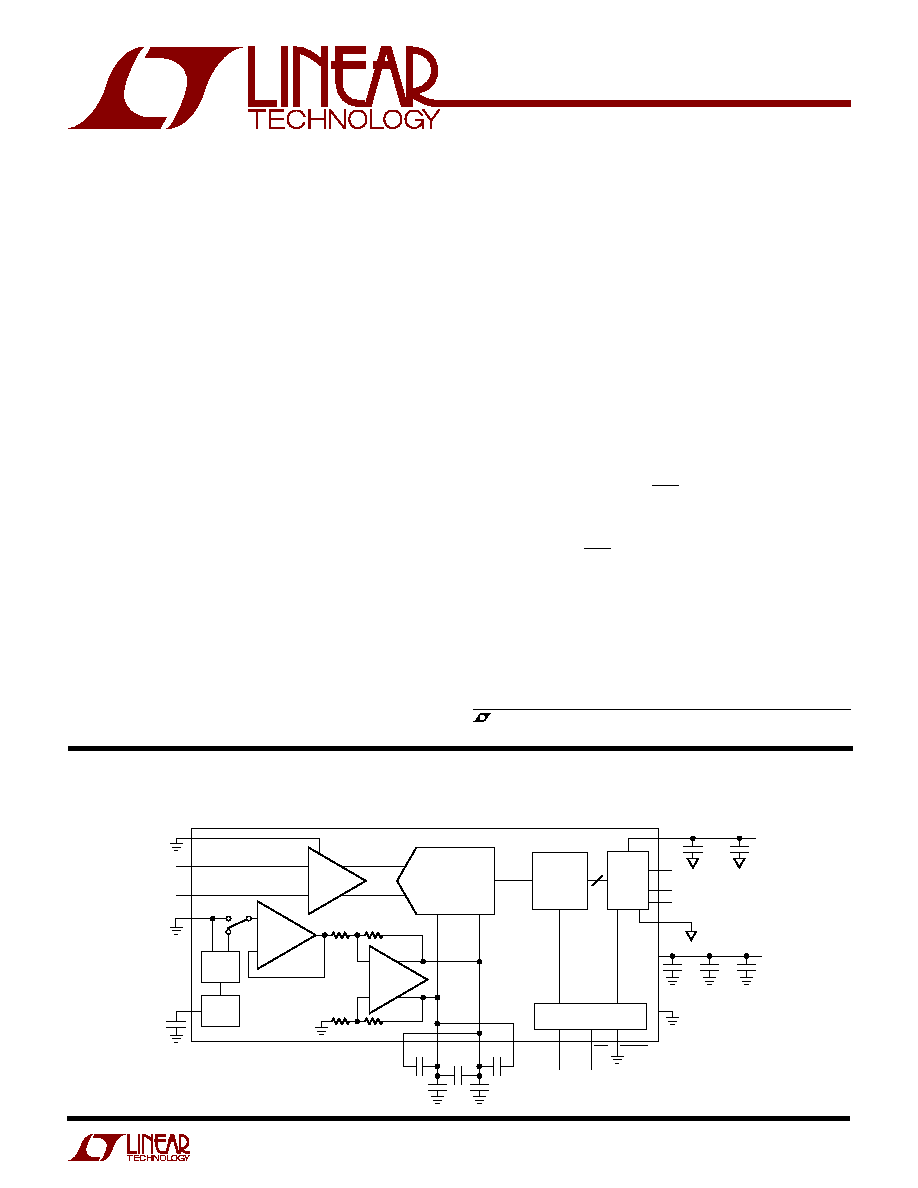

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

TOP VIEW

FW PACKAGE

48-LEAD PLASTIC TSSOP

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

SENSE

V

CM

GND

A

IN

+

A

IN

GND

V

DD

V

DD

GND

REFLB

REFHA

GND

GND

REFLA

REFHB

GND

V

DD

V

DD

GND

V

DD

GND

MSBINV

ENC

ENC

OF

OGND

D11

D10

D9

OV

DD

D8

D7

D6

D5

OGND

GND

GND

D4

D3

D2

OV

DD

D1

D0

NC

NC

OGND

CLKOUT

PGA

3

LTC1749

1749f

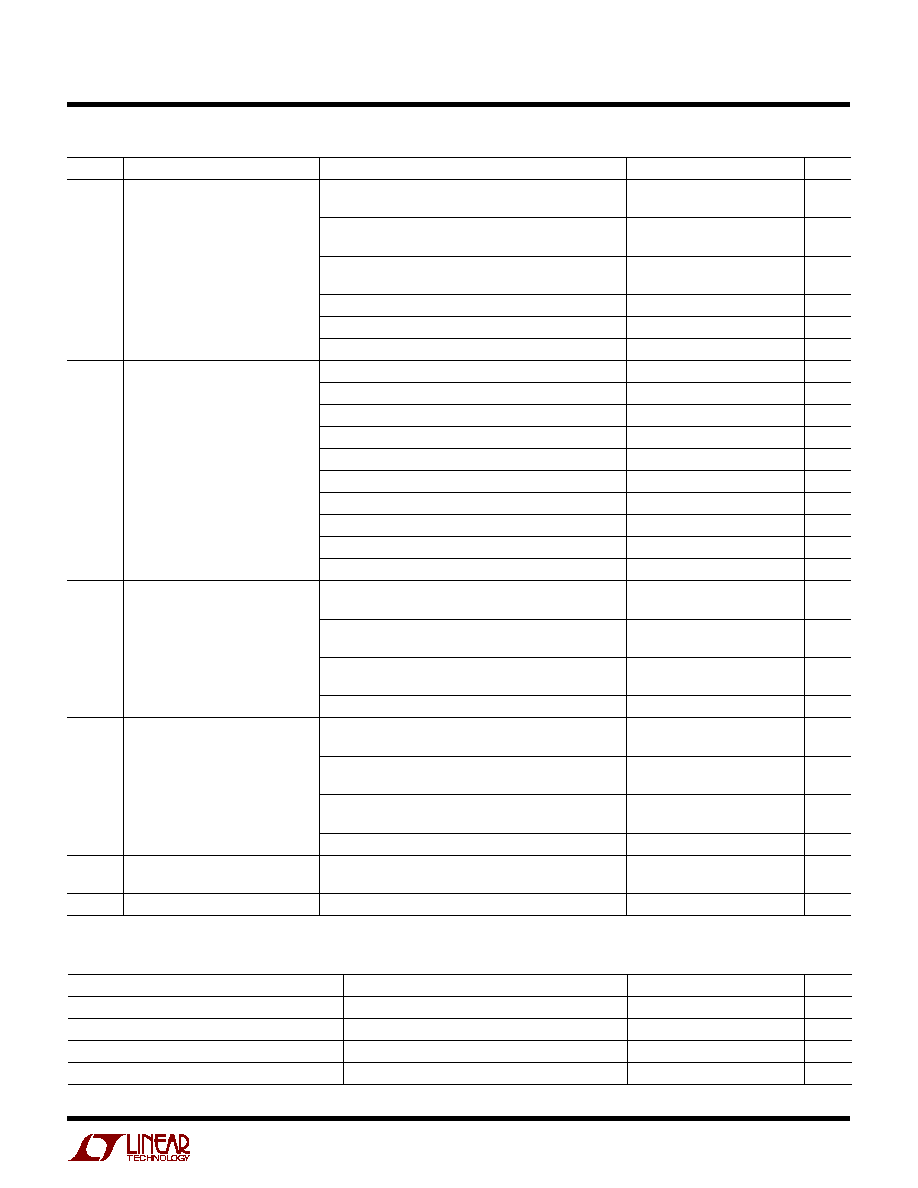

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

V

CM

Output Voltage

I

OUT

= 0

1.95

2

2.05

V

V

CM

Output Tempco

I

OUT

= 0

±

30

ppm/

°

C

V

CM

Line Regulation

4.75V

V

DD

5.25V

3

mV/V

V

CM

Output Resistance

1mA

I

OUT

1mA

4

(Note 5)

I TER AL REFERE CE CHARACTERISTICS

U

U

U

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

SNR

Signal-to-Noise Ratio

5MHz Input Signal (PGA = 0)

71.8

dB

5MHz Input Signal (PGA = 1)

70.2

dB

30MHz Input Signal (PGA = 0)

70.5

71.7

dB

30MHz Input Signal (PGA = 1)

70.2

dB

70MHz Input Signal (PGA = 0)

71.4

dB

70MHz Input Signal (PGA = 1)

68.8

70.1

dB

140MHz Input Signal (PGA = 1)

69.8

dB

250MHz Input Signal (PGA = 1)

69.3

dB

350MHz Input Signal (PGA = 1)

67.4

dB

SFDR

Spurious Free Dynamic Range

5MHz Input Signal (PGA = 0)

87

dB

5MHz Input Signal (PGA = 1)

87

dB

30MHz Input Signal (PGA = 0) (HD2 and HD3)

76

87

dB

30MHz Input Signal (PGA = 0) (Other)

83

90

dB

70MHz Input Signal (PGA = 0)

85

dB

70MHz Input Signal (PGA = 1) (HD2 and HD3)

76

87

dB

70MHz Input Signal (PGA = 1) (Other)

83

90

dB

140MHz Input Signal (PGA = 1)

84

dB

250MHz Input Signal (PGA = 1)

80

dB

350MHz Input Signal (PGA = 1)

74

dB

S/(N + D)

Signal-to-(Noise + Distortion) Ratio

5MHz Input Signal (PGA = 0)

71.7

dB

5MHz Input Signal (PGA = 1)

70.1

dB

30MHz Input Signal (PGA = 0)

71.6

dB

30MHz Input Signal (PGA = 1)

70.0

dB

70MHz Input Signal (PGA = 0)

71.2

dB

70MHz Input Signal (PGA = 1)

69.9

dB

250MHz Input Signal (PGA = 1)

68.6

dB

THD

Total Harmonic Distortion

5MHz Input Signal, First 5 Harmonics (PGA = 0)

87

dB

5MHz Input Signal, First 5 Harmonics (PGA = 1)

87

dB

30MHz Input Signal, First 5 Harmonics (PGA = 0)

87

dB

30MHz Input Signal, First 5 Harmonics (PGA = 1)

87

dB

70MHz Input Signal, First 5 Harmonics (PGA = 0)

85

dB

70MHz Input Signal, First 5 Harmonics (PGA = 1)

87

dB

250MHz Input Signal (PGA = 1)

78

dB

IMD

Intermodulation Distortion

f

IN1

= 2.52MHz, f

IN2

= 5.2MHz (PGA = 0)

87

dBc

f

IN1

= 2.52MHz, f

IN2

= 5.2MHz (PGA = 1)

87

dBc

Sample-and-Hold Bandwidth

R

SOURCE

= 50

500

MHz

T

A

= 25

°

C, A

IN

= 1dBFS (Note 5), V

SENSE

= V

DD

DY

A

IC ACCURACY

U

W

4

LTC1749

1749f

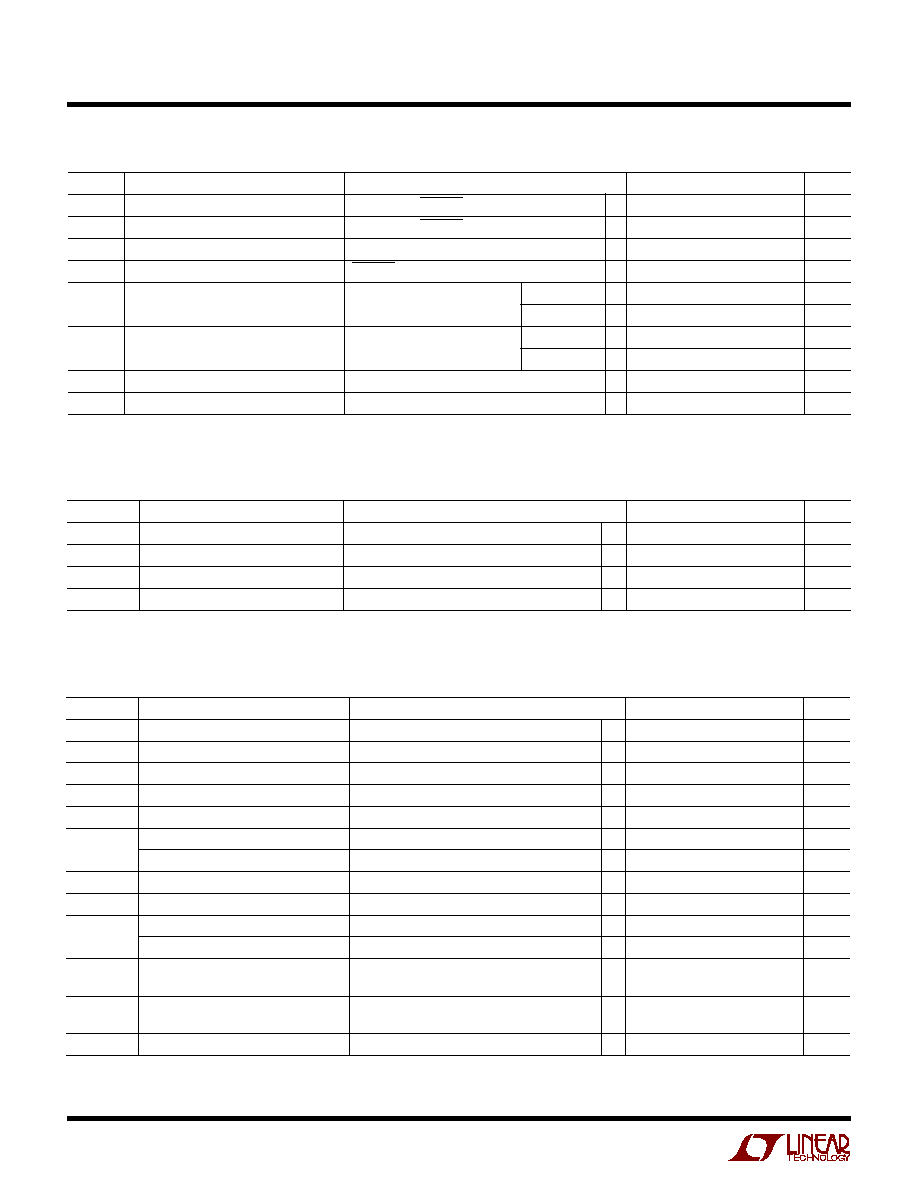

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

t

0

ENC Period

(Note 9)

q

12.5

2000

ns

t

1

ENC High

(Note 8)

q

6

1000

ns

t

2

ENC Low

(Note 8)

q

6

1000

ns

t

3

Aperture Delay

(Note 8)

0

ns

t

4

ENC to CLKOUT Falling

C

L

= 10pF (Note 8)

q

1

2.4

4

ns

t

5

ENC to CLKOUT Rising

C

L

= 10pF (Note 8)

t

1

+ t

4

ns

For 80Msps 50% Duty Cycle

C

L

= 10pF (Note 8)

q

7.25

8.65

10.25

ns

t

6

ENC to DATA Delay

C

L

= 10pF (Note 8)

q

2

4.9

7.2

ns

t

7

ENC to DATA Delay (Hold Time)

(Note 8)

q

1.4

3.4

4.7

ns

t

8

ENC to DATA Delay (Setup Time)

C

L

= 10pF (Note 8)

t

0

t

6

ns

For 80Msps 50% Duty Cycle

C

L

= 10pF (Note 8)

q

5.3

7.6

10.5

ns

t

9

CLKOUT to DATA Delay (Hold Time),

(Note 8)

q

6

ns

80Msps 50% Duty Cycle

t

10

CLKOUT to DATA Delay (Setup Time),

C

L

= 10pF (Note 8)

q

2.1

ns

80Msps 50% Duty Cycle

Data Latency

5

cycles

The

q

indicates specifications which apply over the full operating temperature

range, otherwise specifications are at T

A

= 25

°

C. (Note 5)

TI I G CHARACTERISTICS

U

W

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

V

DD

Positive Supply Voltage

4.75

5.25

V

I

DD

Positive Supply Current

q

290

338

mA

P

DIS

Power Dissipation

q

1.45

1.69

W

OV

DD

Digital Output Supply Voltage

0.5

V

DD

V

The

q

indicates specifications which apply over the full operating temperature

range, otherwise specifications are at T

A

= 25

°

C. (Note 5)

POWER REQUIRE E TS

W

U

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

V

IH

High Level Input Voltage

V

DD

= 5.25V, MSBINV and PGA

q

2.4

V

V

IL

Low Level Input Voltage

V

DD

= 4.75V, MSBINV and PGA

q

0.8

V

I

IN

Digital Input Current

V

IN

= 0V to V

DD

q

±

10

µ

A

C

IN

Digital Input Capacitance

MSBINV and PGA Only

1.5

pF

V

OH

High Level Output Voltage

OV

DD

= 4.75V

I

O

= 10

µ

A

4.74

V

I

O

= 200

µ

A

q

4

4.74

V

V

OL

Low Level Output Voltage

OV

DD

= 4.75V

I

O

= 160

µ

A

0.05

V

I

O

= 1.6mA

q

0.1

0.4

V

I

SOURCE

Output Source Current

V

OUT

= 0V

50

mA

I

SINK

Output Sink Current

V

OUT

= 5V

50

mA

The

q

indicates specifications which apply over the full

operating temperature range, otherwise specifications are at T

A

= 25

°

C. (Note 5)

DIGITAL I PUTS A D DIGITAL OUTPUTS

U

U

5

LTC1749

1749f

Note 1: Absolute Maximum Ratings are those values beyond which the life

of a device may be impaired.

Note 2: All voltage values are with respect to GND (unless otherwise

noted).

Note 3: When these pin voltages are taken below GND or above V

DD

, they

will be clamped by internal diodes. This product can handle input currents

of greater than 100mA below GND or above V

DD

without latchup.

Note 4: When these pin voltages are taken below GND, they will be

clamped by internal diodes. This product can handle input currents of

>100mA below GND without latchup. These pins are not clamped to V

DD

.

Note 5: V

DD

= 5V, f

SAMPLE

= 80MHz, differential ENC/ENC = 2V

P-P

80MHz

sine wave, input range =

±

1.125V differential, unless otherwise specified.

Note 6: Integral nonlinearity is defined as the deviation of a code from a

straight line passing through the actual endpoints of the transfer curve.

The deviation is measured from the center of the quantization band.

Note 7: Bipolar offset is the offset voltage measured from 0.5 LSB

when the output code flickers between 0000 0000 0000 and

1111 1111 1111.

Note 8: Guaranteed by design, not subject to test.

Note 9: Recommended operating conditions.

ELECTRICAL CHARACTERISTICS

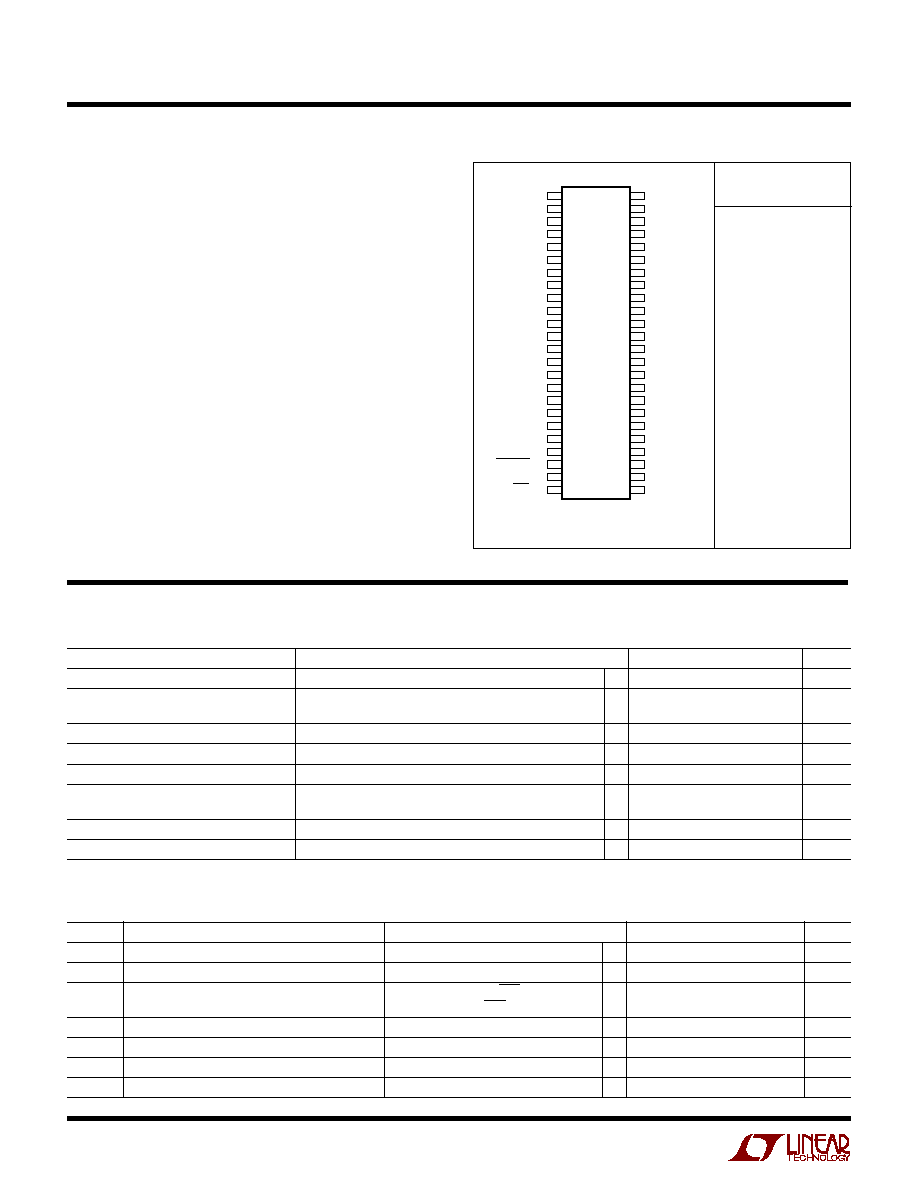

TYPICAL PERFOR A CE CHARACTERISTICS

U

W

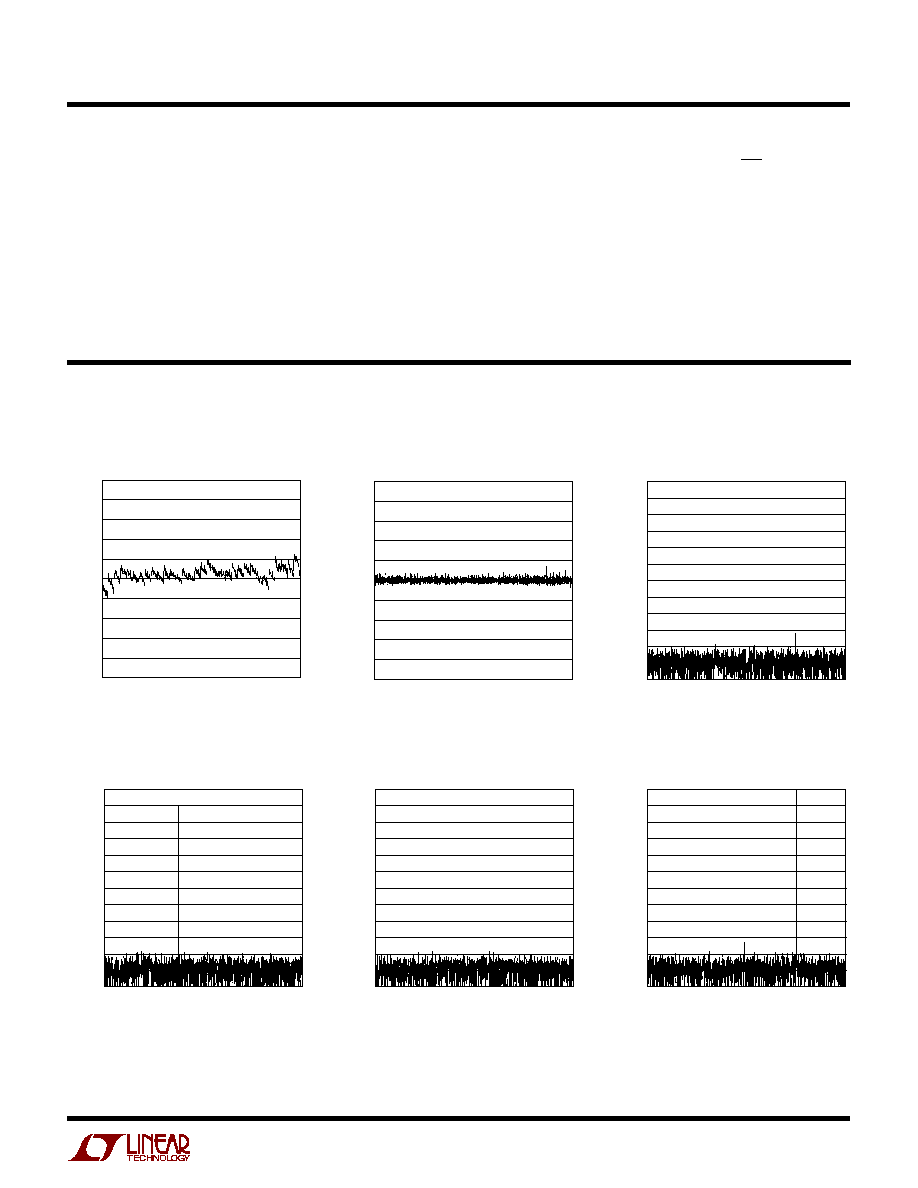

INL

OUTPUT CODE

0

1.0

ERROR (LSB)

0.8

0.4

0.2

0

1.0

0.4

1024

2048

1749 G01

0.6

0.6

0.8

0.2

3072

4096

OUTPUT CODE

0

1.0

ERROR (LSB)

0.8

0.4

0.2

0

1.0

0.4

1024

2048

1749 G02

0.6

0.6

0.8

0.2

3072

4096

FREQUENCY (MHz)

0

AMPLITUDE (dBFS)

60

30

20

40

1749 G03

70

80

120

10

20

30

5

15

25

35

100

0

10

40

50

90

110

DNL

8192 Point FFT, f

IN

= 15MHz,

1dB, PGA = 0

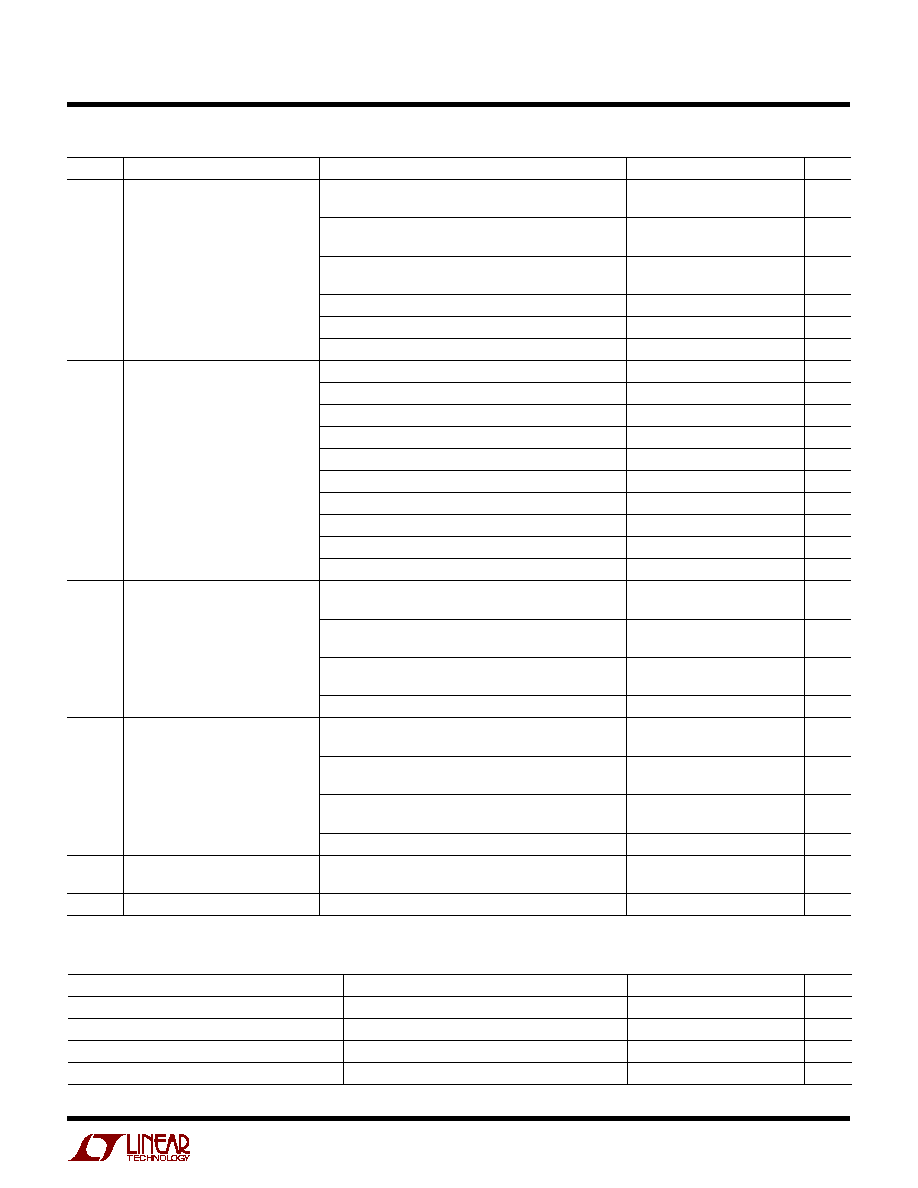

8192 Point FFT, f

IN

= 30.2MHz,

1dB, PGA = 0

8192 Point FFT, f

IN

= 15MHz,

20dB, PGA = 0

8192 Point FFT, f

IN

= 15MHz,

10dB, PGA = 0

FREQUENCY (MHz)

0

AMPLITUDE (dBFS)

60

30

20

40

1749 G04

70

80

120

10

20

30

5

15

25

35

100

0

10

40

50

90

110

FREQUENCY (MHz)

0

AMPLITUDE (dBFS)

60

30

20

40

1749 G05

70

80

120

10

20

30

5

15

25

35

100

0

10

40

50

90

110

FREQUENCY (MHz)

0

AMPLITUDE (dBFS)

60

30

20

40

1749 G06

70

80

120

10

20

30

5

15

25

35

100

0

10

40

50

90

110