| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: L64118 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

February 1999

1

Copyright © 1997, 1998 by LSI Logic Corporation. All rights reserved.

Æ

L64118 MPEG-2 Transport

Controller with

Embedded MIPS CPU (TR4101)

Preliminary Datasheet

LSI Logic's L64118 MPEG-2 Transport Controller with Embedded MIPS

CPU (TR4101) is a highly integrated set-top box control and

communication device, combining most of the logic needed for a digital

broadcast system (DBS) or cable set-top box onto a single chip. The

L64118's embedded 32-bit TinyRISCTM MIPS CPU core provides

processing power to support transport and system data, as well as

general-purpose system control.

The L64118 interfaces directly to LSI Logic's L64704 and L64724

(satellite), and the L64768 (cable) single-chip channel decoders, as well

as to the L64105 MPEG-2 A/V decoder.

The MPEG-2 transport and system demultiplexer can handle 32 Packet

Identifications (PIDs) simultaneously, including audio, video, and general-

purpose data services. It integrates a Digital Video Broadcasting (DVB)-

compliant descrambler block, substantially increasing the security of the

set-top box.

The L64118's synchronous External System Bus (EBus) communicates

with external peripherals. The L64118 communicates with peripherals

through serial, parallel, SmartCard, and infrared ports. Several general-

purpose I/O pins are provided that let system designers expand the

system's capabilities.

The L64118 supports industry-standard SDRAM memory of up to

16 Mbytes, using 16 and 64 Mbit SDRAMs. The SDRAM interface

supports PC66/100-compliant SDRAMS.

The L64118 is offered in LSI Logic's 3.3 V G10

Æ

-p cell-based technology

and is packaged in a 256-pin PBGA (IF) package.

118bds Page 1 Wednesday, February 3, 1999 12:37 PM

2

L64118 MPEG-2 Transport Controller with Embedded MIPS CPU (TR4101)

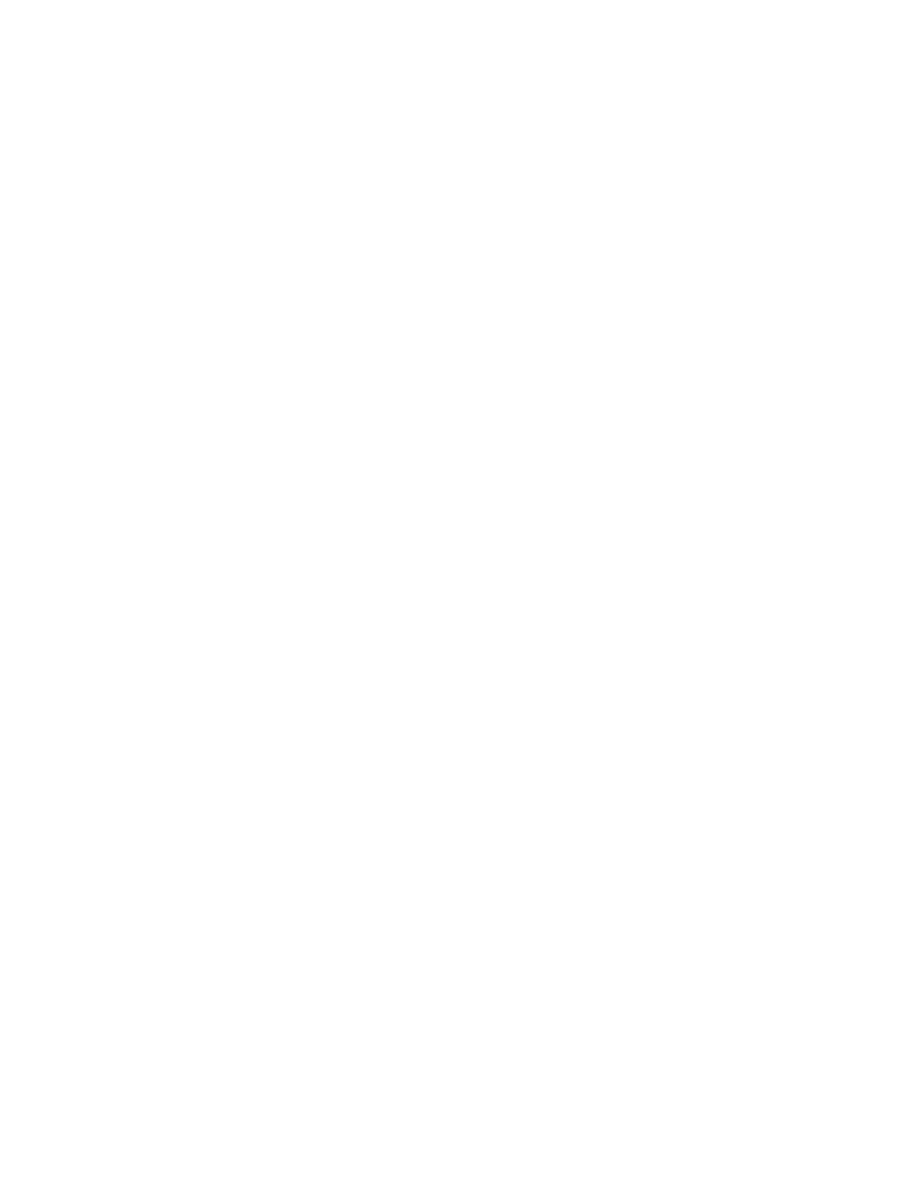

Figure 1

Typical Set-Top Box Using the L64118

The L64118's embedded 32-bit MIPS CPU (TR4101) runs at 54 MHz.

The chip's CPU block is 32 bit, while the bus interface to external

memory (through the SDRAM controller) is 16 bit. The CPU can run

MIPS16 and MIPS32 instructions. The 32-bit operations allow

high-performance operation, while 16-bit operations allow for code

optimization and memory savings. Since most transport processing and

filtering is implemented in hardware, much of the CPU's processing

power can be devoted to system processing.

Tuner

L64724

L64118

16 Mbyte

VCXO

L64105

1 M x 16

SDRAM

SDRAM

PAL / NTSC

NTSC

PAL

S-VIDEO

L-SPEAKER

R-SPEAKER

CCIR601VIDEO

PCM-AUDIO

Encoder

Satellite/Cable

16

16

27MHz

8

1 Mbyte x 16

FLASH

Line Driver

3 x RS232

Line Driver

IEEE1284

2

2

16

/L64768

In

ACLK

External System Bus

Optional 1 Mbyte x 16

SDRAM

Fast

Parallel

Port

PC

Modem

PES

TS

I

2

C

Port

Aux

27 MHz

2

2

2

2

GP I/Os

SmartCards

2 x

PCM

DAC

Optional

16/32

IR Blaster/

Receiver

FLASH

1 Mbyte x 16

(max.)

Teletext

Interface

118bds Page 2 Wednesday, February 3, 1999 12:37 PM

L64118 MPEG-2 Transport Controller with Embedded MIPS CPU (TR4101)

3

The L64118 processes the transport data packets in the PID Processing

Unit (PPU) according to the MPEG-2 standard draft 13818-1, making

Packetized Elementary Stream (PES), Program Specific Information

(PSI), Service Information (SI), and Private data available to the system.

It also buffers and transfers audio and video PES data packets to the

external decoder device.

The L64118 interfaces directly to LSI Logic's L64105 MPEG-2 A/V

decoder. It outputs demultiplexed audio and video PES streams for

processing by the L64105. This decoder's extended channel buffer

feature lets you use part of the L64118 SDRAM space to store A/V PES

data directed to the L64105. One benefit of this is that it lets you free

memory in the L64105 and increases its On-Screen Display (OSD)

capability.

The L64118 also interfaces directly to LSI Logic's family of single-chip

channel decoders (L64704, L64724, and L64768), which allows channel

data to be transferred in parallel or serial modes. The L64118

implements an automatic sync locking mechanism with a programmable

hysteresis function for reliable locking onto MPEG-2 (0x47) transport

packet sync bytes.

The External System Bus (EBus) is a general-purpose, 32-bit wide

system bus. It is controlled by the L64118 for communication with

external components in the system. This bus provides the system

designer with an interface that permits the glueless connection of devices

such as FLASH, ROMs, and external peripherals.

The L64118's peripheral interface blocks let you connect external

systems directly to the set-top box. The RS232 ports let you connect a

PC, modem, or terminal directly to the chip. The IEEE1284 parallel port

lets you connect to fast peripheral devices and transfer filtered transport

packets. The IEEE1284 parallel port includes an on-chip DMA controller

for expediting data transfers between memory to, and from, the port.

The L64118 includes an infrared transmitter (blaster) port for applications

such as (remotely) programming a VCR, as well as two independent

infrared receiver ports, which can be used to program the set-top box

using a remote controller.

118bds Page 3 Wednesday, February 3, 1999 12:37 PM

4

L64118 MPEG-2 Transport Controller with Embedded MIPS CPU (TR4101)

The 27 MHz system clock drives the L64118 internal demultiplexer block,

as well as most of the peripheral modules. The PLL block generates

54 MHz from the 27 MHz system clock to drive the CPU logic.

The L64118 includes four DMA channels (one dedicated to the

IEEE1284 port, three independent) that can be used to transfer data

between peripheral ports and memory, from one memory location to

another, or from memory to an external system device.

Features

The L64118 provides additional system features for a set-top box

application, including:

Channel

∑

Compliance with ISO/IEC 13818-1 (MPEG-2) Transport

specifications

∑

Sustained rates up to 90 Mbits/s serial and up to 13.0 Mbytes/s

parallel transport stream input interface

∑

Direct interface to LSI Logic single-chip channel decoder devices,

such as the L64704, the L64768, and the L64724

Demux

∑

PID filtering (32 user-programmable PIDs)

≠

Hardware-assisted section filtering for 30 general-purpose PIDs

(PSI, SI, and Private)

≠

Each filter includes 12 match bytes and 12 mask bytes

≠

Each PID can select up to 32 filters simultaneously

∑

Support of a Program Clock Reference (PCR) PID

∑

CRC32 in parallel to all sections in the filtering process

∑

Descrambler core compliant to DVB common scrambling

specifications

∑

Support for transport-level and PES-level descrambling

∑

Seamless support of scrambled and unscrambled data

∑

Support of up to 12 pairs of 64-bit keys

118bds Page 4 Wednesday, February 3, 1999 12:37 PM

L64118 MPEG-2 Transport Controller with Embedded MIPS CPU (TR4101)

5

∑

Two 256-byte transport buffers for supporting audio and video PES

streams

∑

32 programmable cyclic buffers in SDRAM memory assignable to a

PID or section filter index

∑

Support for an additional programmable cyclic buffer in SDRAM to

post data to adaptation fields

∑

Program Clock Reference (PCR) recovery and locking

∑

Automatic detecting and switching of audio and video PIDs on splice

points

∑

Audio oversampling (256 or 384 times oversampling) clock

generation

CPU and Subsystems

∑

Integration of the CPU system:

≠

32-bit TR4101 54 MHz TinyRISC CPU

≠

MIPS16 and MIPS-II instruction set compatible

≠

Four Kbyte Data (direct mapped) and Eight Kbyte (two-way set

associative) instruction cache

≠

Basic Bus and Cache Controller unit (BBCC)

≠

Multiply/Divide Unit (MDU)

≠

Debugger Building Module (DBX)

≠

32-bit Timers and Interrupt Controller

≠

In-Circuit Emulator (ICE) port

∑

Two interrupt handling modes:

≠

Interrupt Compatibility mode supports 12 interrupt ports and six

main interrupt levels. This mode is compatible with the L64108

interrupt structure.

≠

Interrupt Extension mode supports 25 interrupt ports with a

software index to each interrupt source. This new mode can

reduce interrupt latency.

118bds Page 5 Wednesday, February 3, 1999 12:37 PM