| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: MAX2308 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at

1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

General Description

The MAX2306/MAX2308/MAX2309 are IF receivers

designed for dual-band, dual-mode, and single-mode

N-CDMA and W-CDMA cellular phone systems. The

signal path consists of a variable-gain amplifier (VGA)

and I/Q demodulator. The devices feature guaranteed

+2.7V operation, a gain control range of over 110dB,

and high input IP3 (-31dBm at 35dB gain, 3.4dBm at

-35dB gain).

Unlike similar devices, the MAX2306 family of receivers

includes dual oscillators and synthesizers to form a

self-contained IF subsystem. The synthesizer's refer-

ence and RF dividers are fully programmable through a

3-wire serial bus, enabling dual-band system architec-

tures using any common reference and IF frequency.

The differential baseband outputs have enough band-

width to suit both N-CDMA and W-CDMA systems, and

offer saturated output levels of 2.7Vp-p at a low +2.75V

supply voltage. Including the low-noise voltage-con-

trolled oscillator (VCO) and synthesizer, the MAX2306

draws only 26mA from a +2.75V supply in CDMA (dif-

ferential IF) mode.

The MAX2306/MAX2308/MAX2309 are available in 28-

pin QFN packages.

Applications

Single/Dual/Triple-Mode CDMA Handsets

Globalstar Dual-Mode Handsets

Wireless Data Links

W-CDMA Handsets

Wireless Local Loop (WLL)

Features

o Complete IF Subsystem Includes VCO and

Synthesizer

o Supports Dual-Band, Triple-Mode Operation

o VGA with >110dB Gain Control

o Quadrature Demodulator

o High Output Level (2.7V)

o Programmable Charge-Pump Current

o Supports Any IF Frequency Between 40MHz and

300MHz

o 3-Wire Programmable Interface

o Low Supply Voltage (+2.7V)

MAX2306/MAX2308/MAX2309

CDMA IF VGAs and I/Q Demodulators

with VCO and Synthesizer

________________________________________________________________ Maxim Integrated Products

1

19-2014; Rev 2; 7/01

EVALUATION KIT AVAILABLE

Pin Configurations appear at end of data sheet.

Block Diagram appears at end of data sheet.

Ordering Information

Selector Guide

*Exposed paddle

PART

TEMP. RANGE

PIN-PACKAGE

MAX2306EGI

-40

∞C to +85∞C

28 QFN-EP*

MAX2308EGI

-40

∞C to +85∞C

28 QFN-EP*

MAX2309EGI

-40

∞C to +85∞C

28 QFN-EP*

PART

MODE

DESCRIPTION

INPUT RANGE

MAX2306

AMPS,

Cellular CDMA,

PCS CDMA

Dual Band, Triple Mode with Two

IF VCOs

40MHz to 300MHz

MAX2308

AMPS,

Cellular CDMA,

PCS CDMA

Dual Band, Triple Mode with Common

IF VCO

70MHz to 300MHz

MAX2309

External AMPS,

Cellular CDMA,

PCS CDMA

Dual Band, Triple Mode (Drives External

AMPS Discriminator)

70MHz to 300MHz

MAX2306/MAX2308/MAX2309

CDMA IF VGAs and I/Q Demodulators

with VCO and Synthesizer

2

_______________________________________________________________________________________

ABSOLUTE MAXIMUM RATINGS

DC ELECTRICAL CHARACTERISTICS

(V

CC

= +2.7V to +3.6V, MODE = DIVSEL = SHDN = STBY = BUFEN = high, differential output load = 10k

, T

A

= -40∞C to +85∞C,

registers set to default power-up settings. Typical values are at V

CC

= +2.75V and T

A

= +25∞C, unless otherwise noted.)

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

V

CC

to GND ...........................................................-0.3V to +6.0V

SHDN to GND.............................................-0.3V to (V

CC

+ 0.3V)

STBY, BUFEN, MODE, EN, DATA,

CLK, DIVSEL ...........................................-0.3V to (V

CC

+ 0.3V)

VGC to GND...............-0.3V, the lesser of +4.2V or (V

CC

+ 0.3V)

AC Signals TANKH ±, TANKL ±,

REF, FM ±, CDMA ± .................................................1.0V peak

Digital Input Current SHDN, MODE, DIVSEL,

BUFEN, DATA, CLK, EN, STBY .....................................±10mA

Continuous Power Dissipation (T

A

= +70∞C)

28-Pin QFN (derate 28.5mW/∞C above T

A

= +70∞C) ...........2W

Operating Temperature Range ...........................-40∞C to +85∞C

Junction Temperature ......................................................+150∞C

Storage Temperature Range .............................-65∞C to +160∞C

Lead Temperature (soldering, 10s) .................................+300∞C

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

T

A

= +25∞C

25.9

37.5

CDMA mode

T

A

= -40∞C to +85∞C

41.5

T

A

= +25∞C

25.4

36.7

FM_IQ mode

T

A

= -40∞C to +85∞C

40.6

T

A

= +25∞C

24.7

35.7

FM_I mode

T

A

= -40∞C to +85∞C

39.5

T

A

= +25∞C

12.3

18.8

STANDBY (VCO_H)

T

A

= -40∞C to +85∞C

20.7

T

A

= +25∞C

11.4

18.4

STANDBY (VCO_L)

T

A

= -40∞C to +85∞C

20.3

Supply Current

(Note 1)

I

CC

Addition for LO out (

BUFEN = low)

3.5

mA

Shutdown Current

I

CC

SHDN = low

1.5

10

µA

Register Shutdown Current

I

CC

4

5.8

mA

Logic High

2.0

V

Logic Low

0.5

V

Logic High Input Current

I

IH

2

µA

Logic Low Input Current

I

IL

2

µA

VGC Control Input Current

0.5V < V

VGC

< 2.3V

-5

5

µA

VGC Control Input Current

During Shutdown

SHDN = low

1

µA

Lock Indicator High (locked)

47k

load

2.0

V

Lock Indicator Low (unlocked)

47k

load

0.5

V

DC Offset Voltage

I+ to I- and Q+ to Q-, PLL locked

-20

±1.5

+20

mV

Common-Mode Output Voltage

V

CC

= +2.75V

V

CC

- 1.4

V

MAX2306/MAX2308/MAX2309

CDMA IF VGAs and I/Q Demodulators

with VCO and Synthesizer

_______________________________________________________________________________________

3

AC ELECTRICAL CHARACTERISTICS

(MAX2306/MAX2308/MAX2309 EV kit, V

CC

= +2.75V, registers set to default power-up states except M1 = M2 = 306, R1 = R2 = 16,

f

IN

= 183.7MHz, f

REF

= 19.2MHz, 0.6Vp-p synthesizer locked with passive 3rd-order lead-lag loop filter, SHDN = high, VGC set for

+35dB voltage gain, differential output load = 10k

, all power levels referred to 50, T

A

= +25∞C, unless otherwise noted.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Input Frequency

f

IN

(Note 2)

40

300

MHz

Reference Frequency

f

REF

39

MHz

Frequency Reference Signal

Level

V

REF

0.2

Vp-p

SIGNAL PATH, CDMA MODE

Gain = -35dB, (Note 3)

3.4

Input 3rd-Order Intercept

IIP3

Gain = +35dB, T

A

= -40∞C to +85∞C

(Notes 4, 5)

-38

-31.0

dBm

Gain = -35dB

-9

Input 1dB Compression

P

1dB

Gain = +35dB

-44

dBm

Gain = -35dB

-14.8

Input 0.25dB Desensitization

(Note 6)

Gain = +35dB

-49

dBm

Minimum Voltage Gain

A

V

V

VGC

= 0.5V (Note 5)

-56

-51

dB

Maximum Voltage Gain

A

V

V

VGC

= 2.3V (Note 5)

57

61

dB

Gain = -35dB

62.9

DSB Noise Figure

NF

Gain = +35dB

6.36

dBm

SIGNAL PATH, FM_IQ MODE

Gain = -35dB, (Note 7)

-6.5

Input 3rd-Order Intercept

IIP3

Gain = +35dB, T

A

= -40∞C to +85∞C

(Notes 5, 8)

-40.2

-32

dBm

Gain = -35dB

-20

Input 1dB Compression

P

1dB

Gain = +35dB

-44

dBm

Minimum Voltage Gain

A

V

V

VGC

= 0.5V (Note 5)

-56.7

-52

dB

Maximum Voltage Gain

A

V

V

VGC

= 2.3V (Note 5)

56

59.5

dB

SIGNAL PATH, CDMA AND FM_IQ MODE

Gain Variation Over Temperature

Normalized to +25∞C

±2.5

dB

Baseband 0.5dB Bandwidth

4.2

MHz

Quadrature Suppression

T

A

= -40∞C to +85∞C (Note 5)

28

40

dB

LO to Baseband Leakage

1

mVp-p

Saturated Output Level

V

SAT

Differential

2.7

Vp-p

PHASE-LOCKED LOOP

F

VCO

_

L

(Note 2)

80

300

VCO Tune Range

F

VCO

_

H

(Note 2)

135

600

MHz

LO_OUT Output Power

P

LO

R

L

= 50

, BUFEN = low

-13.7

dBm

VCO Minimum Divide Ratio

M1, M2

256

VCO Maximum Divide Ratio

M1, M2

16383

REF Minimum Divide Ratio

R1, R2

2

MAX2306/MAX2308/MAX2309

CDMA IF VGAs and I/Q Demodulators

with VCO and Synthesizer

4

_______________________________________________________________________________________

AC ELECTRICAL CHARACTERISTICS (continued)

(MAX2306/MAX2308/MAX2309 EV kit, V

CC

= +2.75V, registers set to default power-up states except M1 = M2 = 306, R1 = R2 = 16,

f

IN

= 183.7MHz, f

REF

= 19.2MHz, 0.6Vp-p synthesizer locked with passive 3rd-order lead-lag loop filter, SHDN = high, VGC set for

+35dB voltage gain, differential output load = 10k

, all power levels referred to 50, T

A

= +25∞C, unless otherwise noted.)

Note 1:

FM_IQ and FM_I modes are not available on MAX2309.

Note 2:

Recommended operating frequency range. Contact factory for operating frequency outside this range.

Note 3:

f

1

= 183.7MHz, f

2

= 183.71MHz, P

f1

= P

f2

= -15dBm.

Note 4:

f

1

= 183.7MHz, f

2

= 183.71MHz, P

f1

= P

f2

= -50dBm.

Note 5:

Guaranteed by design.

Note 6:

Small-signal gain at 200kHz below the LO frequency will be reduced by less than 0.25dB when an interfering signal at

1.25MHz below the LO frequency is applied at the specified level.

Note 7:

f

1

= 183.7MHz, f

2

= 183.71MHz, P

f1

= P

f2

= -23dBm.

Note 8:

f

1

= 183.7MHz, f

2

= 183.71MHz, P

f1

= P

f2

= -55dBm.

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

REF Maximum Divide Ratio

R1, R2

2047

Minimum Phase Detector

Comparison Frequency

(Note 5)

20

kHz

Maximum Phase Detector

Comparison Frequency

(Note 5)

1500

kHz

1kHz offset, T

A

= -40∞C to +85∞C

-79.6

12.5kHz offset, T

A

= -40∞C to +85∞C

-94.6

30kHz offset, T

A

= -40∞C to +85∞C

-105

120kHz offset, T

A

= -40∞C to +85∞C

-115.3

Phase Noise

900kHz offset, T

A

= -40∞C to +85∞C

-125

dBc/Hz

TURBO LOCK

Acquisition, CPX = XX, TC =1

1480

2100

2650

Locked, CPX = 00

105

150

190

Locked, CPX = 01

150

210

265

Locked, CPX = 10

210

300

380

Charge-Pump Source/Sink

Current

Locked, CPX = 11

300

425

530

µA

Charge-Pump Source/Sink

Matching

Locked, all values of CPX,

0.5V < V

CP

< V

CC

- 0.5V

0.2

10

%

MAX2306/MAX2308/MAX2309

CDMA IF VGAs and I/Q Demodulators

with VCO and Synthesizer

_______________________________________________________________________________________

5

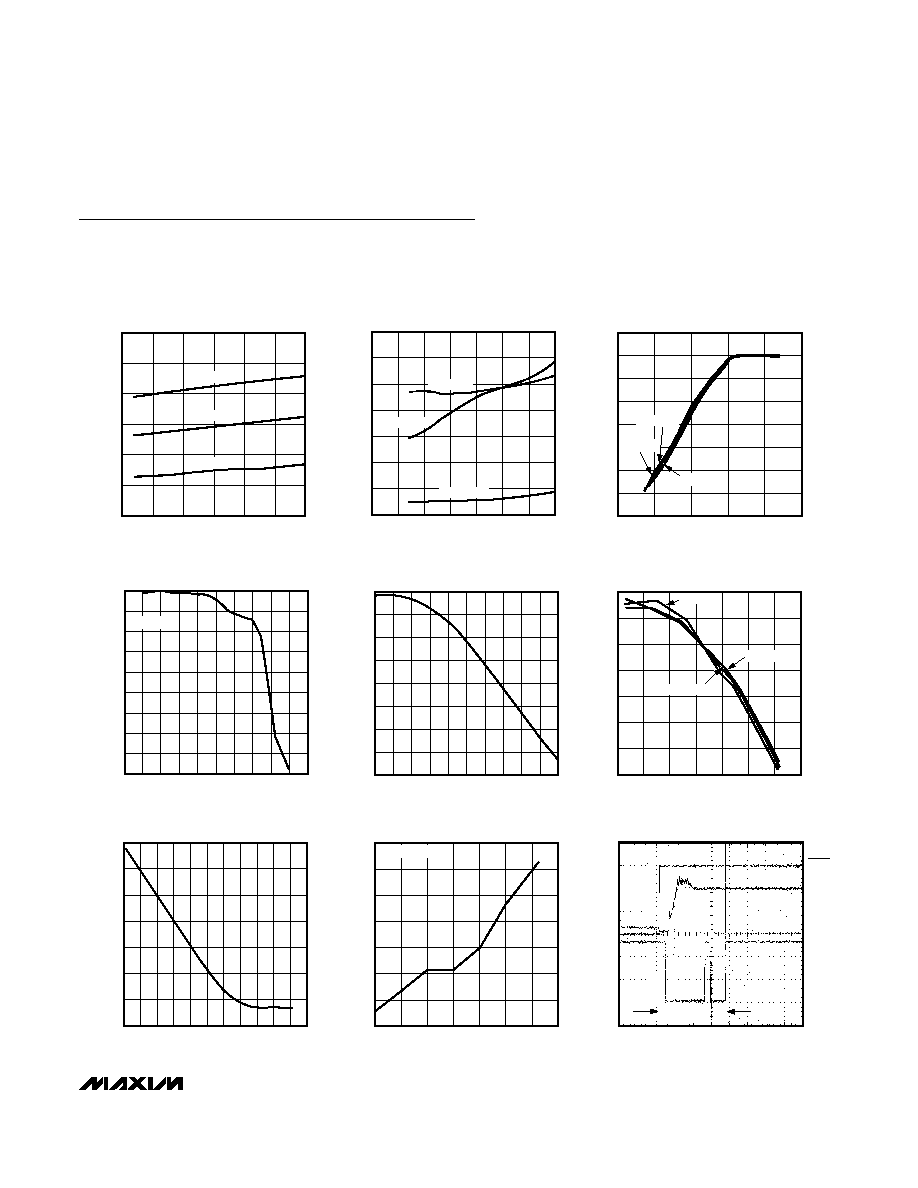

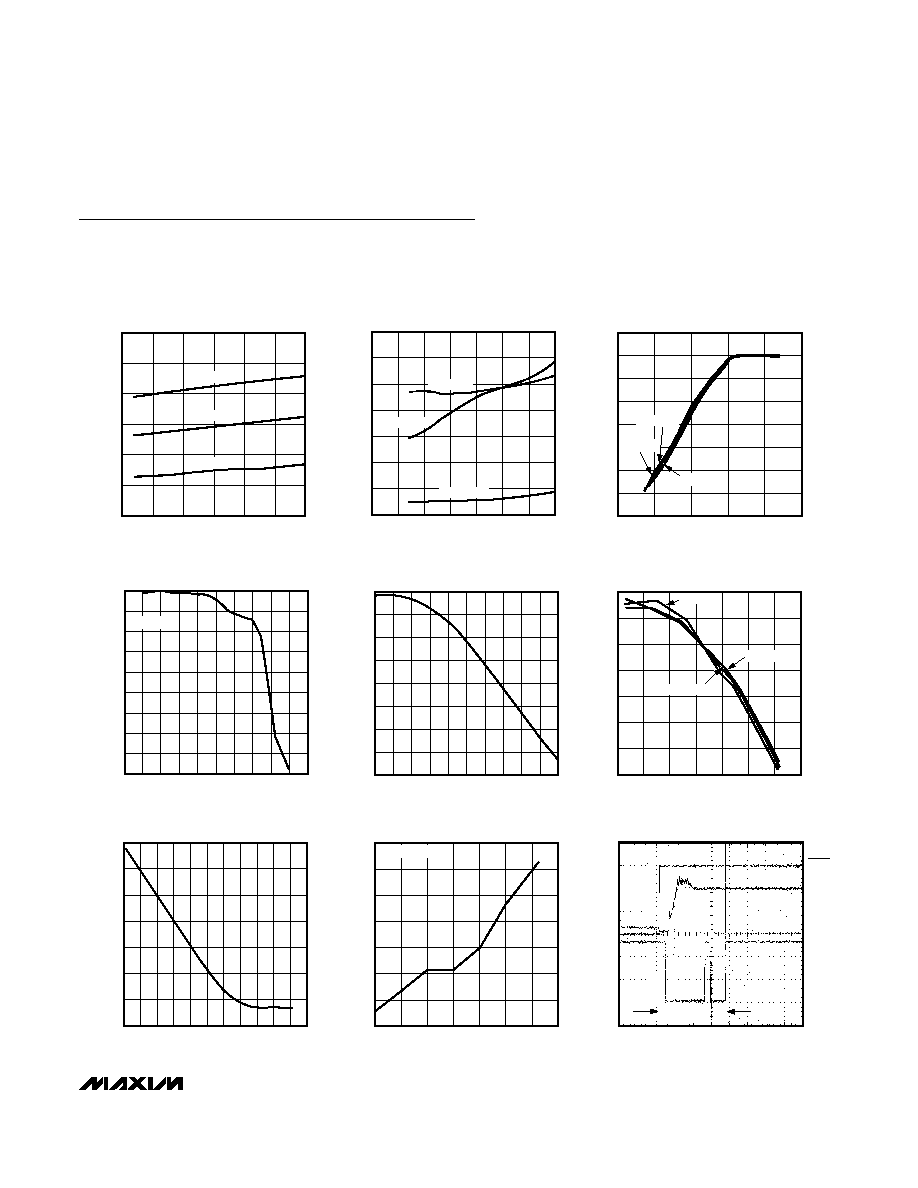

20.00

25.00

22.50

30.00

27.50

32.50

35.00

2.5

3.5

4.0

3.0

4.5

5.0

5.5

RECEIVE SUPPLY CURRENT

vs. SUPPLY VOLTAGE

MAX2306/8/9 toc01

SUPPLY VOLTAGE (V)

SUPPLY CURRENT (mA)

T

A

= +85

∞C

T

A

= +25

∞C

T

A

= -40

∞C

0

0.004

0.002

0.008

0.006

0.012

0.010

0.014

2.0

3.0

3.5

2.5

4.0

4.5

5.0

5.5

RECEIVE SHUTDOWN CURRENT vs.

SUPPLY VOLTAGE

MAX2306/8/9 toc02

SUPPLY VOLTAGE (V)

SHUTDOWN CURRENT (mA)

T

A

= -40

∞C

T

A

= +25

∞C

T

A

= +85

∞C

-80

-60

-40

-20

0

20

40

60

80

0.5

1.0

1.5

2.0

2.5

3.0

GAIN vs. V

GC

MAX2306/8/9 toc03

V

GC

(V)

GAIN (dB)

T

A

= +25

∞C

T

A

= -40

∞C

T

A

= +85

∞C

15

25

20

35

30

40

45

55

50

60

0

100

200

300

400

500

GAIN vs. INPUT FREQUENCY

MAX2306/8/9 toc04

FREQUENCY (MHz)

GAIN (dB)

V

GC

= 2.5V

56.0

57.0

56.5

57.5

59.0

59.5

58.5

58.0

60.0

0

4

6

8

10

2

12 14 16 18 20

GAIN vs. BASEBAND FREQUENCY

MAX2306/8/9 toc05

FREQUENCY (MHz)

RELATIVE GAIN (dB)

-60

-40

-50

-20

-30

0

-10

10

-60

-20

0

-40

20

40

60

80

THIRD-ORDER INPUT

INTERCEPT vs. GAIN

MAX2306/8/9 toc06

GAIN (dB)

IIP3 (dBm)

T

A

= -40

∞C

T

A

= +85

∞C

T

A

= +25

∞C

0

60

20

10

30

40

50

70

-40

-20 -10 0

-30

10 20

50

40

60

30

70

NOISE FIGURE vs. GAIN

MAX2306/8/9 toc07

GAIN (dB)

NF (dB)

6.0

6.4

6.2

6.8

6.6

7.2

7.0

7.4

-40

0

20

-20

40

60

80

100

NOISE FIGURE vs. TEMPERATURE

MAX2306/8/9 toc08

TEMPERATURE (∞C)

NF (dB)

GAIN = 50dB

LOCK

VCO

VOLTAGE

VCO VOLTAGE vs. TIME

MAX2306/8/9 toc09

500

µs/div

SHDN

LOCK TIME

1.83ms

1V/div

Typical Operating Characteristics

(MAX2306/MAX2308/MAX2309 EV kits, V

CC

= +2.75V, registers set to default power-up states, f

IN

= 183.7MHz, f

REF

= 19.2MHz,

synthesizer locked with passive 3rd-order lead-lag loop filter, SHDN = high, VGC set for +35dB voltage gain, differential output load

= 10k

, all power levels referred to 50, T

A

= +25∞C, unless otherwise noted.)