| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: MAX9489 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

General Description

The MAX9489 clock generator provides multiple clock

outputs, ideal for network routers. The MAX9489 pro-

vides 15 buffered clock outputs, each independently

programmable to any of 10 individual frequencies:

133MHz, 125MHz, 100MHz, 83MHz, 80MHz, 66MHz,

62.5MHz, 50MHz, 33MHz, or 25MHz. All of the outputs

are single-ended LVCMOS. The MAX9489 is controlled

through its I

2

CTM interface.

At power-up, the frequency of output CLK1 is set by the

tri-level input SEL to 100MHz, 125MHz, or 133MHz,

while all other outputs are logic low. All outputs are then

programmable to any available frequency through the

I

2

C interface. Additionally, all output frequencies are

adjustable up or down, by a margin of 5% or 10%,

through the I

2

C interface.

The MAX9489 requires a 25MHz reference that can be

either a crystal or an external clock signal. The

MAX9489 requires a +3.0V to +3.6V power supply and

is available in a 32-pin thin QFN package with an

exposed pad for heat removal.

Applications

Network Routers

Telecom/Networking Equipment

Storage Area Networks/Network Attached

Storage

Features

15 LVCMOS Outputs with 10 Independently

Programmable Frequencies: 133MHz, 125MHz,

100MHz, 83MHz, 80MHz, 66MHz, 62.5MHz, 50MHz,

33MHz, and 25MHz

25MHz Crystal or Clock Input Reference

Programmable Through I

2

C Interface

Programmable Output Frequency Margin of ±5%

or ±10%

Pin-Selectable Power-Up Frequency for CLK1

Output: 100MHz, 125MHz, or 133MHz

Low Output Period Jitter: < 48ps

RMS

Output-to-Output Skew < 200ps

Available in 32-Lead, 5mm x 5mm x 0.8mm,

Thin QFN Package

Operates from +3.0V to +3.6V Power Supply

Power Dissipation 450mW (typ)

Extended Temperature Range: -40∞C to +85∞C

MAX9489

Multiple-Output Network Clock Generator

________________________________________________________________ Maxim Integrated Products

1

Ordering Information

19-3385; Rev 0; 8/04

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at

1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

PART

TEMP RANGE

PIN-PACKAGE

MAX9489ETJ

-40

∞C to +85∞C

32 Thin QFN-EP*

5mm x 5mm x 0.8mm

GND

1

SCL

2

SDA

3

SEL

4

AV

DD

5

X1

6

X2

7

AGND

8

V

DD

24

CLK12

23

CLK11

22

CLK10

21

V

DD

20

CLK9

19

CLK8

18

CLK7

17

CLK1

9

CLK2

10

CLK3

11

V

DD

12

CLK4

13

CLK5

14

CLK6

15

V

DD

16

V

DD

32

SA1

31

SA0

30

GND

29

V

DD

28

CLK15

27

CLK14

26

CLK13

25

MAX9489

THIN QFN-EP

TOP VIEW

EXPOSED PAD (GND)

Pin Configuration

MAX9489

25MHz

10pF

10pF

X1

AV

DD

X2

SDA

0.1

µF

SCL

SA0

SA1

SEL

AGND

GND

CLK15

CLK1

V

DD

V

DD

V

DD

V

DD

V

DD

+3.3V

+3.3V

SERIAL

INTERFACE

CLOCK

OUTPUTS

0.1

µF x 5

Typical Operating Circuit

I

2

C is a trademark of Philips Corp.

Purchase of I

2

C components of Maxim Integrated Products, Inc.,

or one of its sublicensed Associated Companies, conveys a

license under the Philips I

2

C Patent Rights to use these compo-

nents in an I

2

C system, provided that the system conforms to the

I

2

C Standard Specification as defined by Philips.

*EP = Exposed pad.

MAX9489

Multiple-Output Network Clock Generator

2

_______________________________________________________________________________________

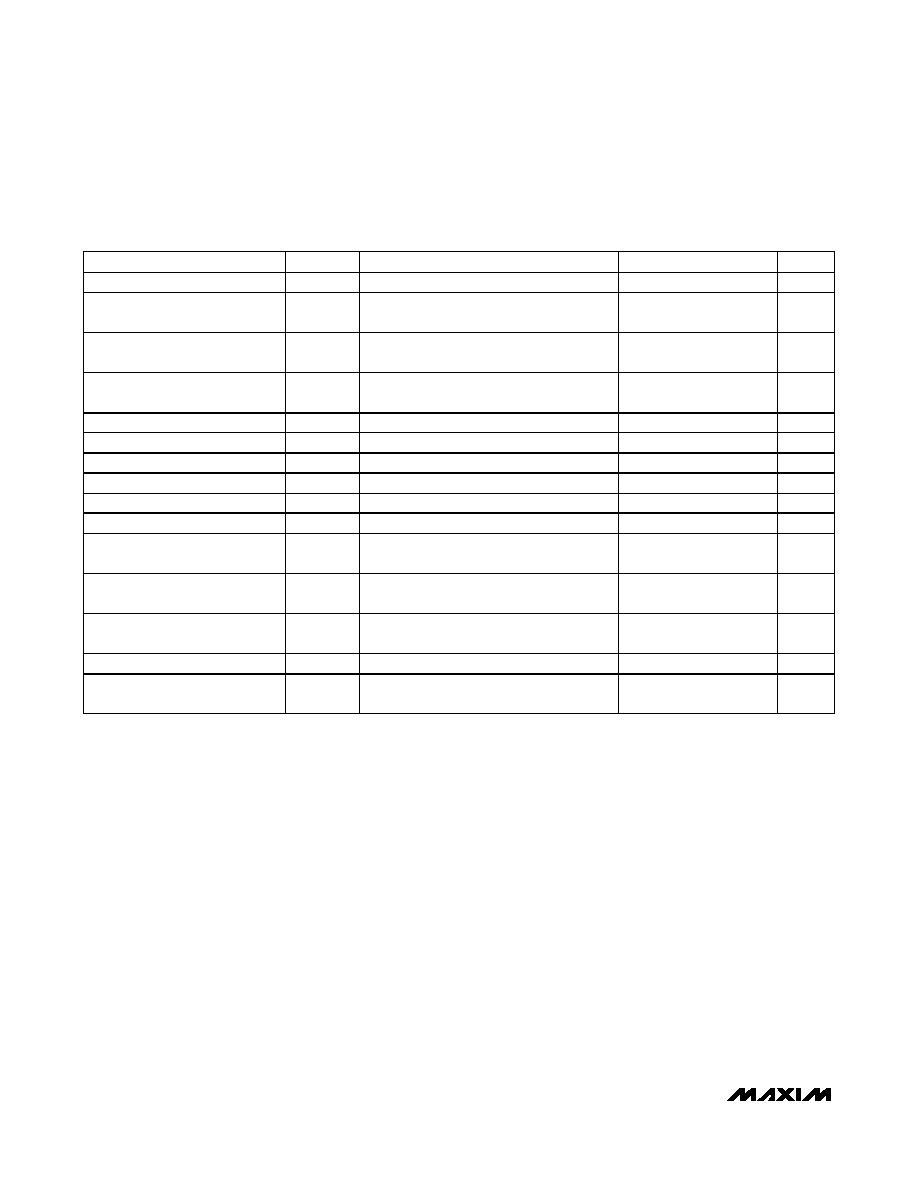

ABSOLUTE MAXIMUM RATINGS

DC ELECTRICAL CHARACTERISTICS

(V

DD

= AV

DD

= +3.0V to +3.6V, T

A

= -40∞C to +85∞C, unless otherwise noted. Typical values are at V

DD

= AV

DD

= +3.3V, T

A

= +25∞C.)

(Note 1)

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

V

DD

to GND .........................................................-0.3V to +4.0V

AGND to GND ......................................................-0.3V to +0.3V

All Other Pins to GND.................................-0.3V to (V

DD

+ 0.3V)

Short-Circuit Duration for all CLK_ Outputs ...............Continuous

Continuous Power Dissipation (T

A

= +70∞C)

32-Pin Thin QFN (derate 21.3mW/∞C above +70∞C) ....1702mW

Storage Temperature Range .............................-65∞C to +150∞C

Maximum Junction Temperature .....................................+150∞C

Operating Temperature Range ...........................-40∞C to +85∞C

ESD Rating (Human Body Model) .......................................±2kV

Lead Temperature (soldering, 10s) .................................+300∞C

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

CLOCK INPUT (X1)

Input High Level

V

IH1

2.0

V

Input Low Level

V

IL1

0.8

V

Input Current

I

IL1

, I

IH1

V

X

_ = 0 to V

DD

-5

+5

µA

CLOCK OUTPUTS (CLK_)

I

OH

= -100µA

V

DD

-

0.2

I

OH

= -4mA

2.4

Output High Level

V

OH

I

OH

= -8mA

2.1

V

I

OL

= 100µA

0.2

I

OL

= 4mA

0.4

Output Low Level

V

OL

I

OL

= 8mA

0.75

V

Output Short-Circuit Current

I

OS

CLK_ = V

DD

or GND

45

mA

Output Capacitance

C

O

(Note 2)

5

pF

TRI-LEVEL INPUTS (SEL, SA0, SA1)

Input High Level

V

IH2

2.5

V

Input Low Level

V

IL2

0.8

V

Input Open Level

V

IO2

1.35

1.90

V

Input Current

I

IL2

, I

IH2

V

IL2

= 0 or V

IH2

= V

DD

-10

+10

µA

SERIAL INTERFACE (SCL, SDA) (Note 3)

Input High Level

V

IH

0.7 x

V

DD

V

DD

V

Input Low Level

V

IL

0

0.3 x

V

DD

V

Input leakage Current

I

IH

, I

IL

-1

+1

µA

Low-Level Output

V

OL

I

SINK

= 4mA

0

0.4

V

Input Capacitance

Ci

(Note 2)

10

pF

MAX9489

Multiple-Output Network Clock Generator

_______________________________________________________________________________________

3

DC ELECTRICAL CHARACTERISTICS (continued)

(V

DD

= AV

DD

= +3.0V to +3.6V, T

A

= -40∞C to +85∞C, unless otherwise noted. Typical values are at V

DD

= AV

DD

= +3.3V, T

A

= +25∞C.)

(Note 1)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

POWER SUPPLIES

Digital Power-Supply Voltage

V

DD

3.0

3.6

V

Analog Power-Supply Voltage

AV

DD

3.0

3.6

V

Total Supply Current

C

L

= 10p f ( w i th al l C LK_ outp uts at 133M H z) 134

160

mA

Total Power-Down Current

I

PD

All clock registers = 0x00

38

47

mA

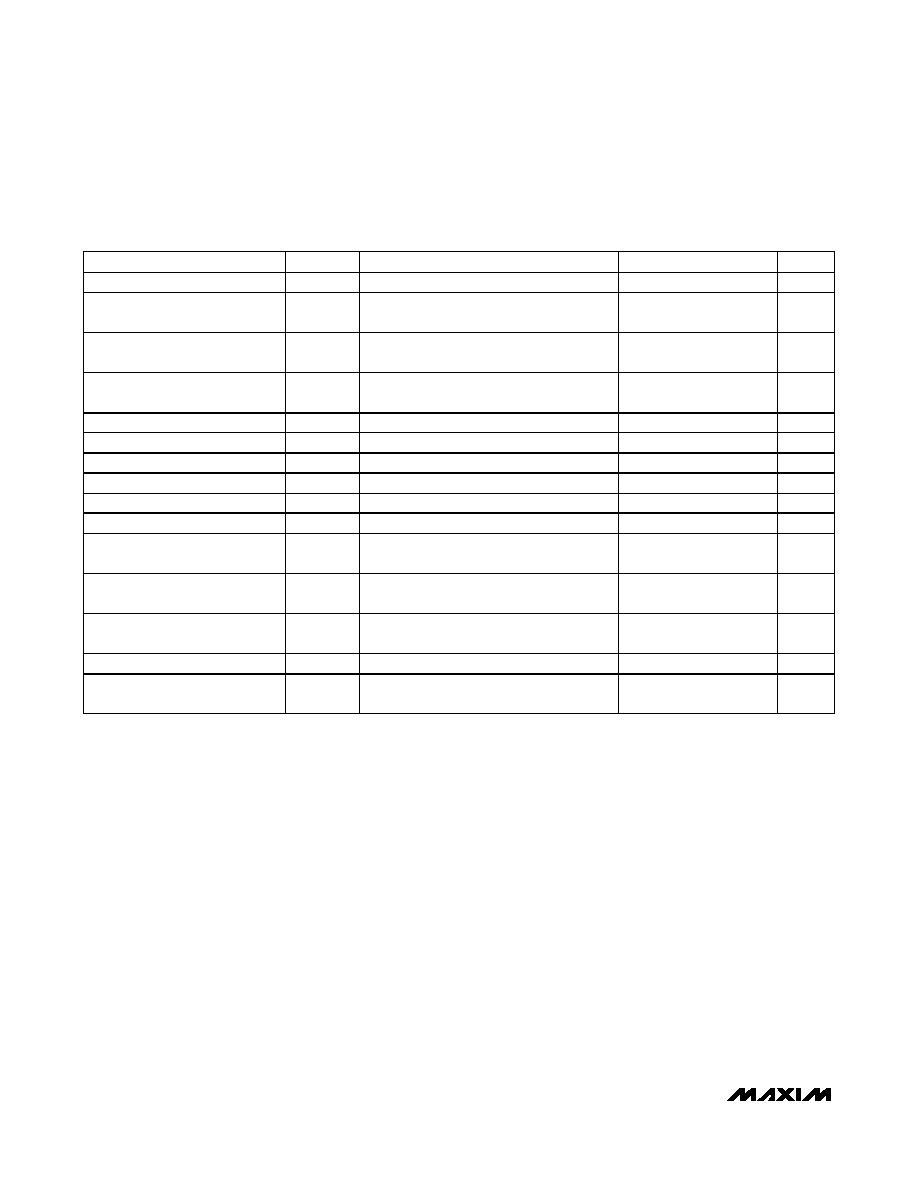

AC ELECTRICAL CHARACTERISTICS

(V

DD

= AV

DD

= +3.0V to +3.6V, C

L

= 10pF, unless otherwise noted. Typical values are at V

DD

= AV

DD

= +3.3V, T

A

= +25∞C, with all

CLK_ outputs at 133MHz.) (Note 2)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

OUTPUTS (CLK_)

Crystal Frequency Tolerance

f

A

-50

+50

ppm

Output-to-Output Skew

t

SKO

Any two CLK_ outputs

200

ps

Rise Time

t

R1

20% V

DD

to 80% V

DD

1.8

2.5

ns

Fall Time

t

F1

80% V

DD

to 20% V

DD

1.8

2.5

ns

Duty Cycle

40

60

%

Output Period Jitter

J

P

RMS

53

ps

Power-Up Time

t

PO

V

DD

> 2.8V to PLL lock

2

ms

PLL Lockup Time

t

Lock

PLL dividing ratio set to PLL lock

20

µs

Margin Accuracy

Select ±5% or ±10% margin

-1

+1

%

MAX9489

Multiple-Output Network Clock Generator

4

_______________________________________________________________________________________

Note 1: All DC parameters tested at T

A

= +25∞C. Specifications over temperature are guaranteed by design.

Note 2: Guaranteed by design.

Note 3: No high output level is specified but only the output resistance to the bus. For I

2

C, the high-level voltage is provided by

pullup resistors on the bus.

Note 4: A master device must provide a hold time of at least 300ns for the SDA signal (referred to V

IL

of the SCL signal) to bridge

the undefined region of SCL's falling edge.

Note 5: C

b

= total capacitance of one bus line in pF. t

R

and t

F

measured between 0.3(V

DD

) and 0.7(V

DD

).

Note 6: Input filters on the SDA and SCL inputs suppress noise spikes less than 50ns.

SERIAL INTERFACE TIMING

(V

DD

= AV

DD

= +3.3V, T

A

= -40∞C to +85∞C.) (Note 1, Figure 2)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Serial Clock

f

SCL

400

kHz

Bus Free Time Between STOP

and START Conditions

t

BUF

1.3

µs

Hold Time, Repeated START

Condition

t

HD,STA

0.6

µs

Repeated START Condition

Setup Time

t

SU,STA

0.6

µs

STOP Condition Setup Time

t

SU,STO

0.6

µs

Data Hold Time Master

t

HD,DAT

(Note 4)

15

900

ns

Data Hold Time Slave

t

HD,DAT

(Note 4)

15

900

ns

Data Setup Time

t

SU,DAT

100

ns

SCL Clock Low Period

t

LOW

1.3

µs

SCL Clock High Period

t

HIGH

0.7

µs

Rise Time of SDA and SCL,

Receiving

t

R

(Notes 2, 5)

20 +

0.1C

b

300

ns

Fall Time of SDA and SCL,

Receiving

t

F

(Notes 2, 5)

20 +

0.1C

b

300

ns

Fall Time of SDA, Transmitting

t

F,TX

(Notes 2, 5)

20 +

0.1C

b

250

ns

Pulse Width of Spike Suppressed

t

SP

(Notes 2, 6)

0

50

ns

Capacitive Load for Each Bus

Line

C

b

(Note 2)

400

pF

MAX9489

Multiple-Output Network Clock Generator

_______________________________________________________________________________________

5

Typical Operating Characteristics

(V

DD

= 3.3V, T

A

= +25

∞C, unless otherwise noted.)

SUPPLY CURRENT

vs. TEMPERATURE

MAX9489 toc01

TEMPERATURE (

∞C)

SUPPLY CURRENT (mA)

60

35

10

-15

110

120

130

140

150

160

100

-40

85

RISE AND FALL TIMES

vs. TEMPERATURE

MAX9489 toc02

TEMPERATURE (

∞C)

TRANSITION TIME (ns)

60

35

10

-15

1.2

1.4

1.7

1.9

2.3

2.1

1.0

-40

85

t

FALL

t

RISE

JITTER vs. TEMPERATURE

MAX9489 toc03

TEMPERATURE (

∞C)

RMS PERIOD JITTER (ps)

60

35

10

-15

10

20

30

40

50

60

70

0

-40

85

133MHz

25MHz

JITTER vs. FREQUENCY

MAX9489 toc04

FREQUENCY (MHz)

RMS PERIOD JITTER (ps)

115

97

79

61

43

15

30

45

60

75

0

25

133

TYPICAL CLOCK WAVEFORMS

MAX9489 toc05

10ns/div

A

B

A: 100MHz, 100mV/div

B: 25MHz, 100mV/div