| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: CX29503 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

500238B

Mindspeed TechnologiesTM

November

Advance Information

2002

Advance Information

This document contains information on a product under development. The parametric information

contains target parameters that are subject to change.

CX29503

Broadband Access Multiplexer (BAM)

The CX29503 Broadband Access Multiplexer (BAM) is a highly integrated, cost-effective,

monolithic device which performs the mapping, multiplexing, demultiplexing, and framing

of three STS-1, AU-3, DS3, E3, or one AU-4 inputs to any valid combination of 84 DS1 or

63 E1 signals. The CX29503 may be used as a SONET/SDH-to-PDH mapper supporting all

standard mappings at 51 Mbps, 2 Mbps, and 1.5 Mbps rates, or it may be used as a PDH

muldem only. It generates and terminates all Virtual Tributary (VT) and Virtual Container

(VC) path overhead. It includes three embedded DS3/E3 framers, three M13/E13

MUX/DEMUX blocks with G.747 support, and 84 embedded DS1 framers and 63

embedded E1 framers. Other features include standards-compliant alarm indicators,

status monitoring and error counters for all supported tributaries, and an embedded

Command and Status Processor (CSP) that offloads major network maintenance activities

from the host processor.

The CX29503, in conjunction with Mindspeed's 1,024-channel HDLC Controller device

(CX28500) and the STS-12/STM-4 SONET/SDH Framer/Multiplexer device (CX29610),

allows equipment suppliers to develop single, high-density, software-configurable system

solutions for datacom and IP path terminating applications supporting both North

American and European transmission standards. The high level of integration drives down

per-port framer cost and dramatically reduces board space requirements. A complete

STS-12/STM-4 system channelized down to DS1/E1 for an IP HDLC packet processing

solution requires only seven devices from Mindspeed.

The CX29503 supports current ANSI, ETSI, ITU, and Telcordia standards with embedded,

enhanced network alarming and maintenance features that reduce real-time requirements

on the host processor. Physical layer support is provided for alarm generation and

detection, error monitoring, and data link maintenance.

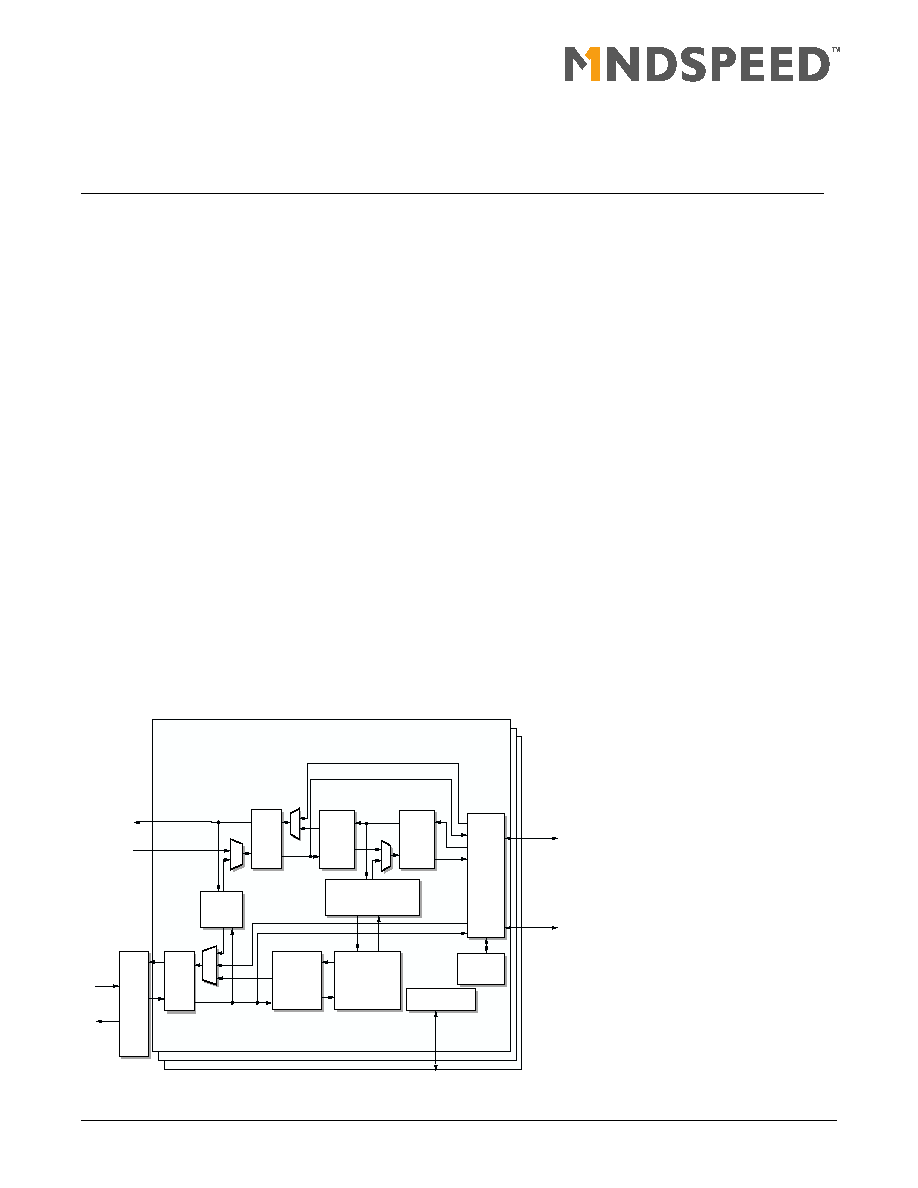

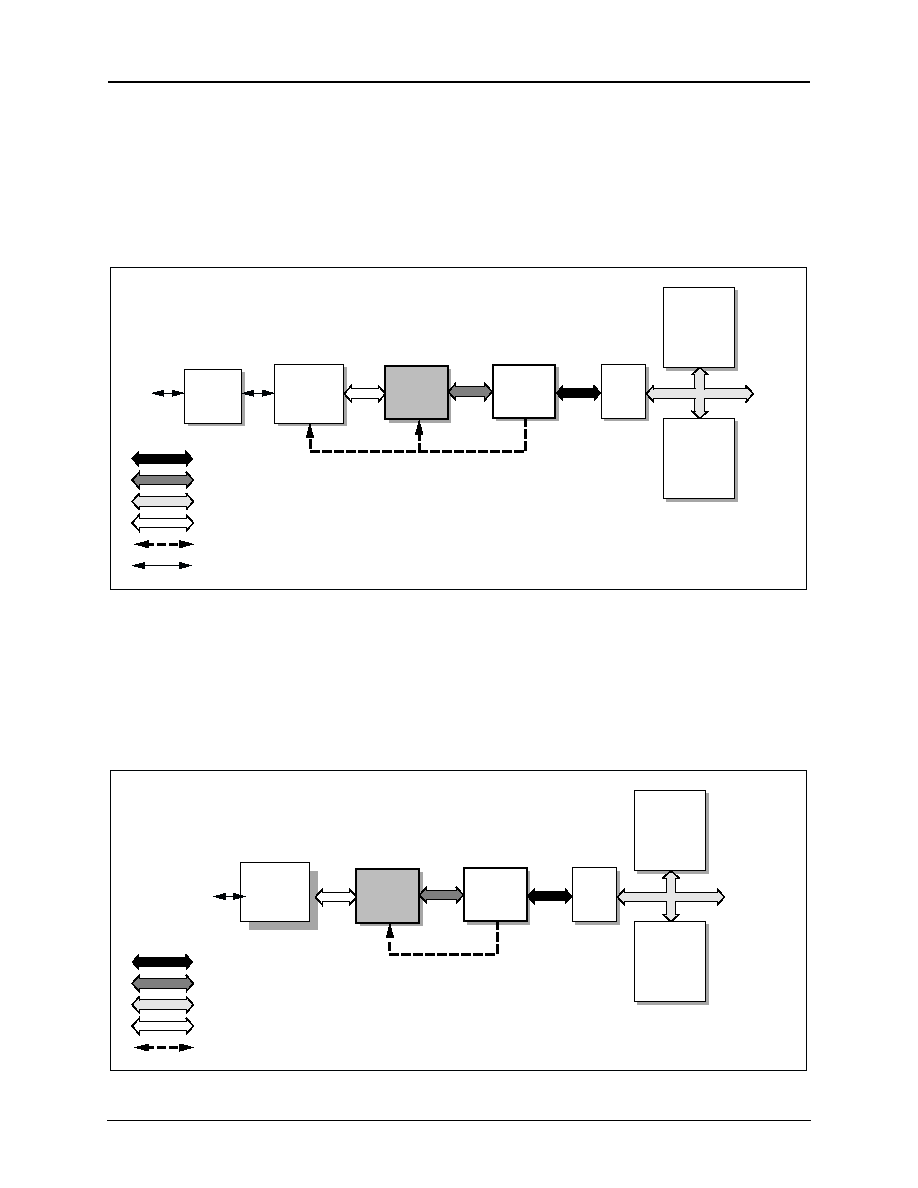

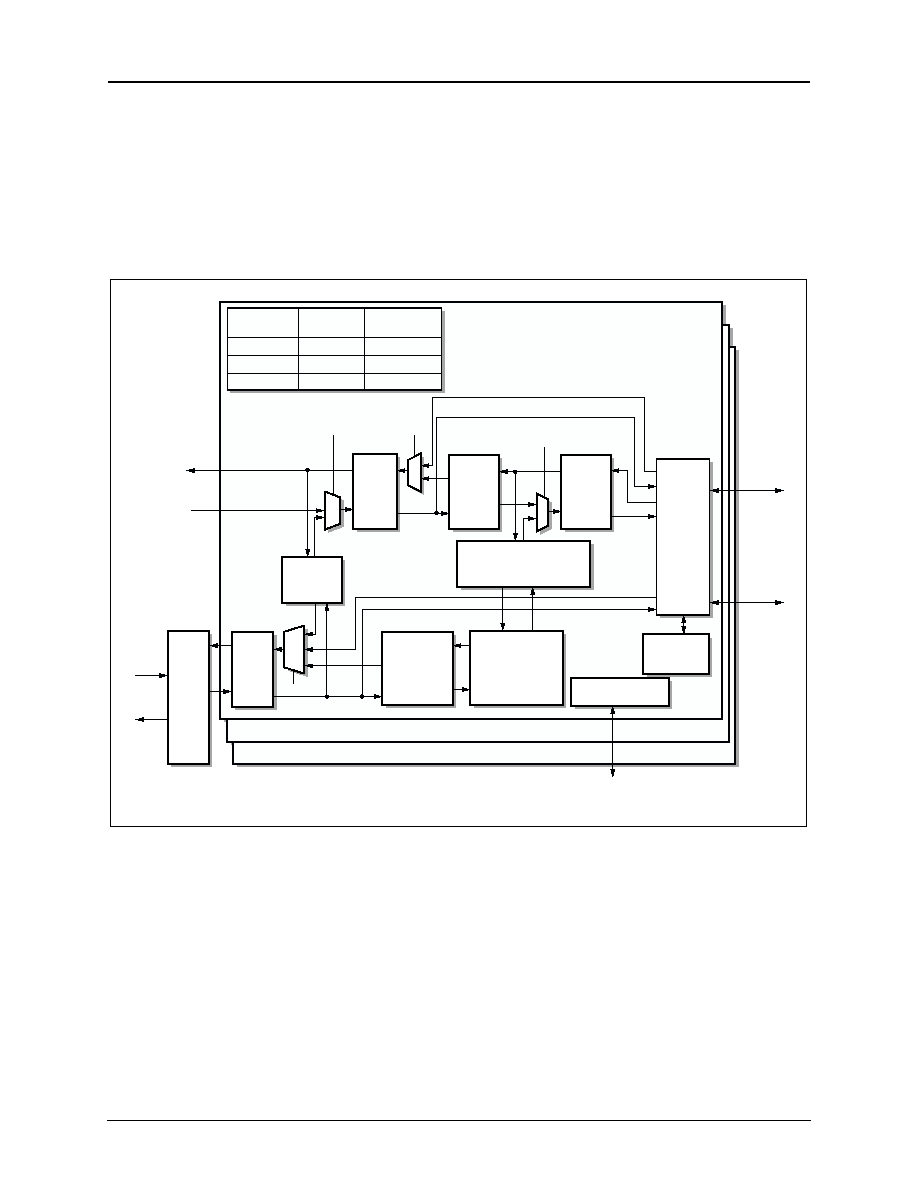

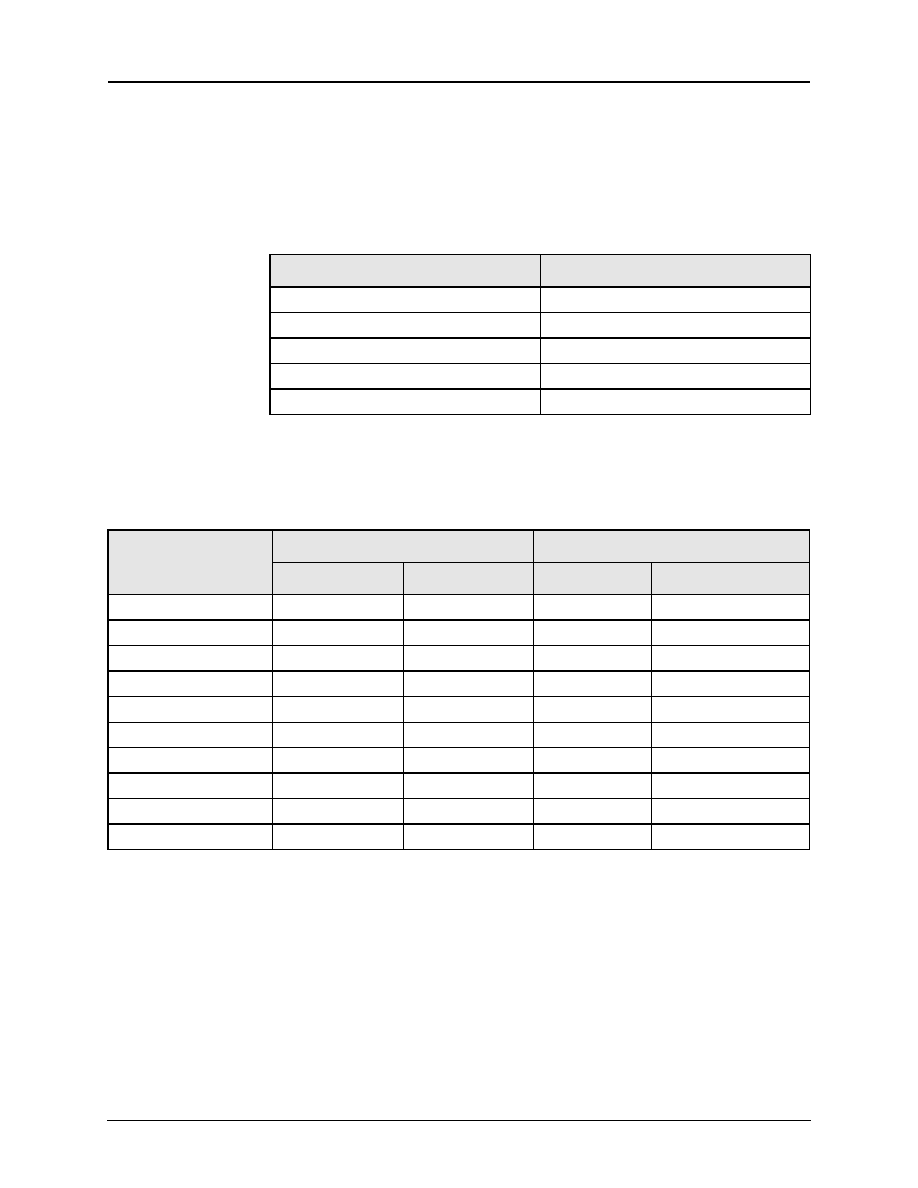

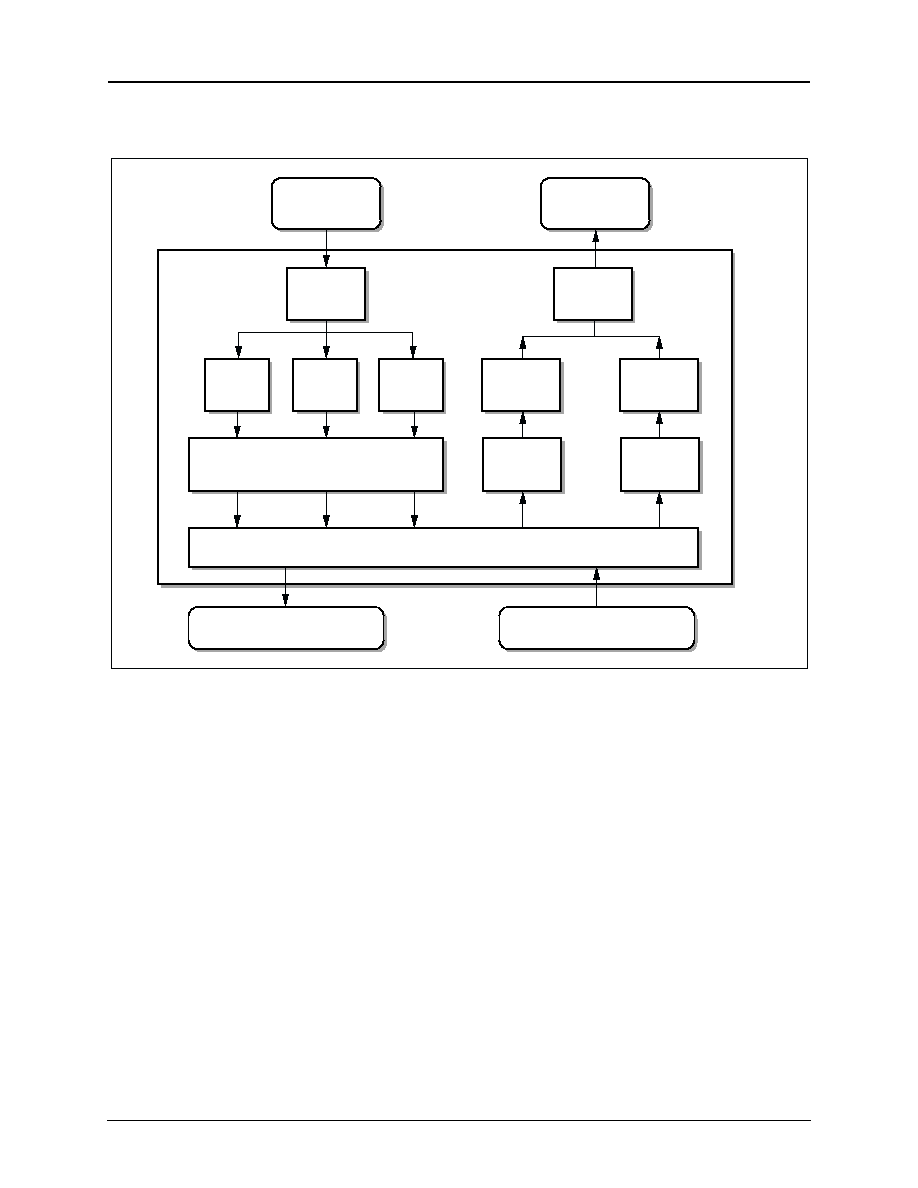

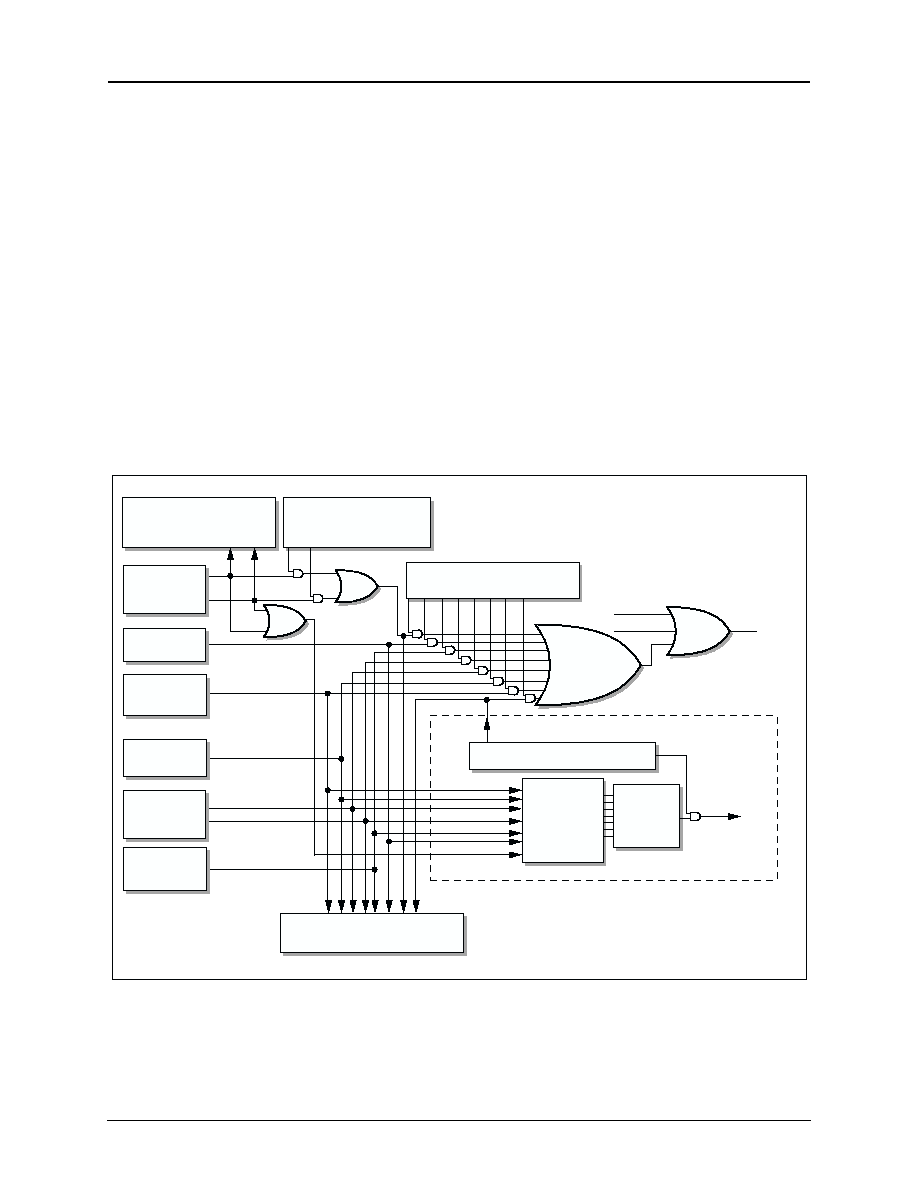

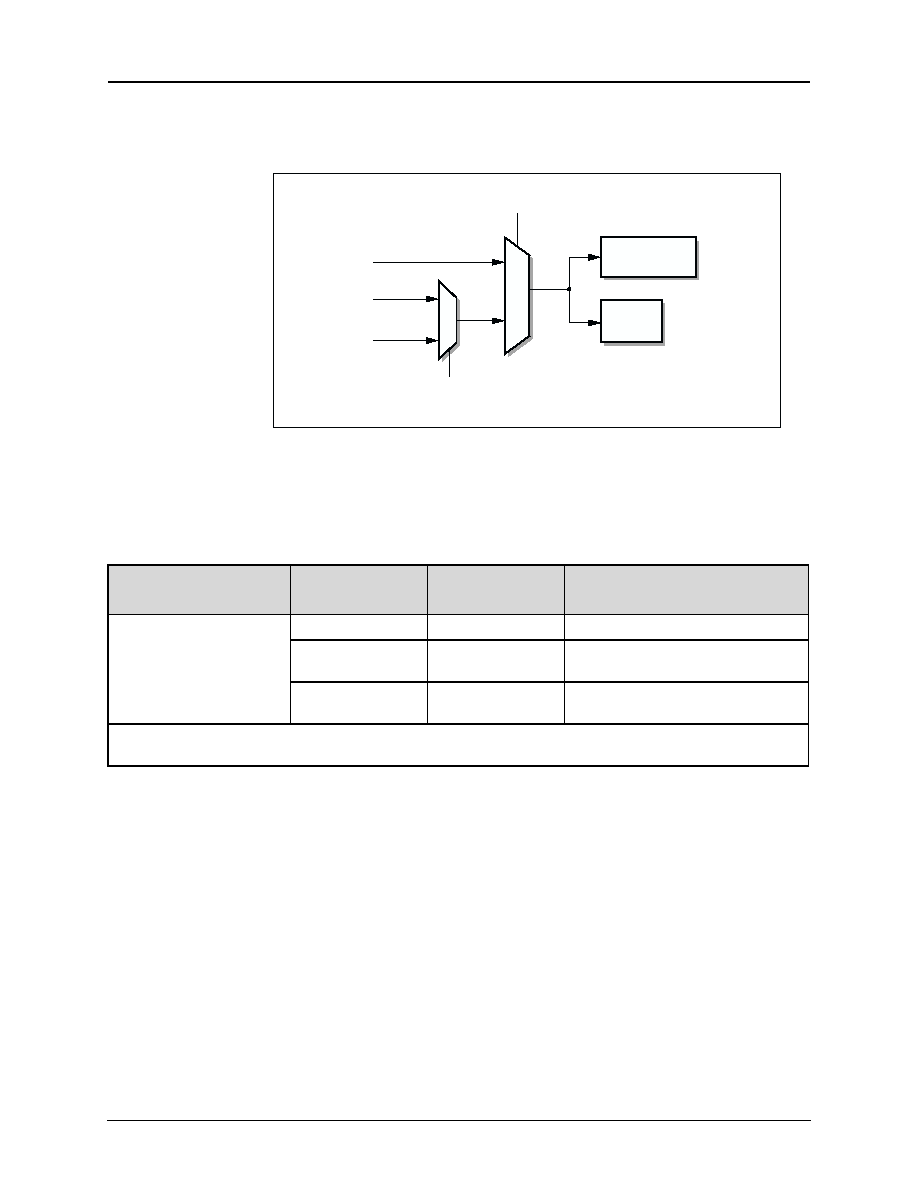

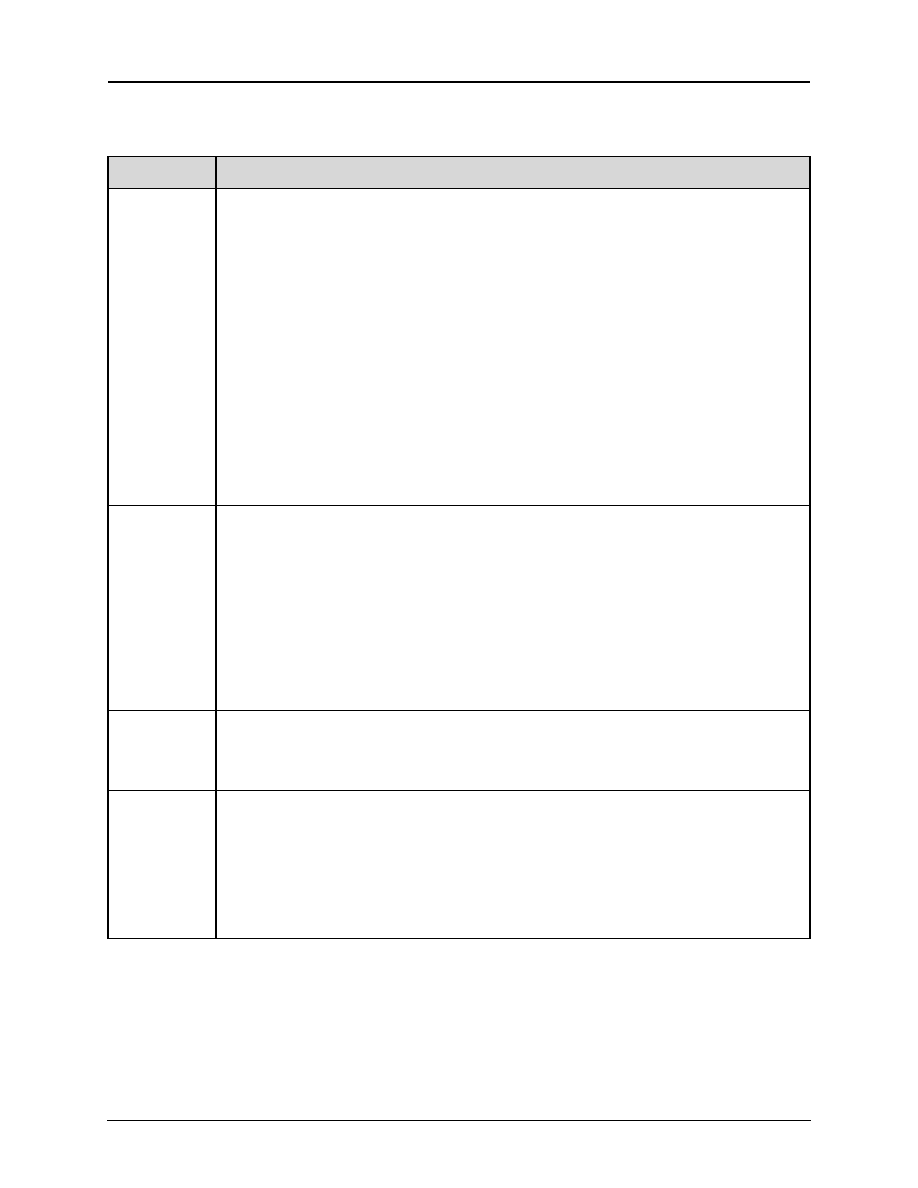

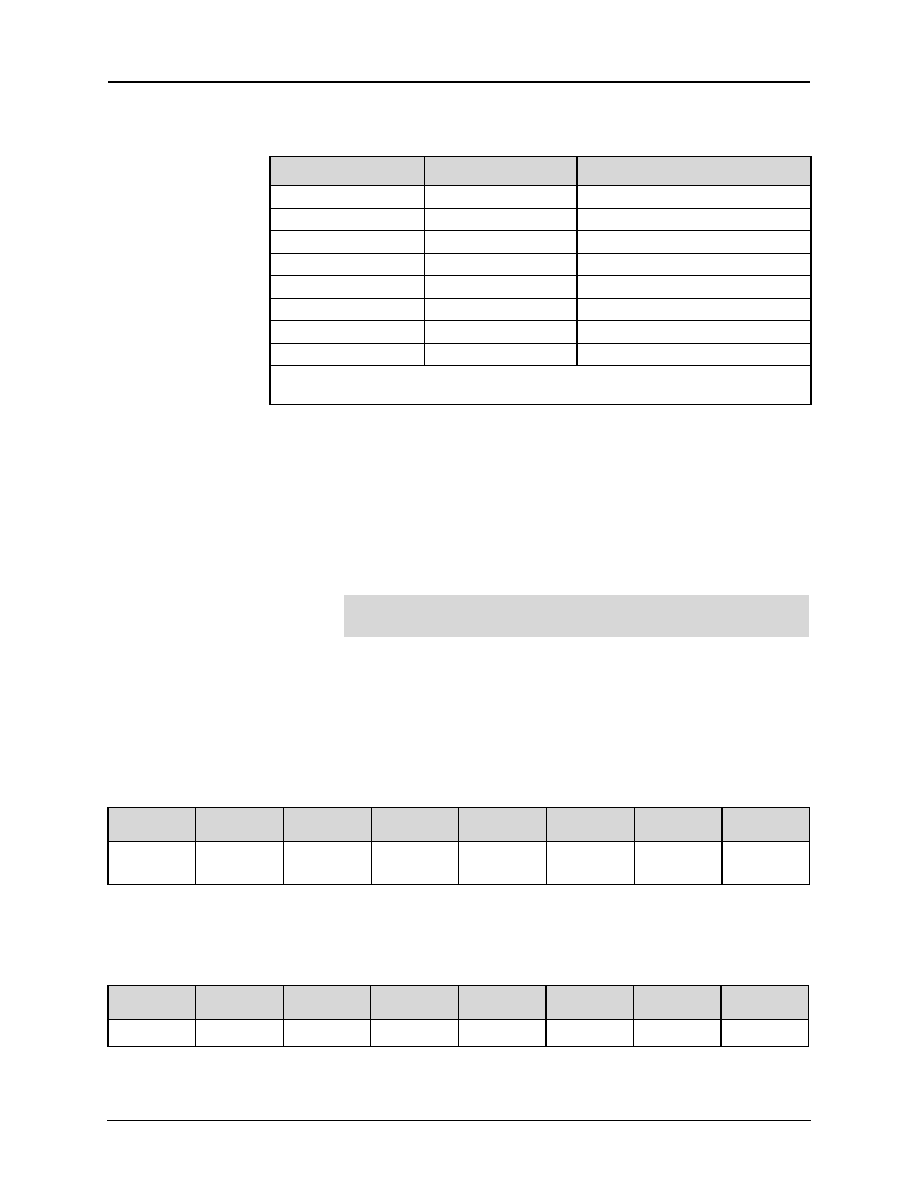

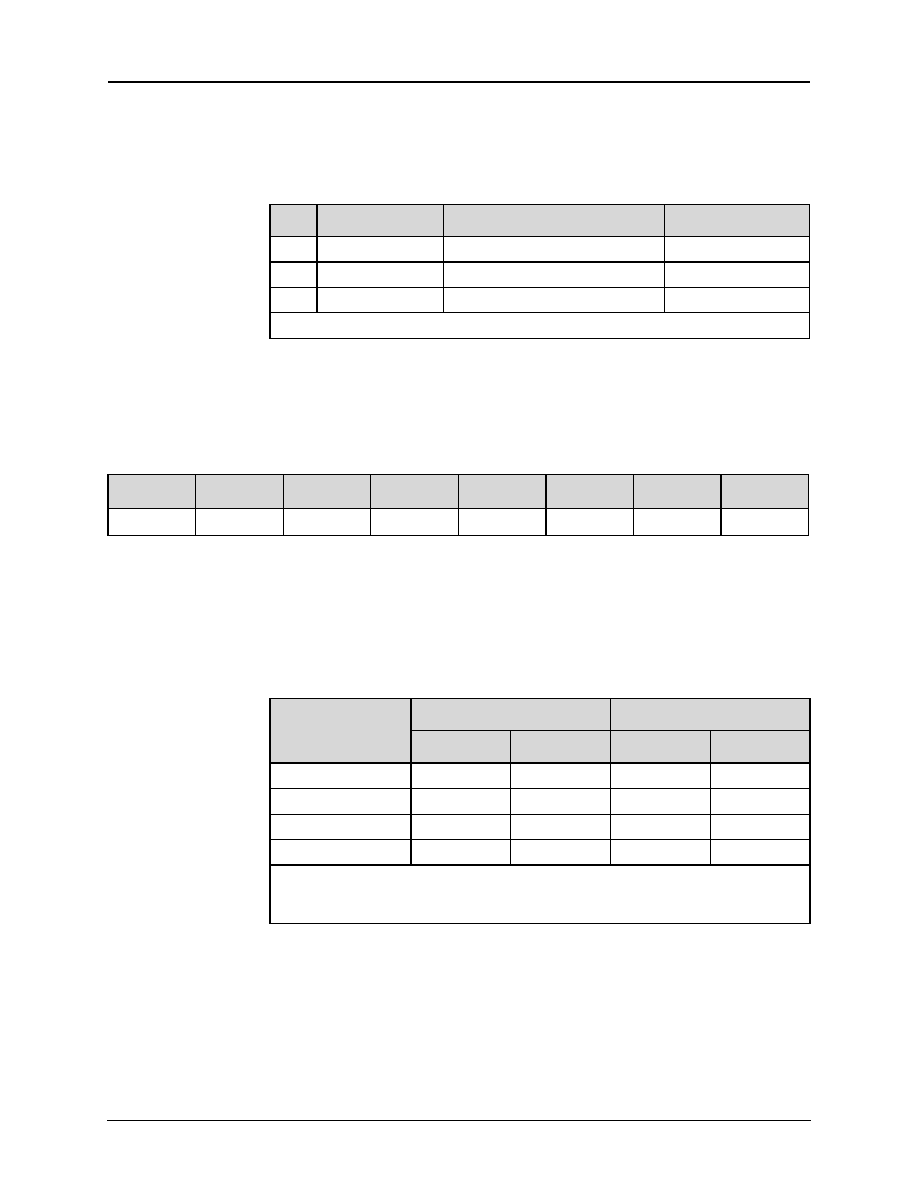

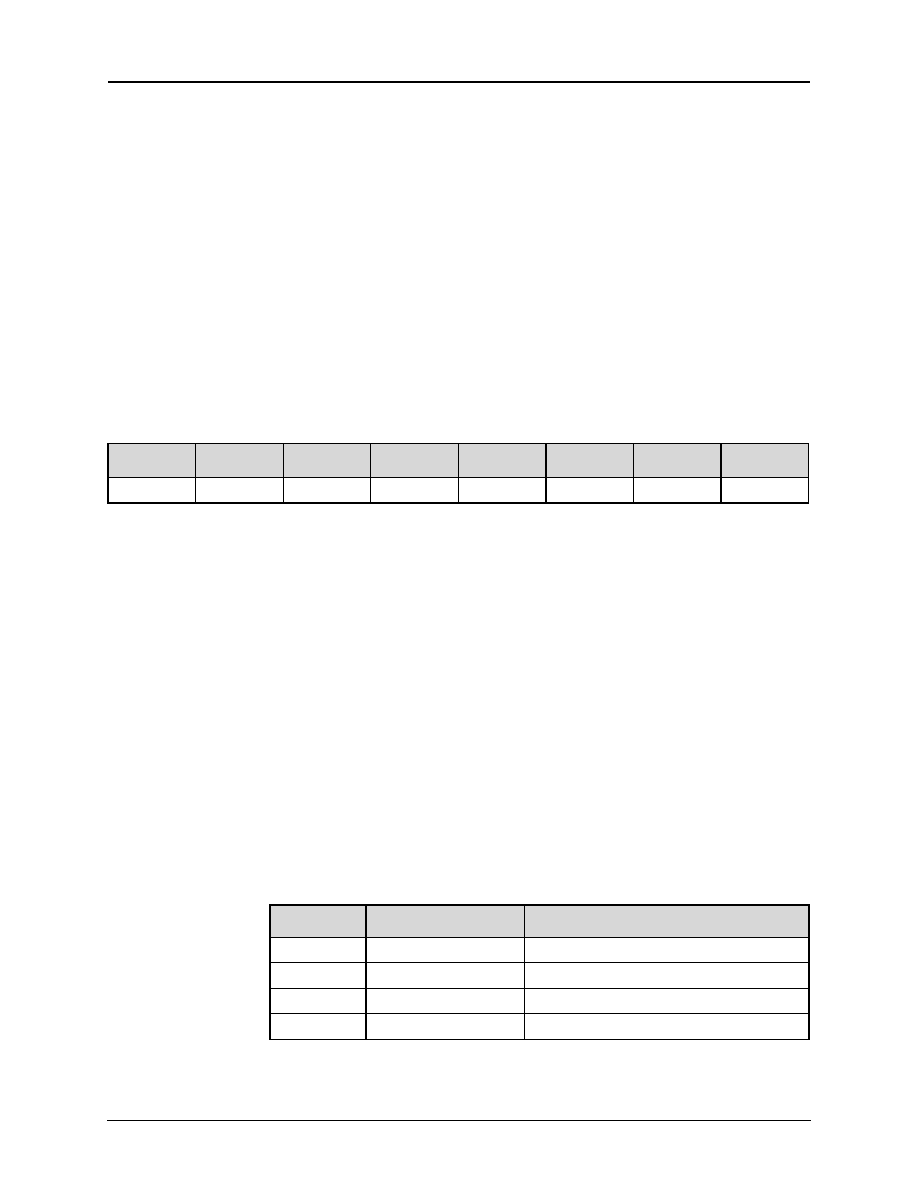

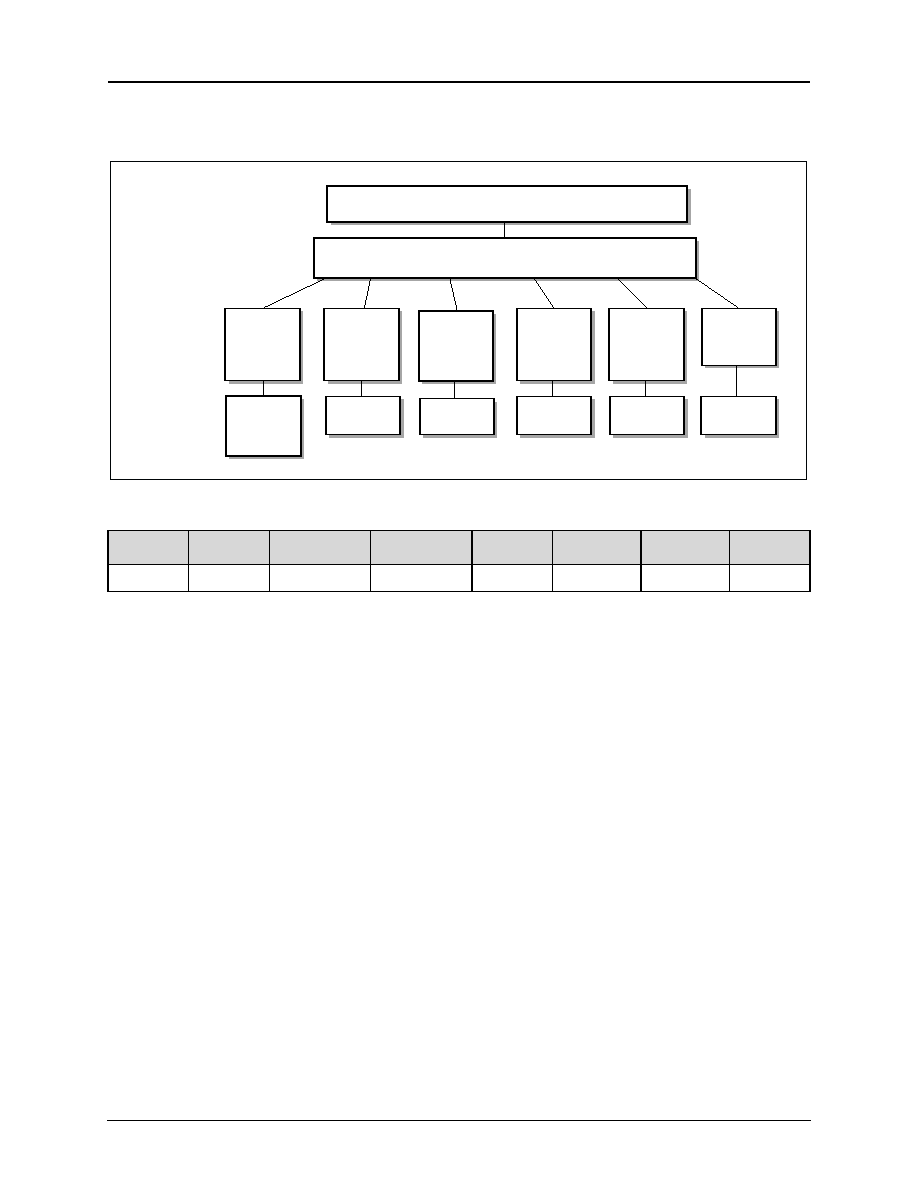

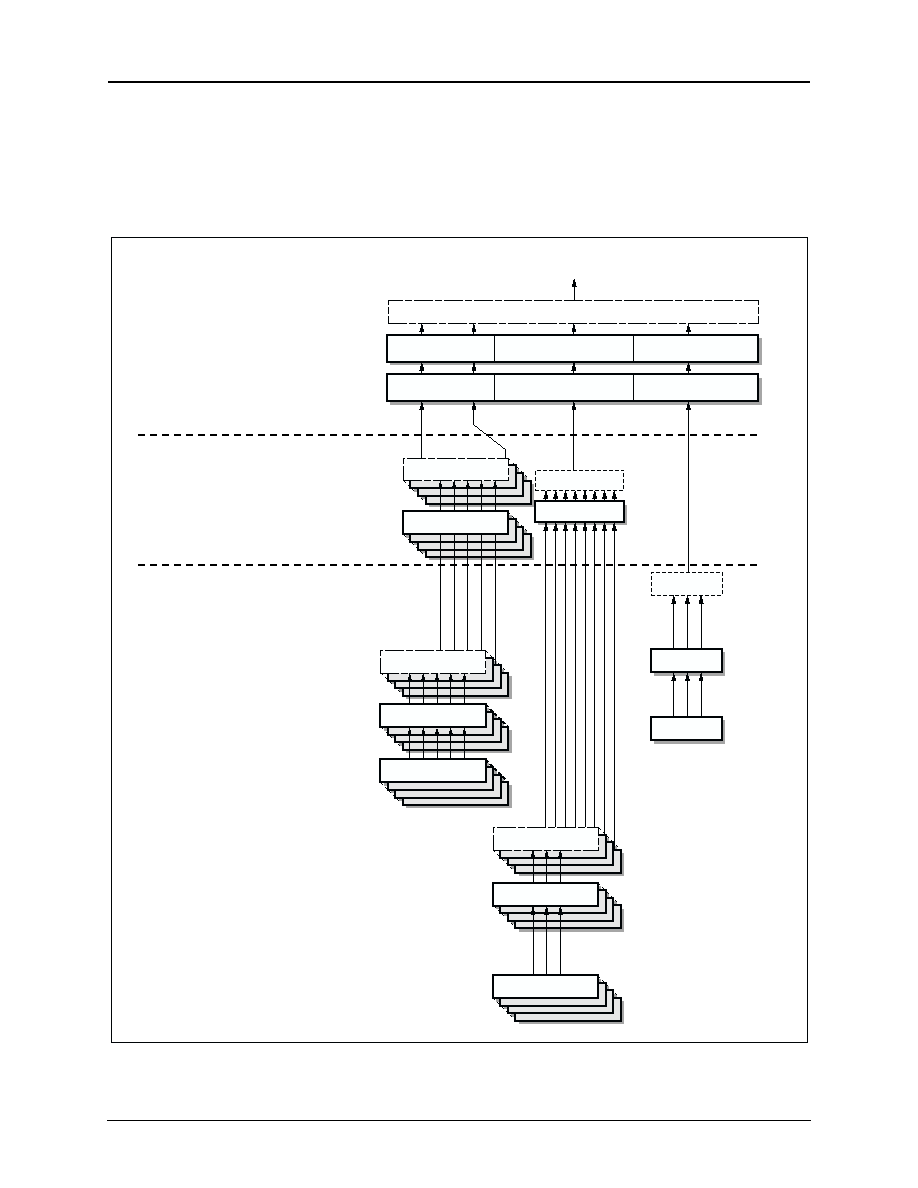

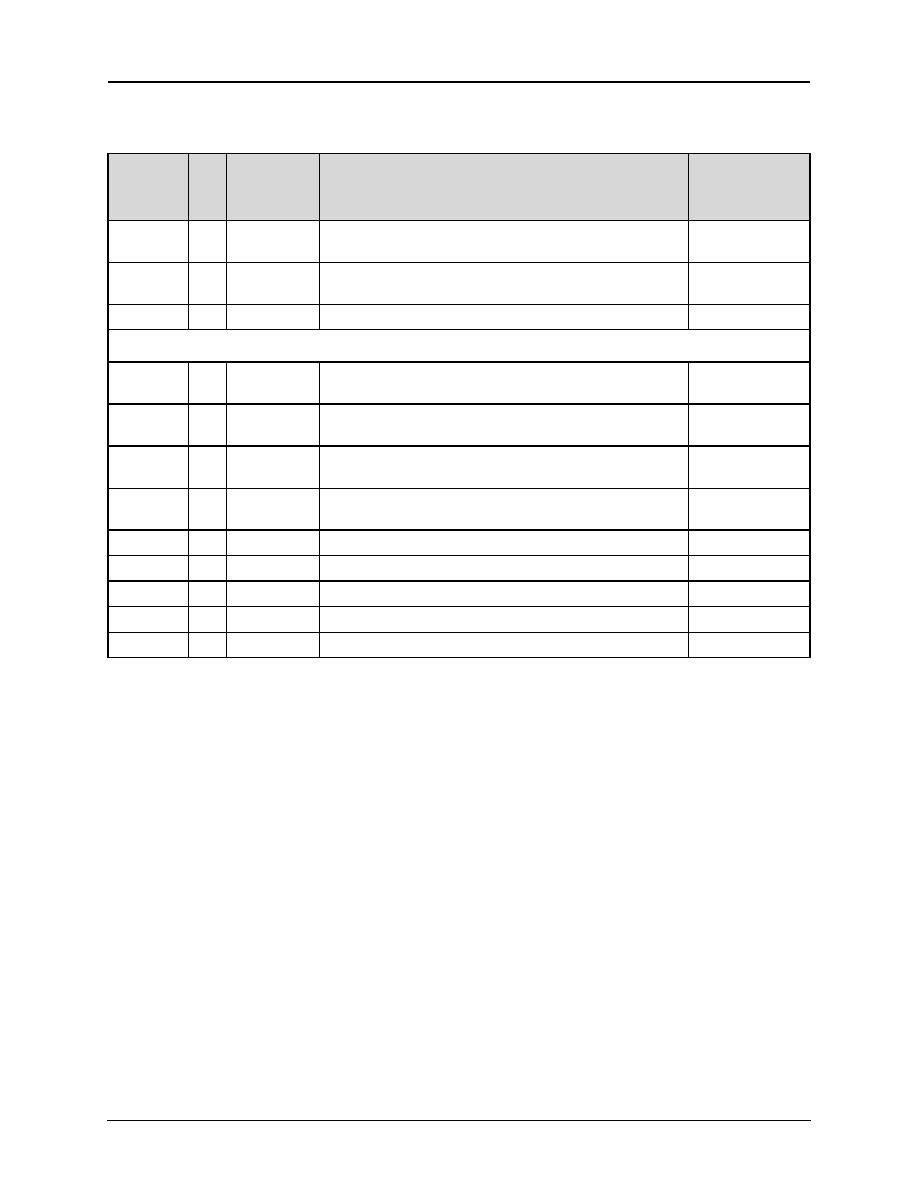

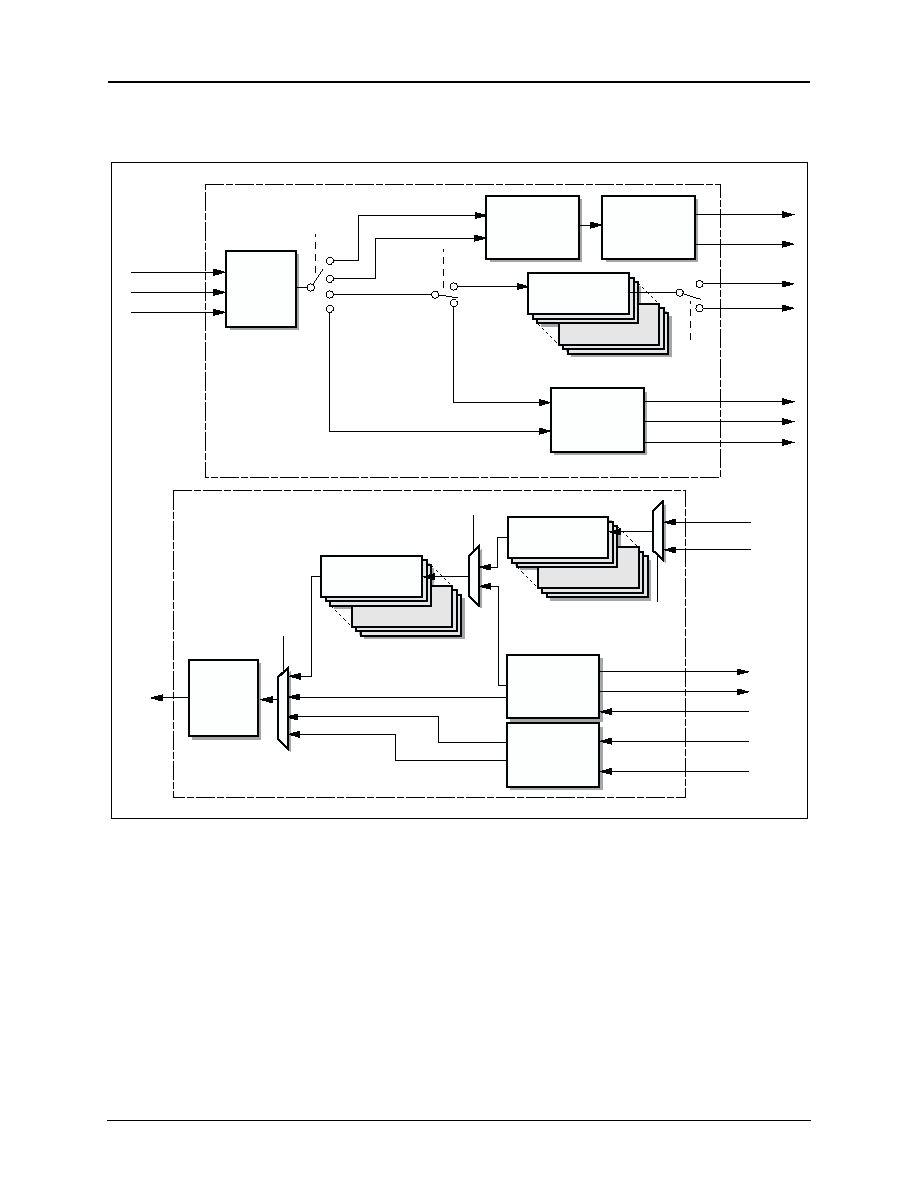

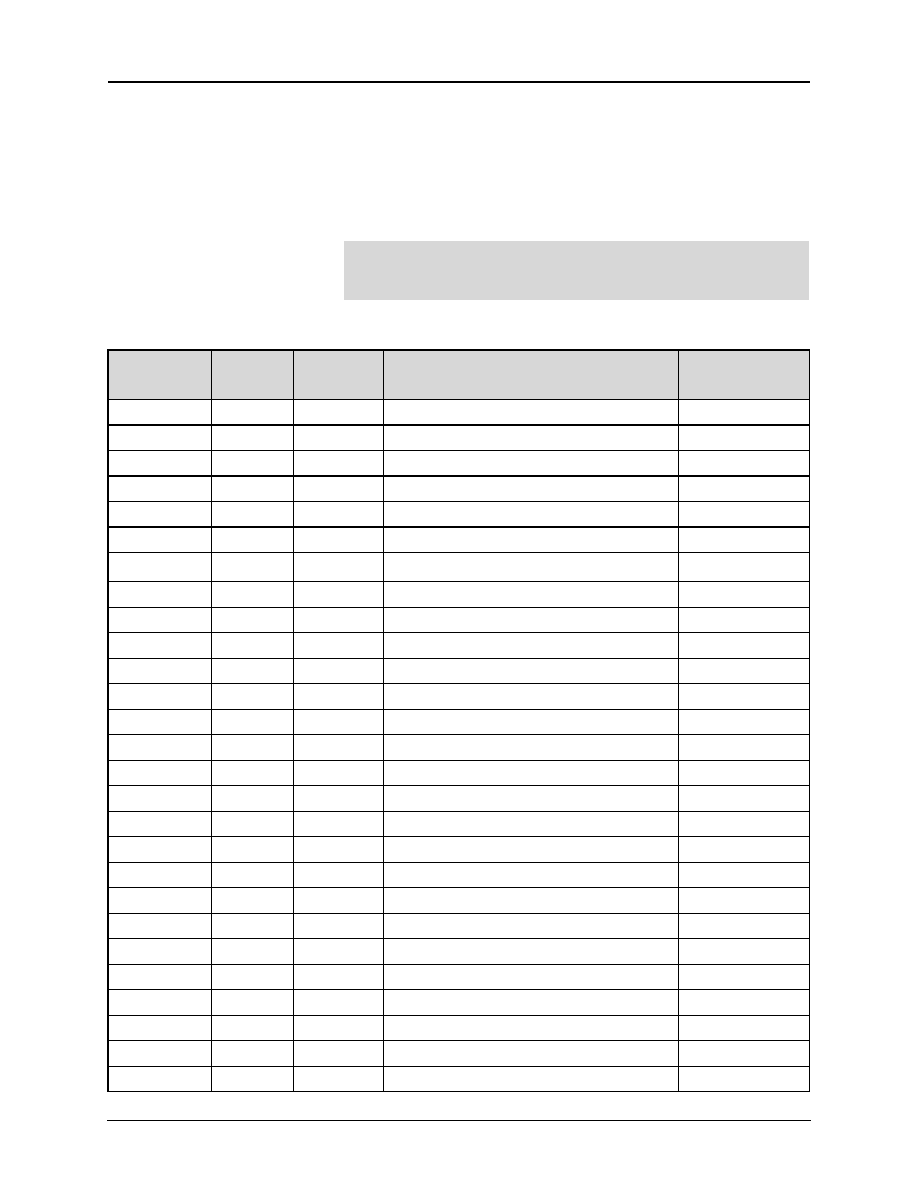

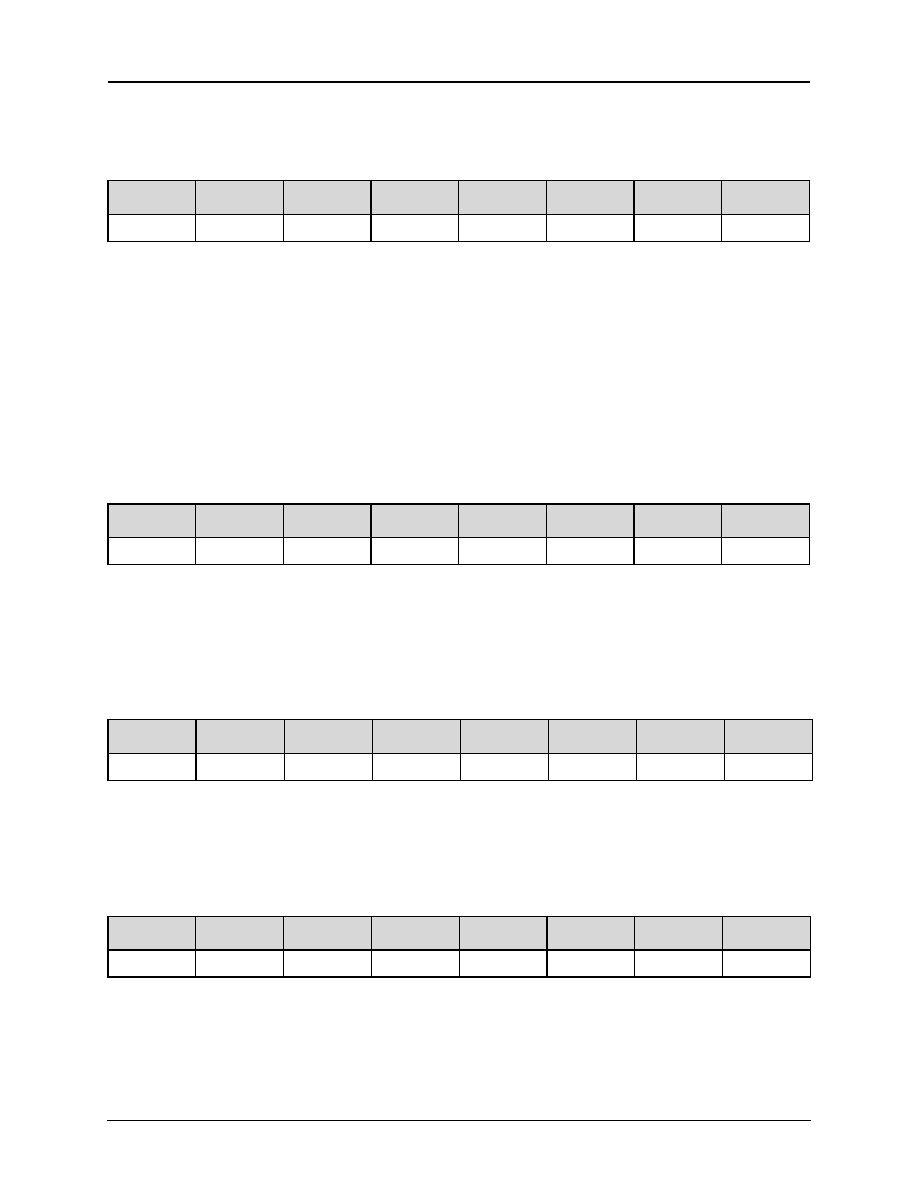

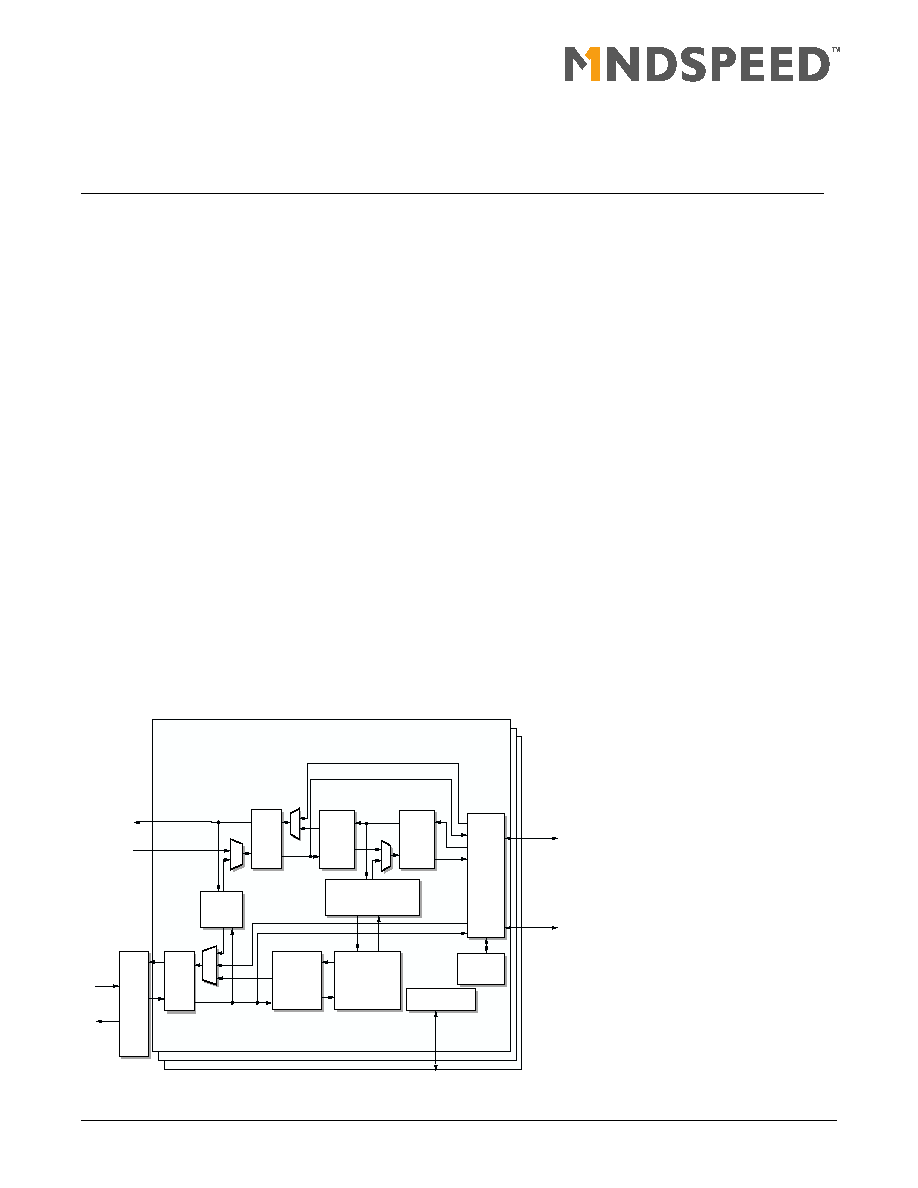

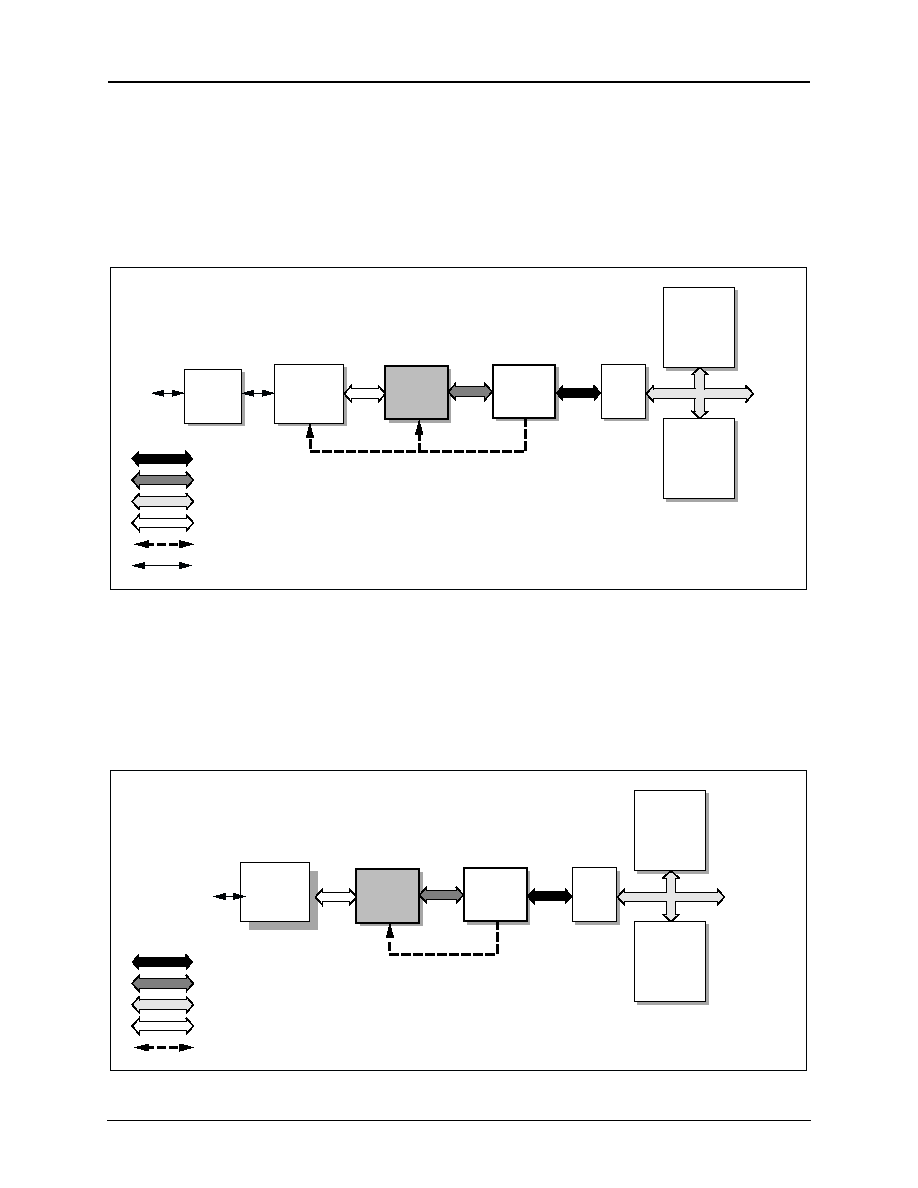

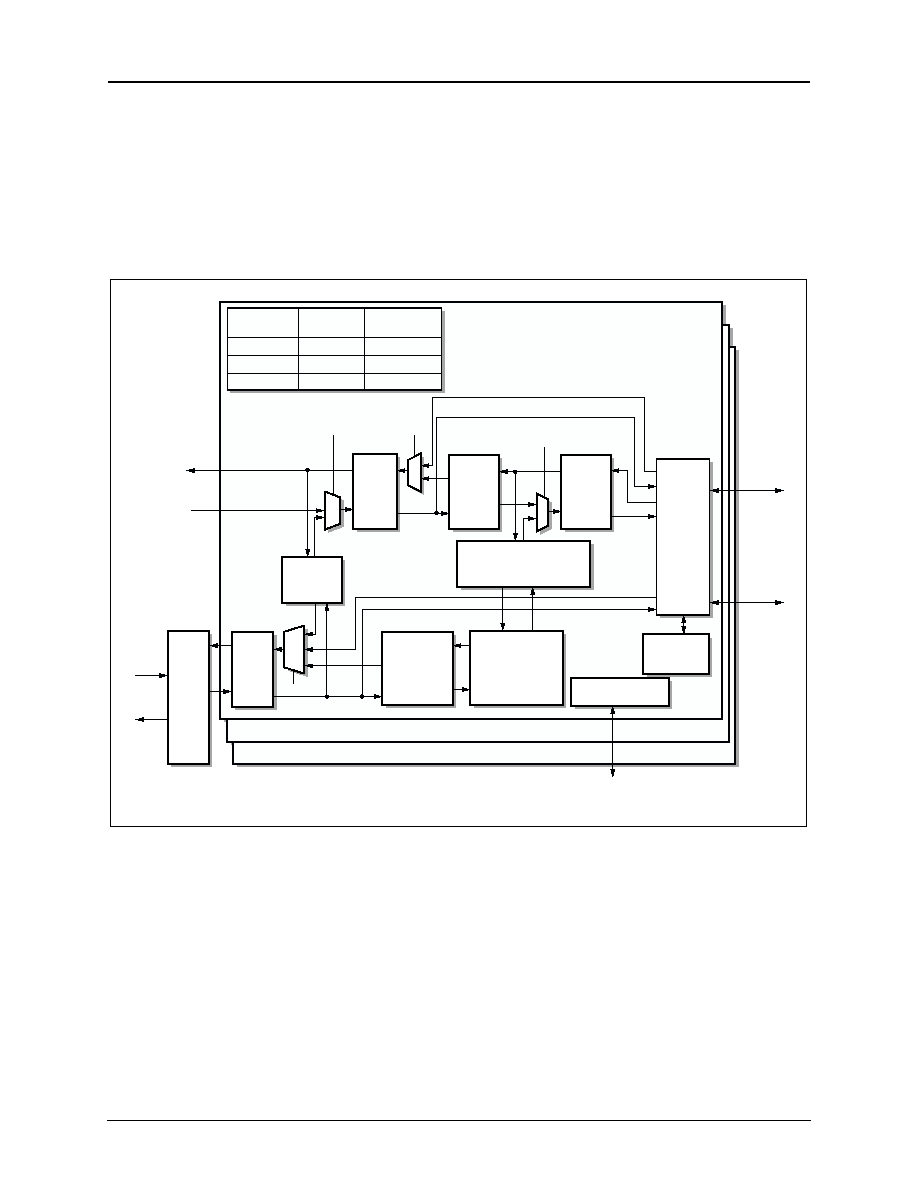

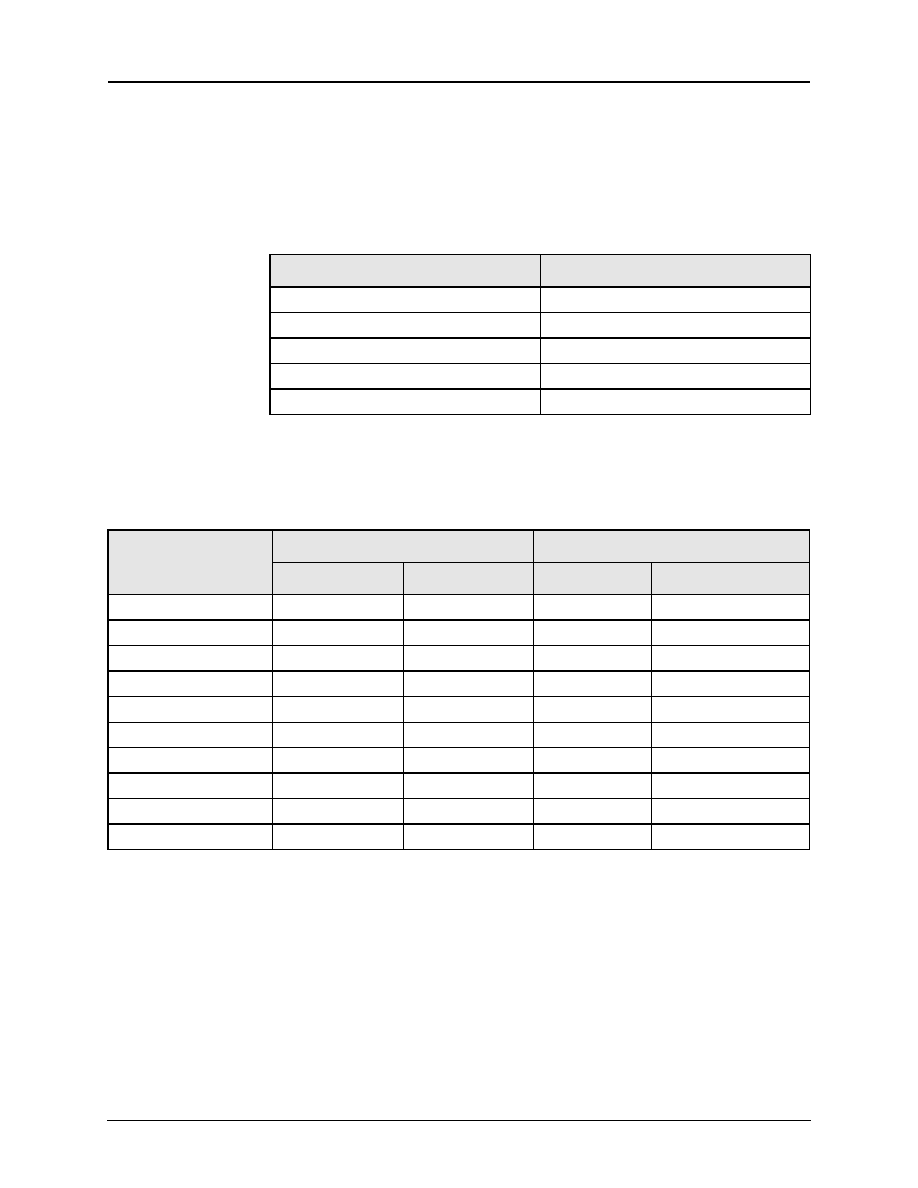

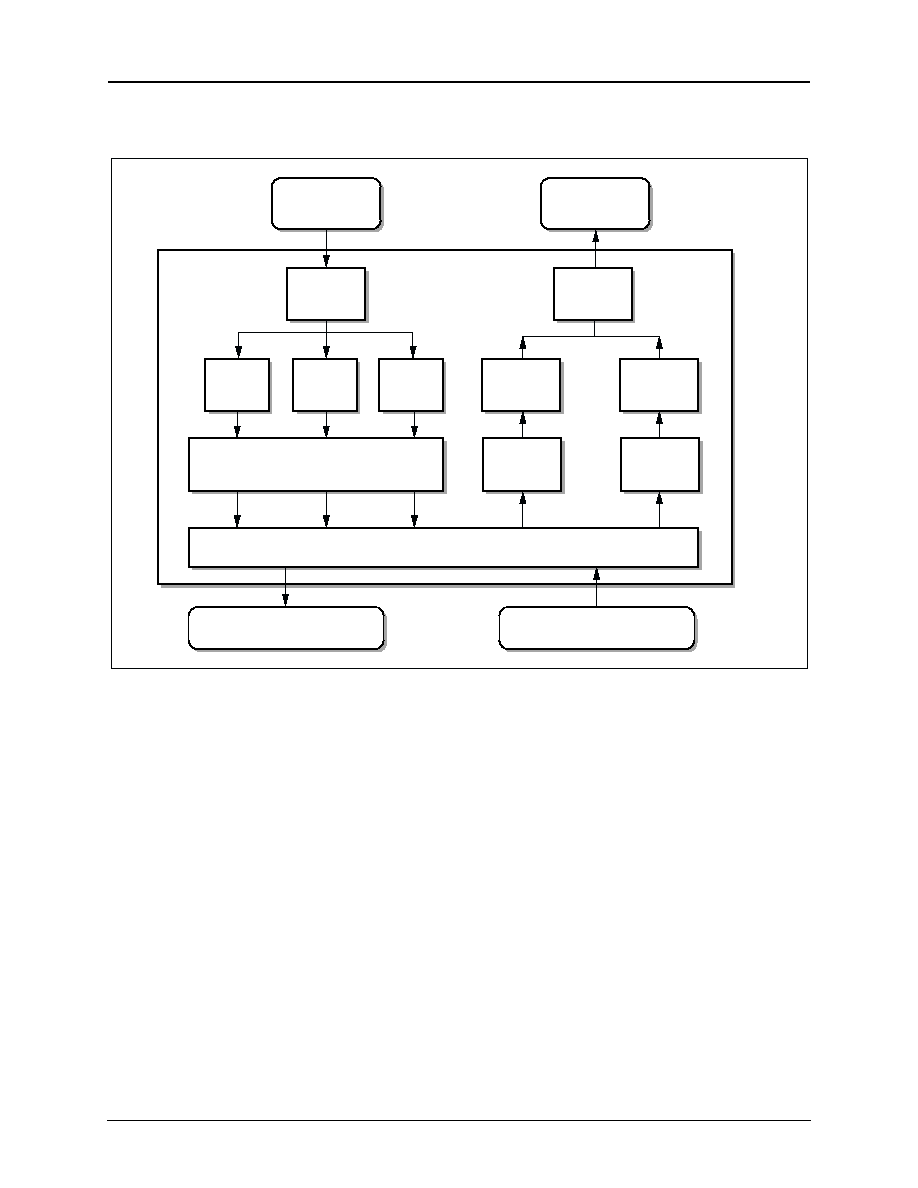

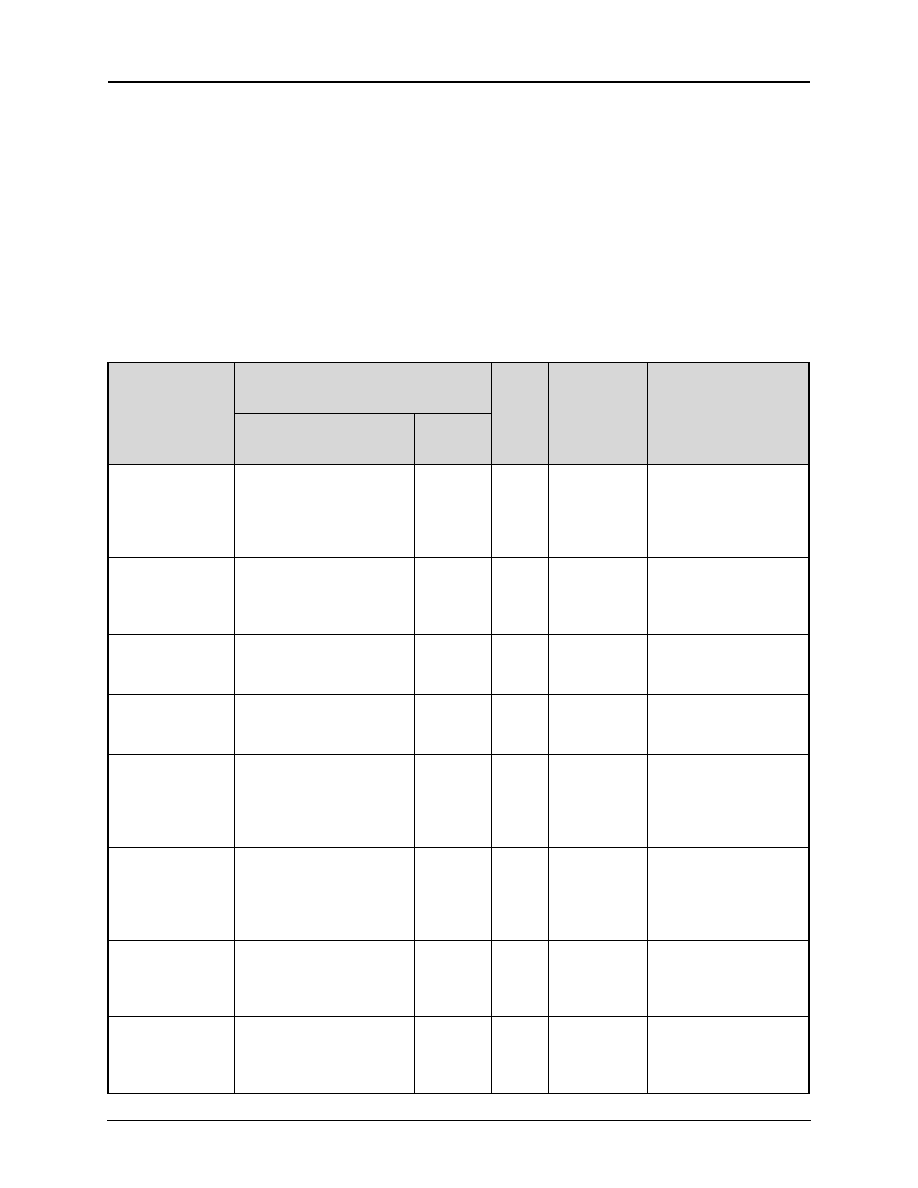

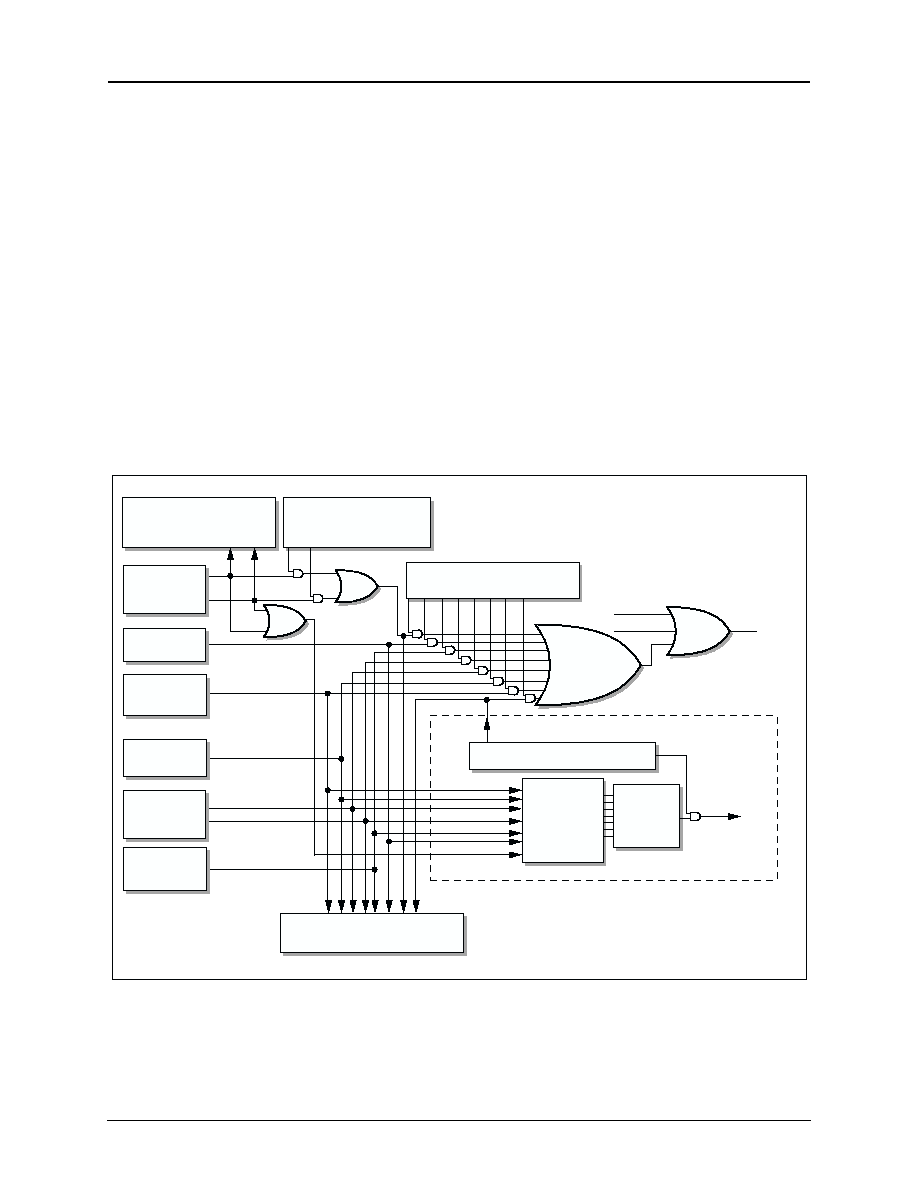

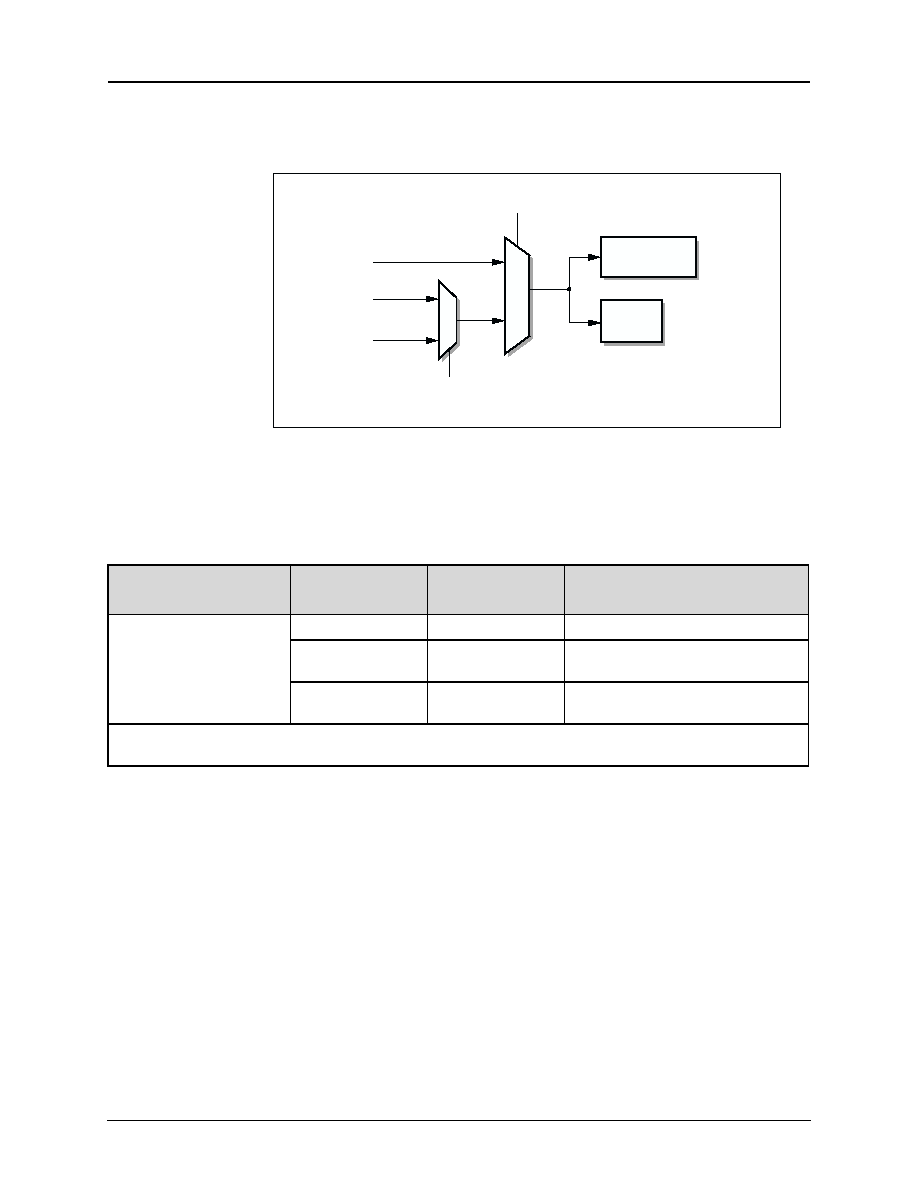

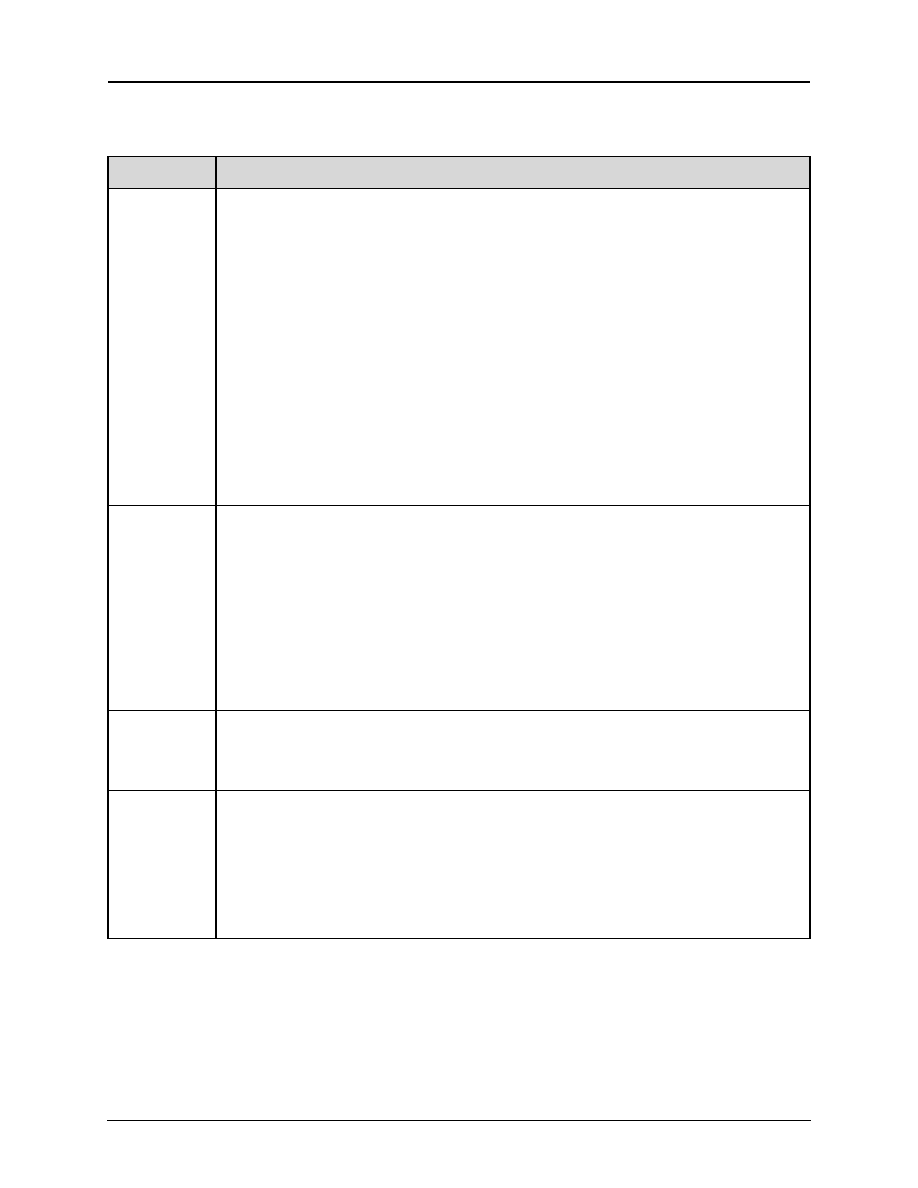

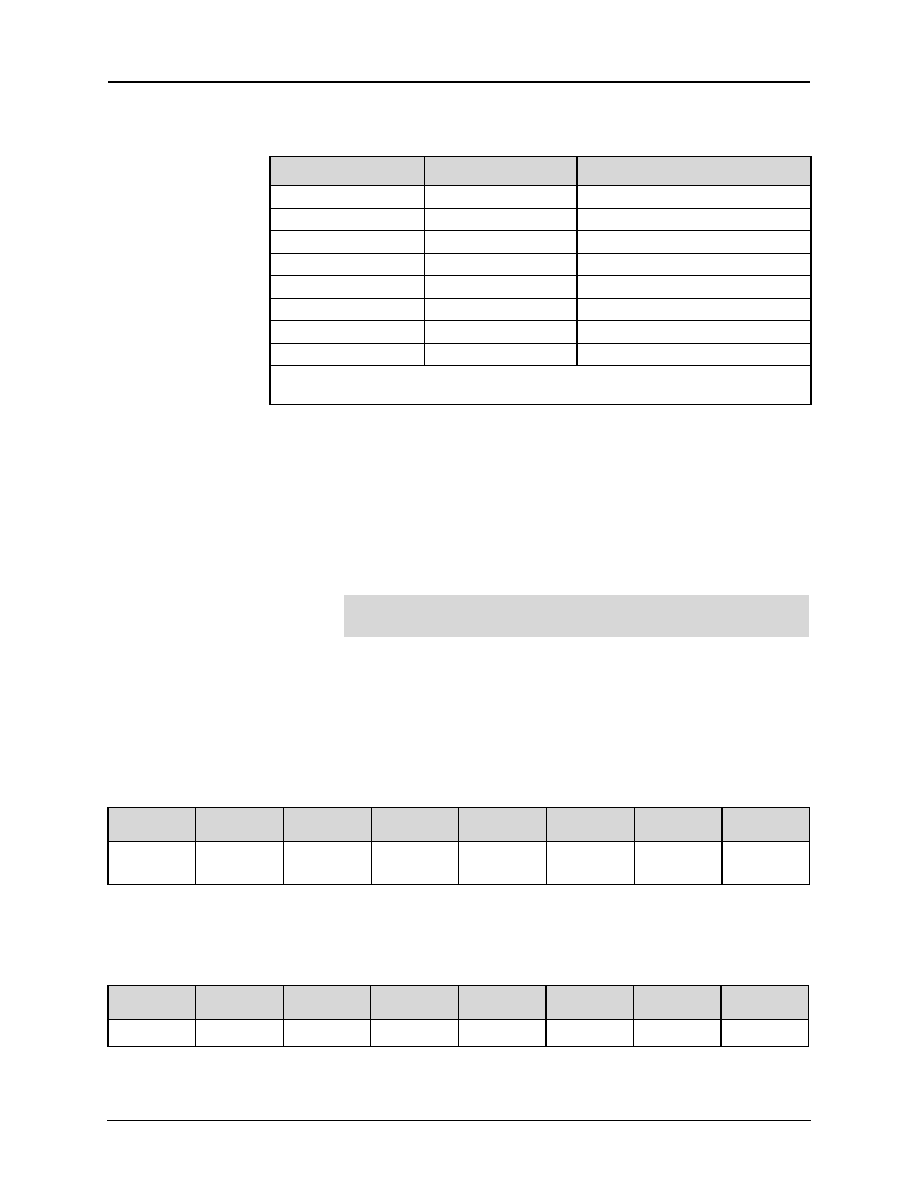

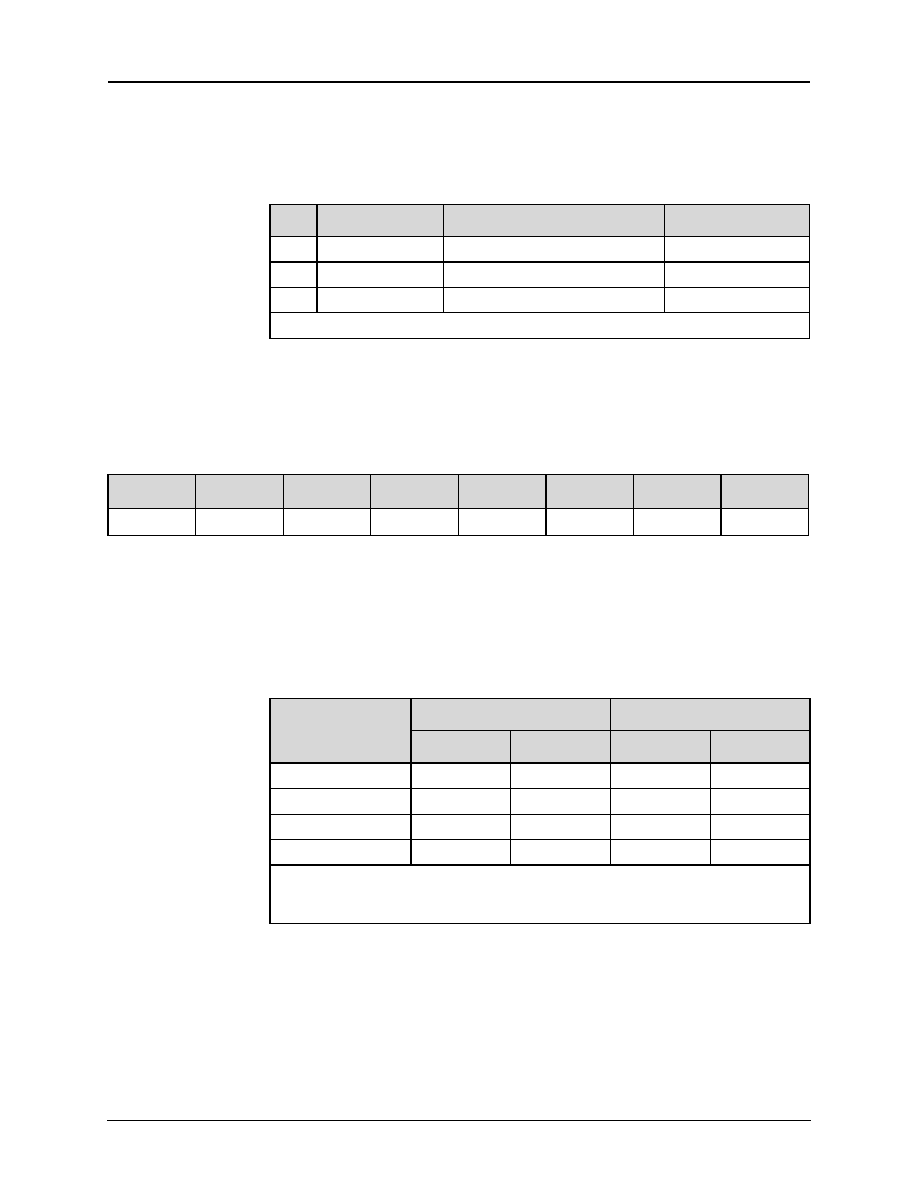

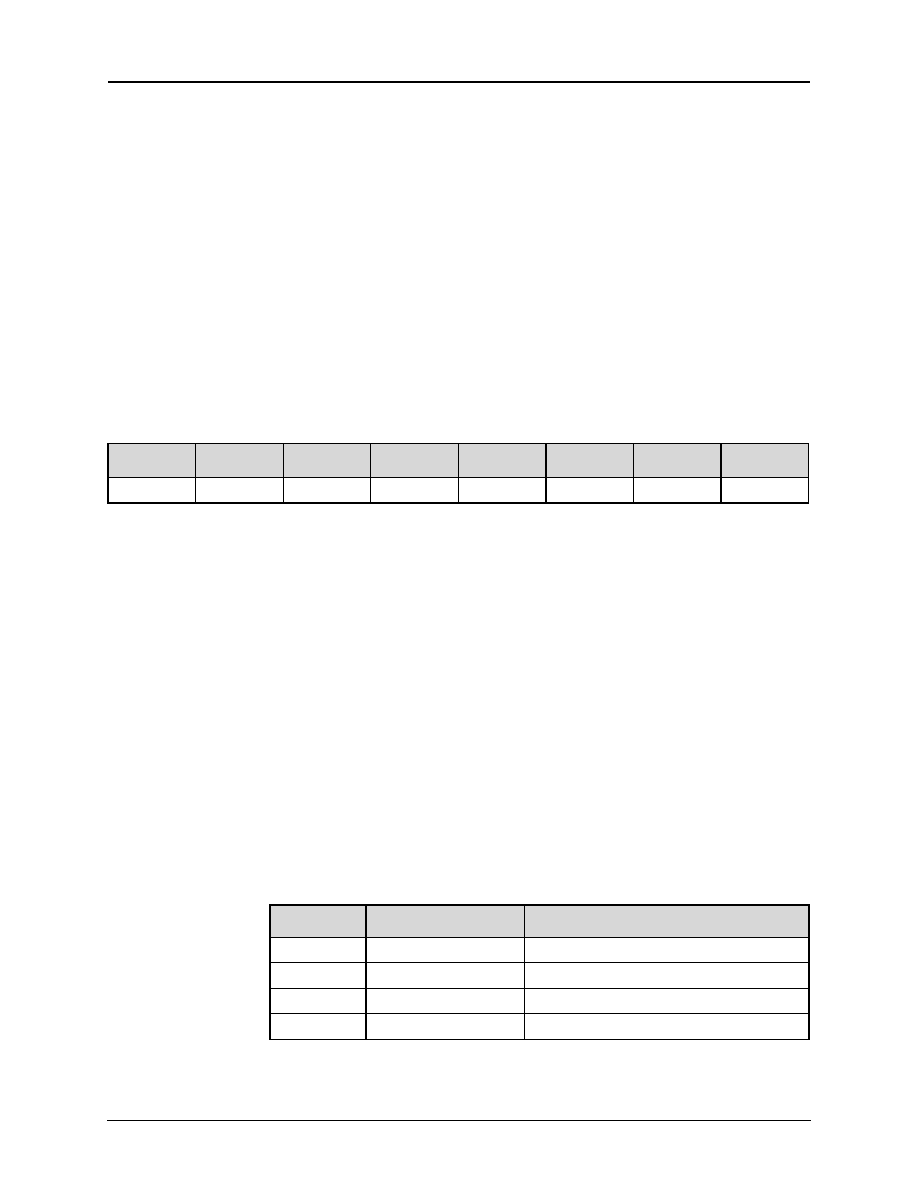

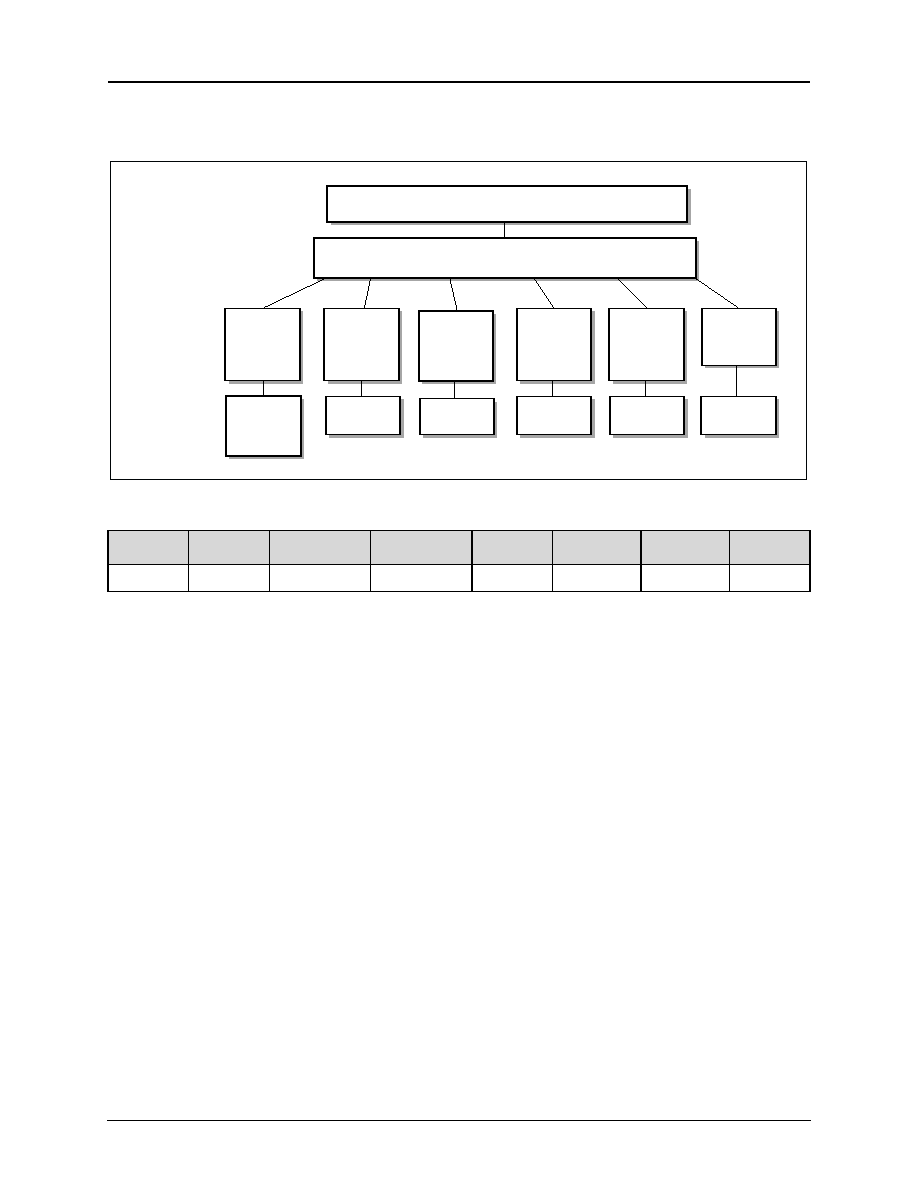

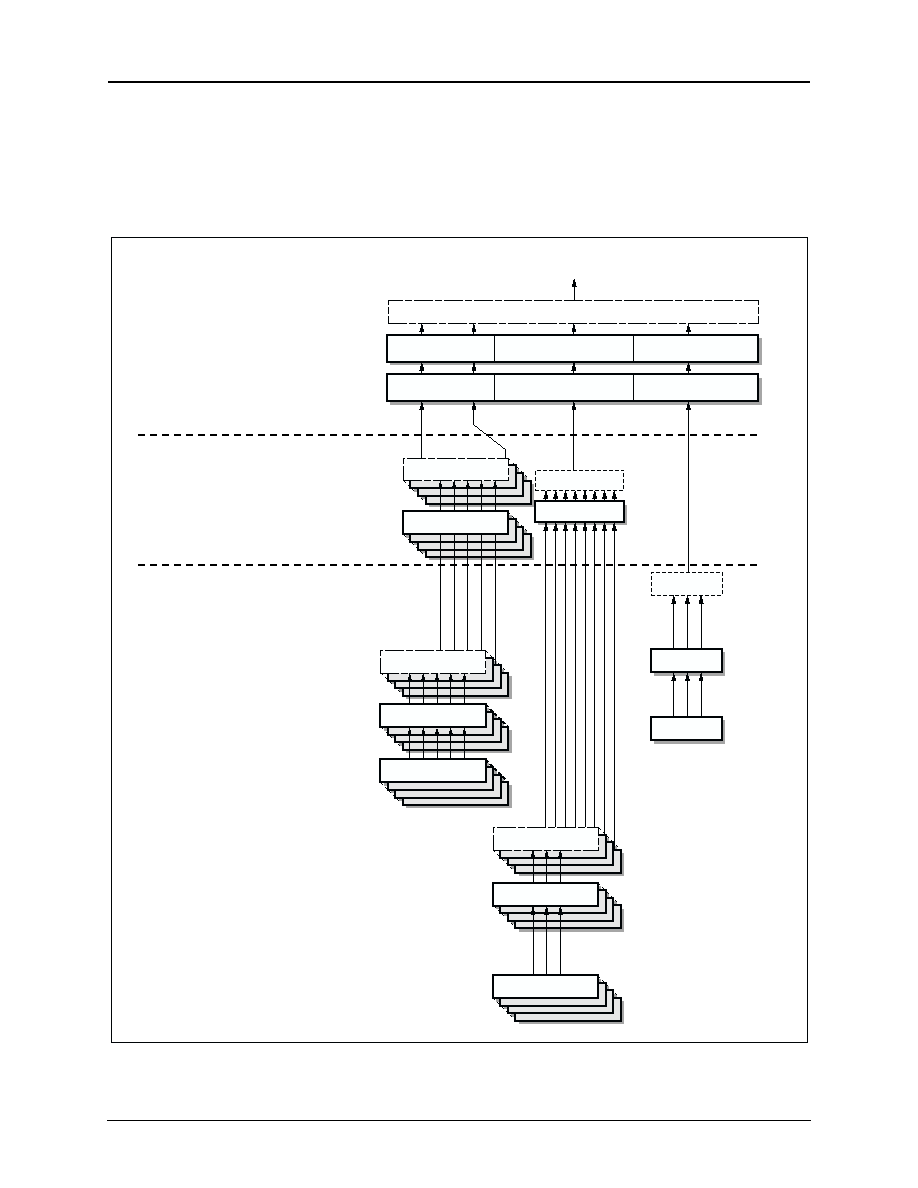

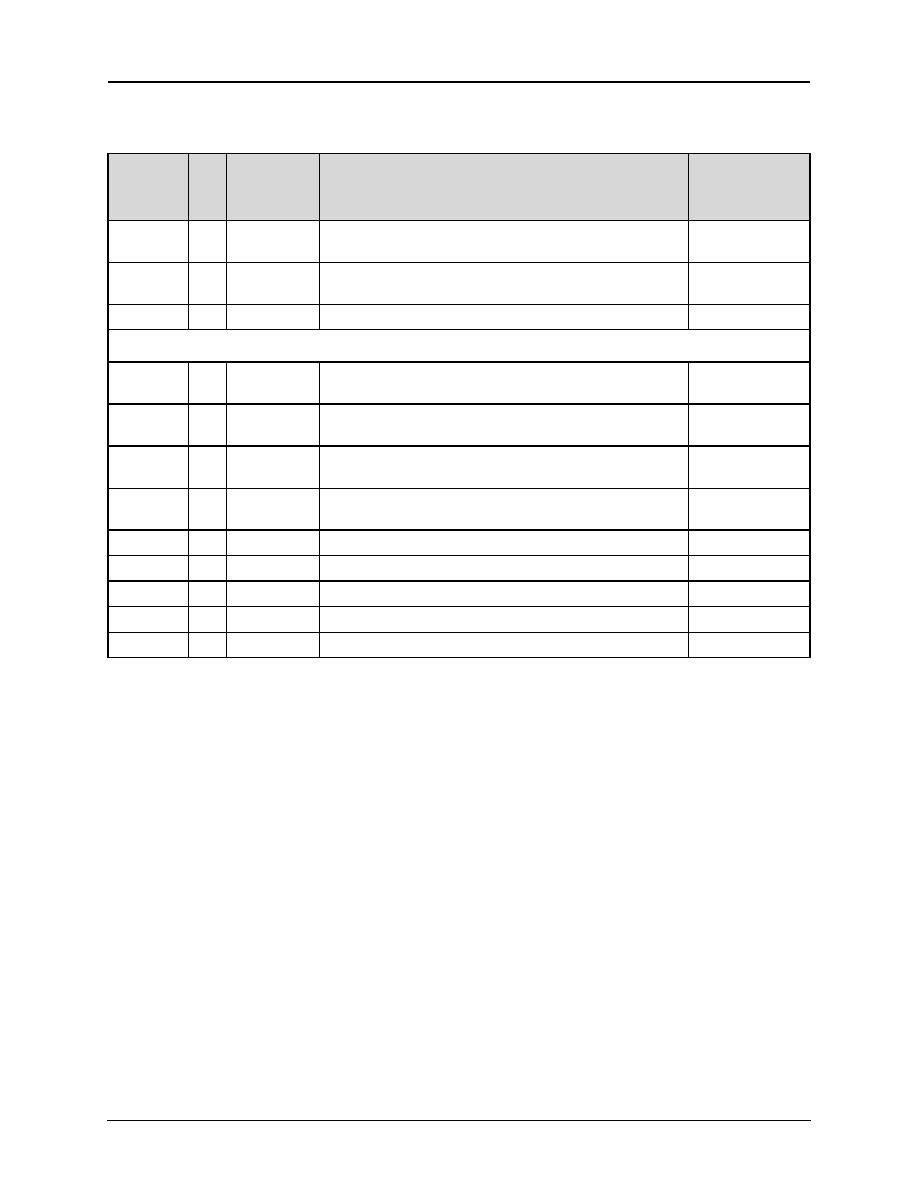

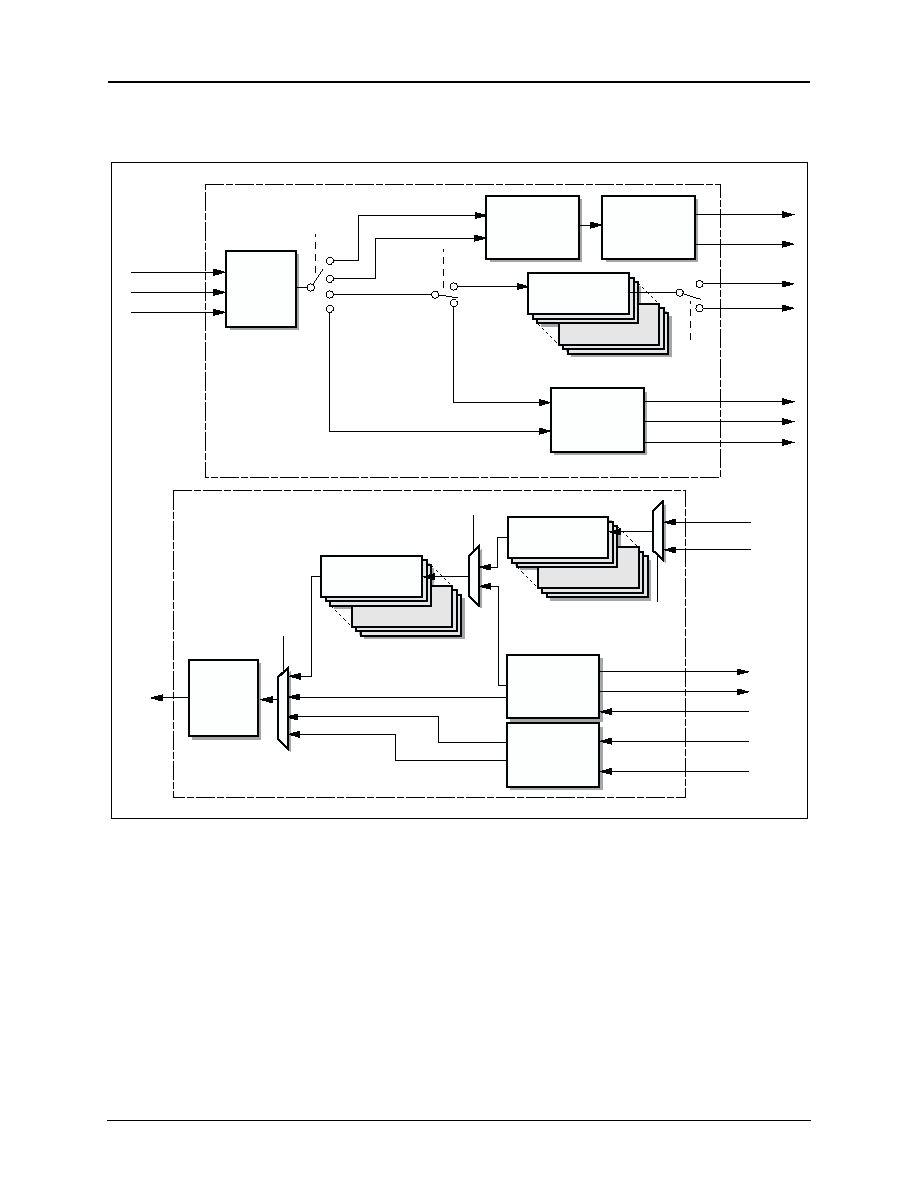

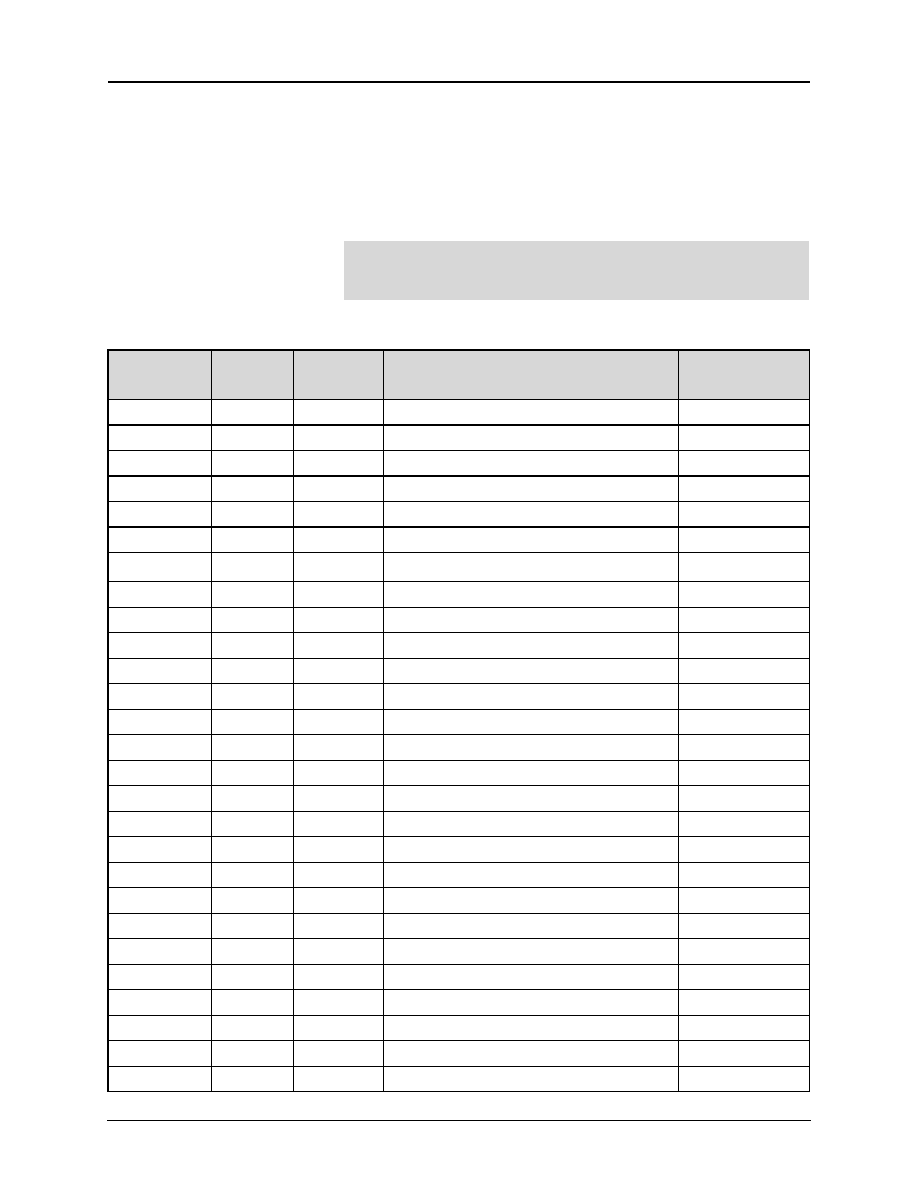

Functional Block Diagram

100702_010a

DS1/VT1.5, E1/VT2.0,

DS1/VC-11, and E1/VC-12

Tributary Mapper

STS-1 to

VT1.5/2.0

TUG-2/3 to

VC-11/VC-12

MUX

Time Slot

Bus

Interface

Module

Command

and Status

Processor

E-Bus

Processor Interface

28xVT1.5/VC-11

21xVT2.0/VC-12

Overhead

Termination/

Generation

SLICE 2

SLICE 3

Payload

TSB

Overhead

TSB

E-Bus Interface

To Host Processor

(Optional)

SI-Bus

Interface

DS3/E3 Serial

Interface

Unchannelized DS3/E3

Unchannelized STS-1

SI-Bus

I/F

Top-

Level

SI-Bus

MUX

STS-1 to

DS3/E3

Mapper

DS3/E3

Framer

M13/E13

MUX

DEMUX

28xDS1

21xE1

Framers

SLICE 1

Distinguishing Features

∑

Capacity

≠ Three STS-1 or TUG-3 or DS3 or

E3 line-side inputs

∑

Supports two types of line interfaces:

≠ SONET Interleave Bus (SI-Bus)

interfaces for a parallel data bus

connection to the SONET/SDH

multiplexer devices at the

STS-1/TUG-3 data rates

≠ DS3/E3 serial interfaces for a

connection to Line Interface Units

(LIU)

∑

System Interface

≠ Supports three serial Time Slot

Bus (TSB) interfaces for a

connection to high-density HDLC

controller devices. Time slots can

be configured to transmit DS3/E3,

DS1/E1/J1, STS-1, or VT1.5

payloads

∑

Supports the following multiplexing

modes:

≠ PDH

∑

M13

∑

E13

∑

G.747

≠ SONET/SDH

∑

STS-1/VT1.5

∑

STS-1/VT2.0

∑

TUG-3/VC-11

∑

TUG-3/VC-12

∑

Supports the following mapping

modes:

≠ SONET/PDH

∑

DS3 to STS-1

∑

E3 to STS-1

∑

DS1 to VT1.5

∑

J1 to VT1.5

∑

E1 to VT2.0

≠ SDH/PDH

≠ DS3 to VC-3

∑

E3 to VC-3

∑

DS1 to VC-11

∑

J1 to VC-11

∑

E1 to VC-12

∑

Embedded PDH framers including:

≠ 3 x DS3/E3 framers

≠ 21 x DS2/E2 framers

≠ 84 x DS1/E1/J1 framers

© 2002,

Mindspeed TechnologiesTM, A Conexant Business

All rights reserved.

Information in this document is provided in connection with Mindspeed Technologies ("Mindspeed") products. These materials are

provided by Mindspeed as a service to its customers and may be used for informational purposes only. Mindspeed assumes no

responsibility for errors or omissions in these materials. Mindspeed may make changes to specifications and product descriptions at

any time, without notice. Mindspeed makes no commitment to update the information and shall have no responsibility whatsoever for

conflicts or incompatibilities arising from future changes to its specifications and product descriptions.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as

provided in Mindspeed's Terms and Conditions of Sale for such products, Mindspeed assumes no liability whatsoever.

THESE MATERIALS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING

TO SALE AND/OR USE OF MINDSPEED PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A

PARTICULAR PURPOSE, CONSEQUENTIAL OR INCIDENTAL DAMAGES, MERCHANTABILITY, OR INFRINGEMENT OF ANY

PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. MINDSPEED FURTHER DOES NOT WARRANT THE

ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE

MATERIALS. MINDSPEED SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL

DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS, WHICH MAY RESULT FROM THE USE

OF THESE MATERIALS.

Mindspeed products are not intended for use in medical, lifesaving or life sustaining applications. Mindspeed customers using or

selling Mindspeed products for use in such applications do so at their own risk and agree to fully indemnify Mindspeed for any

damages resulting from such improper use or sale.

The following are trademarks of Conexant Systems, Inc.: Mindspeed TechnologiesTM, the MindspeedTM logo, and "Build It First"TM.

Product names or services listed in this publication are for identification purposes only, and may be trademarks of third parties.

Third-party brands and names are the property of their respective owners.

For additional disclaimer information, please consult Mindspeed Technologies Legal Information posted at

www.mindspeed.com

which is incorporated by reference.

ii

Mindspeed TechnologiesTM

500238B

Advance Information

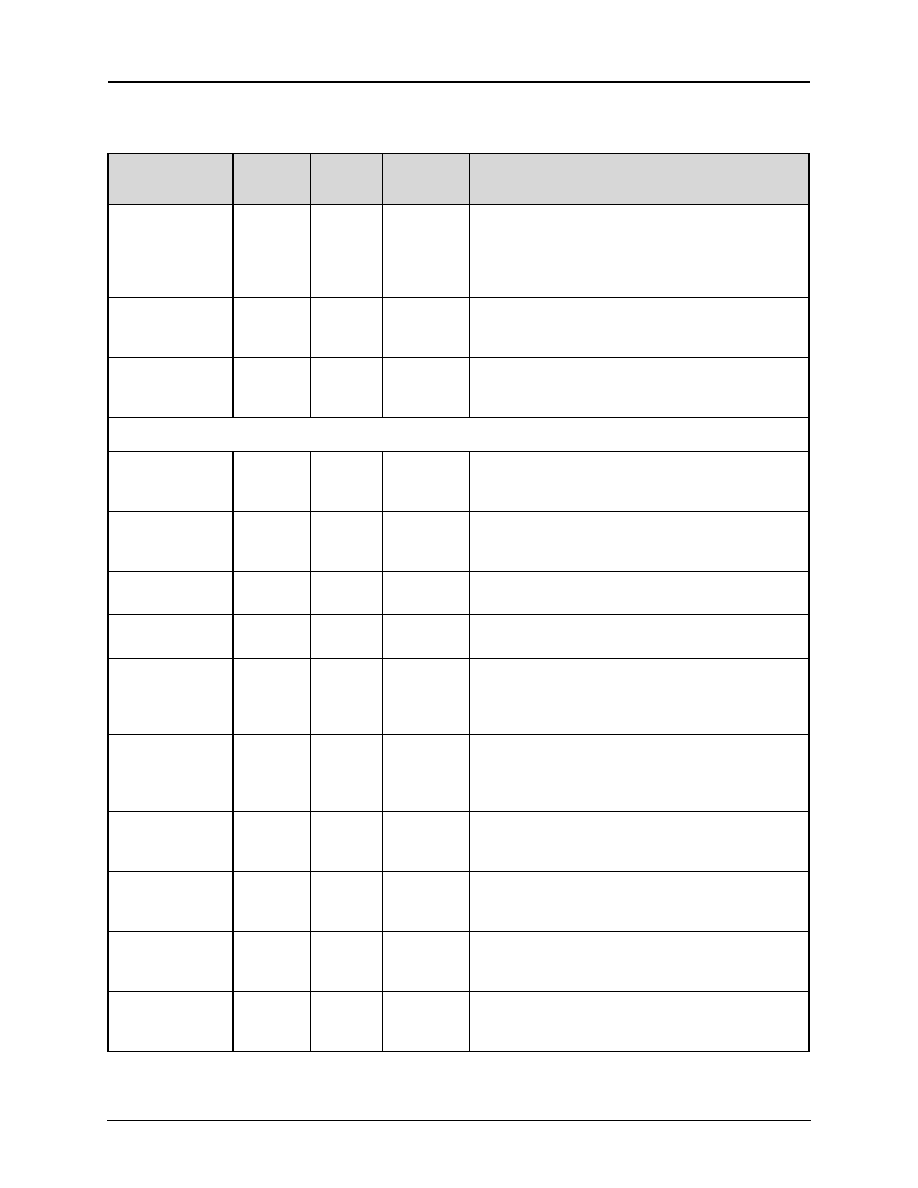

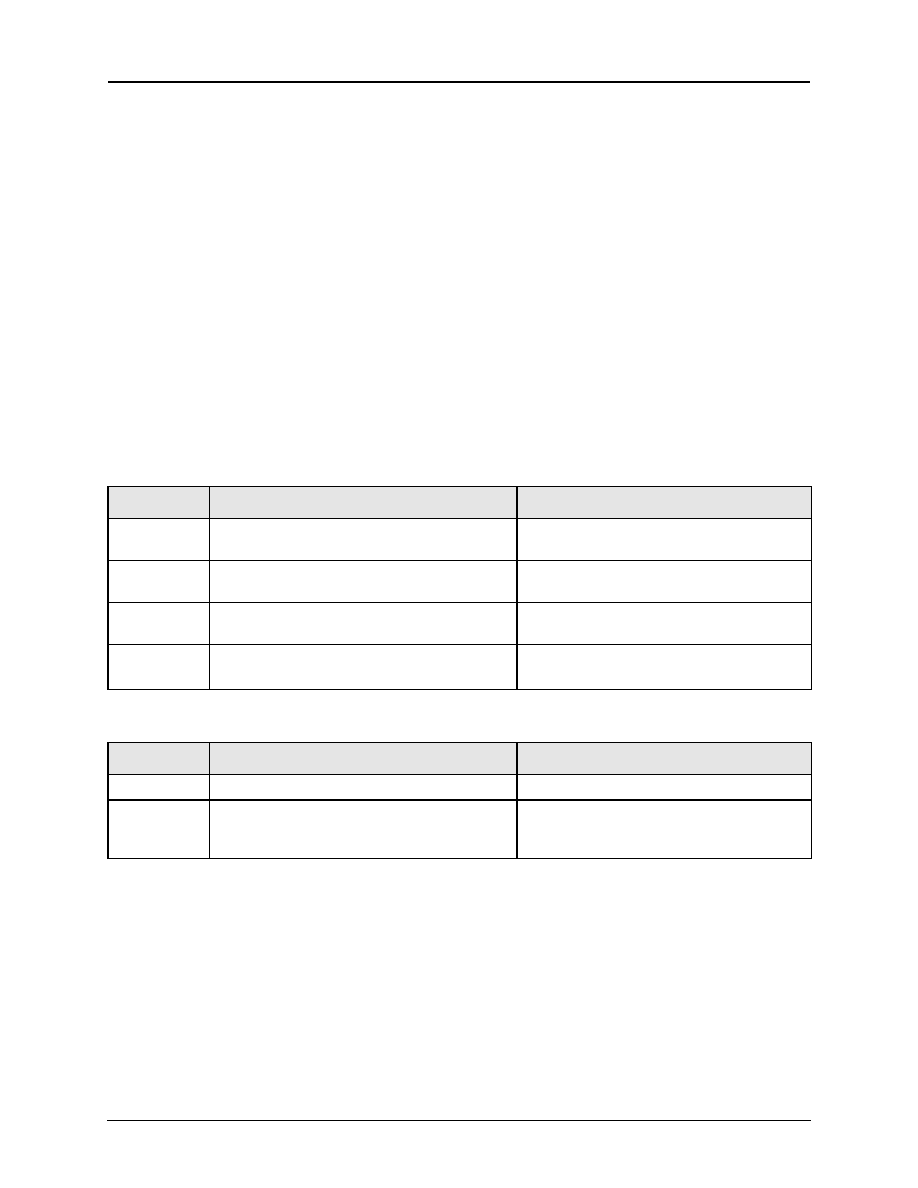

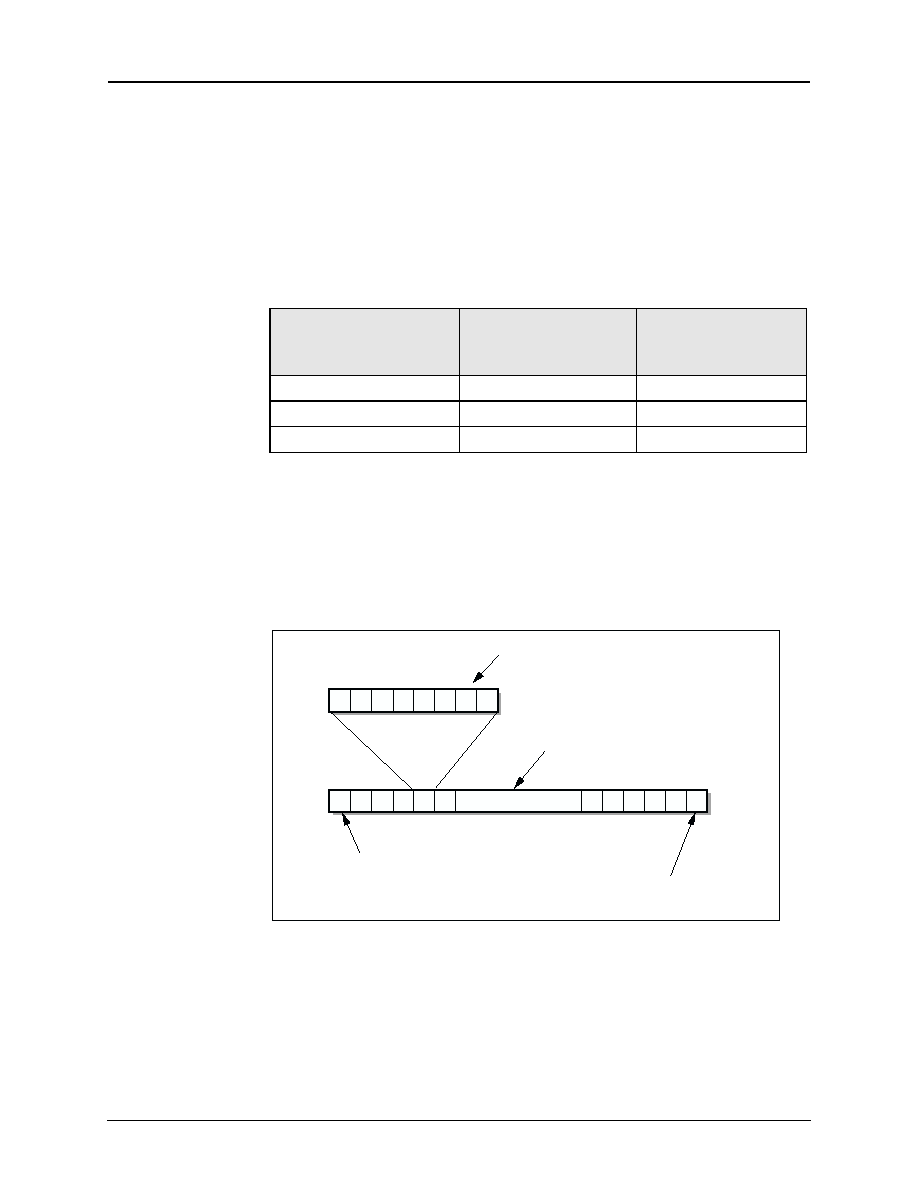

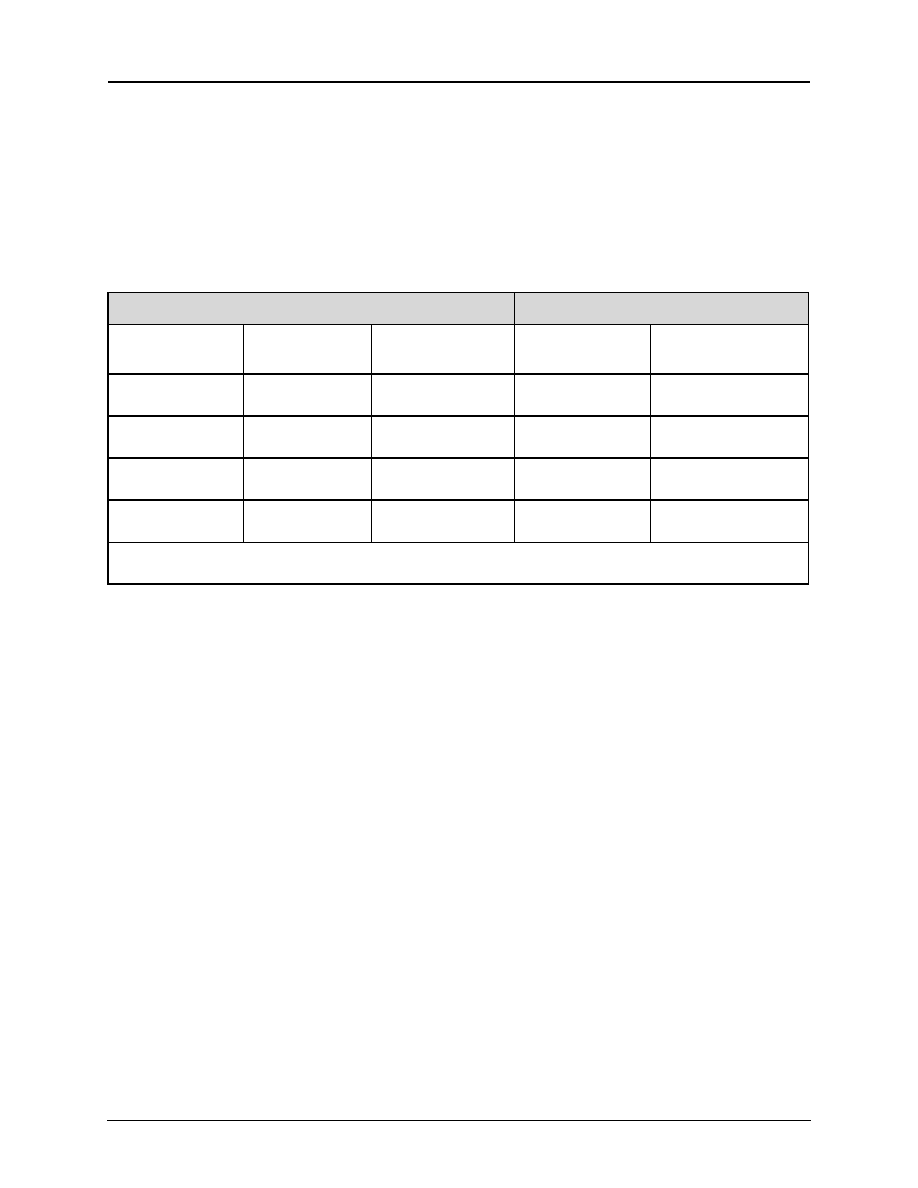

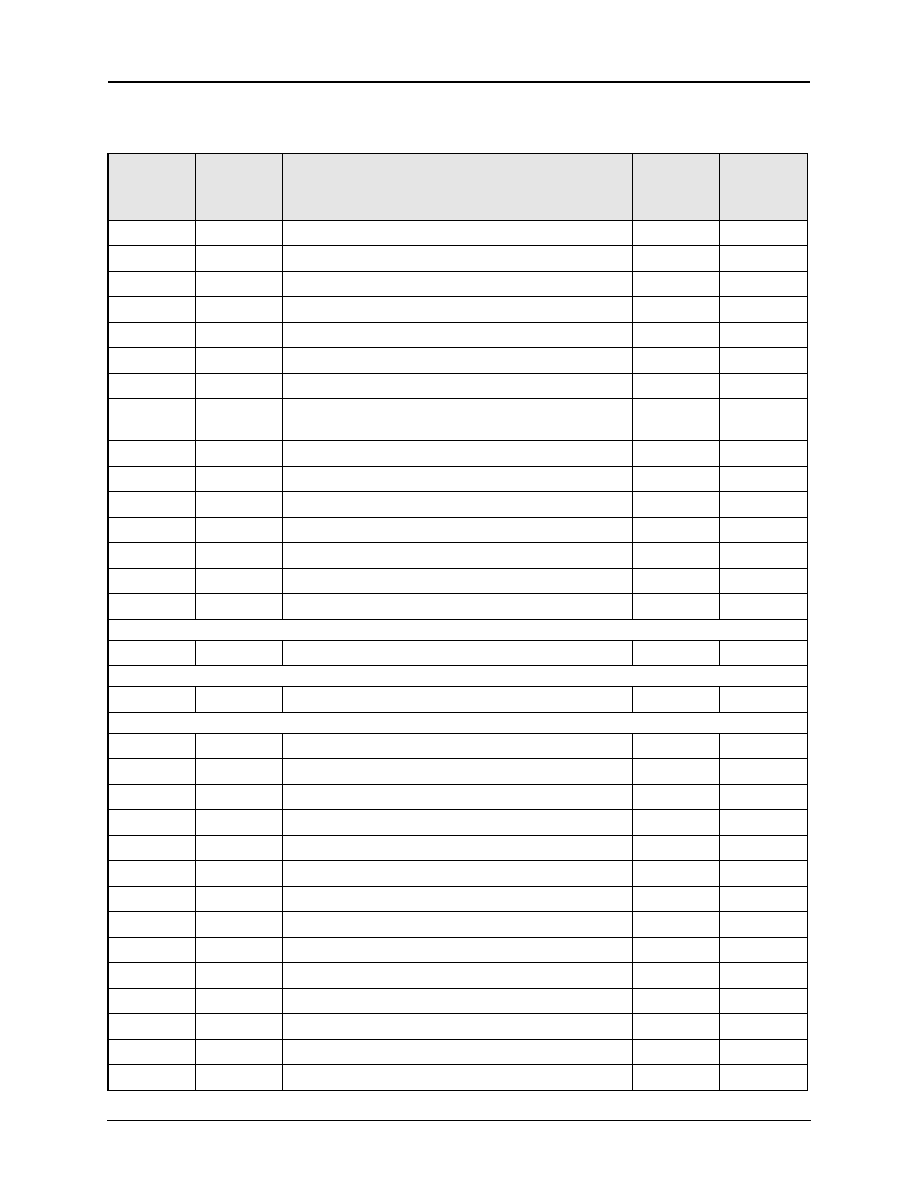

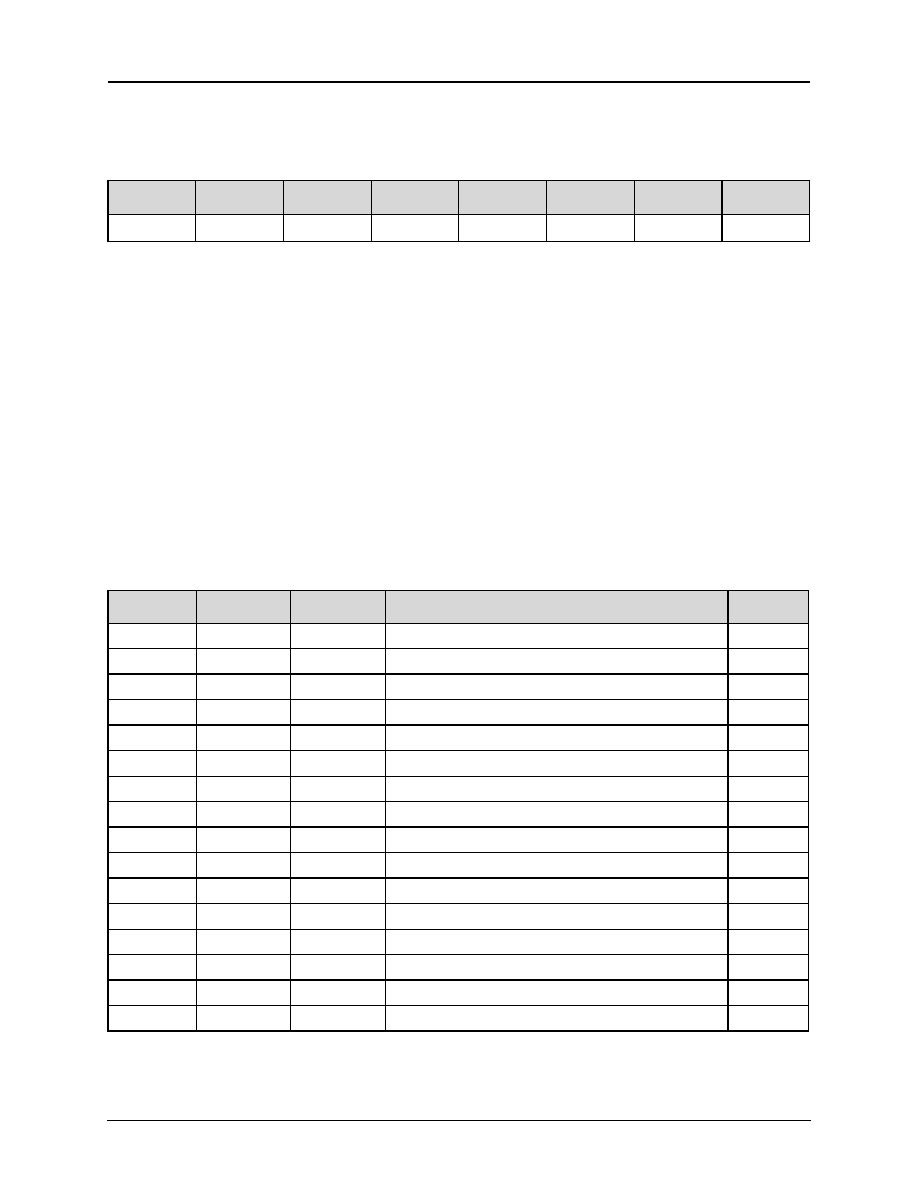

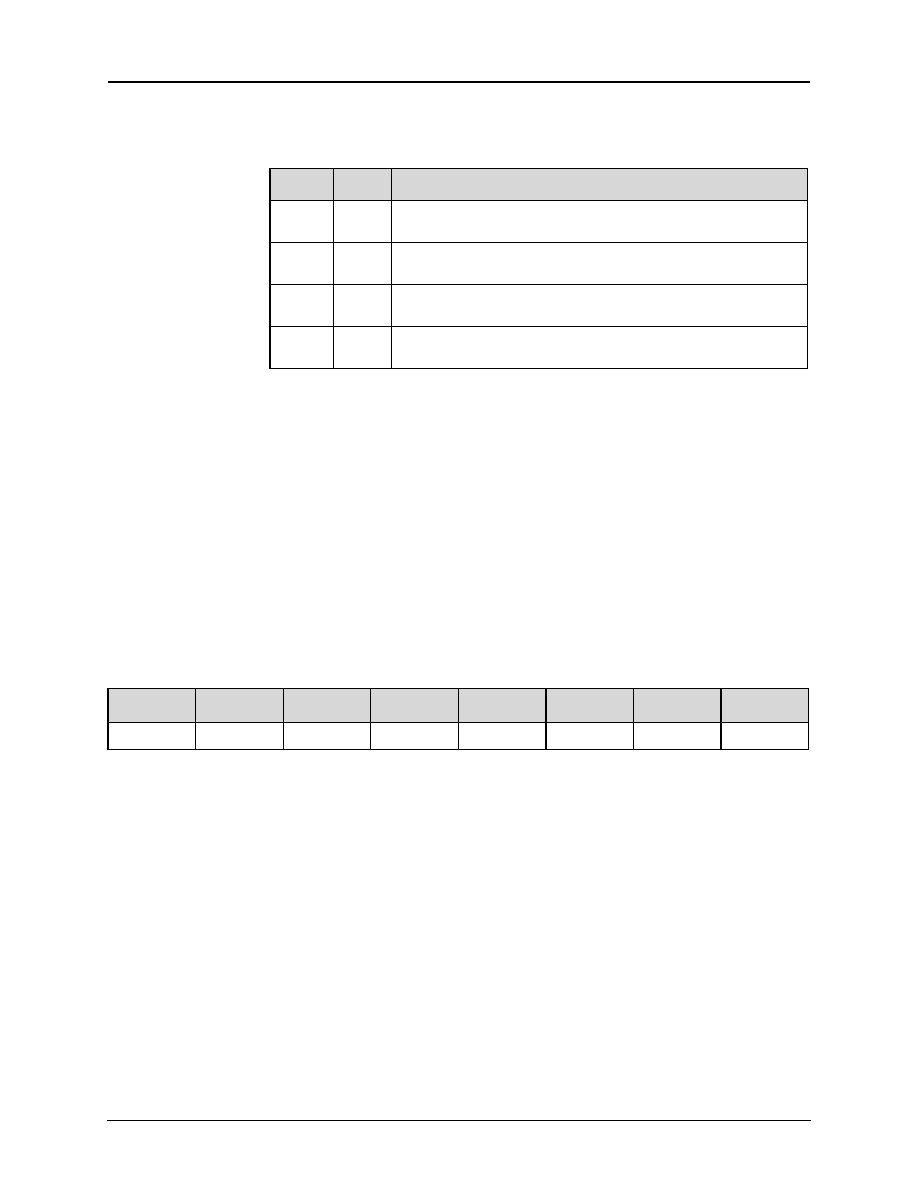

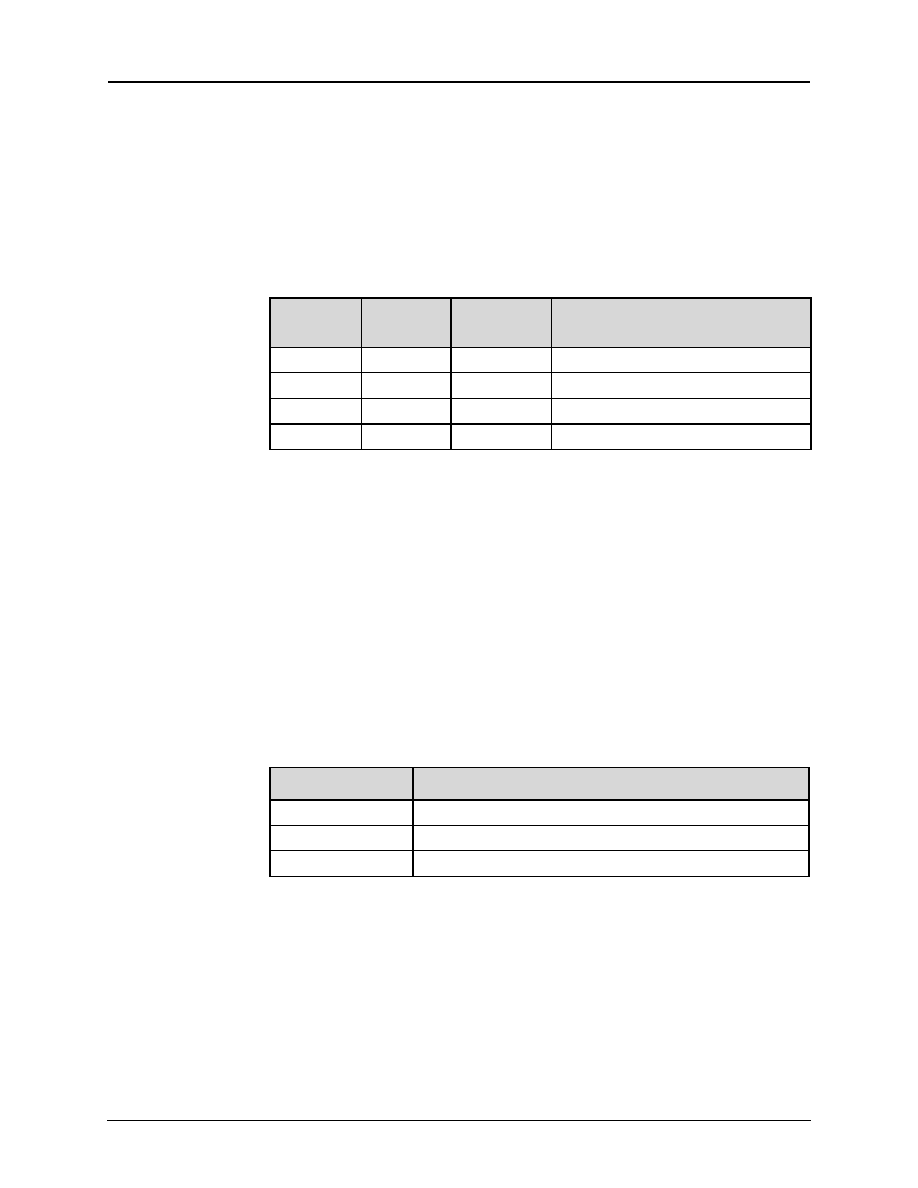

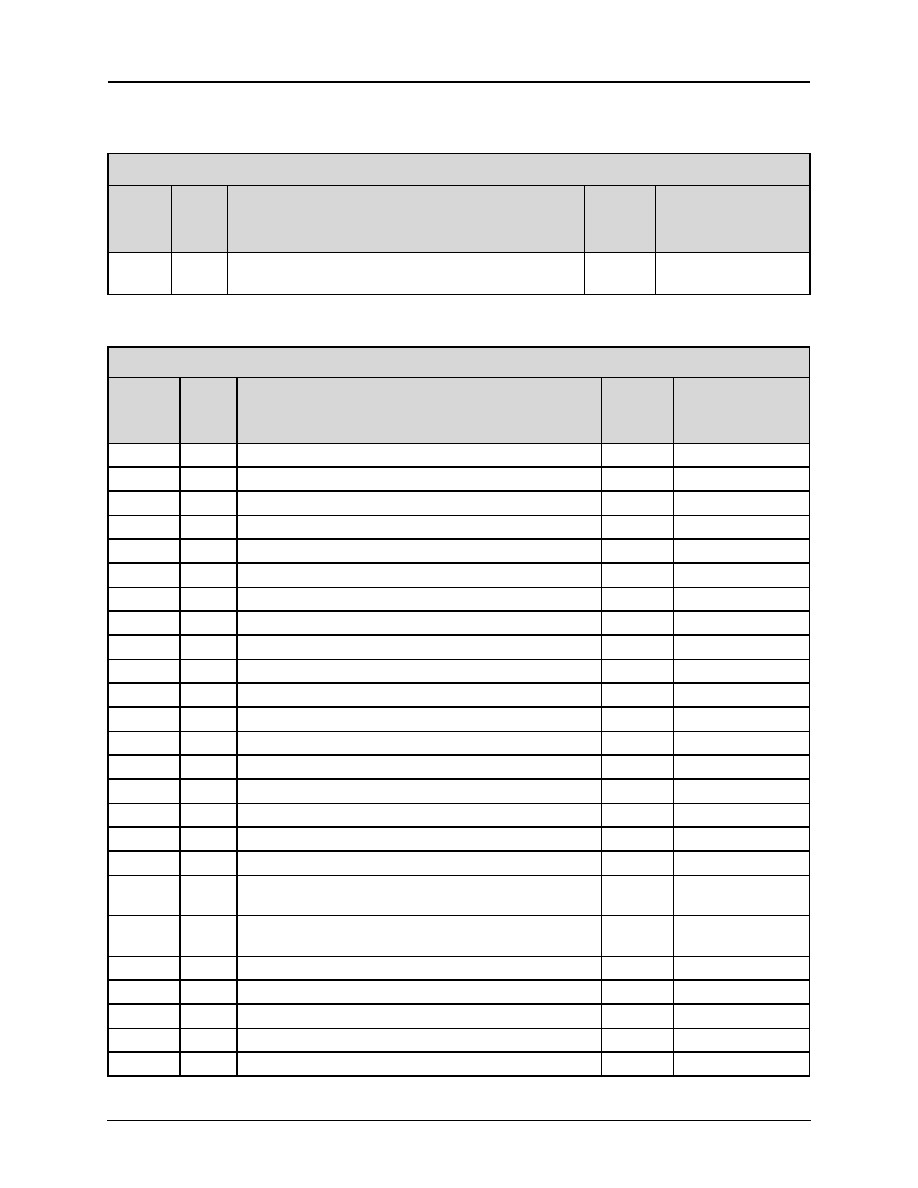

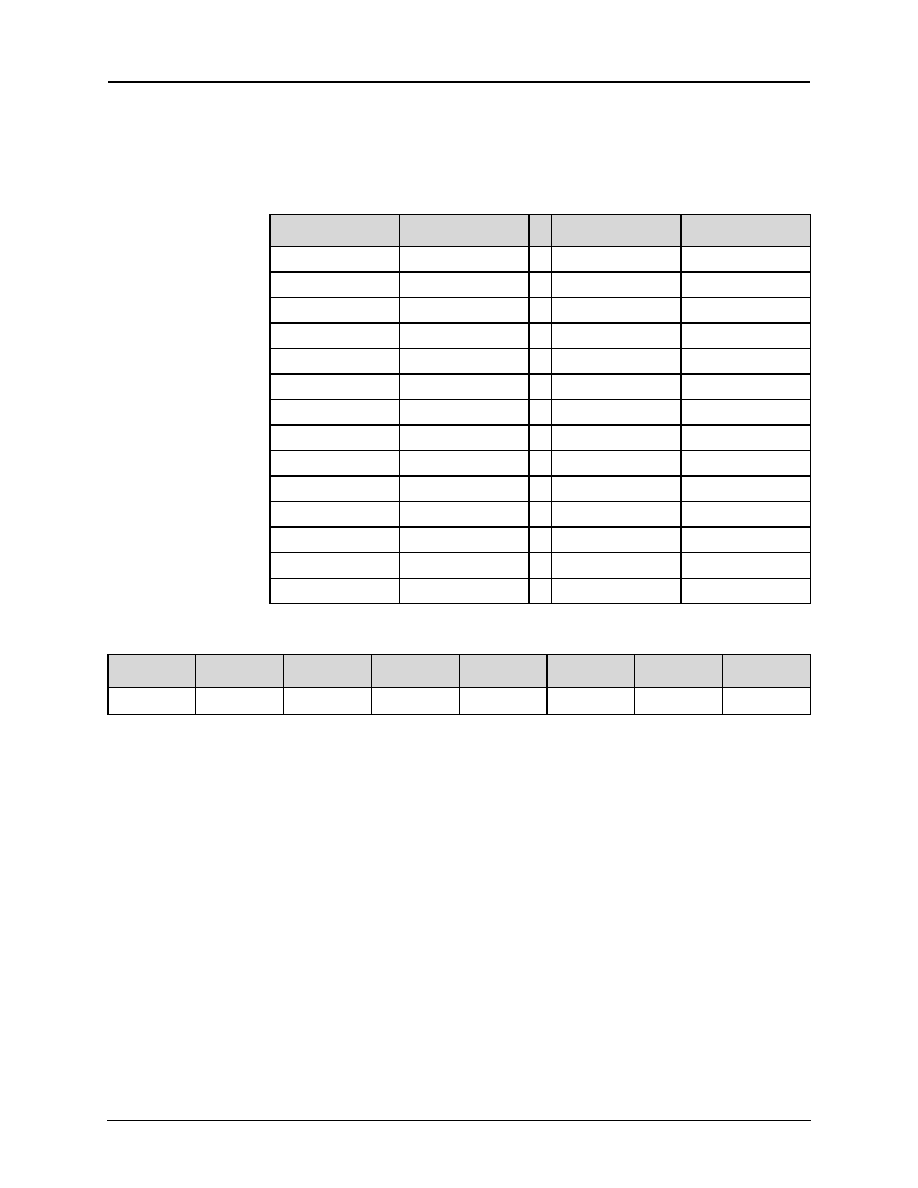

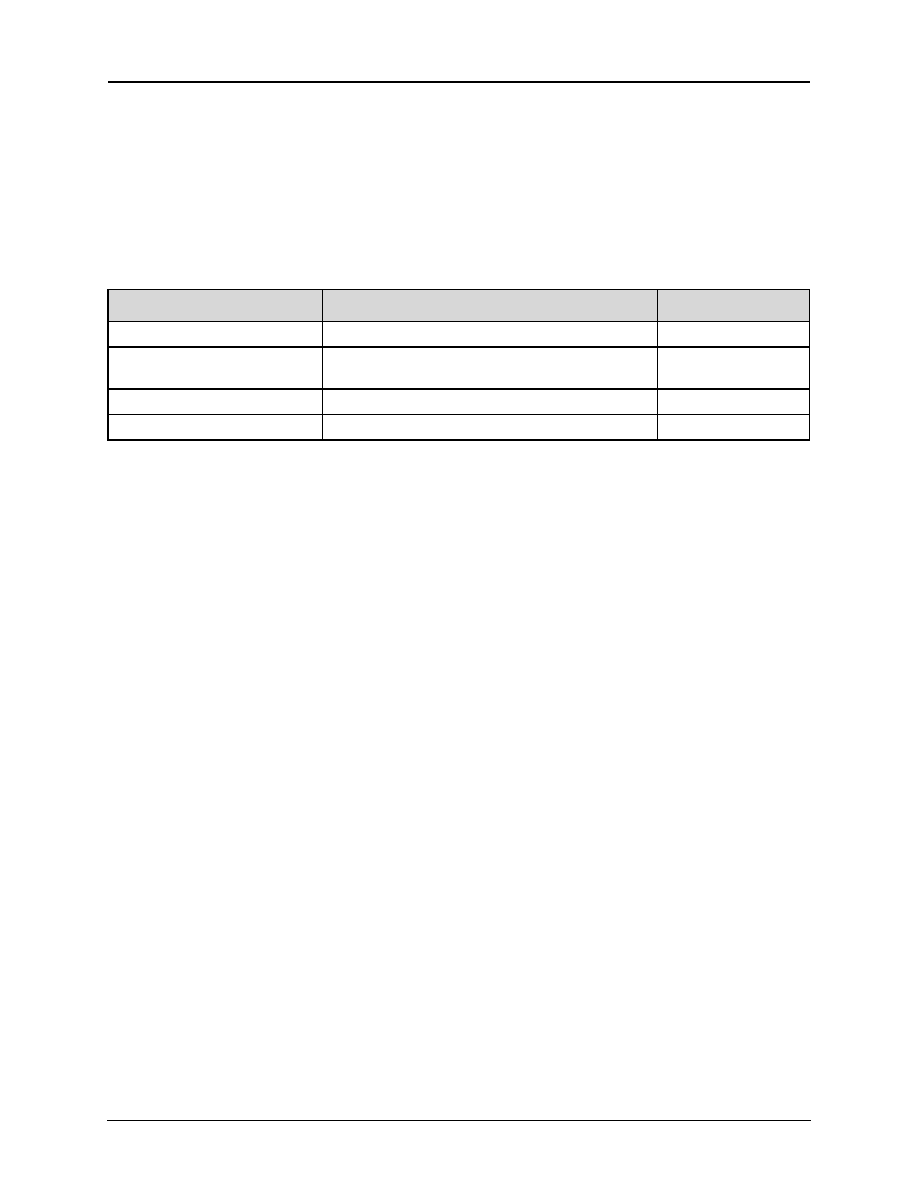

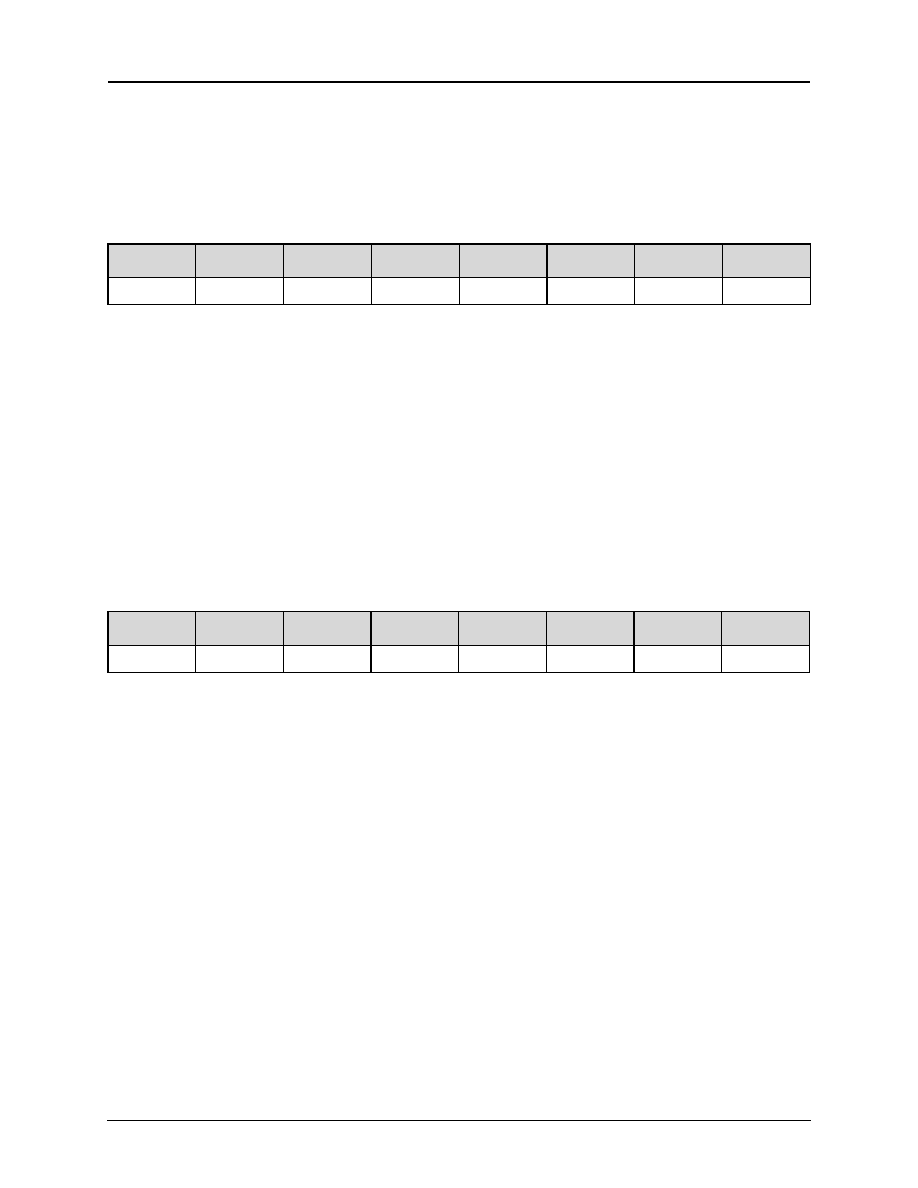

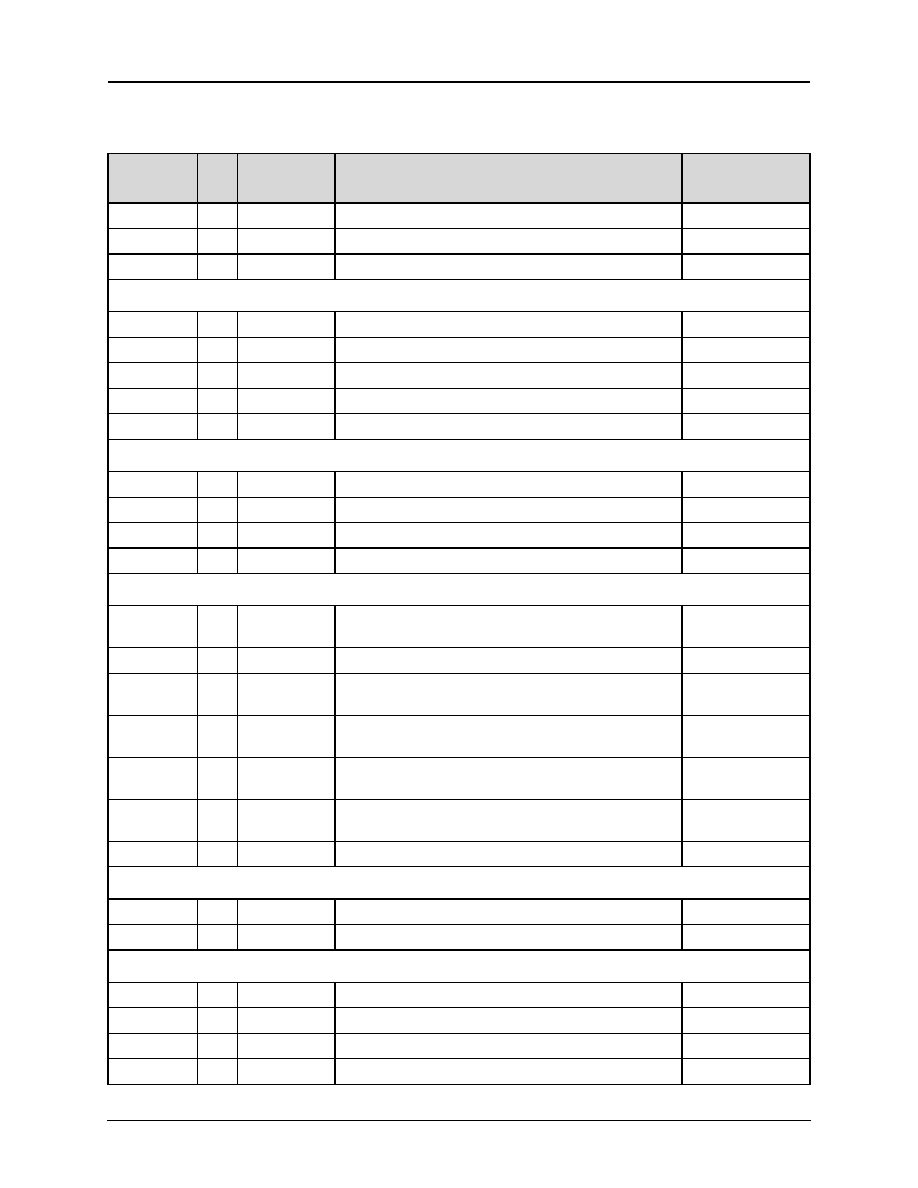

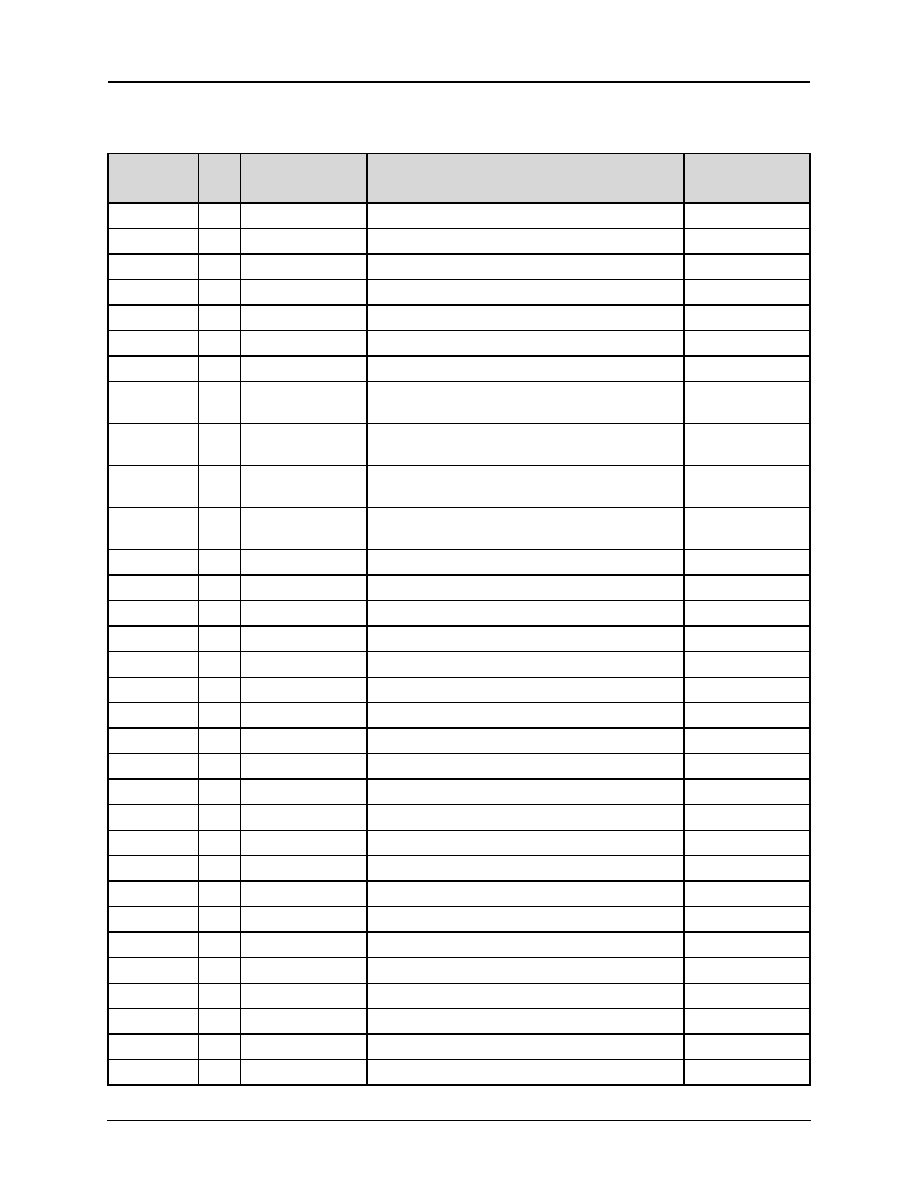

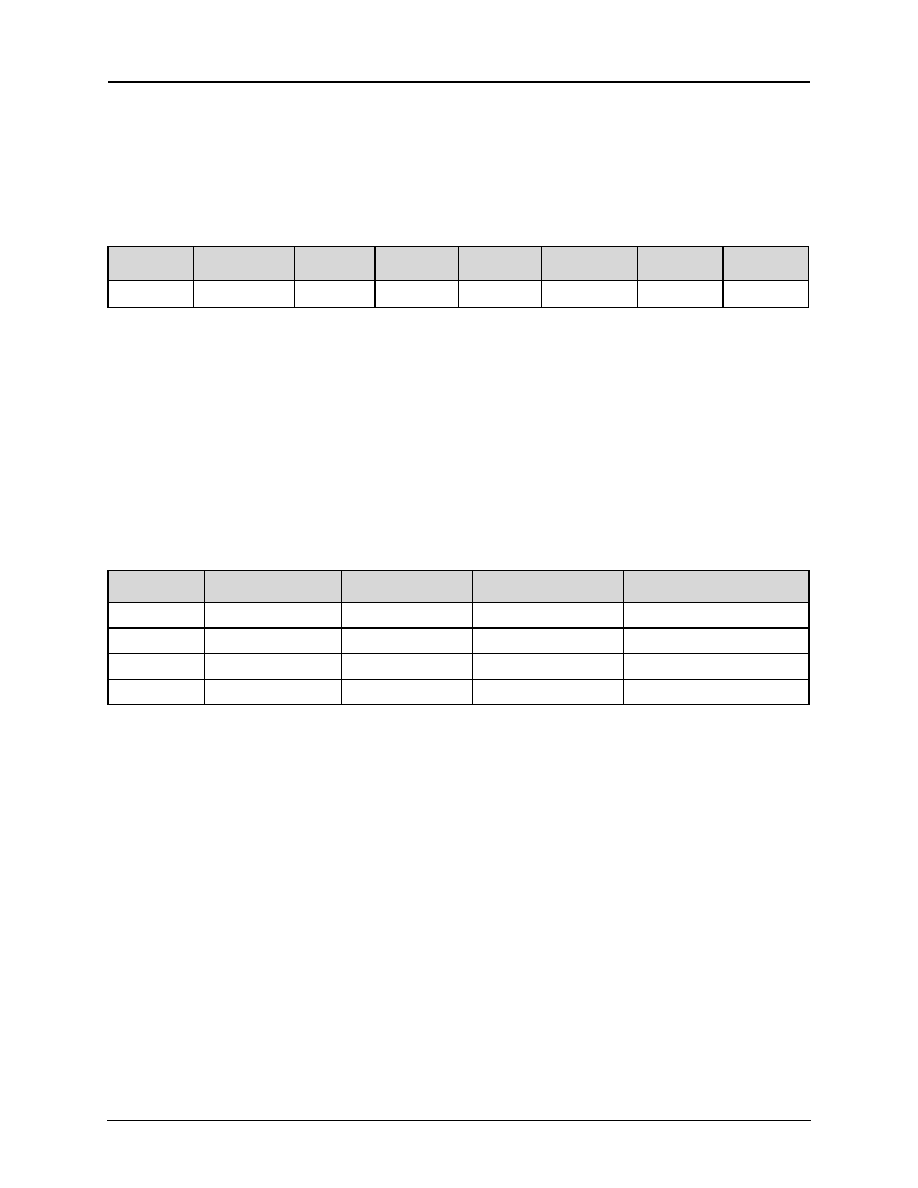

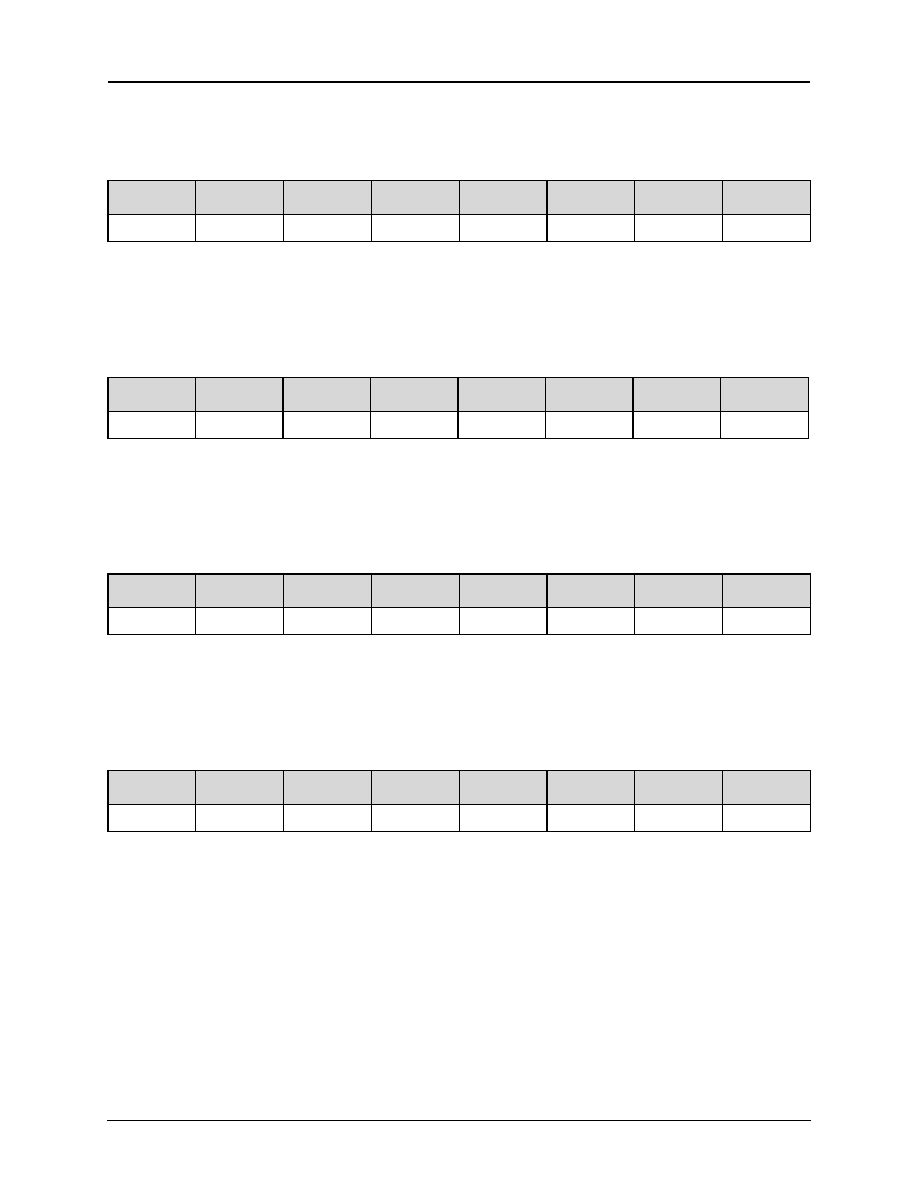

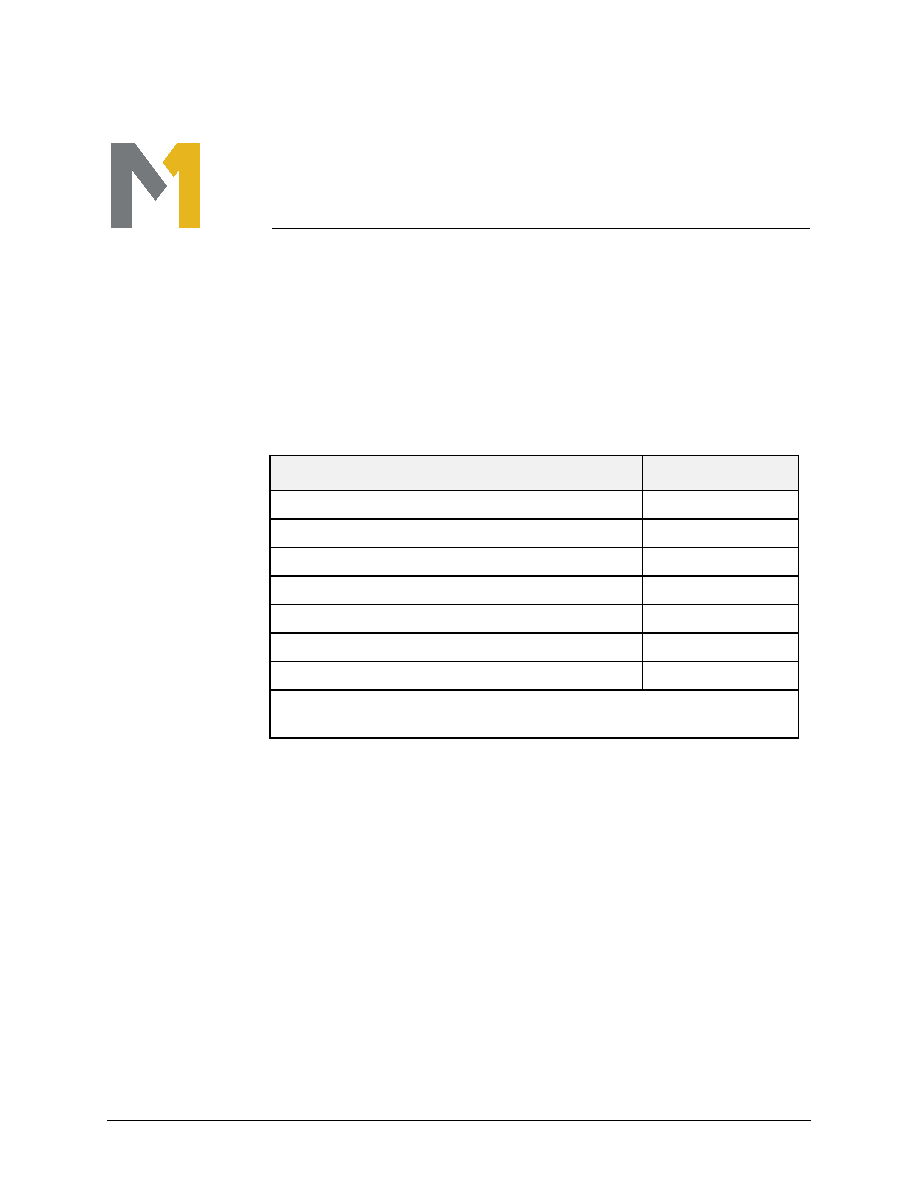

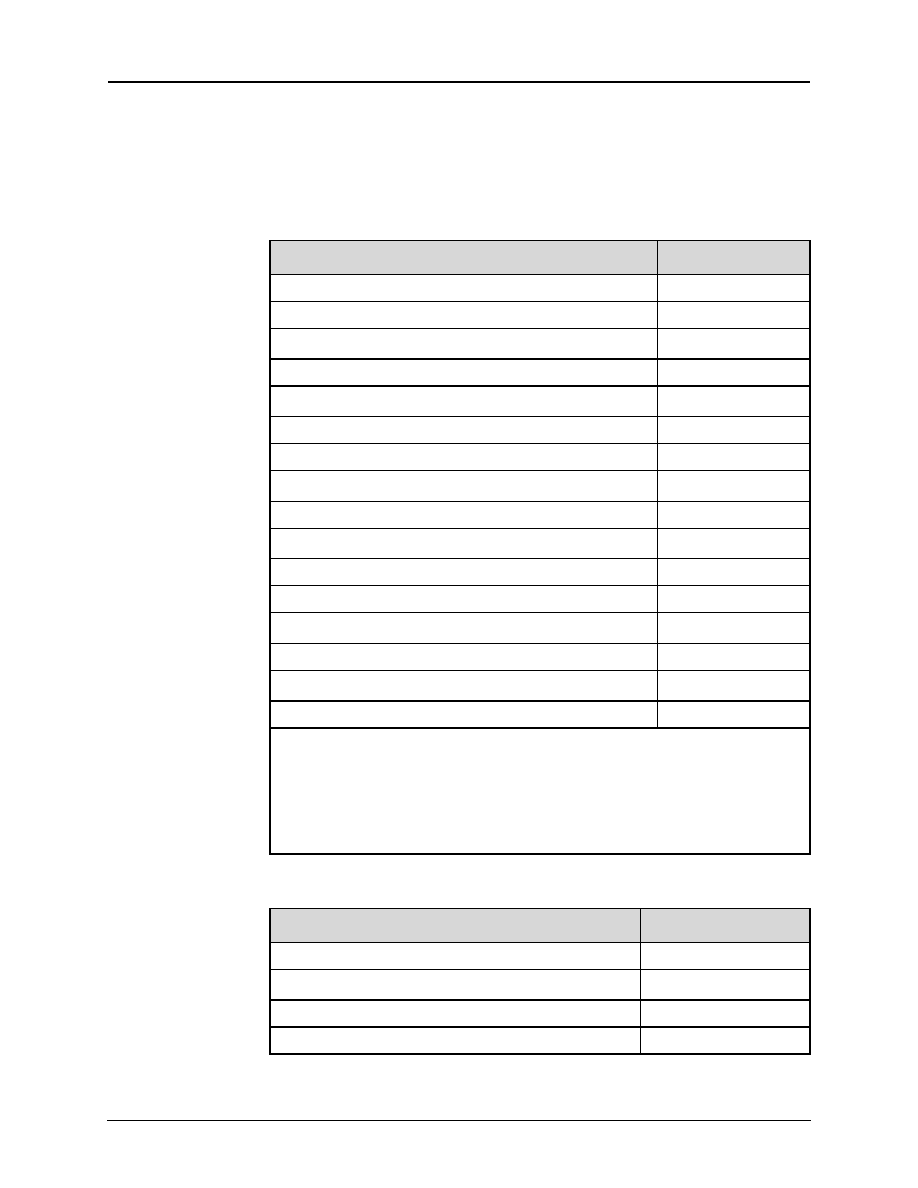

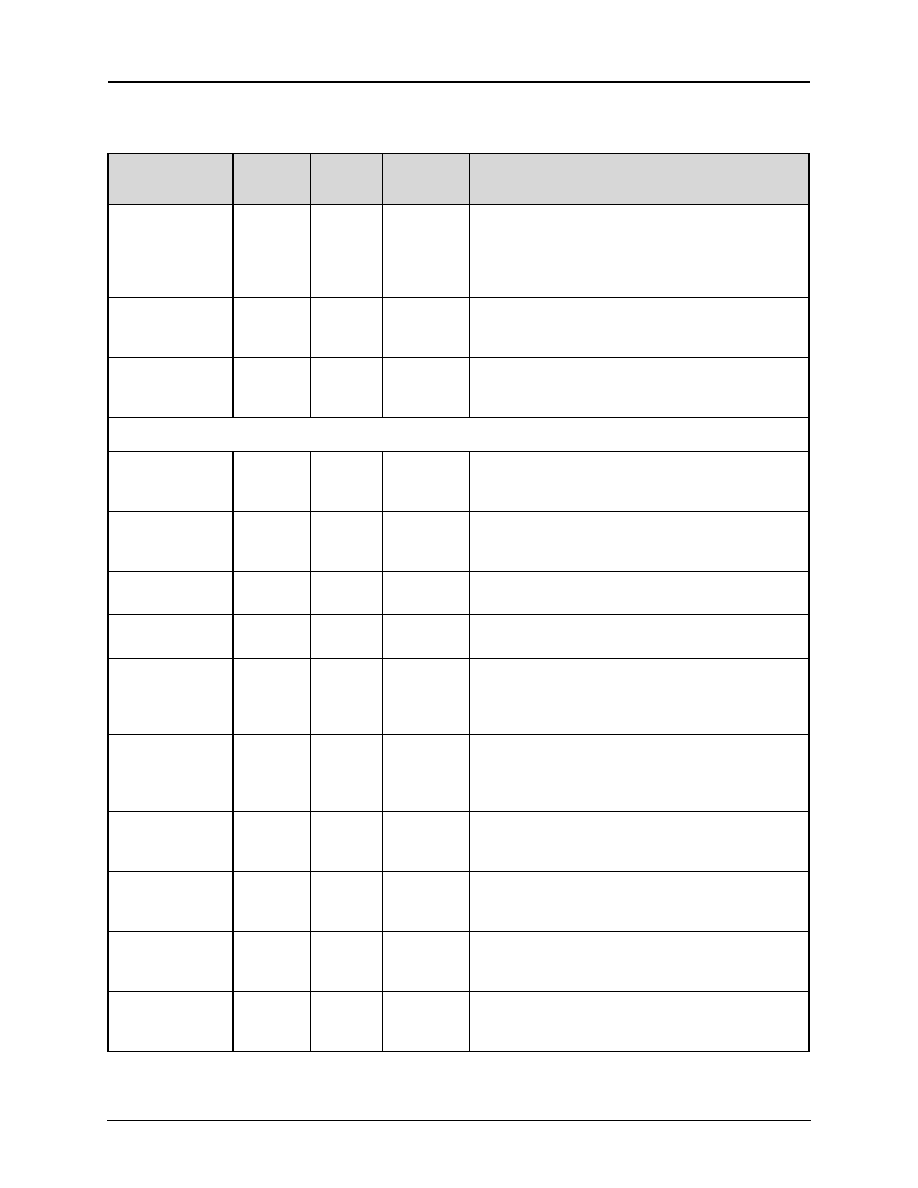

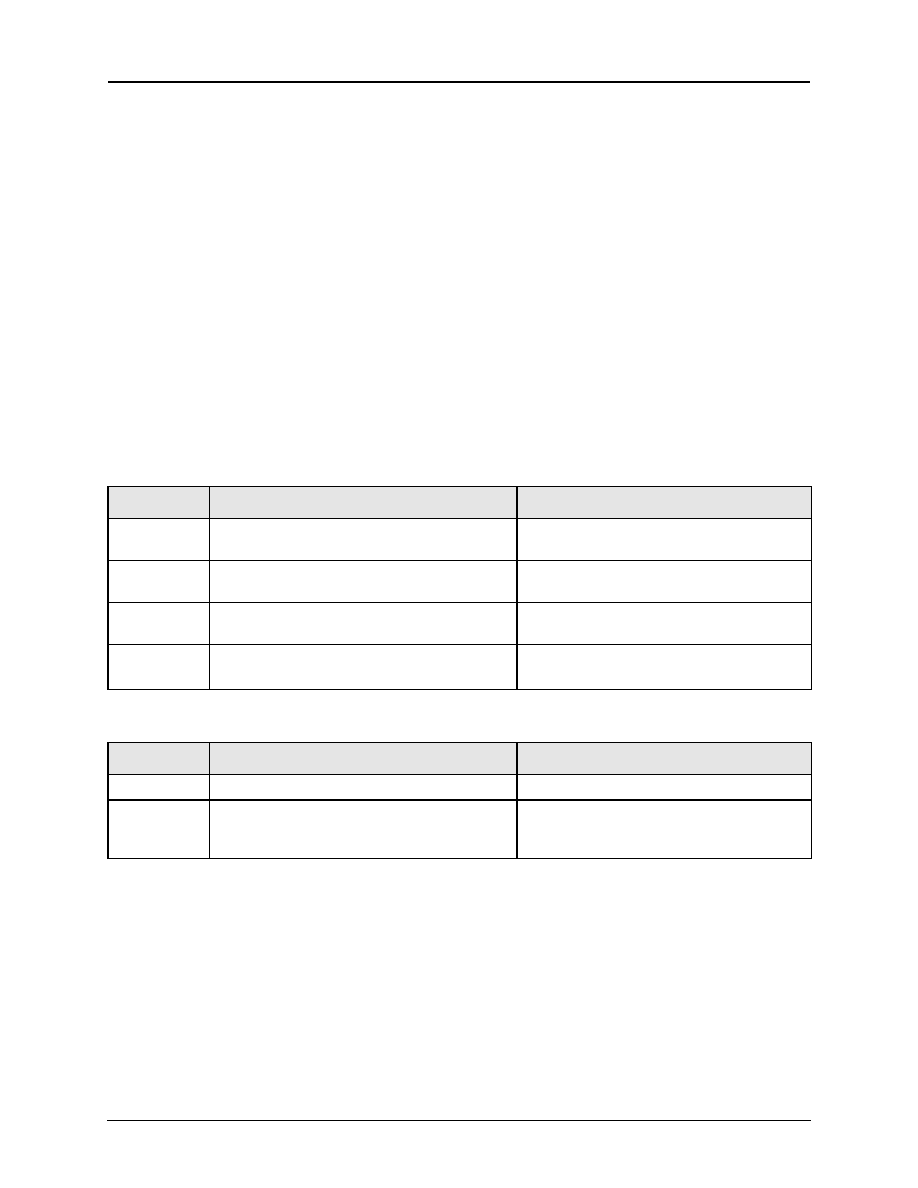

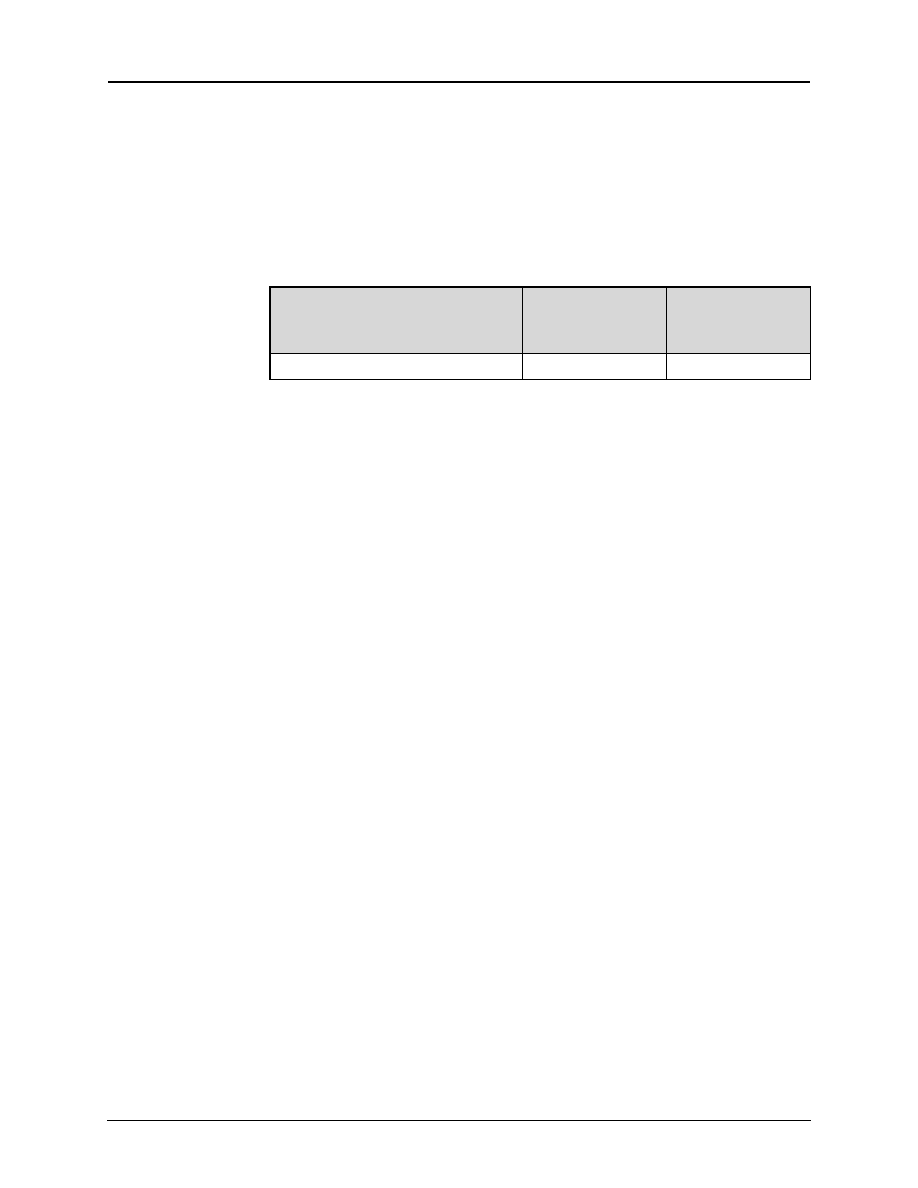

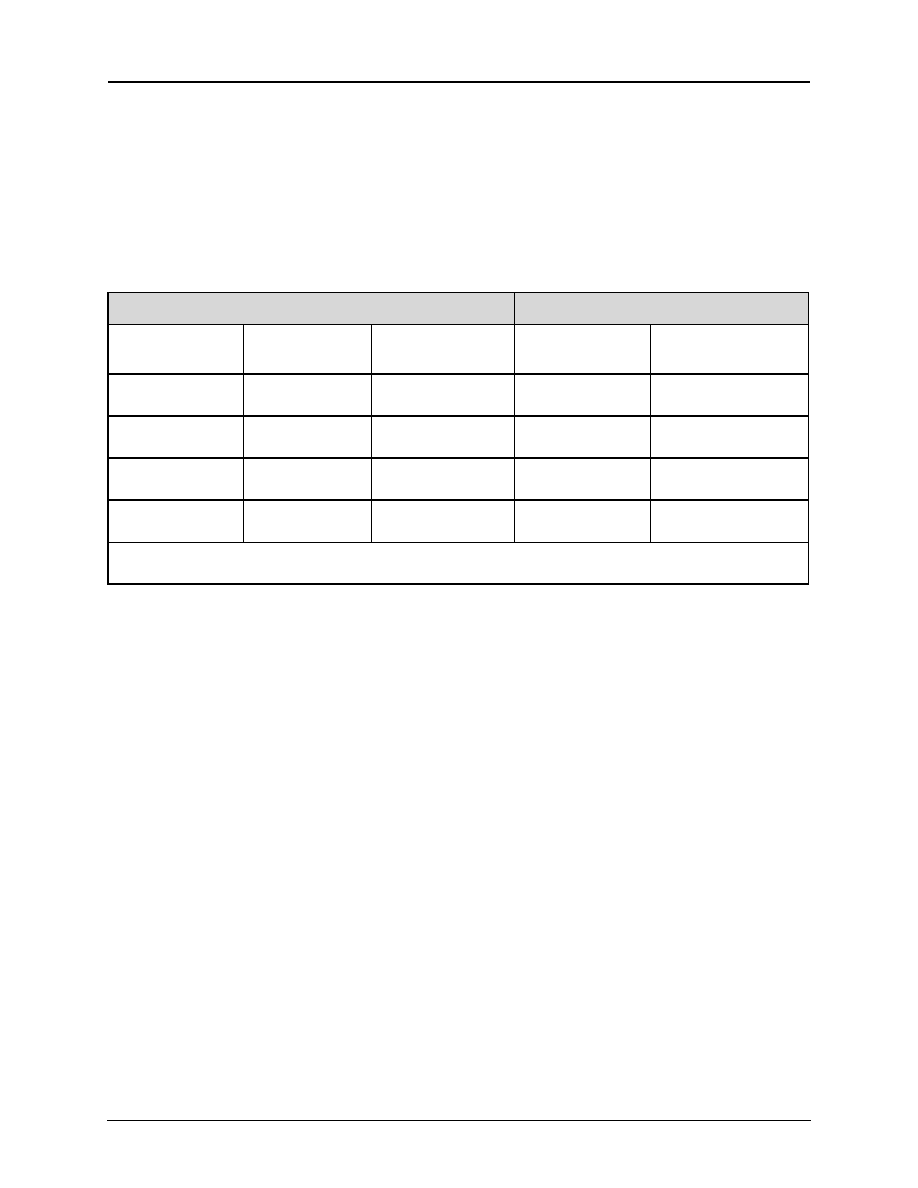

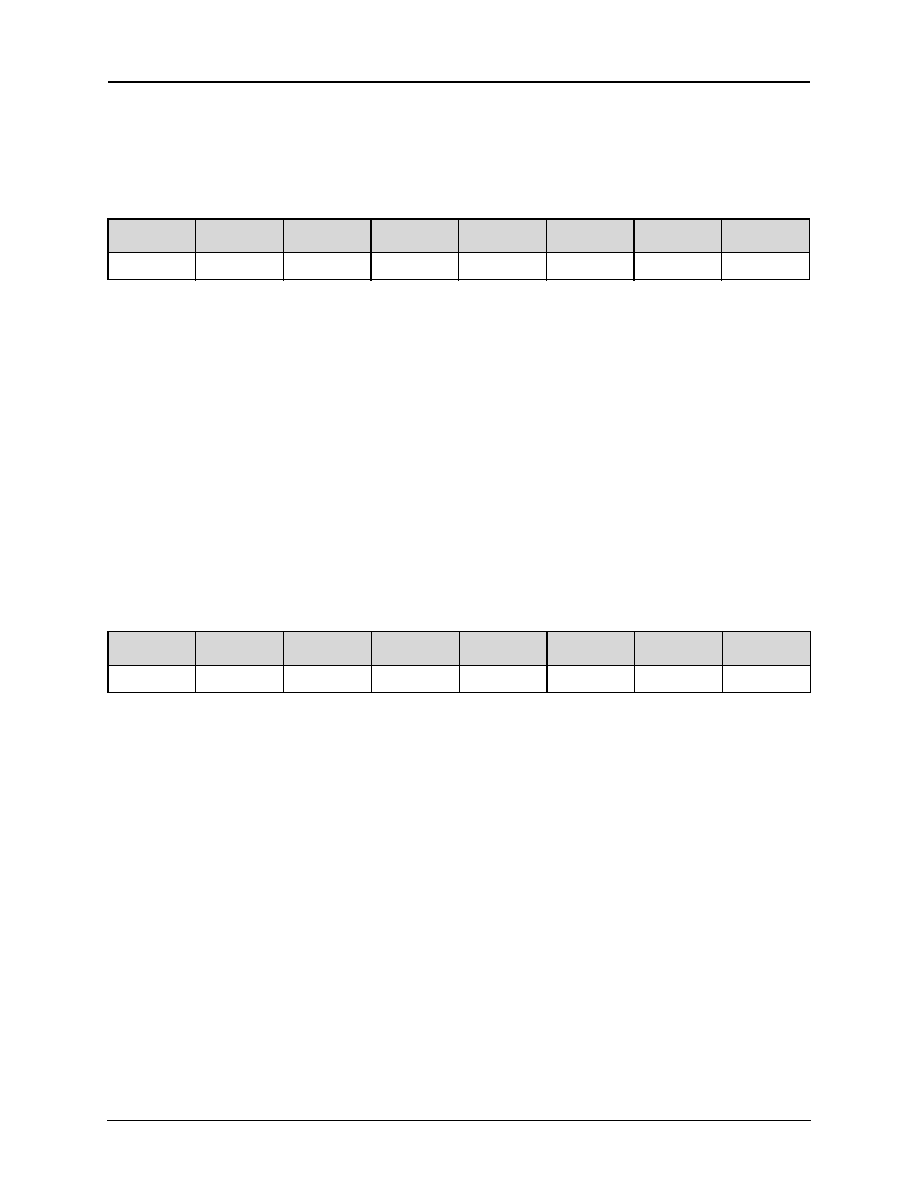

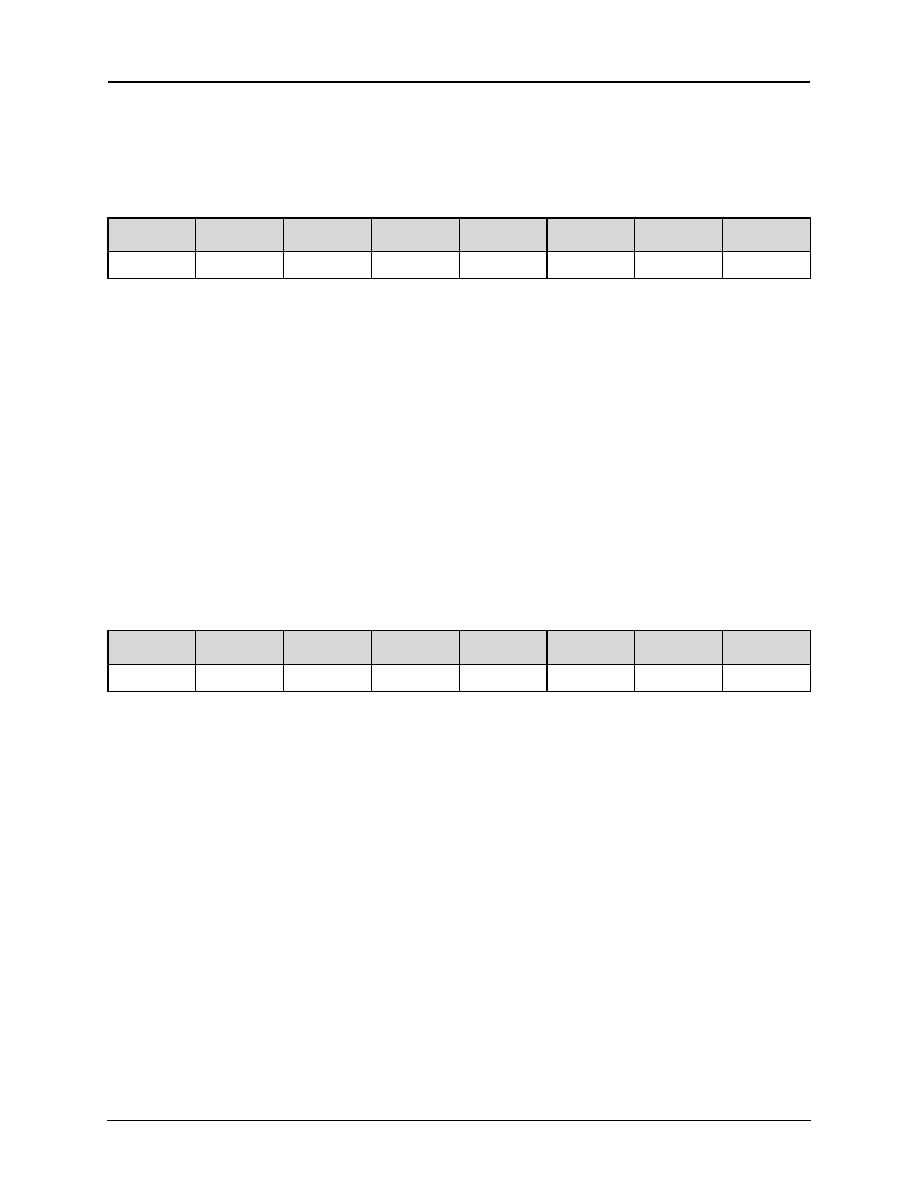

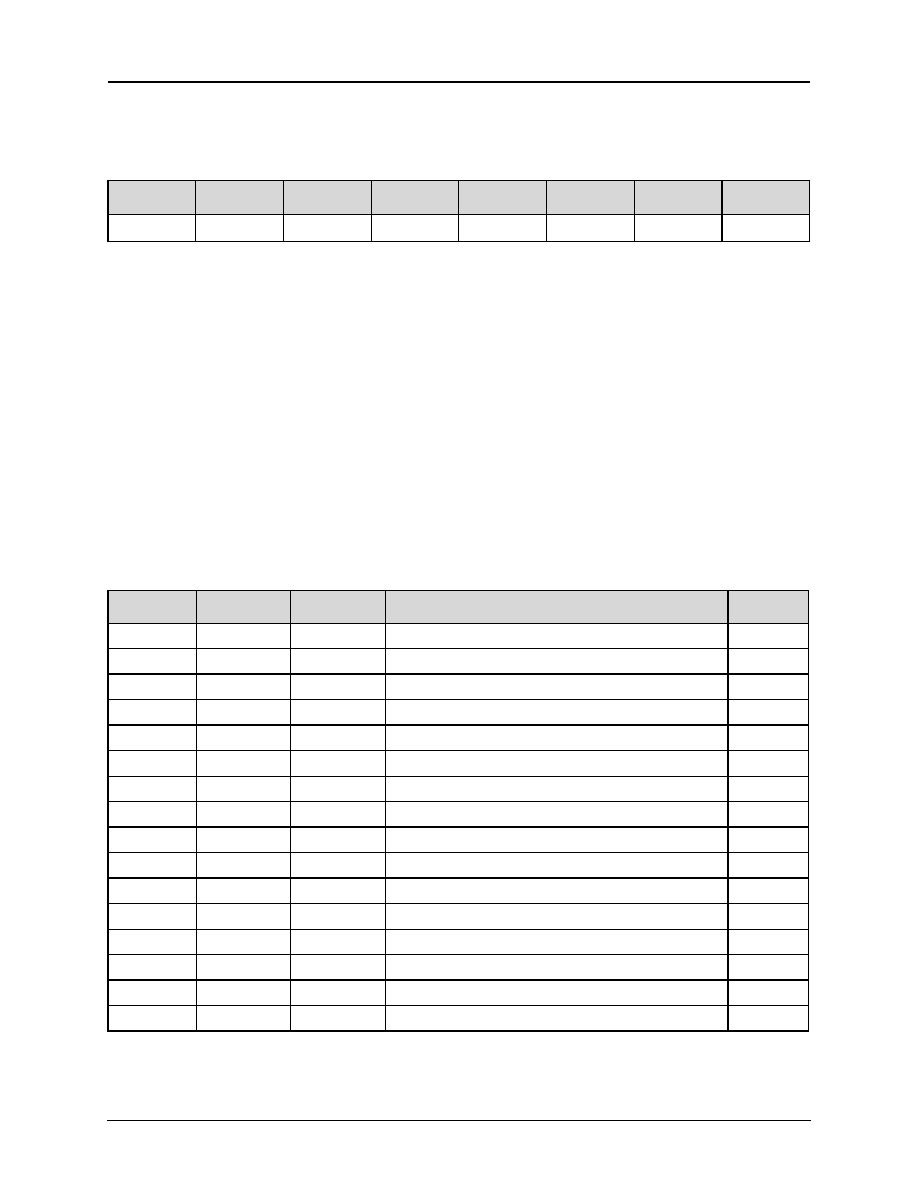

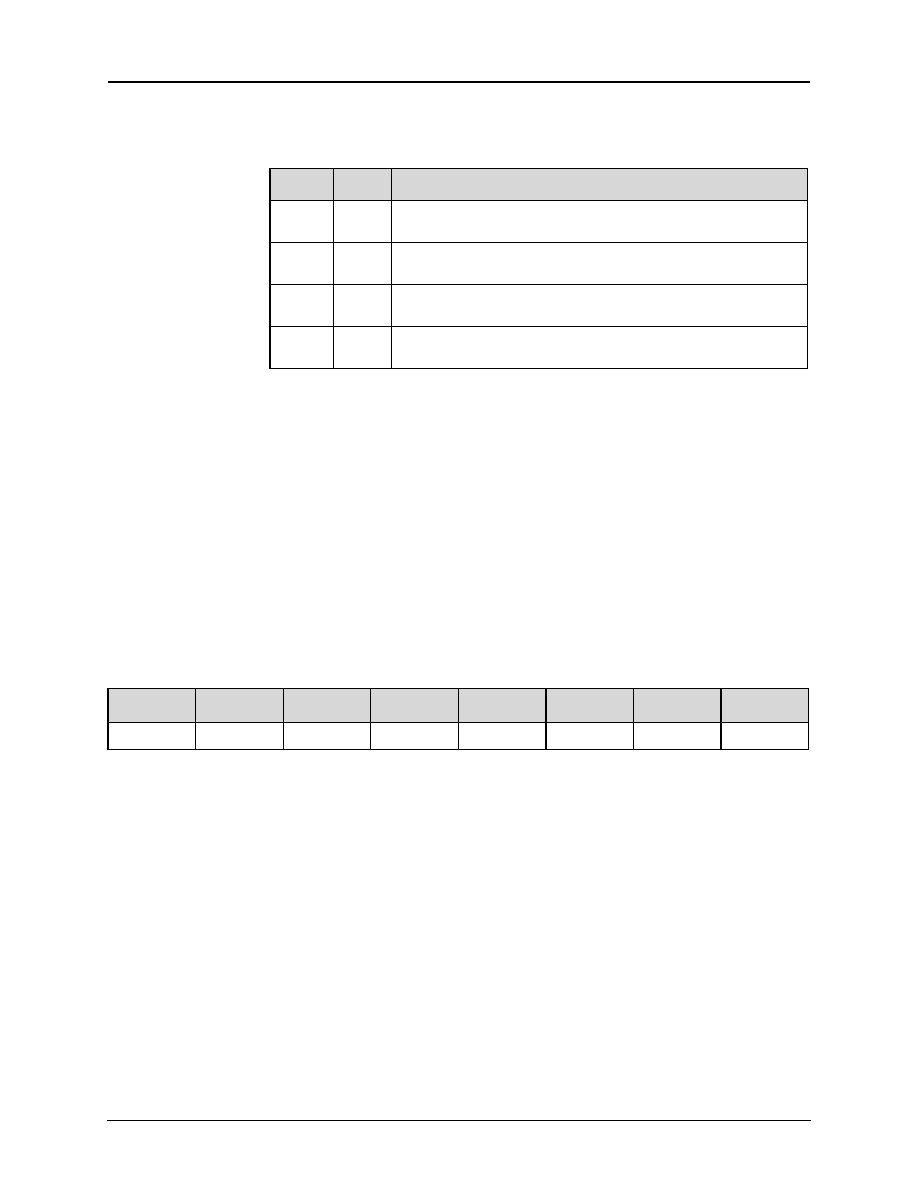

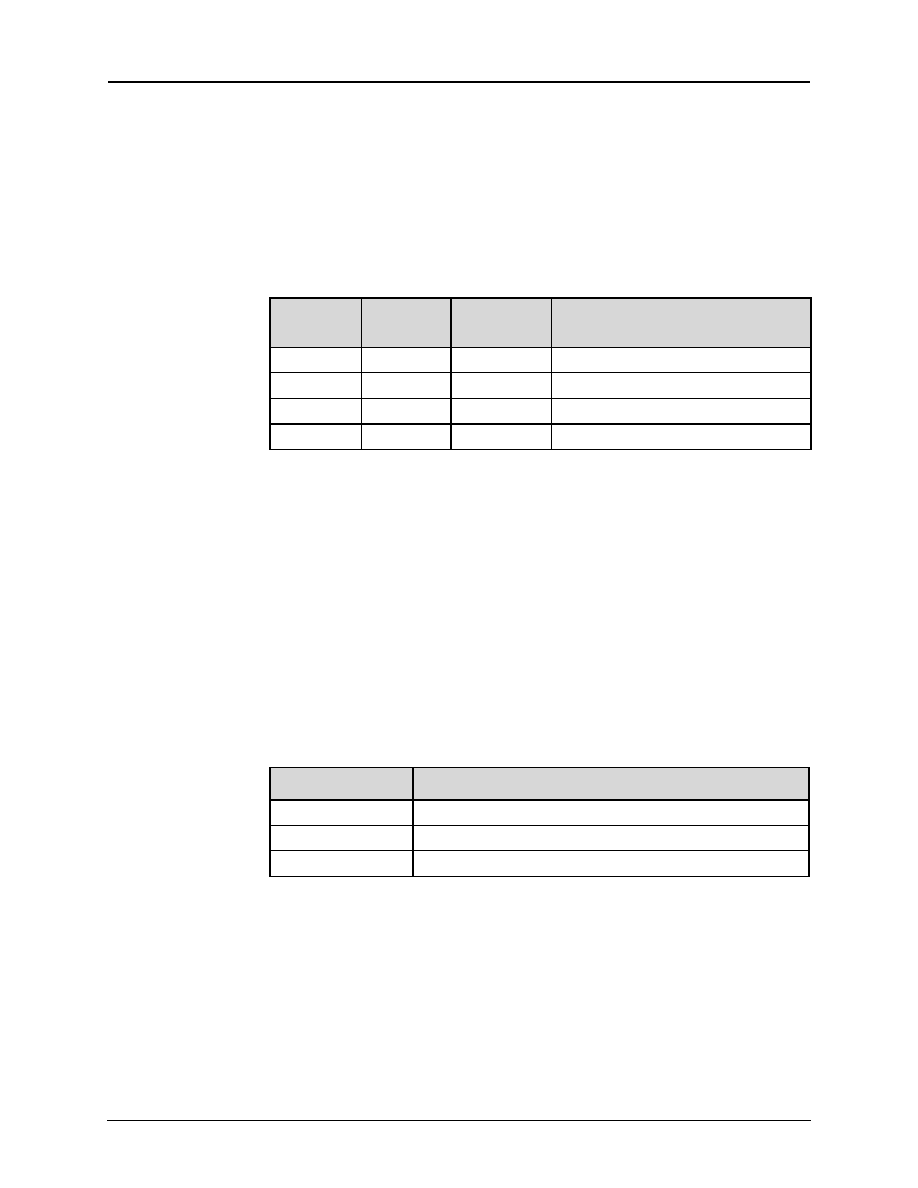

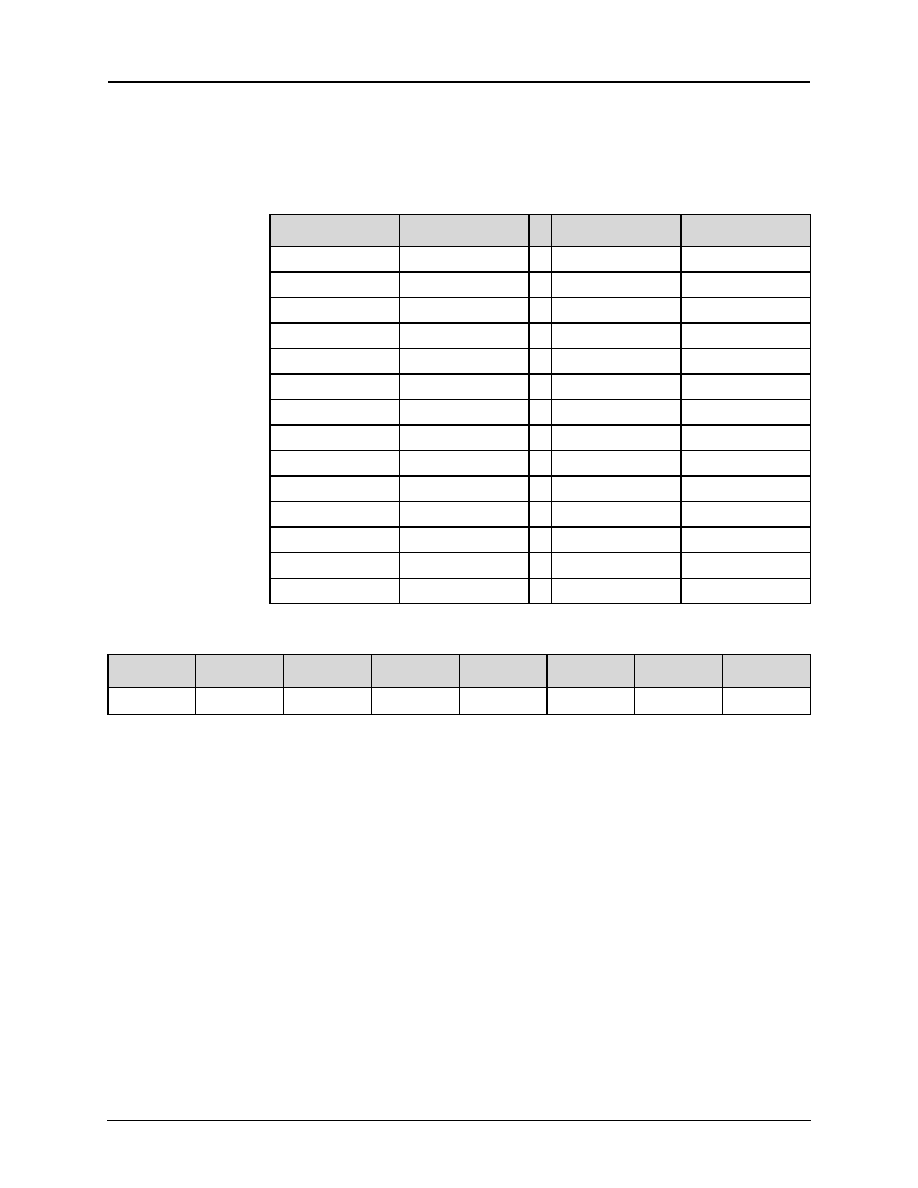

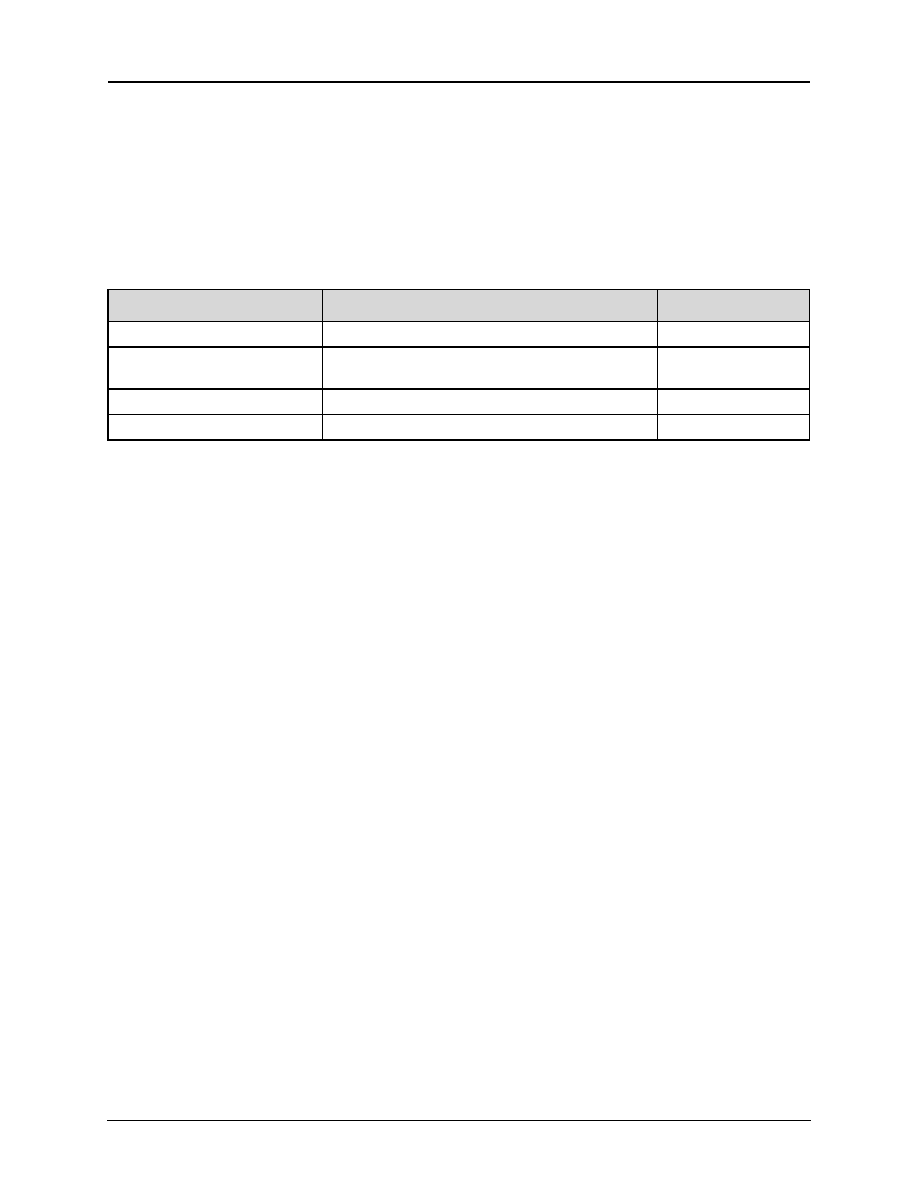

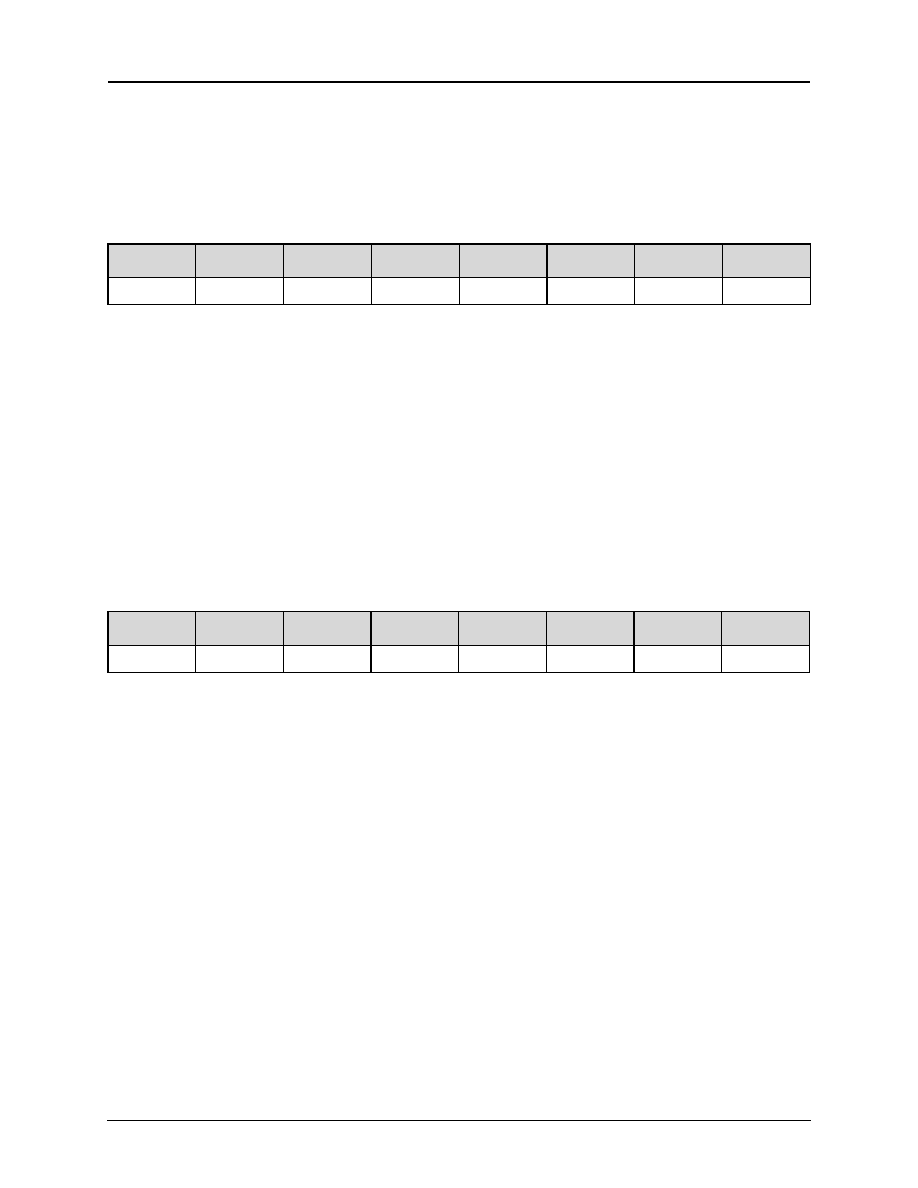

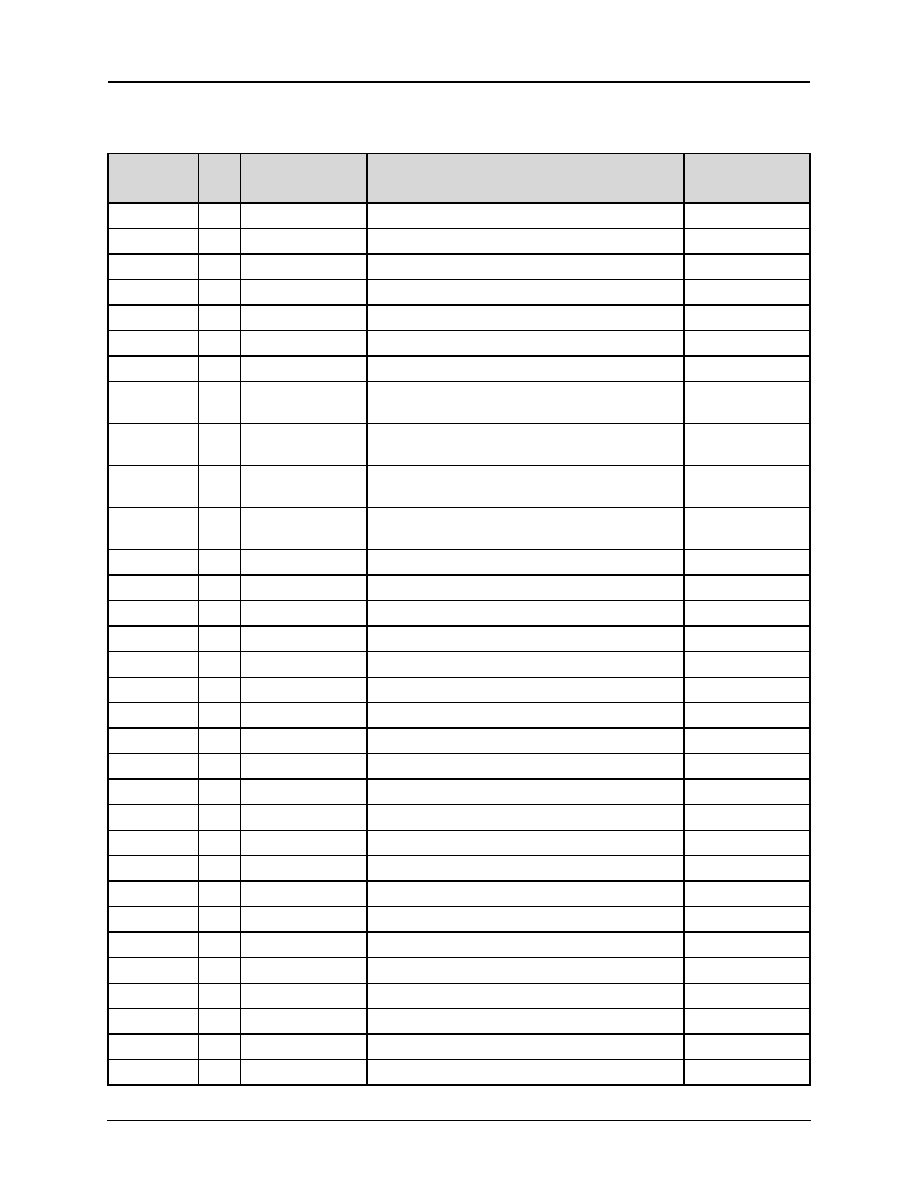

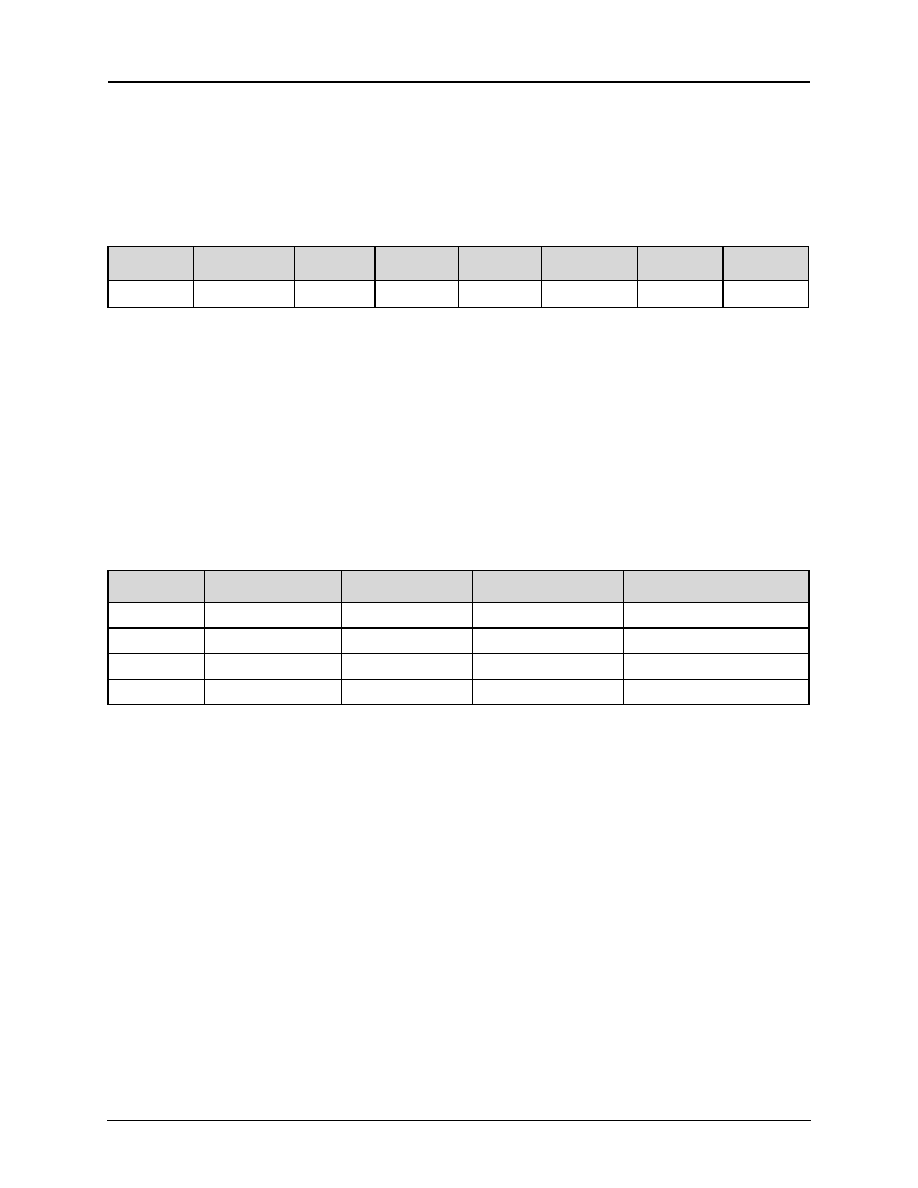

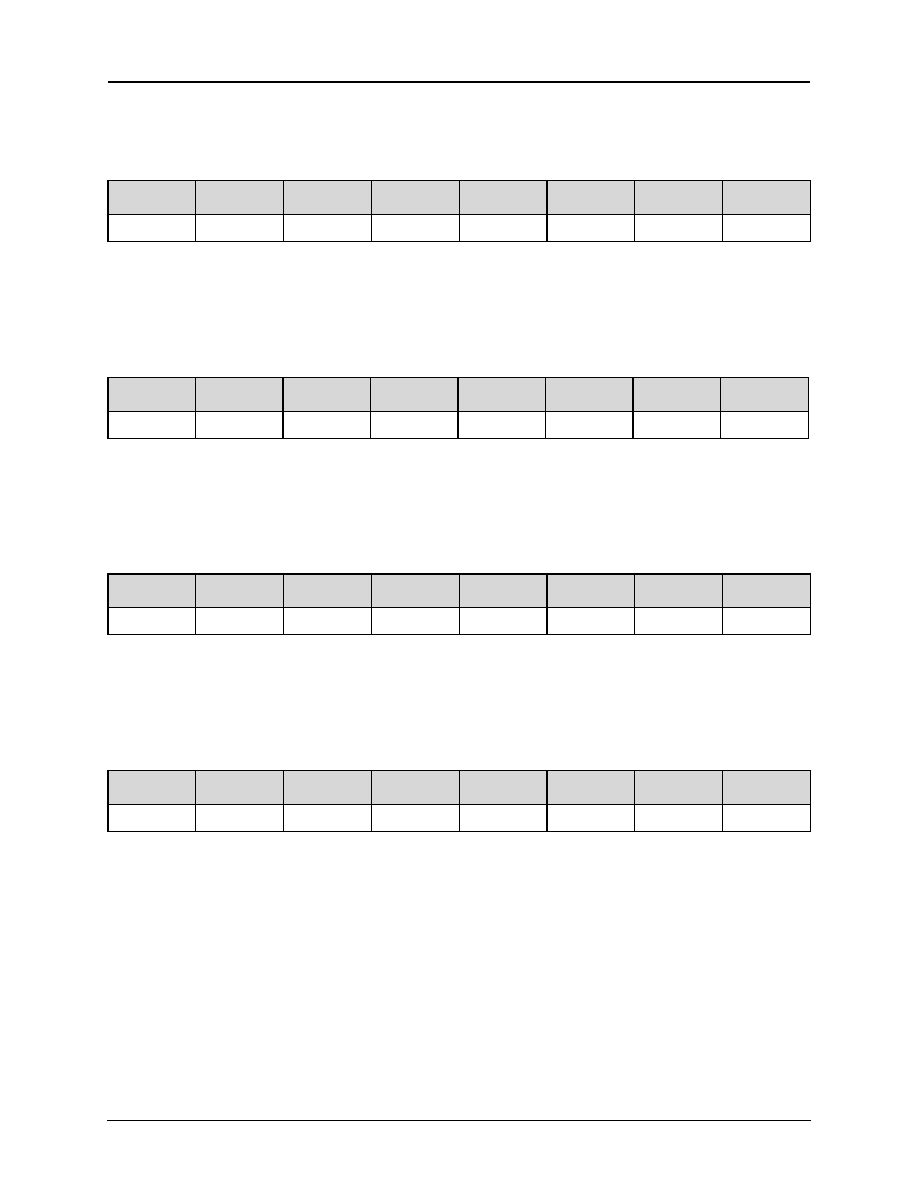

Ordering Information

Model Number

Package

Operating Temperature

CX29503

TBGA

-40

∞C to 85 ∞C

500238B

Mindspeed TechnologiesTM

iii

Advance Information

∑

Receive and mapping operation

using built-in digital jitter

attenuators; external PLL not

required.

∑

Standards-compliant Performance

Monitoring (PM) at the DS3/E3,

DS1/E1, VT1.5/VT2.0 levels.

STS-1-level PM is performed in the

accompanying SONET/SDH

multiplexer device (CX29610).

∑

Standards-compliant network alarm

detection and insertion for both

SONET/SDH and PDH signals.

∑

Dual edge network alarm indicators

reporting start and end of an alarm

condition with corresponding

maskable interrupts.

∑

Detects and counts errors for

SONET/SDH and PDH signals. Error

counter sizes are sufficient to count

one second of errors without counter

saturation in the presence of up to a

10

-3

error rate.

≠ Error counters operate in two

modes:

∑

one-second mode-counter

values are latched on a

one-second boundary

∑

count to saturation mode

∑

Embedded CSP state machine

∑

Performs device access

activities by communicating

with the host processor via

HDLC command/response

packets.

∑

Automates device activities by

internally responding to

network events, reducing

real-time requirements on the

host processor.

∑

Full data link support at the SONET

STS-1/VT1.5/VT2.0. SDH VC-11,

VC12, and PDH DS3/E3, DS1/E1/J1

levels.

∑

Full line and system side loopback

support:

≠ Line loopbacks: STS-1/TUG-3,

DS3/E3, DS2/E2, DS1/E1/J1

≠ System loopbacks: STS-1,

DS3/E3

∑

Complies with GR 253-CORE,

TR-TSY-000009, T1.105, T1.231, T1.403,

T1.404, G.707, G.742, G.743, G.747,

G.751, G.752, G.781, G.783, ETS300.147,

ETS300.417-1-1

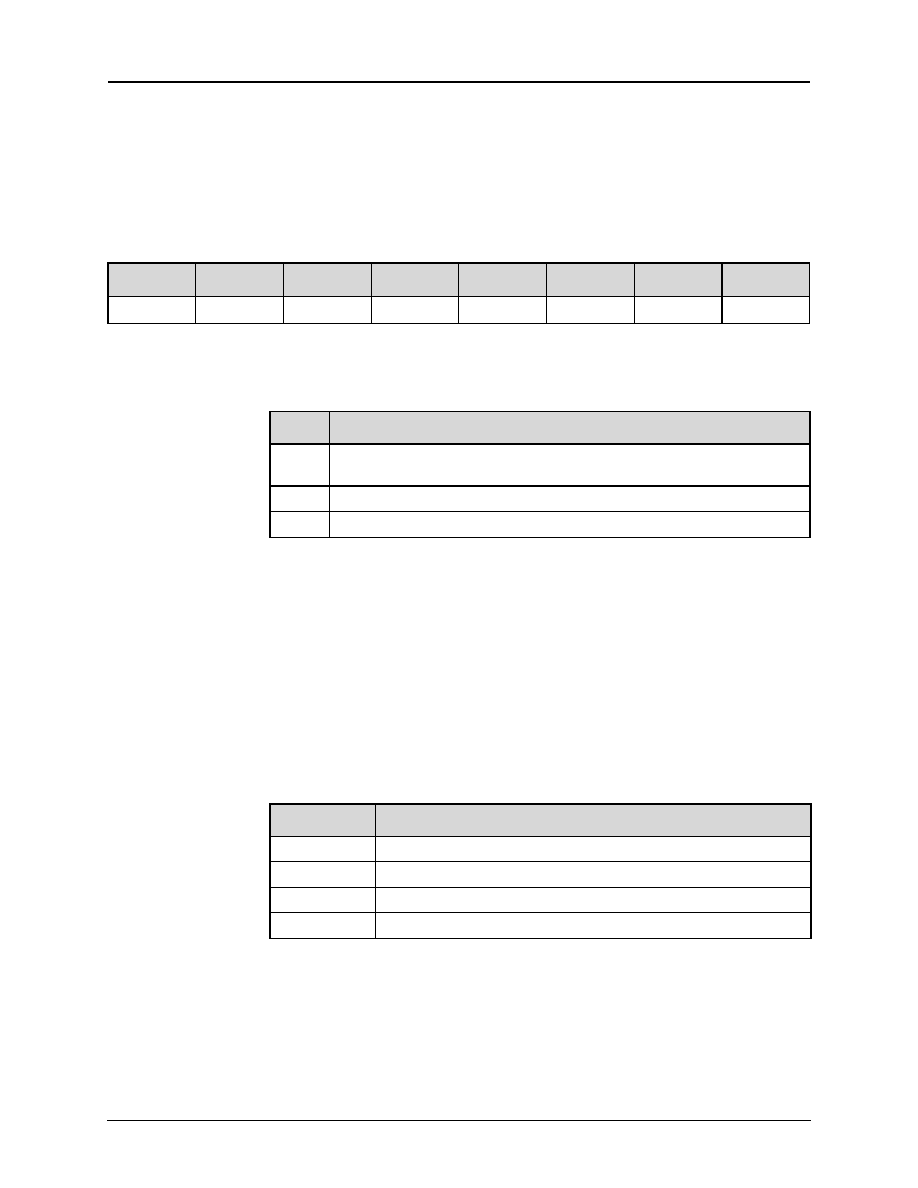

≠ Power Supplies/Power

Consumption

≠ Requires 3.3 V and 1.8 V power

supplies

∑

3.3 V input/output

∑

1.8 V core

∑

Optional 5 V power supply for

5 V input tolerance

∑

Power consumption

≠ under 2 Watts

∑

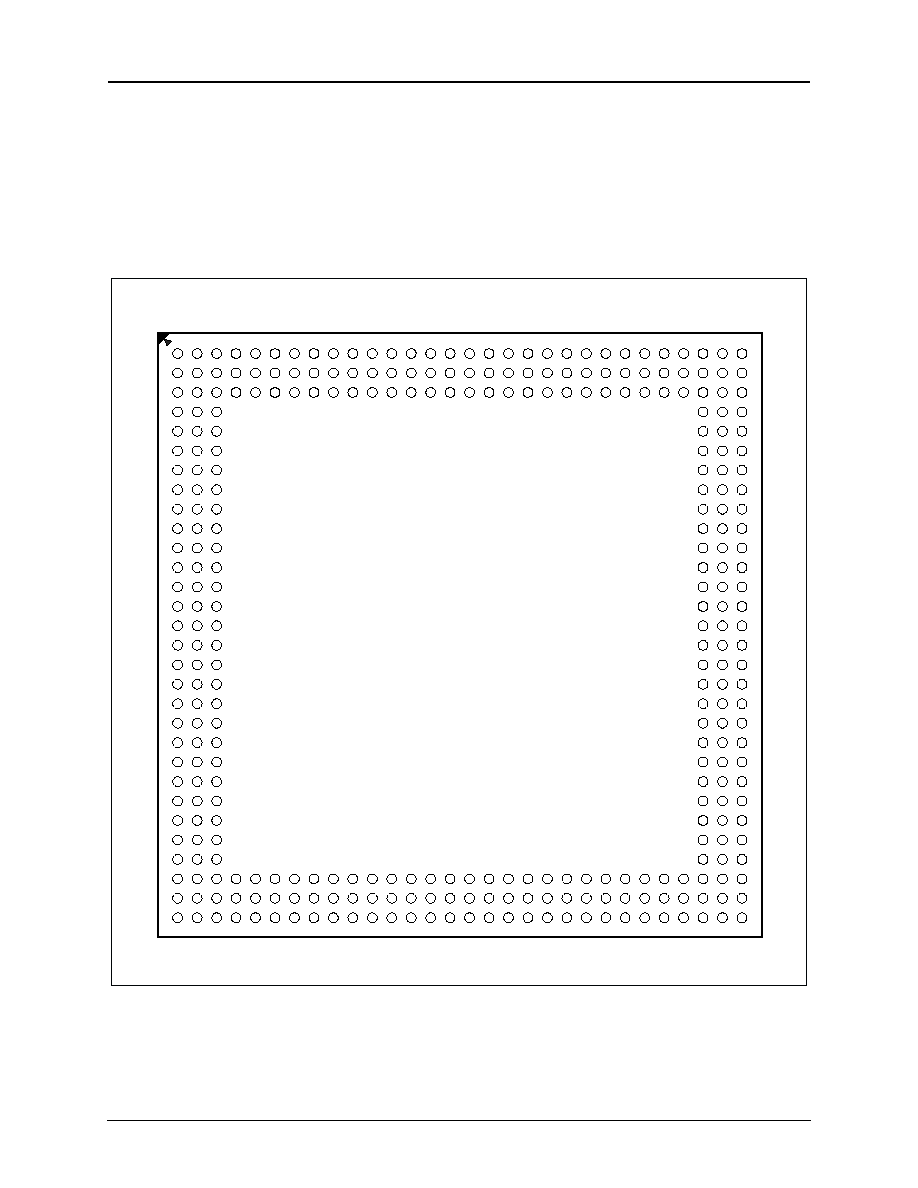

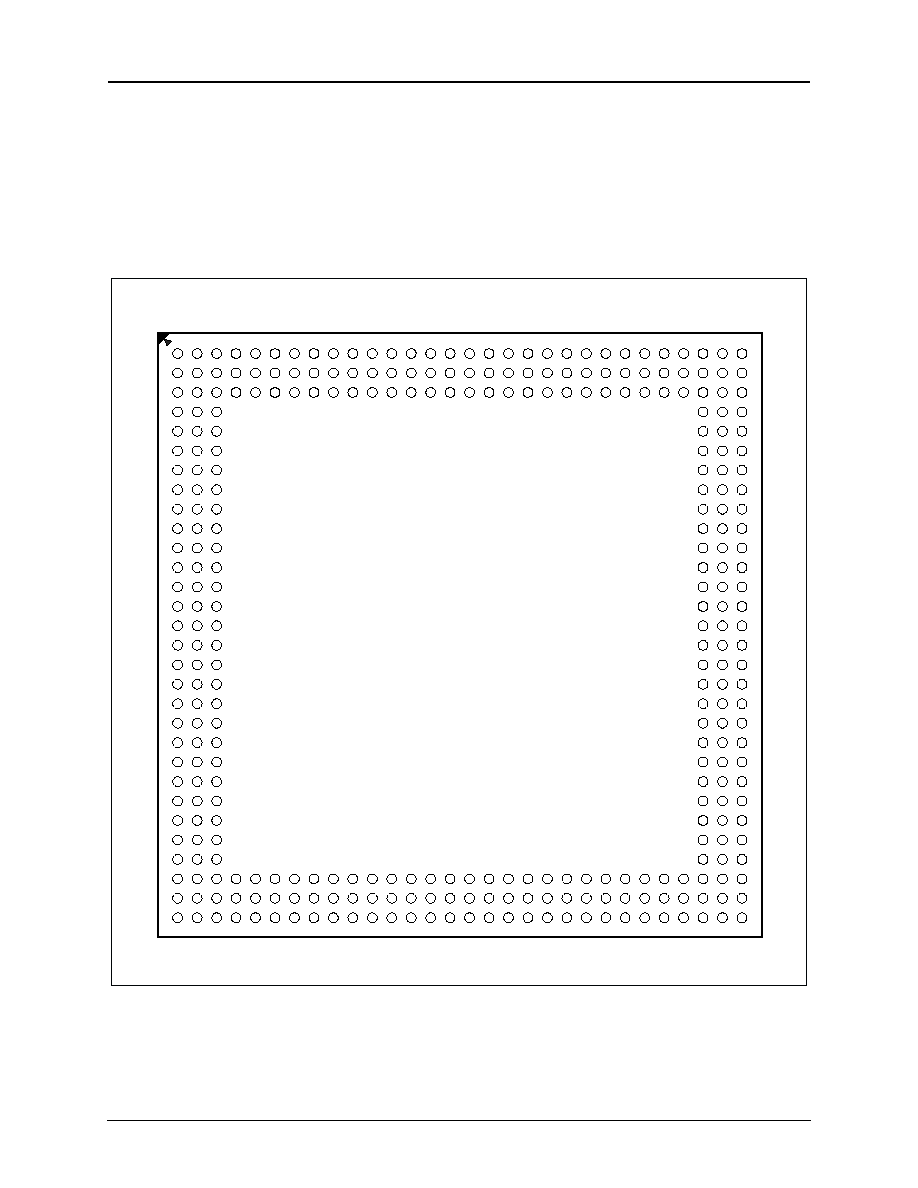

Package: 31 mm, 324 ball TPBGA

with a heat spreader.

∑

Operating temperature: ≠40 to 85 ∞C

∑

Testing: JTAG boundary scan

support

Applications

∑

Routers

∑

Access Concentrators

∑

Multiservice Switches

∑

T1/T3 Frame Relay Switches

500238B

Mindspeed TechnologiesTM

iv

Advance Information

500238B

Mindspeed TechnologiesTM

i

Advance Information

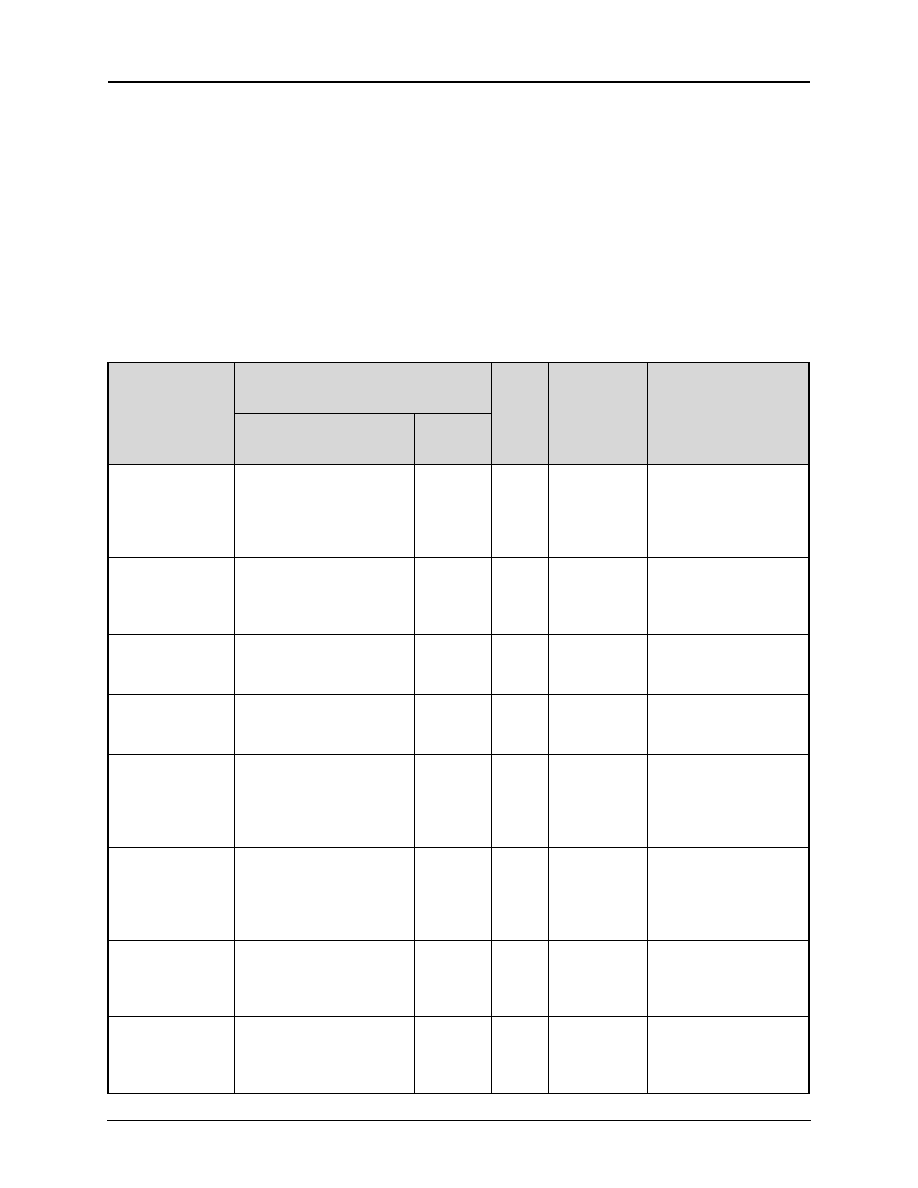

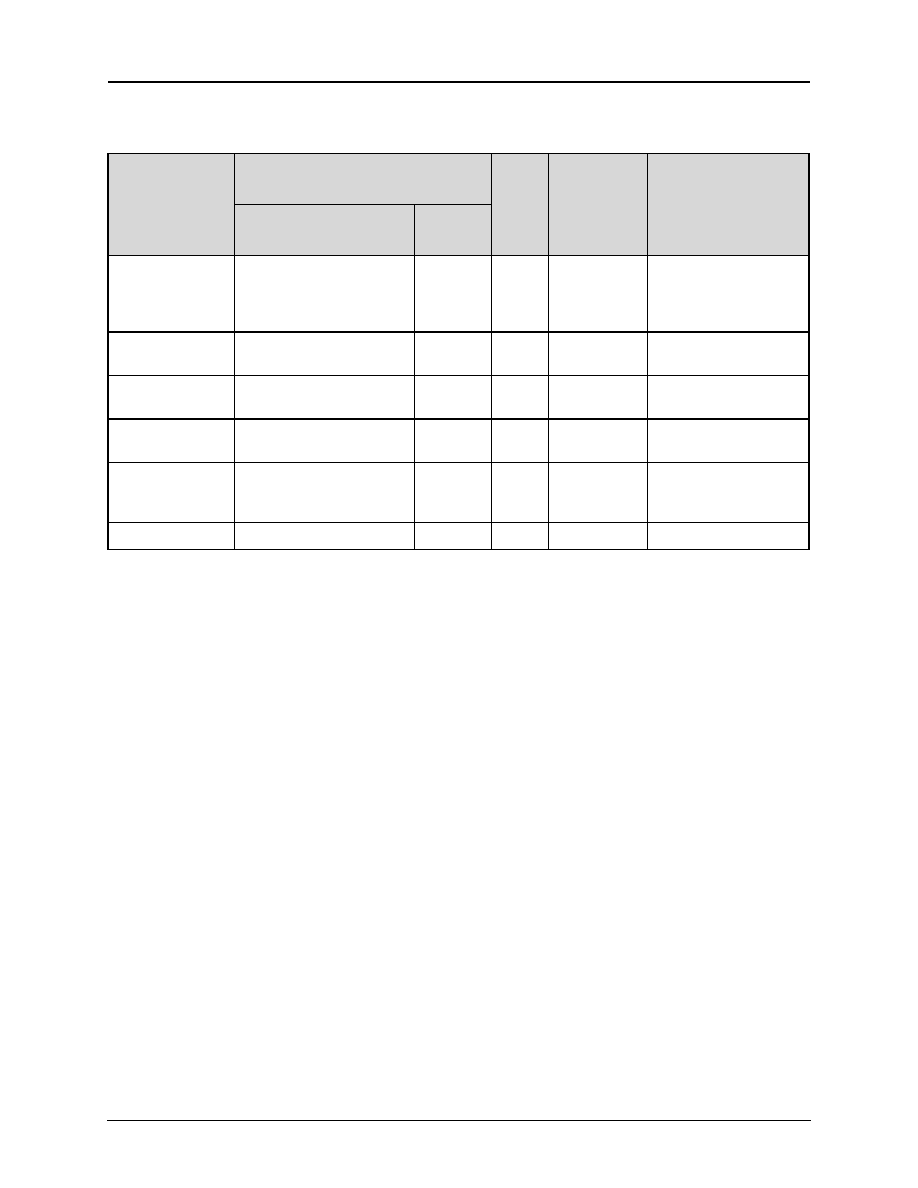

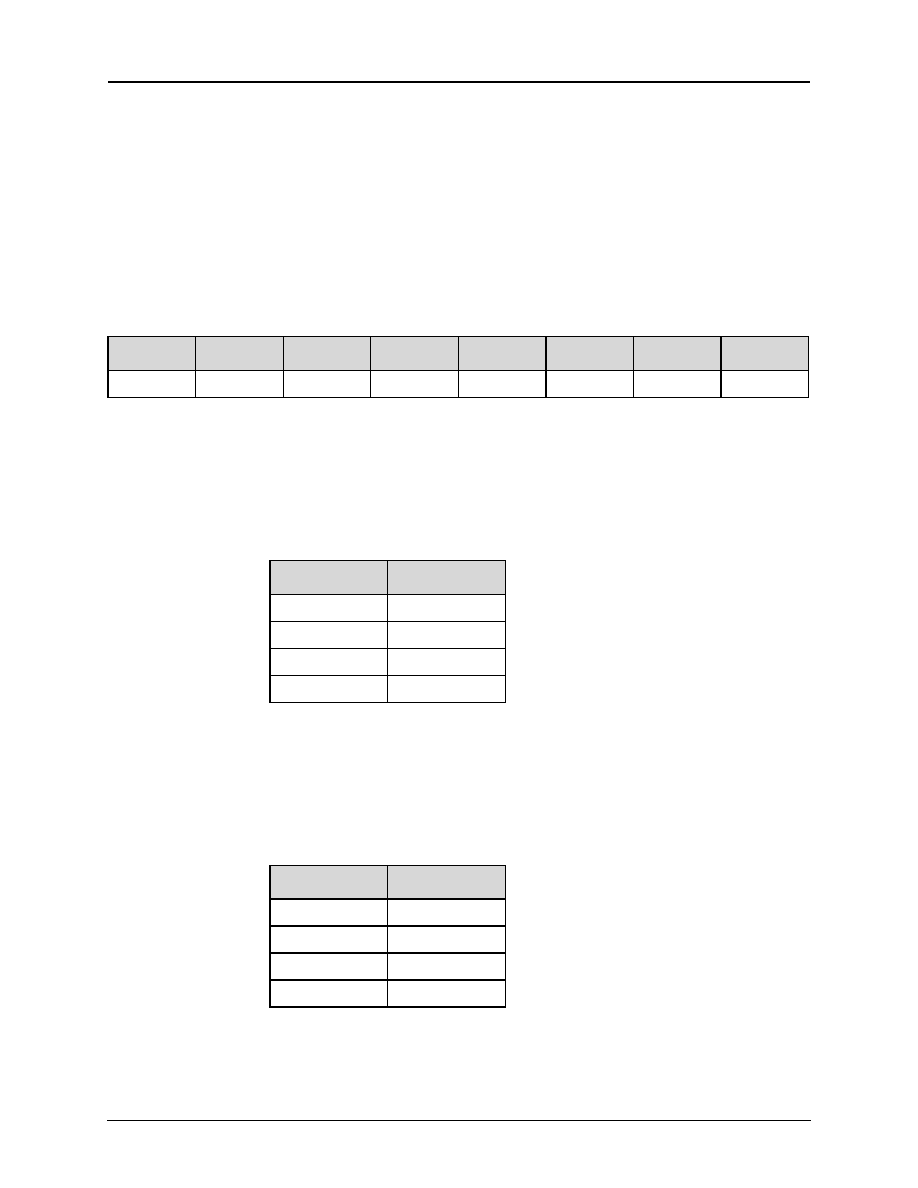

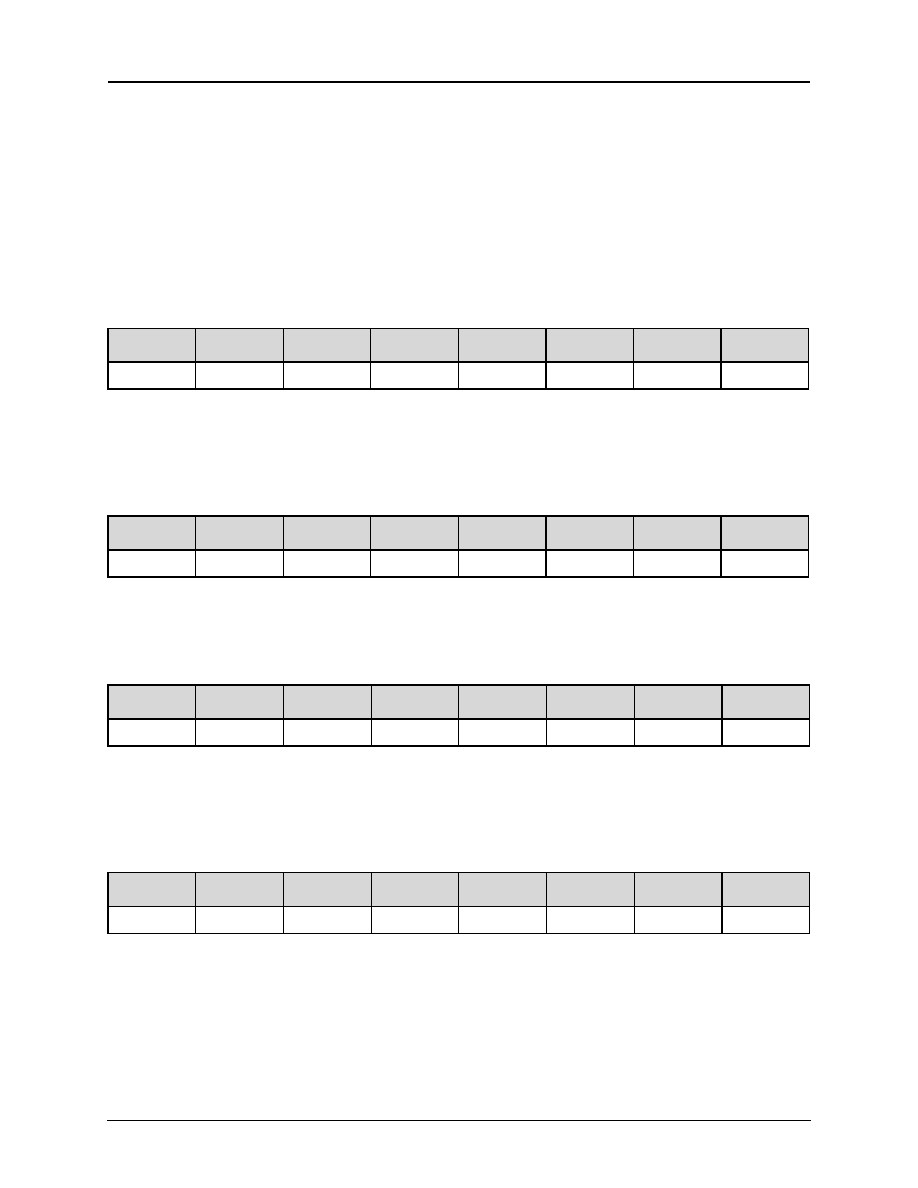

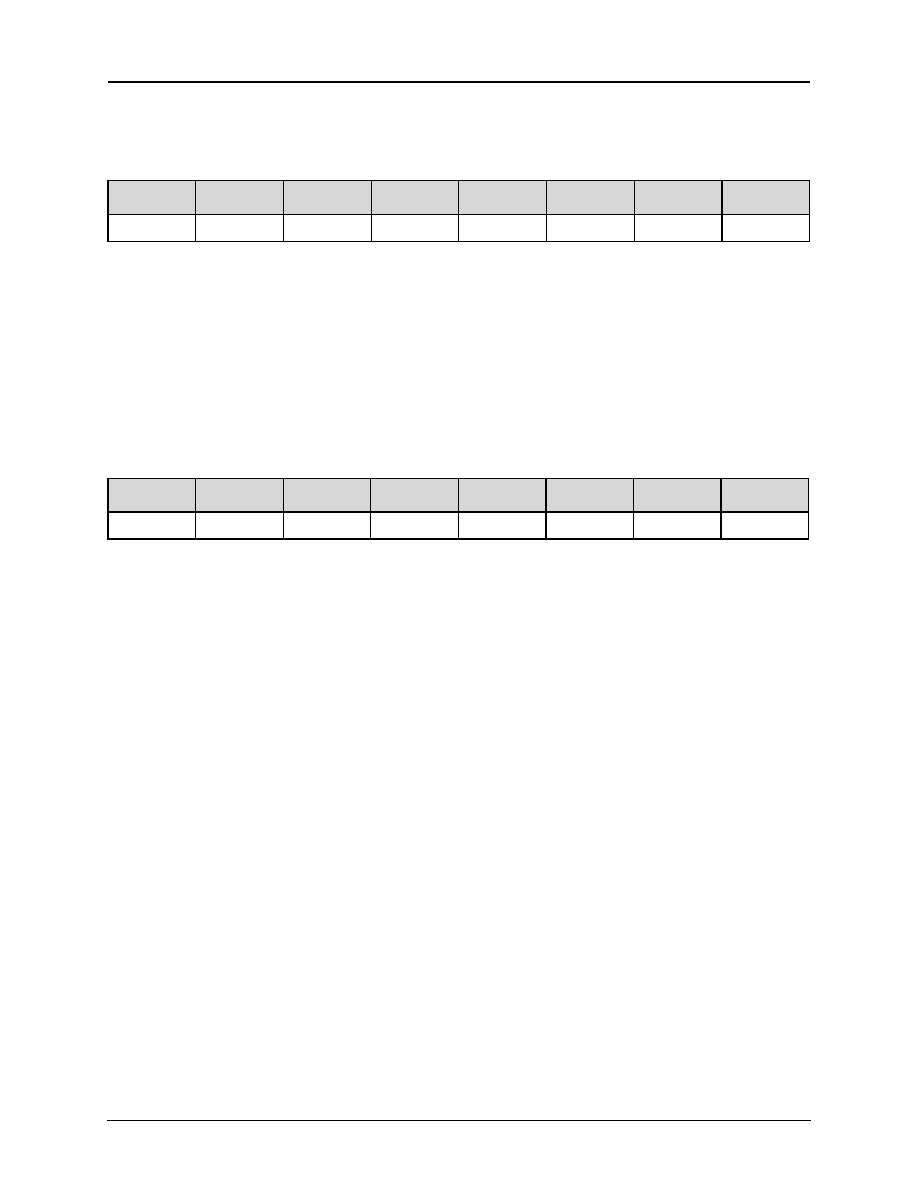

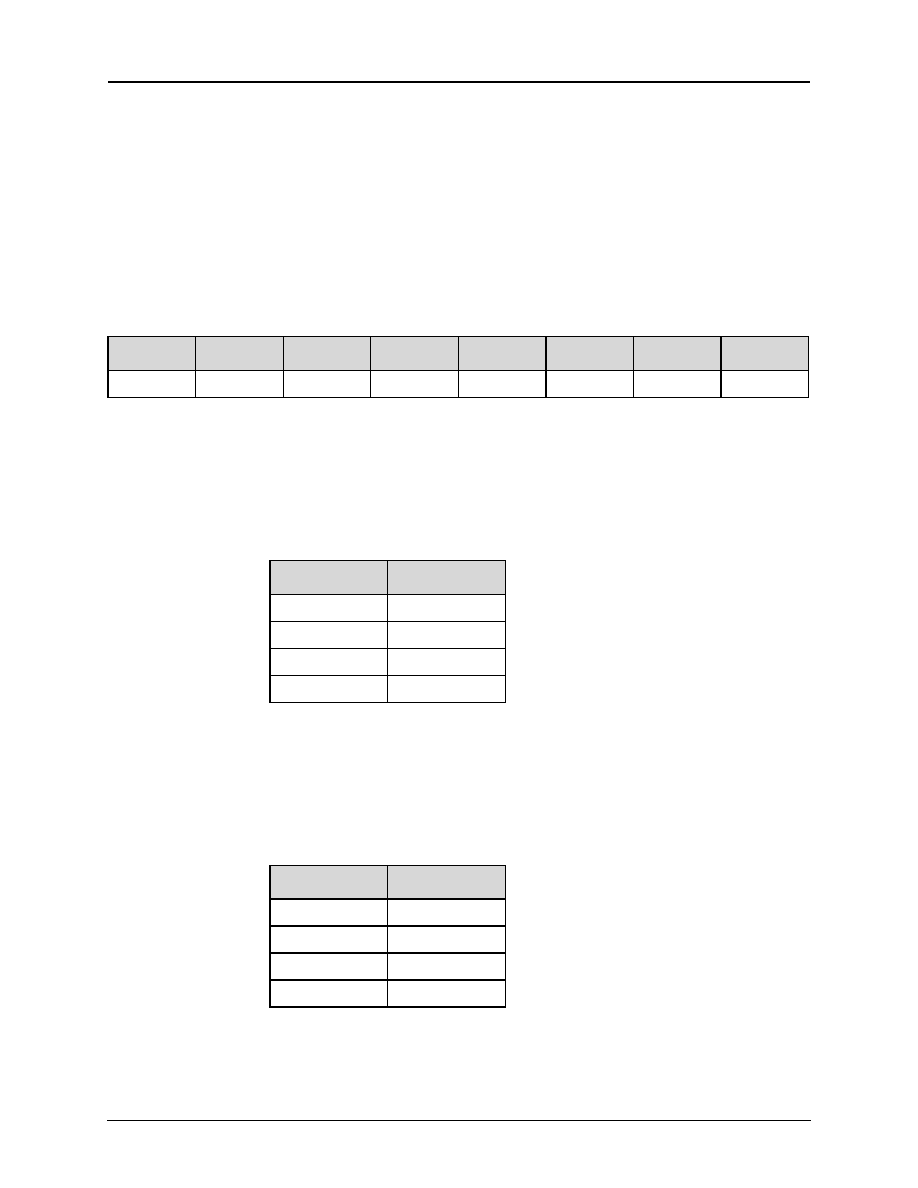

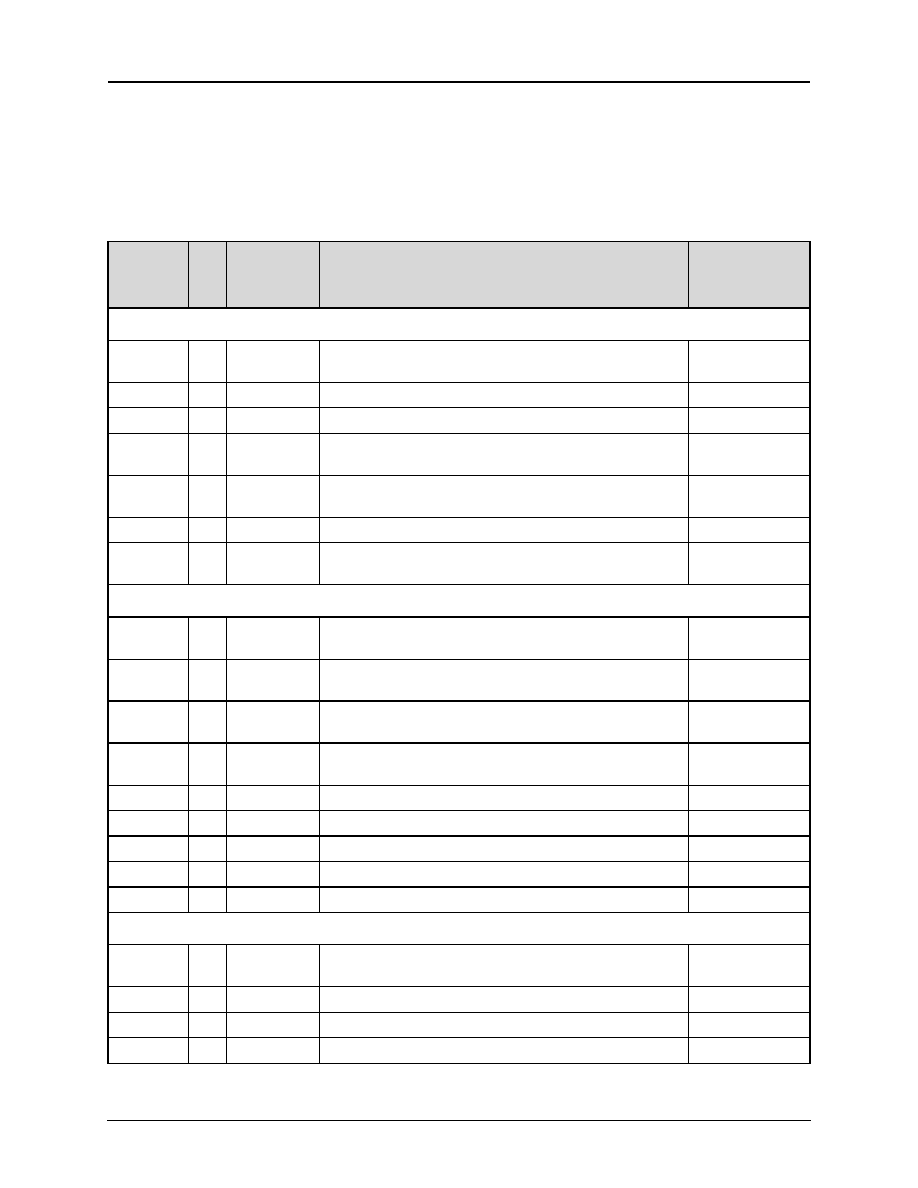

Contents

Figures

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .xvii

Tables

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xix

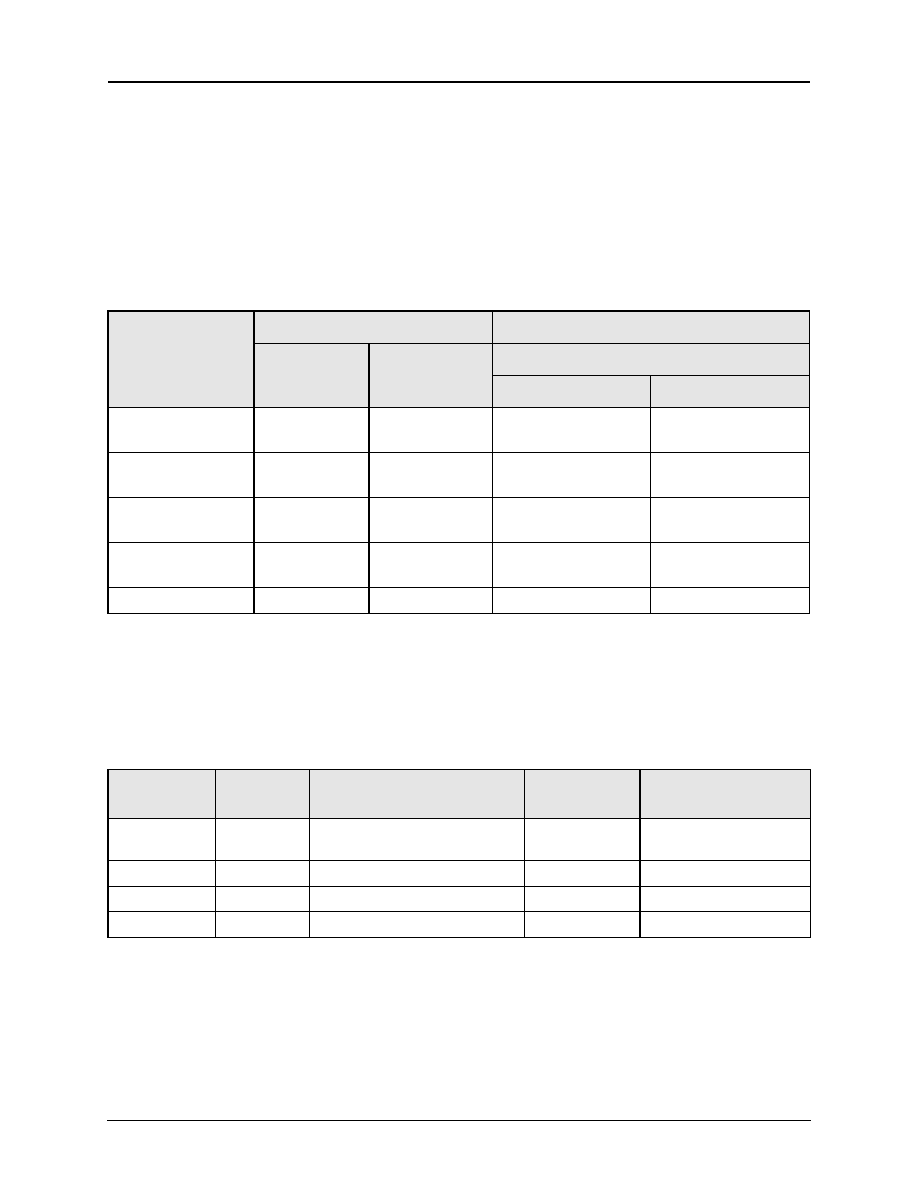

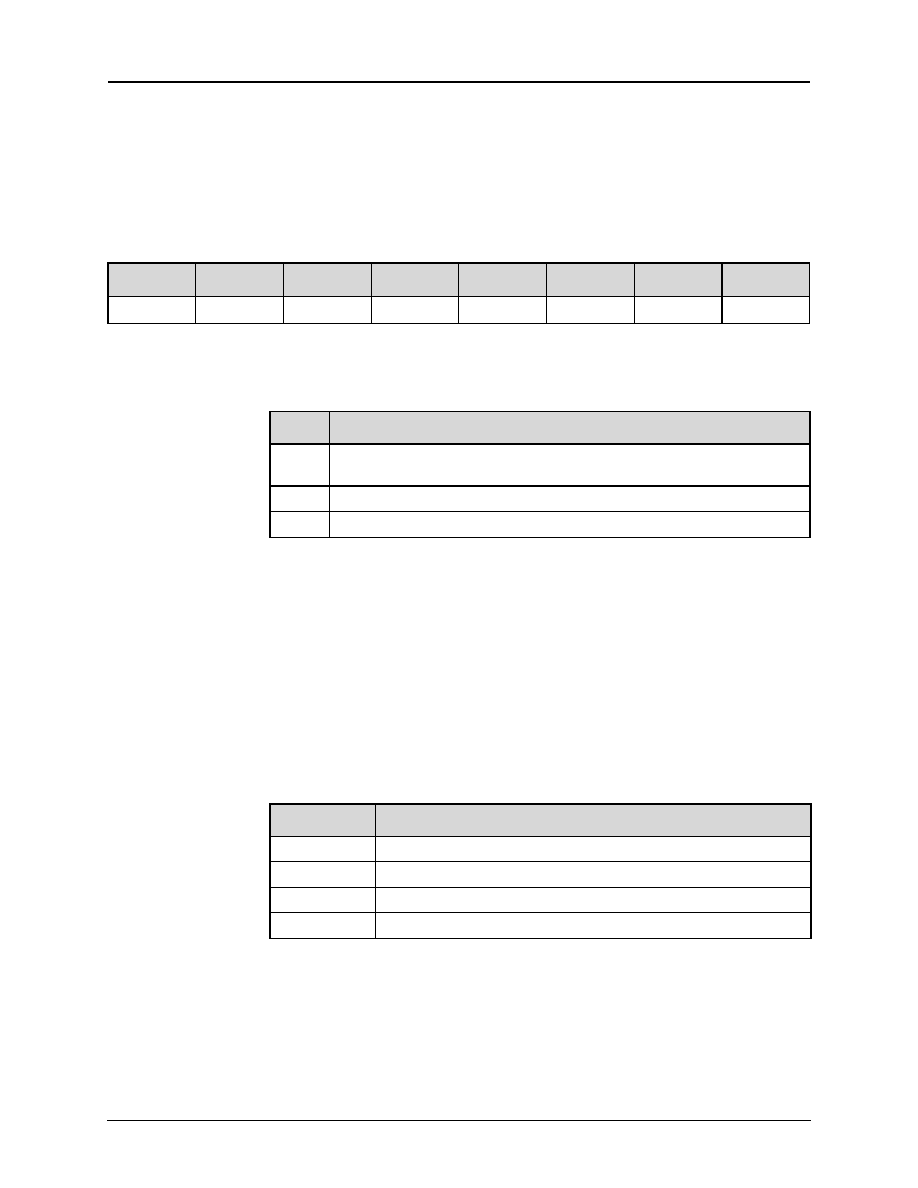

1.0 Product Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.1

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.2

Line Side Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

1.2.1

Line Side Serial Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

1.2.2

SONET Interleave Bus (SI-Bus) Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

1.3

System Side Interfaces≠Time Slot Bus (TSB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

1.4

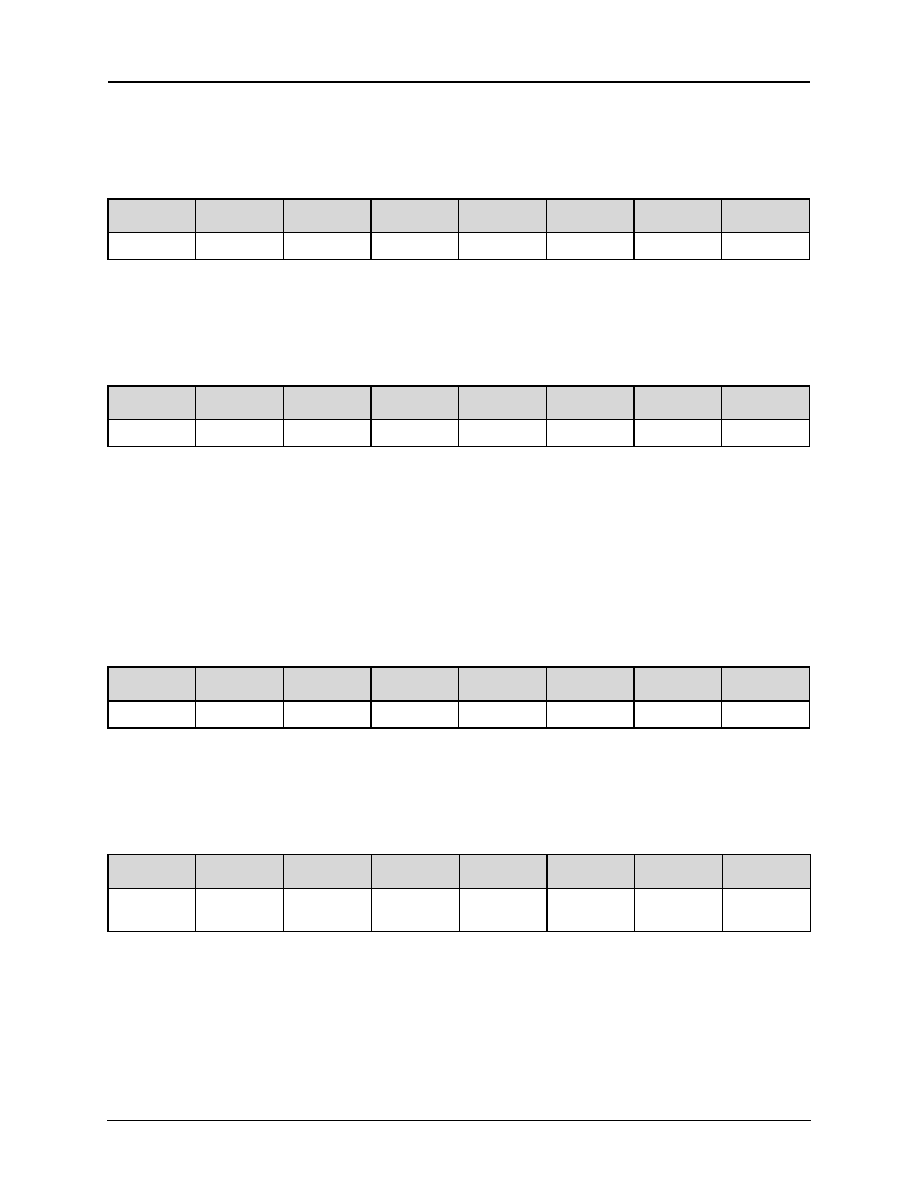

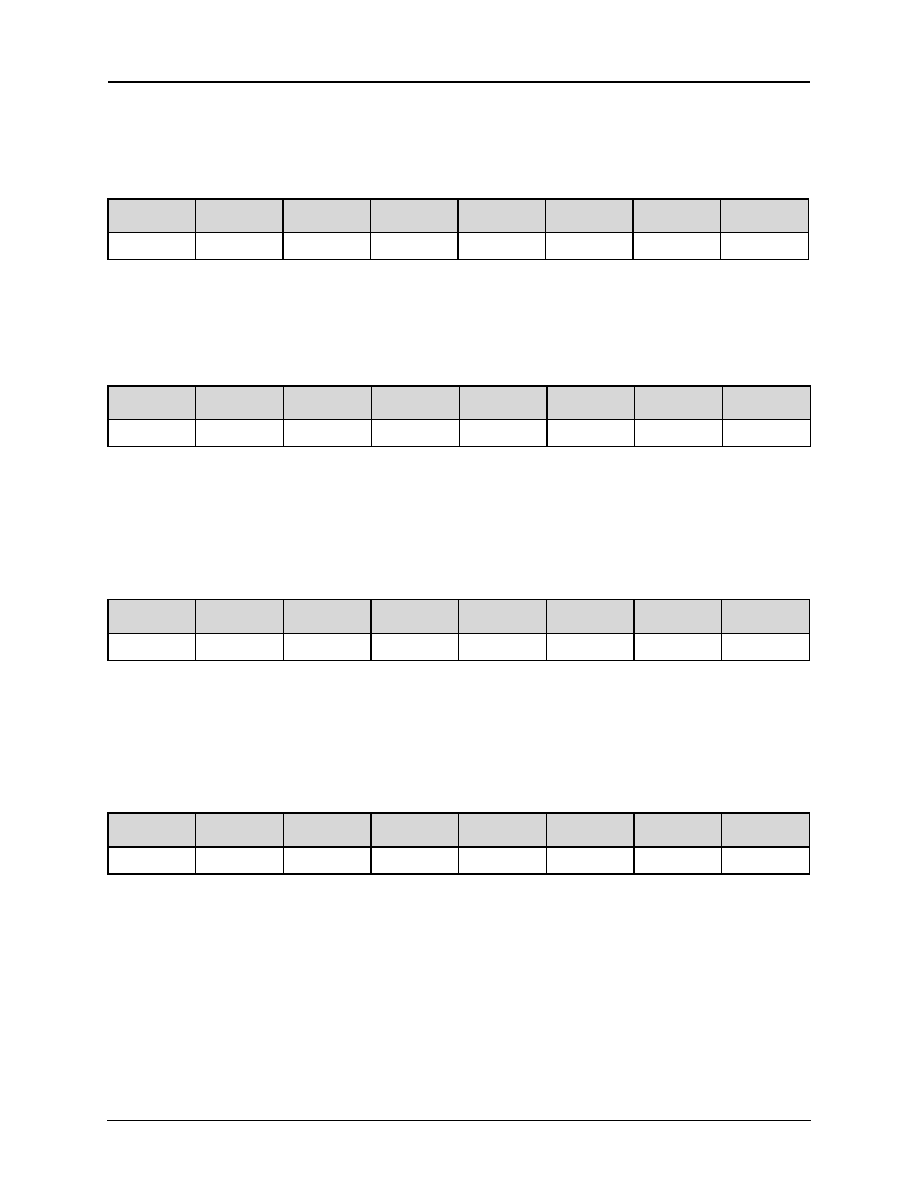

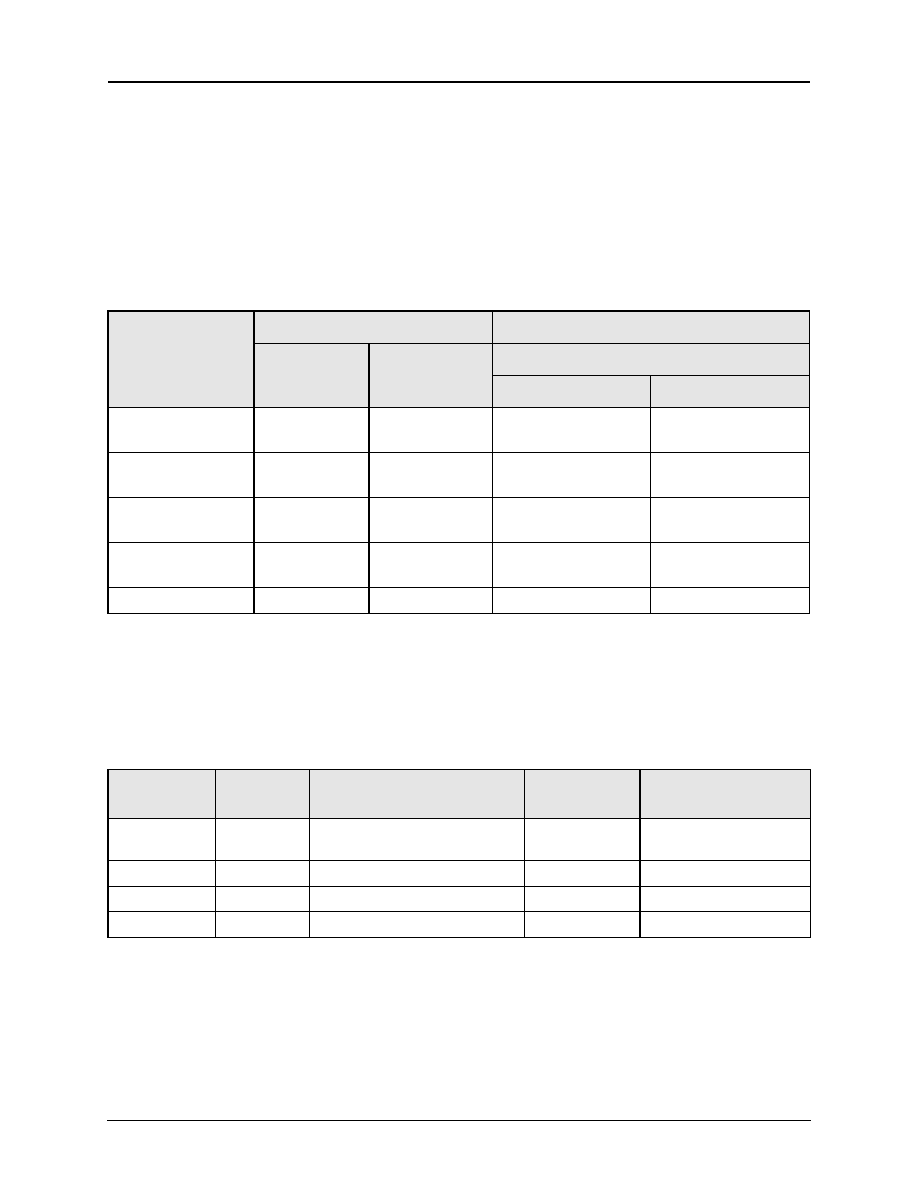

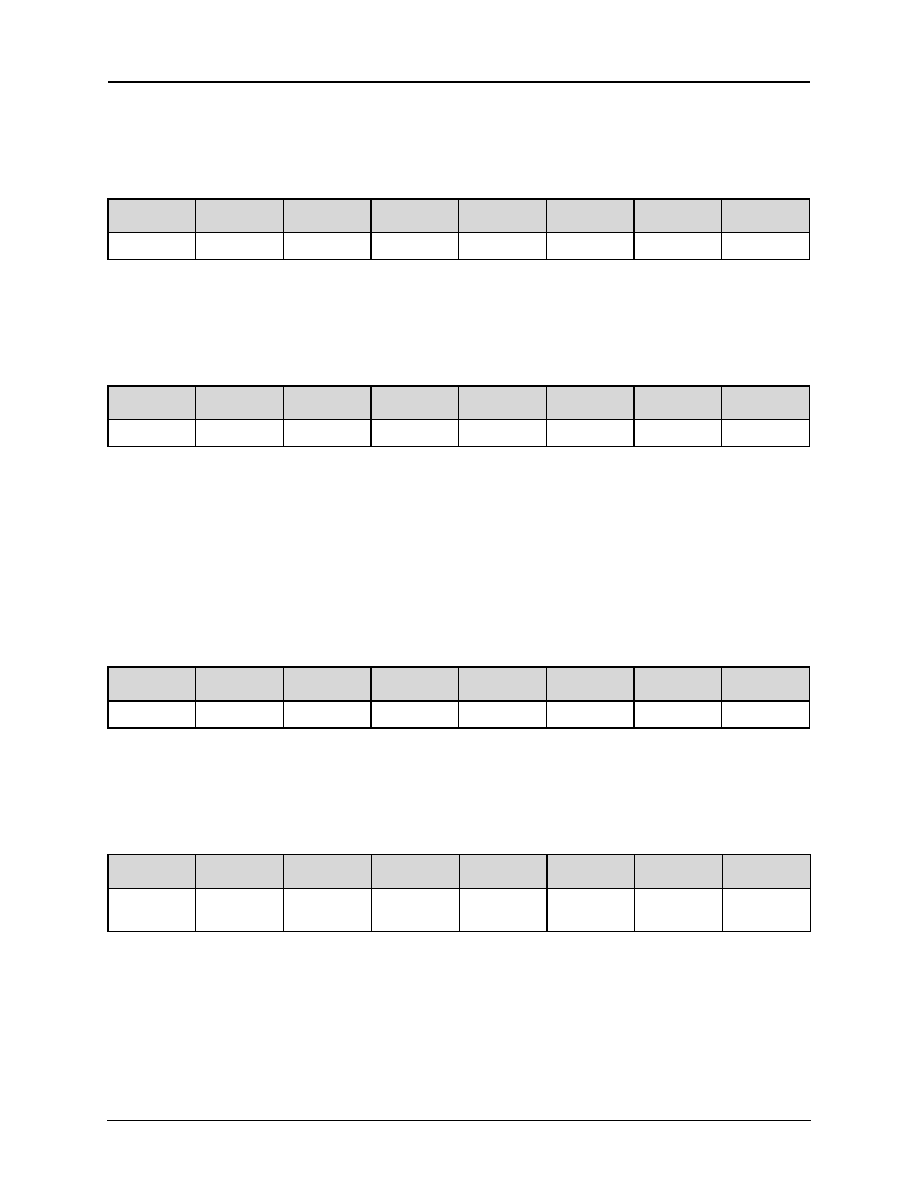

Supported Multiplexing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

1.5

Supported Mapping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

1.6

Embedded Framers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

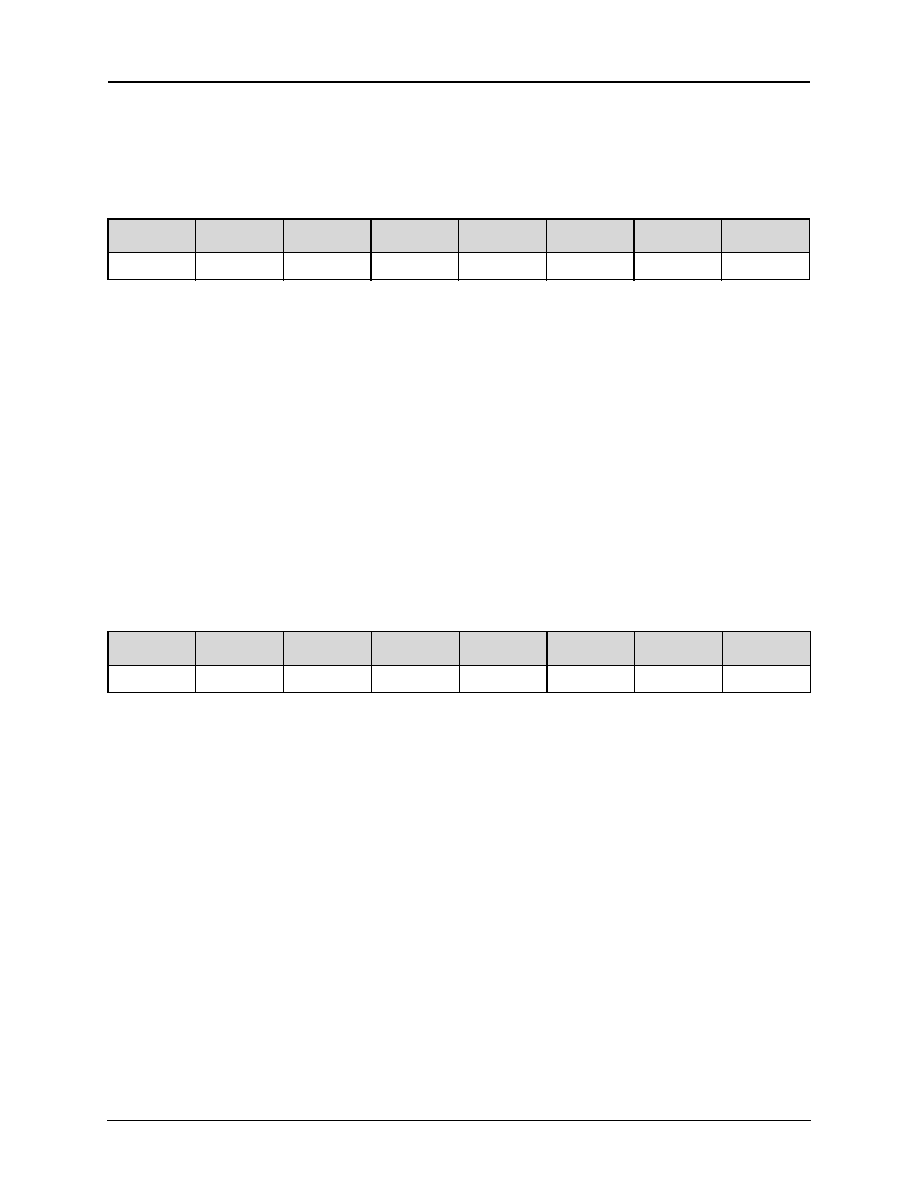

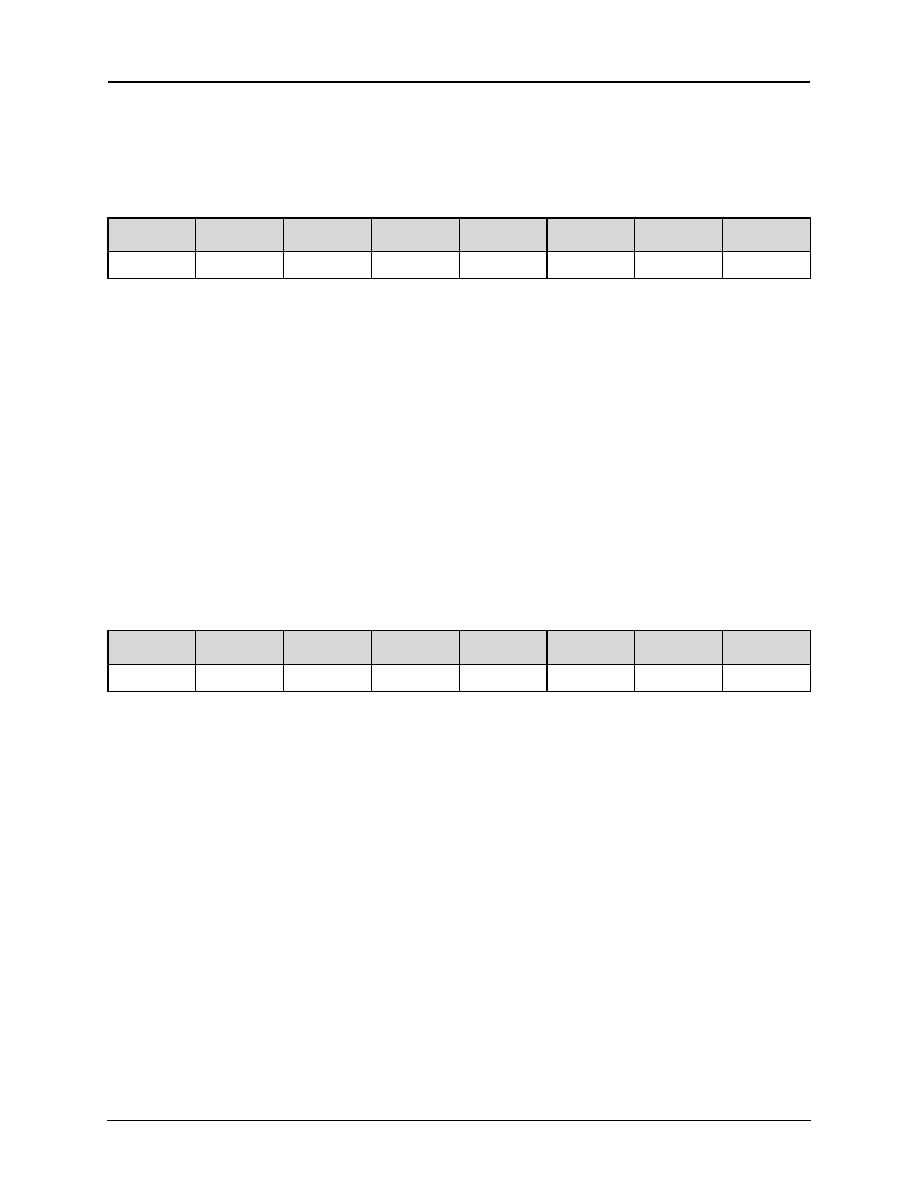

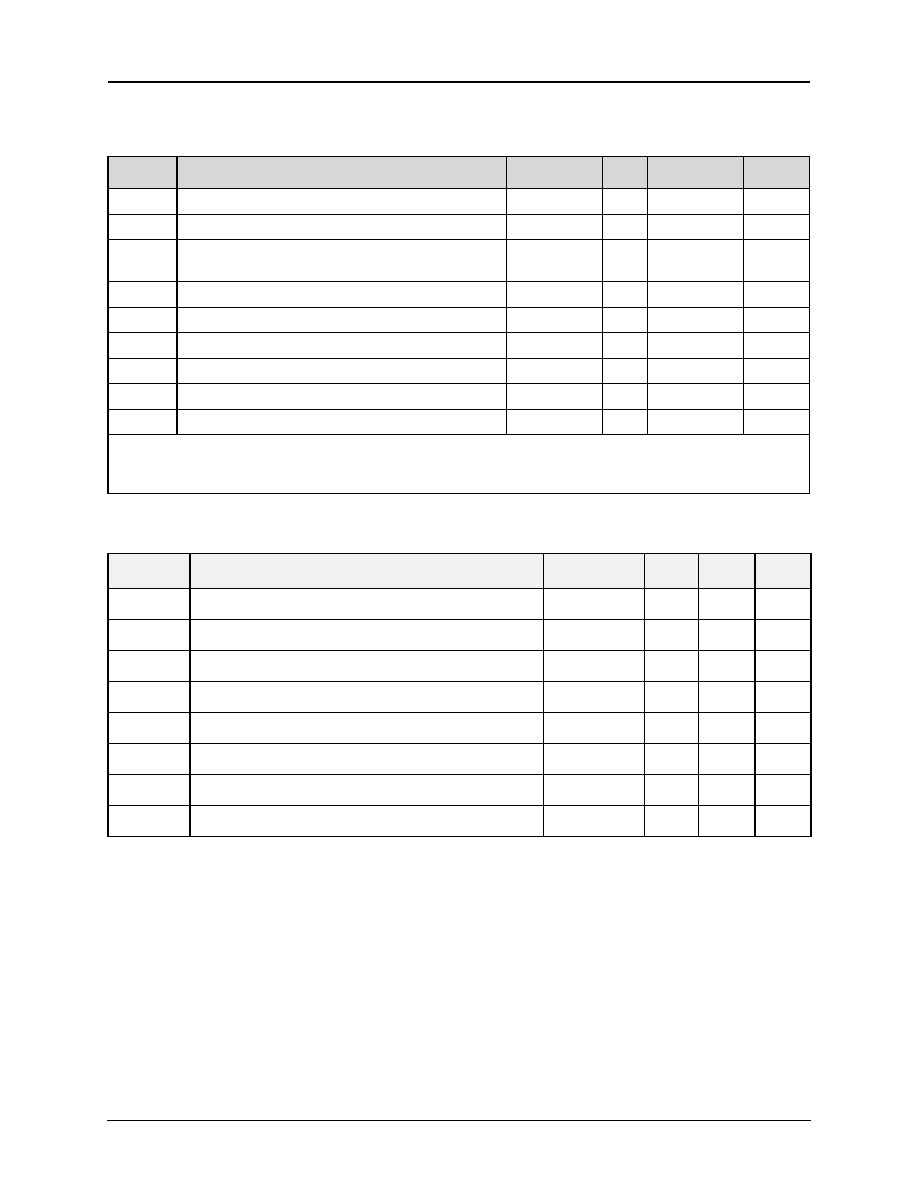

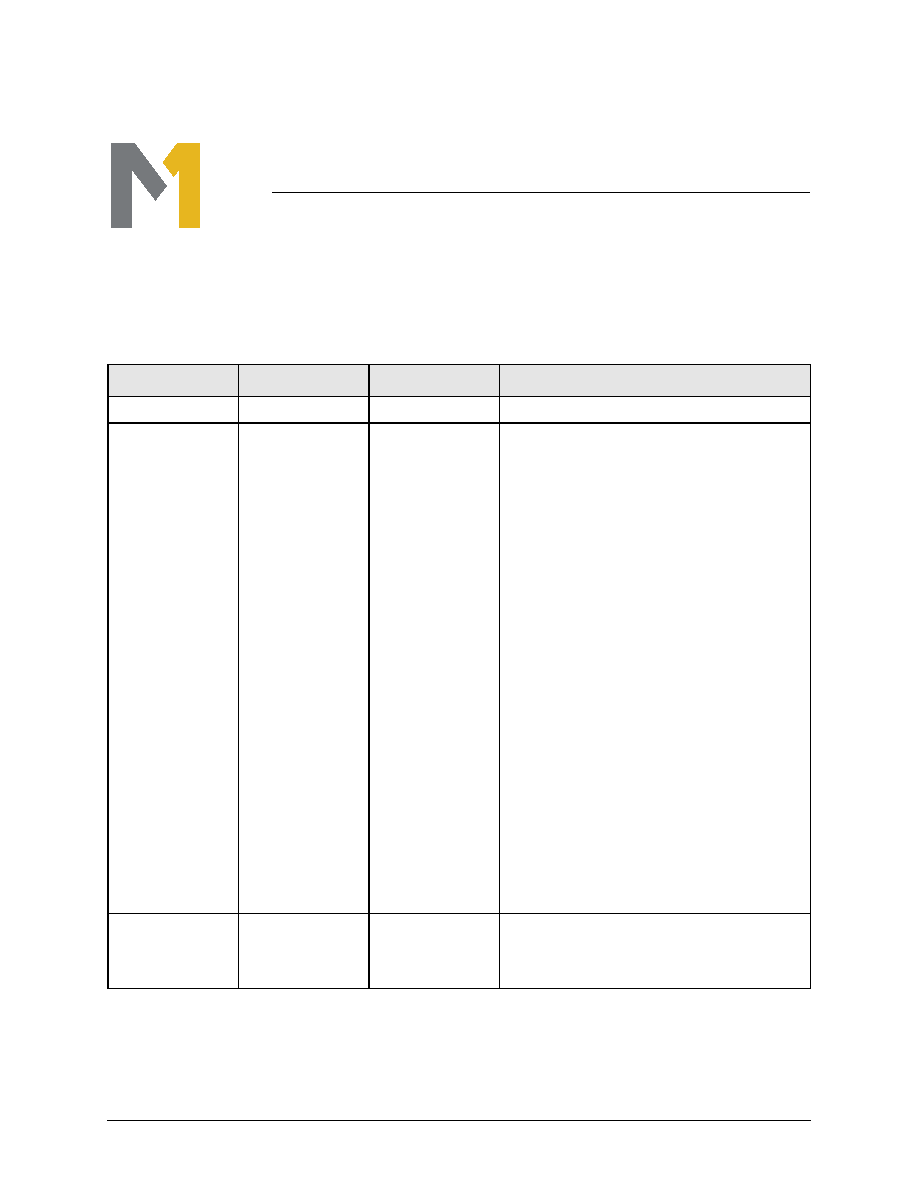

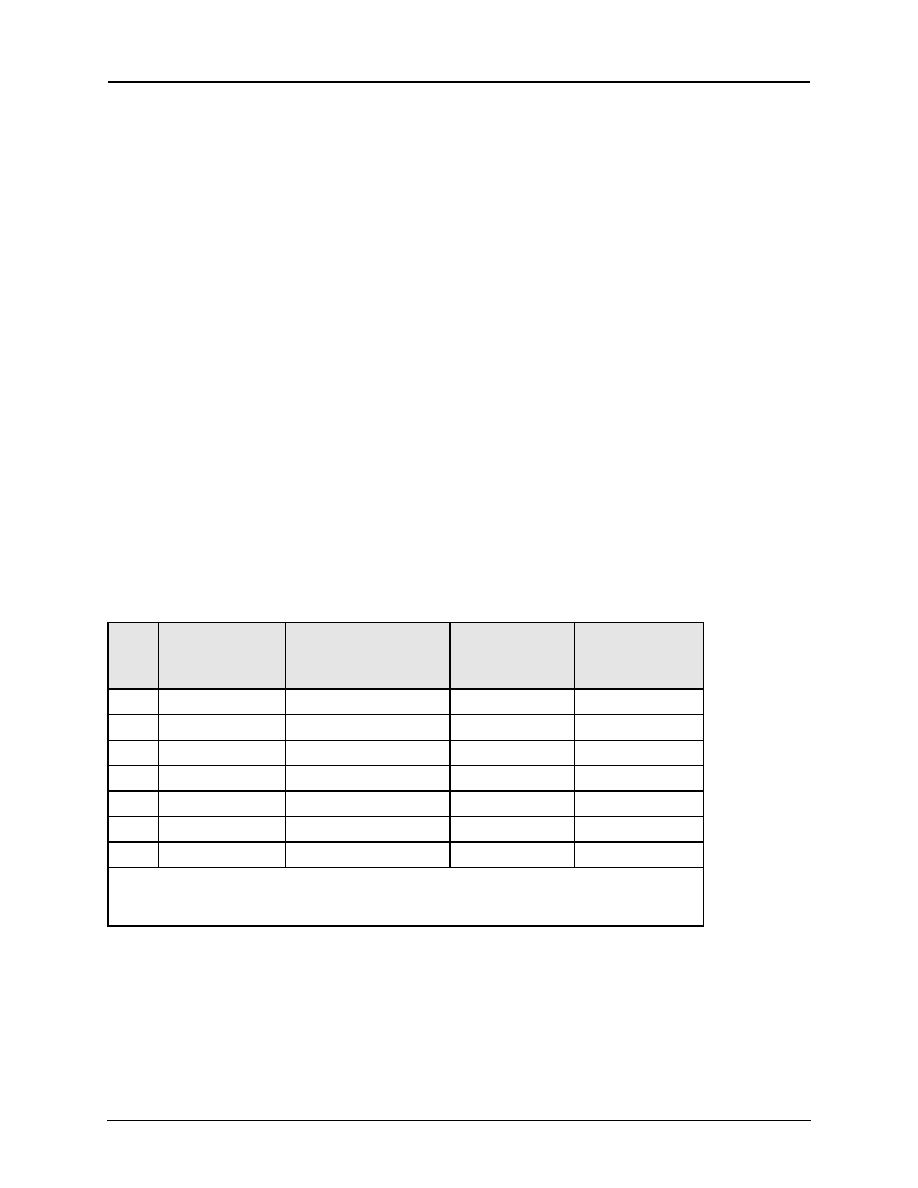

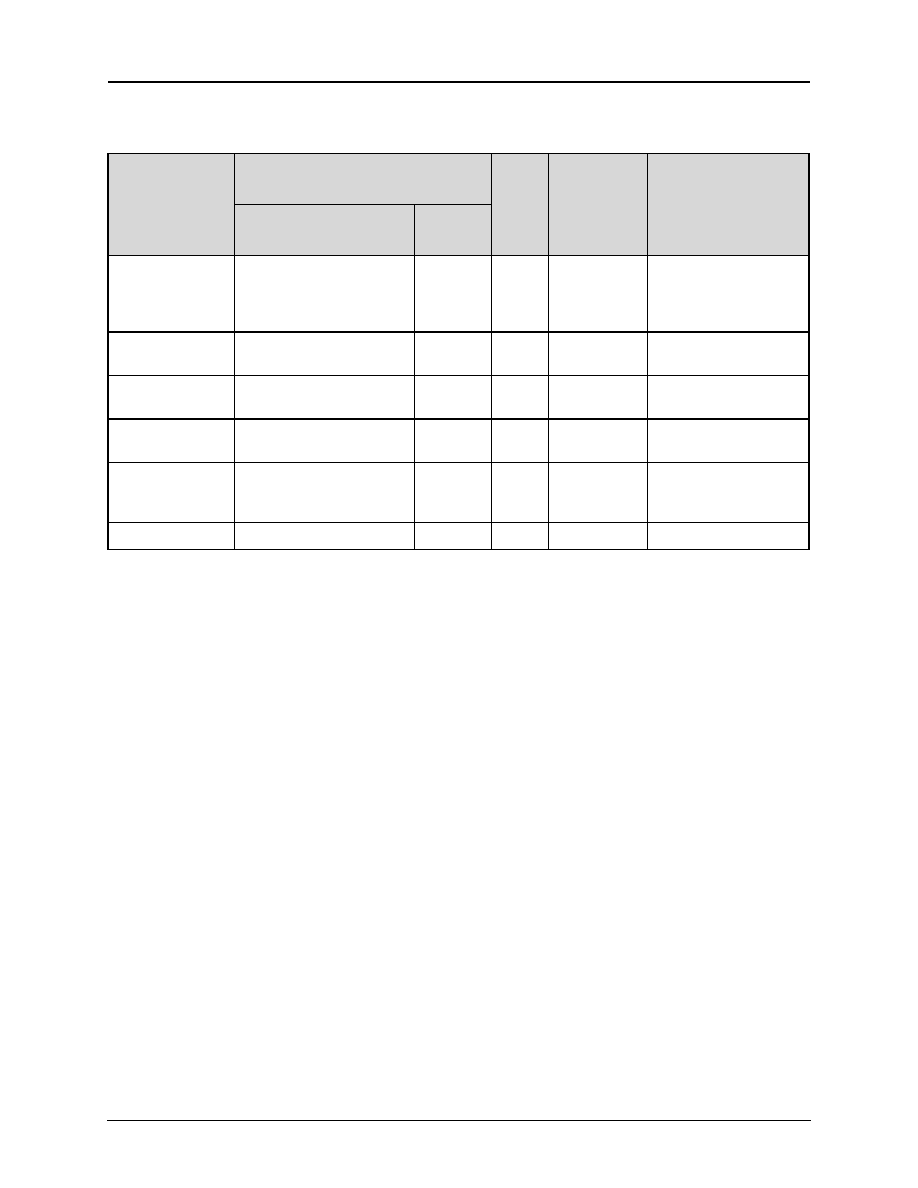

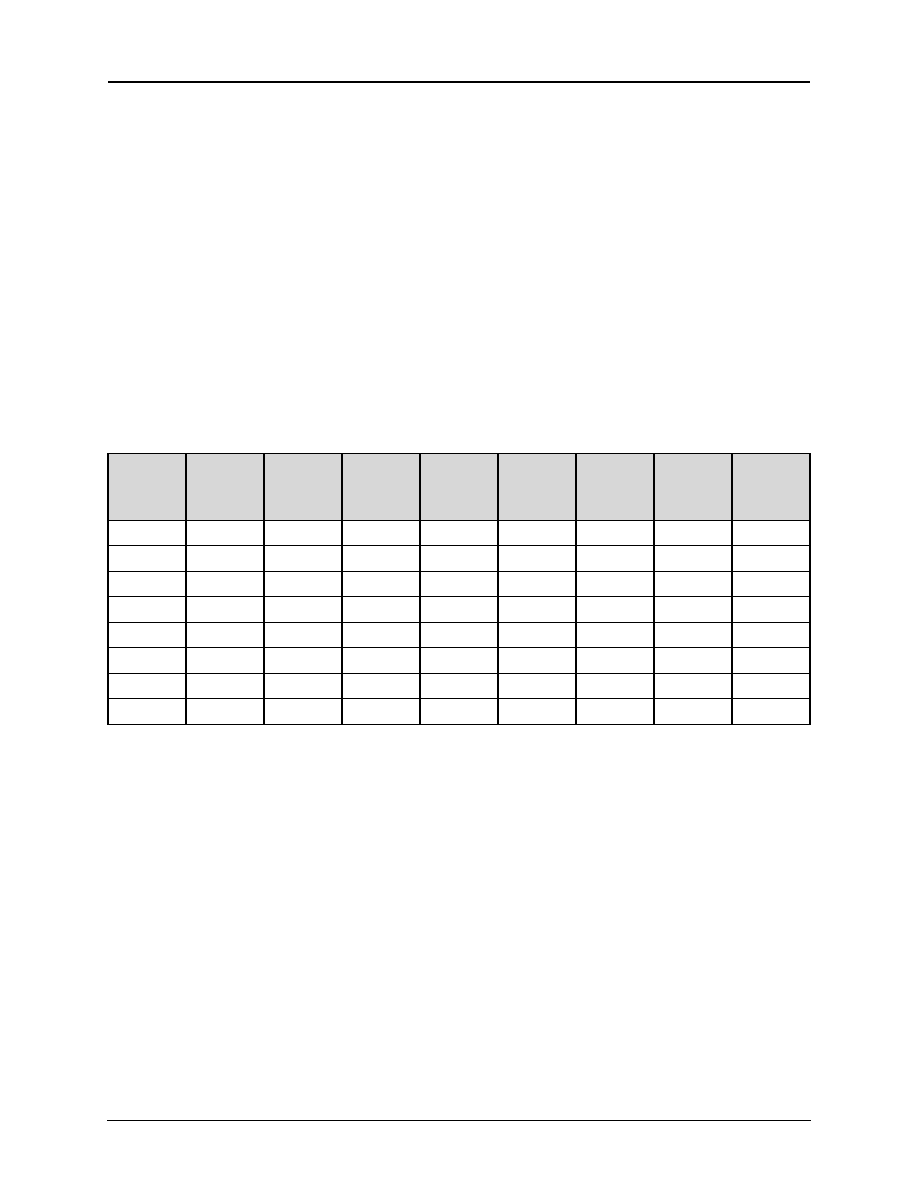

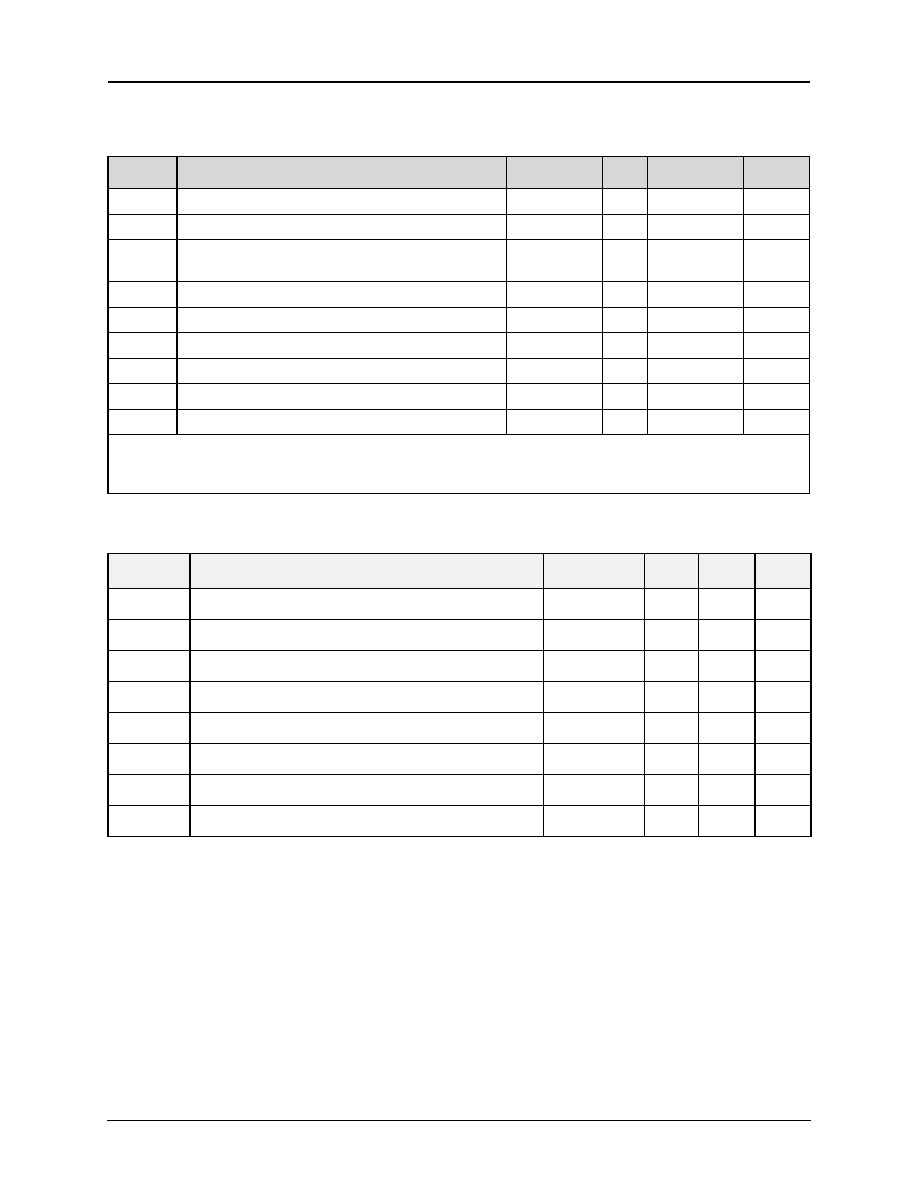

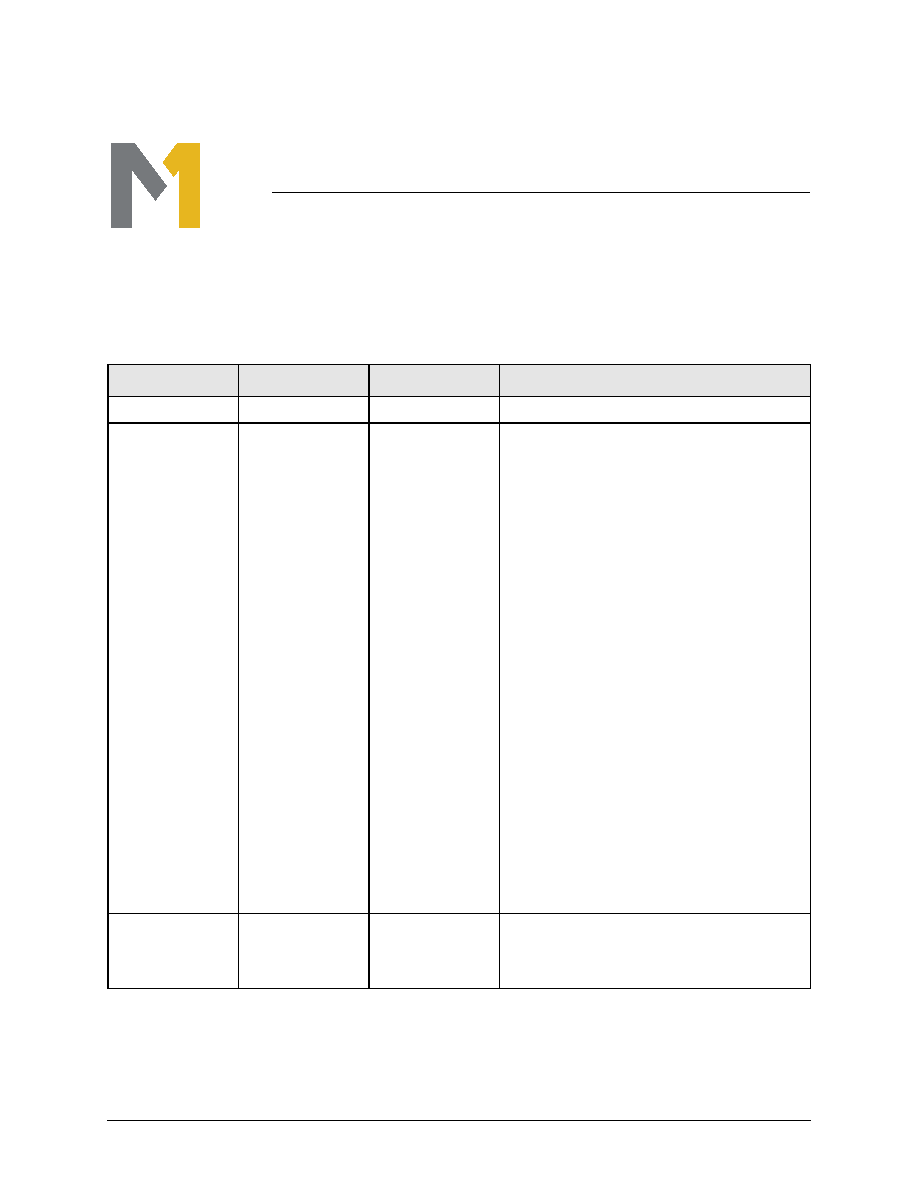

1.7

Supported Through-Paths . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

1.7.1

Commonly Used Through-Paths . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

1.7.2

Other Supported Through-Paths . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-9

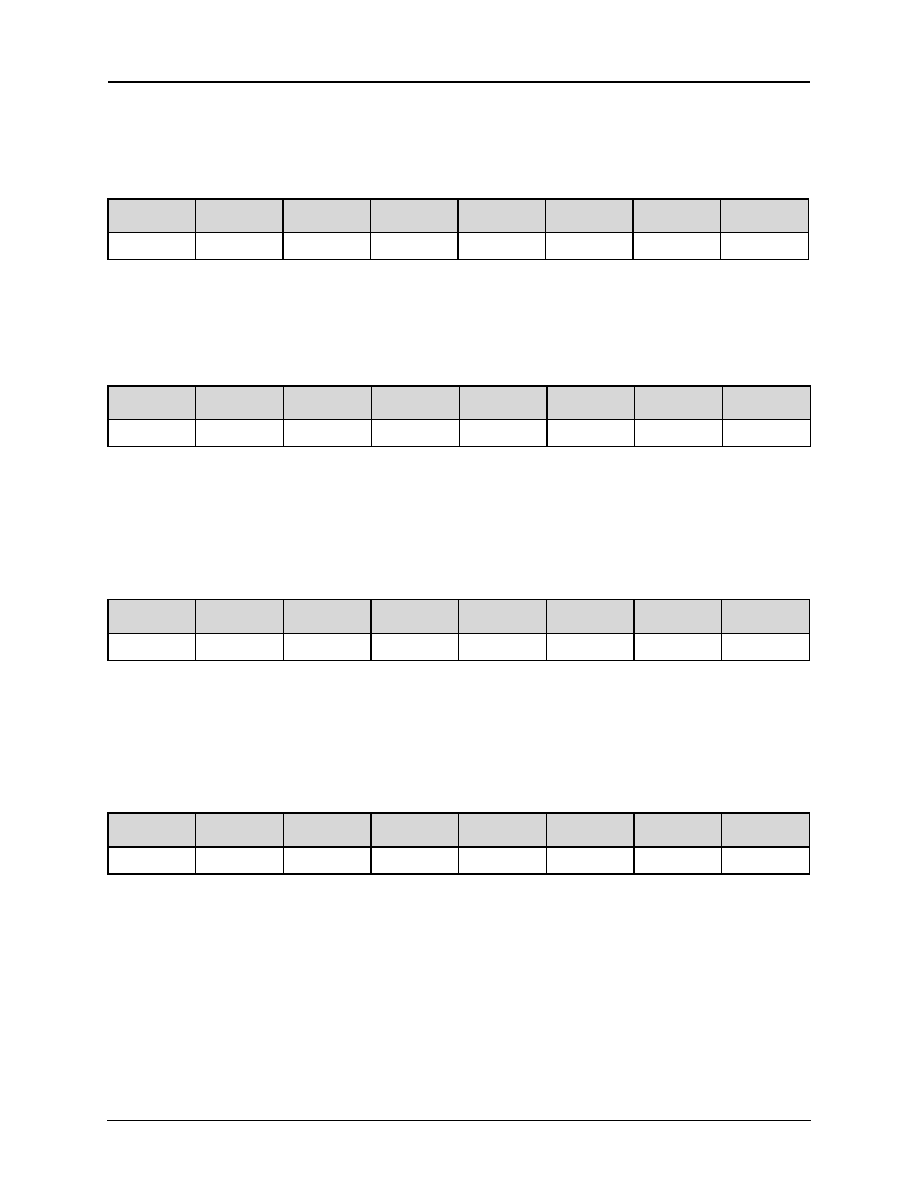

1.8

Applications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-10

1.8.1

OC-12/STM-4 Path Termination for HDLC Application . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-10

1.8.2

OC-3/STM-1 Path Termination for HDLC Application . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-11

1.8.3

DS3/E3 Path Termination for HDLC Application . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-11

1.9

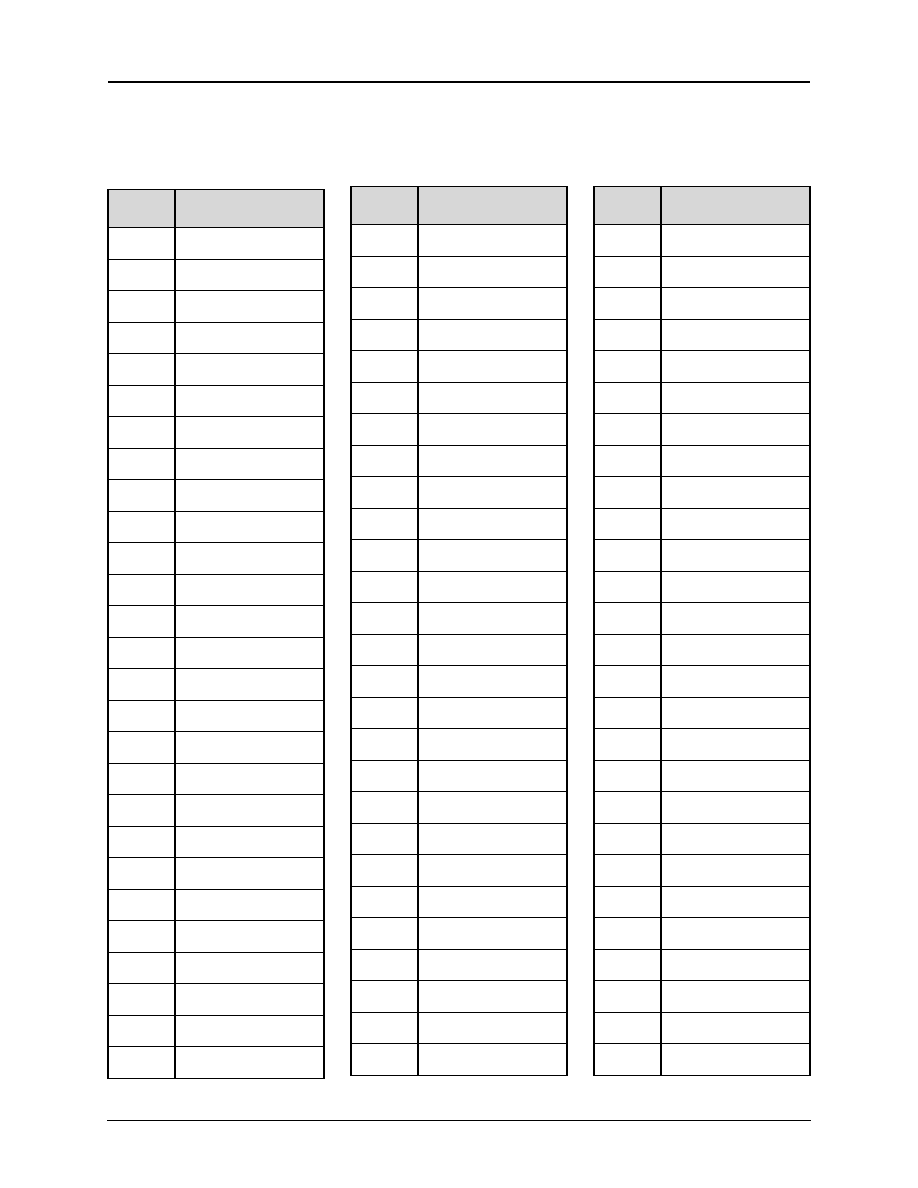

Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-12

2.0 Functional Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

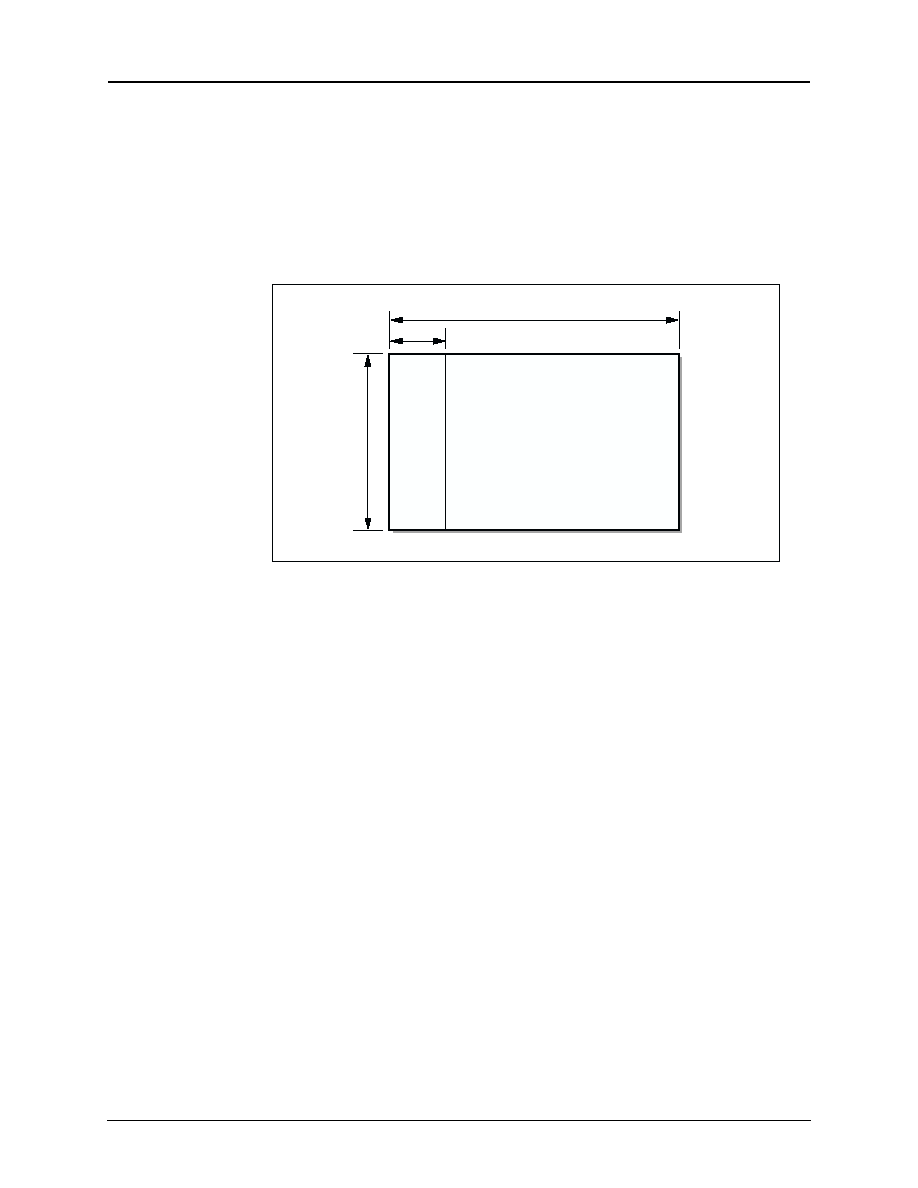

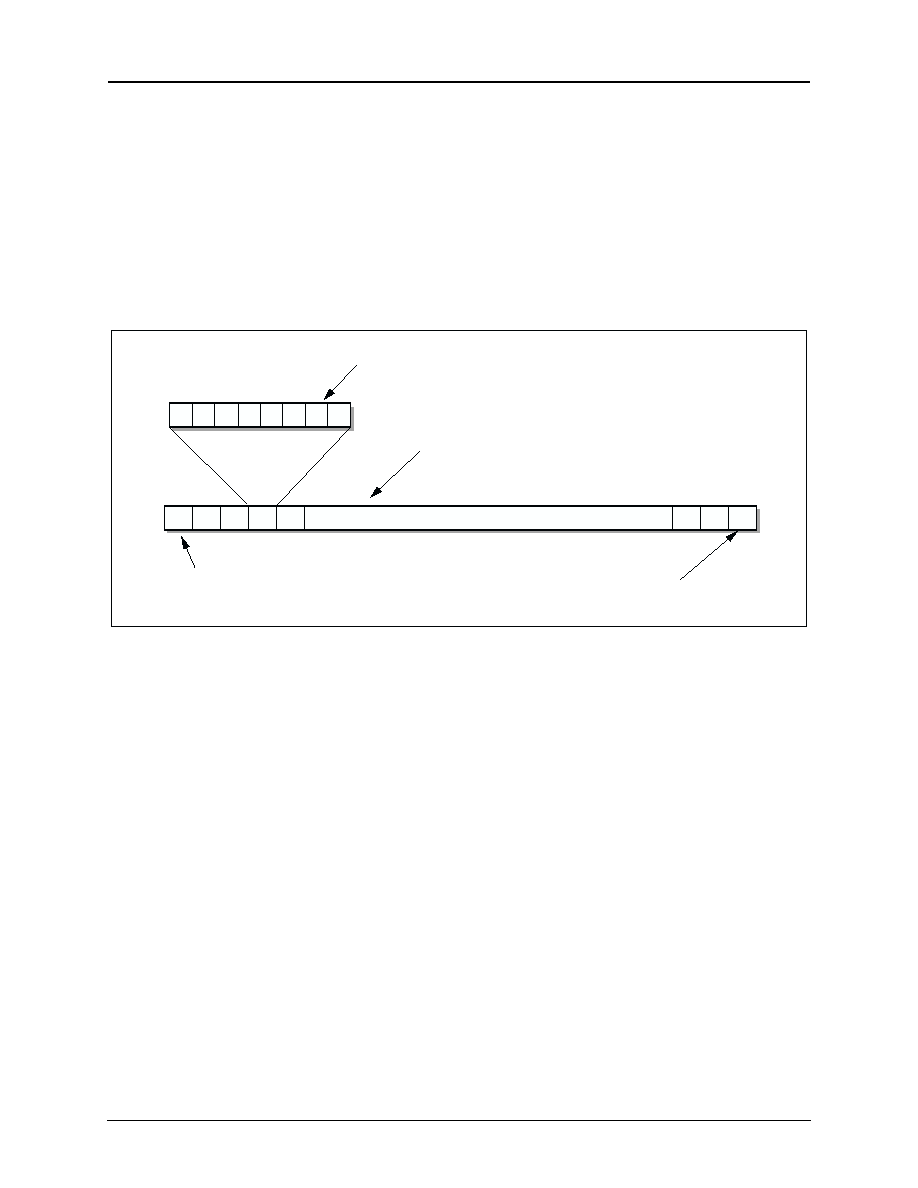

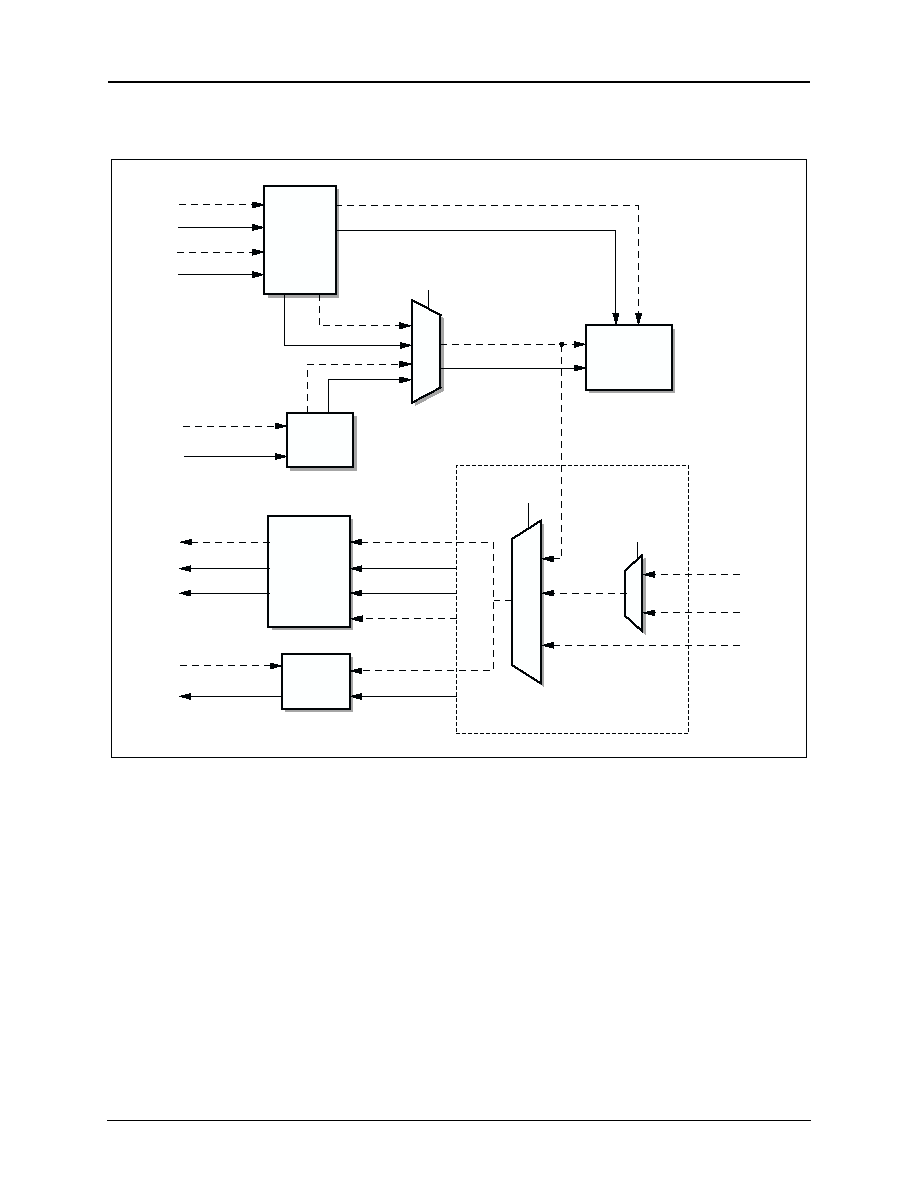

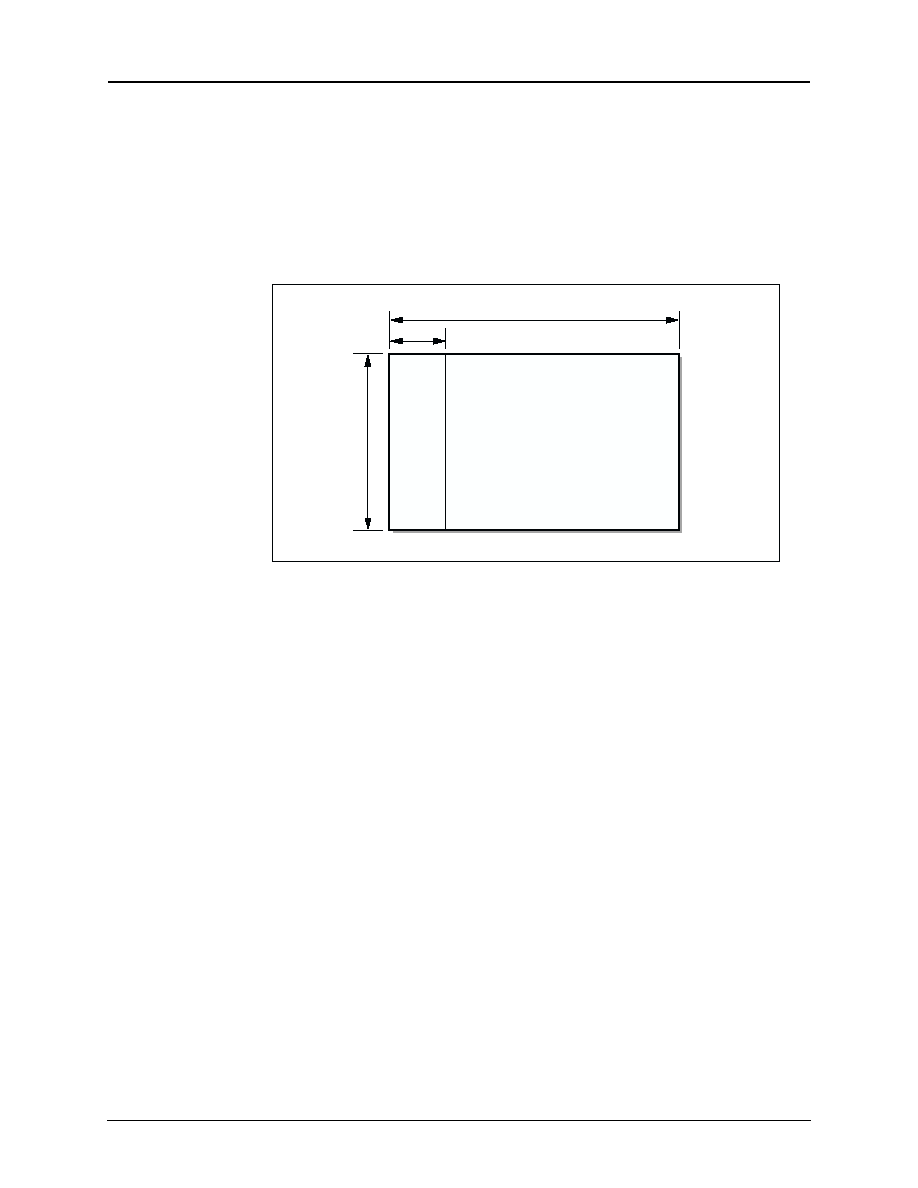

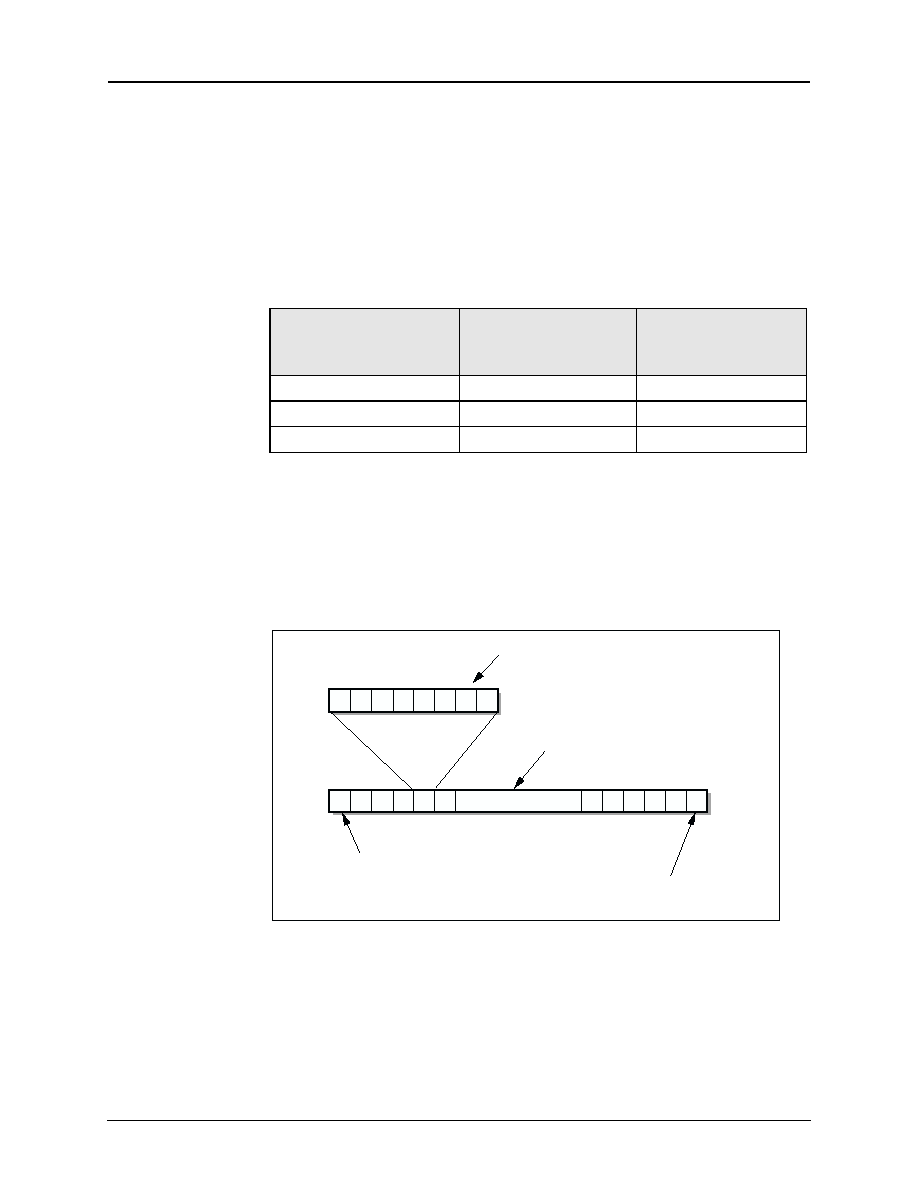

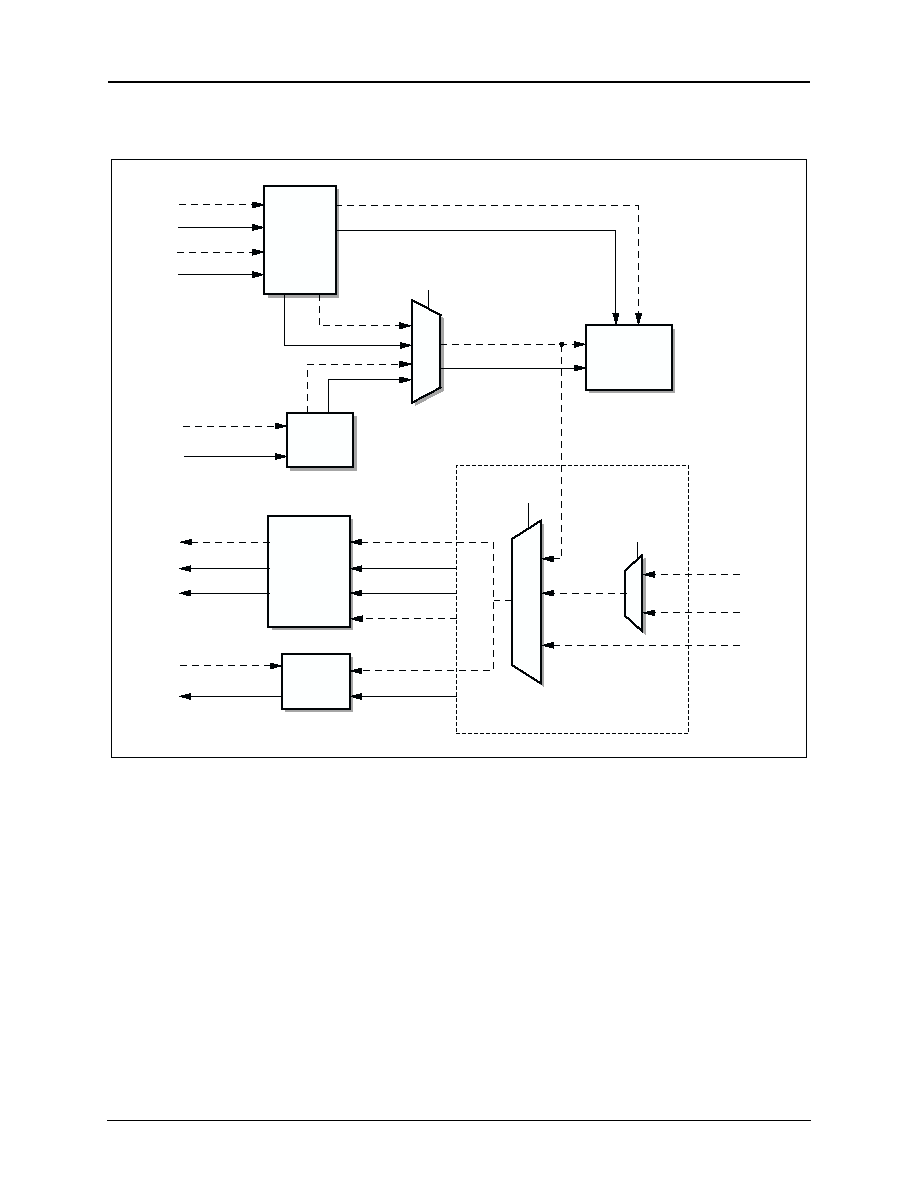

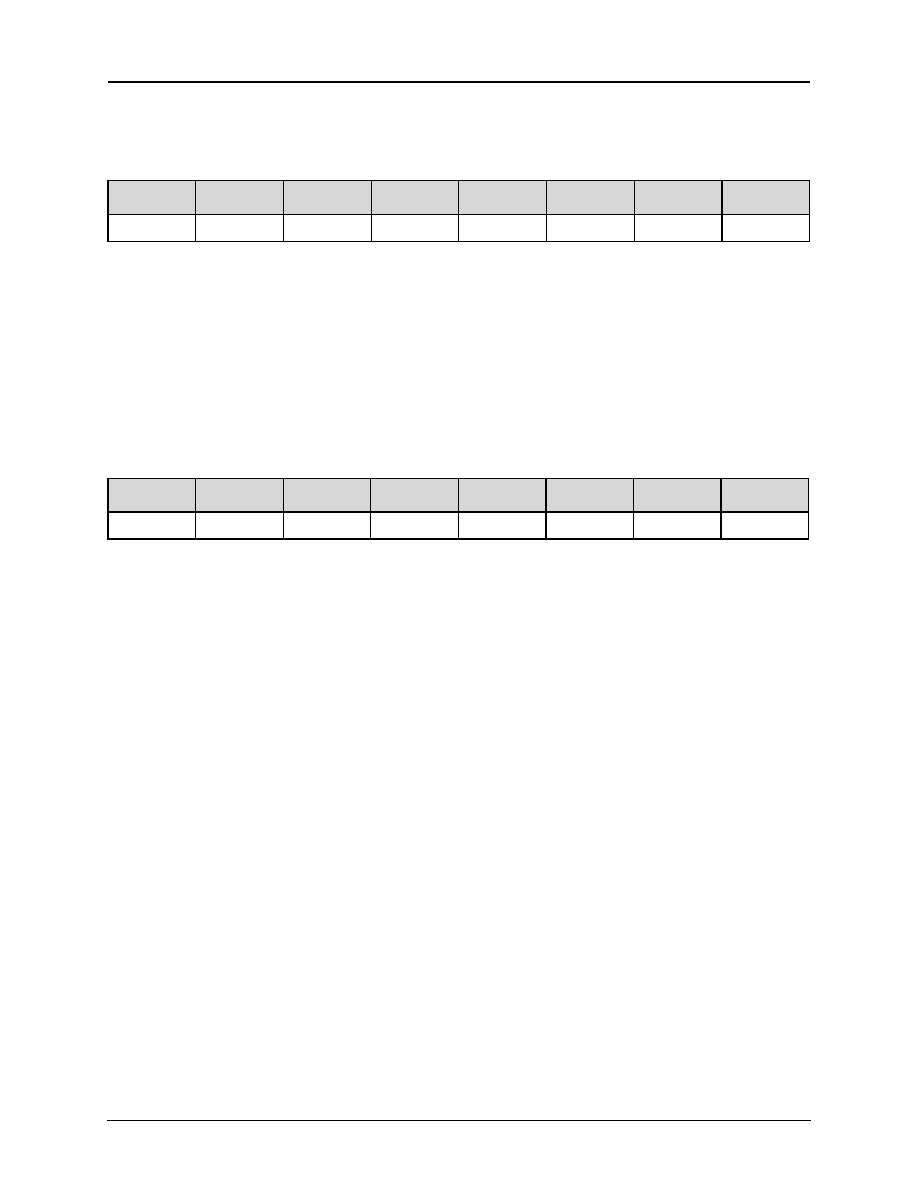

2.1

CX29503 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

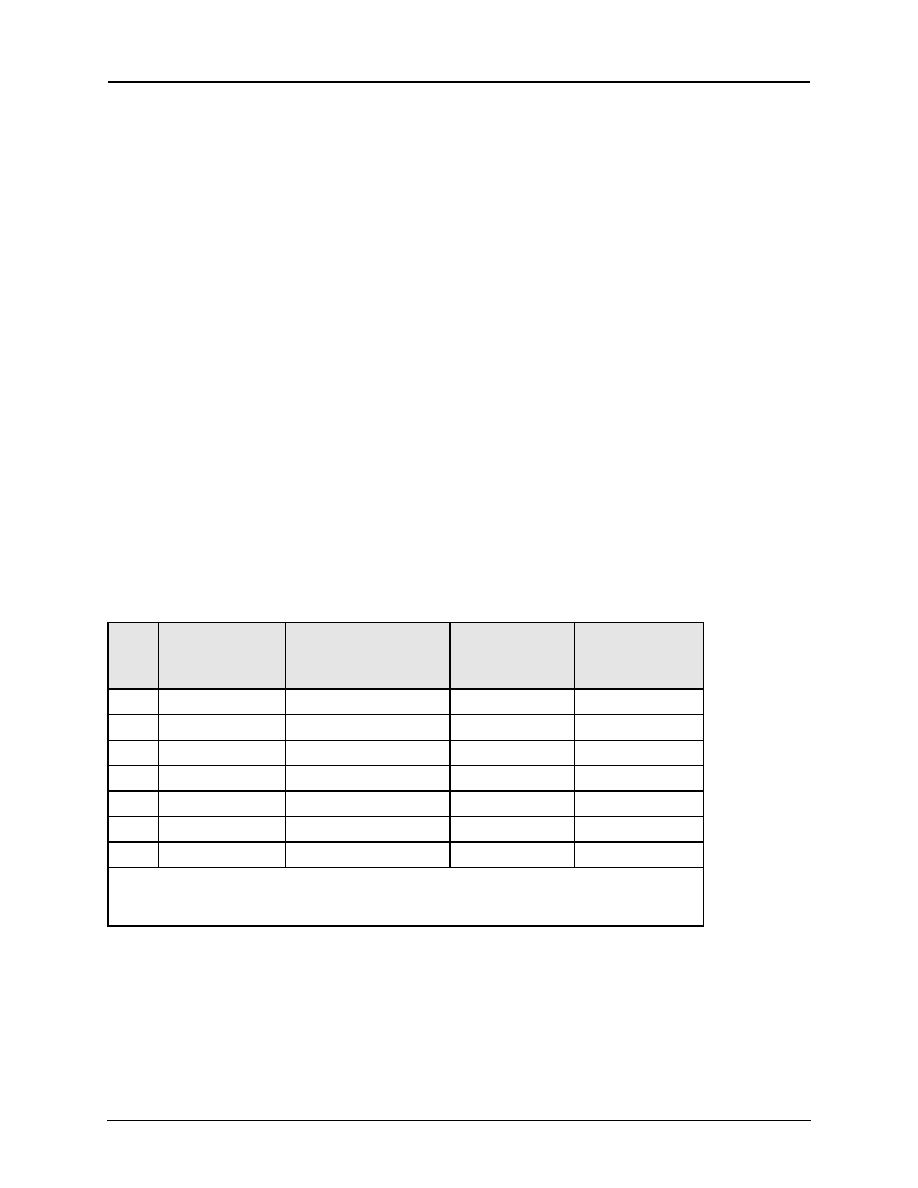

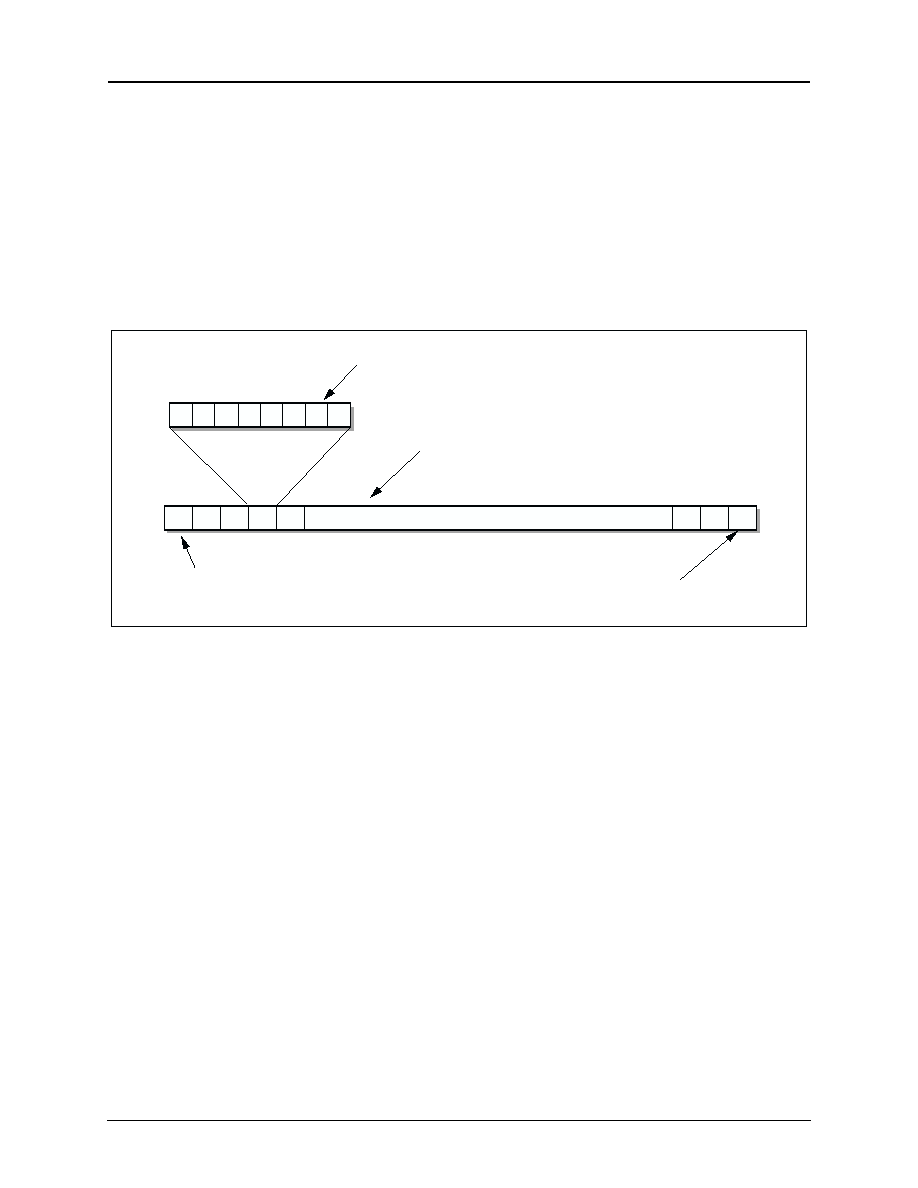

2.2

CX29503 Detailed Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

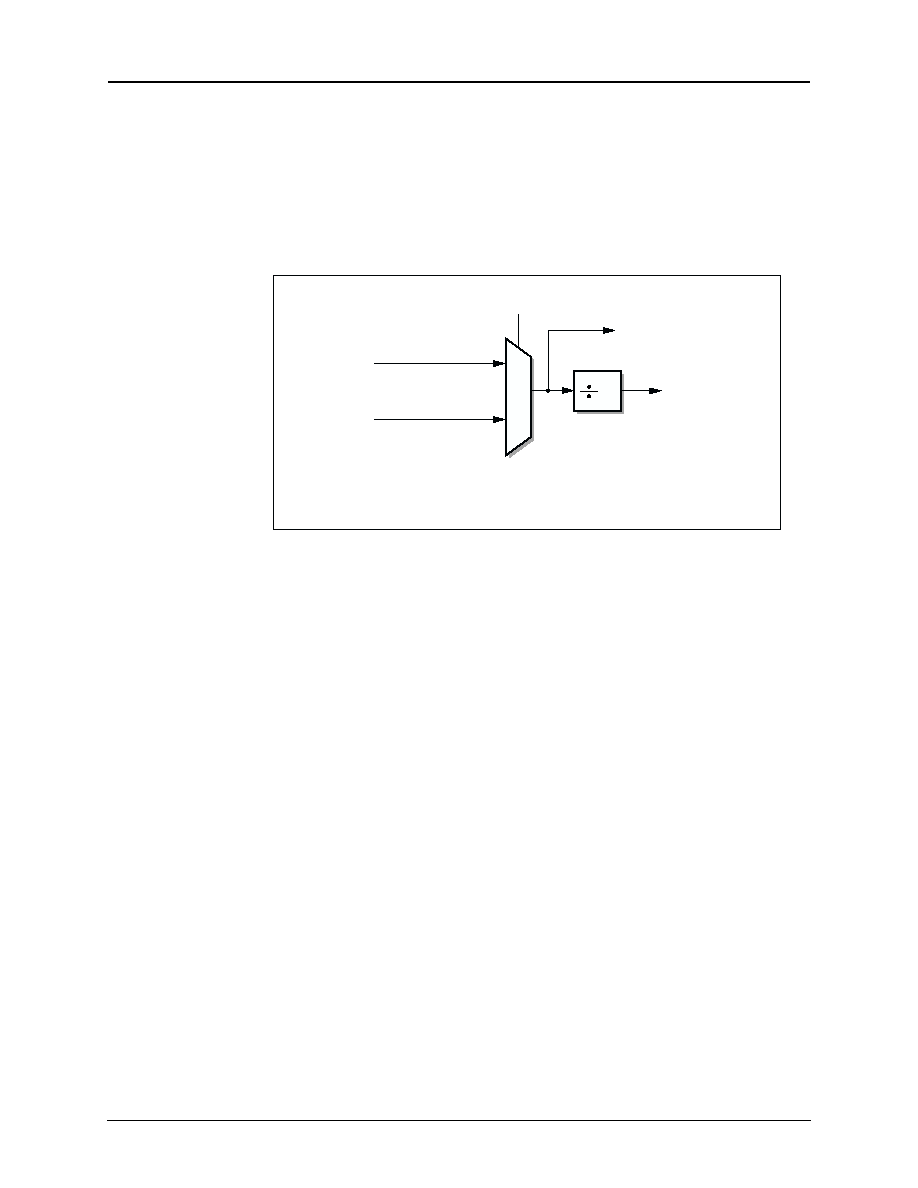

2.3

Top-Level MUX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

2.4

Global Control and Status Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

2.5

SONET Interleave Bus (SI-Bus) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

2.5.1

SI-Bus Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

2.5.1.1 Transmit Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

2.5.1.2 Receive Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

2.5.2

CX29503 Connection to CX29610 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

2.6

SONET/SDH Mapper/Multiplexer (MUX) Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

2.6.1

SONET/SDH Mapper/MUX Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-12

2.6.1.1 SI-Bus Receiver Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-12

2.6.1.2 STS-1/TUG-3 SPE Extraction Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-12

Contents

CX29503 Data Sheet

ii

Mindspeed TechnologiesTM

500238B

Advance Information

l

2.6.1.3 DS3/E3 Demapping Function. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-12

2.6.1.4 DS3/E3 Smoothing Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-13

2.6.1.5 VT Extraction Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-13

2.6.1.6 VT Performance Monitoring . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

2.6.1.7 VT Path Conditioning. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-15

2.6.1.8 DS1/E1 Demapping Function. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-15

2.6.1.9 Receive Time Slot Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-15

2.6.2

SONET/SDH Mapper/MUX Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-16

2.6.2.1 SI-Bus Transmitter Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-16

2.6.2.2 STS-1/TUG-3 Overhead Insertion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-16

2.6.2.3 VT Build and VT Overhead Insertion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-16

2.6.2.4 DS3/E3 Mapping Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-17

2.6.2.5 DS1/E1 Mapping Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-17

2.6.2.6 Transmit Time Slot Bus (TSB) Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-18

2.6.3

SONET/SDH Transmitter to Receiver Loopback Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-18

2.7

DS3/E3 Framer Block. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-19

2.8

DS1/E1 Framer Block. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-23

2.8.1

Module Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-24

2.9

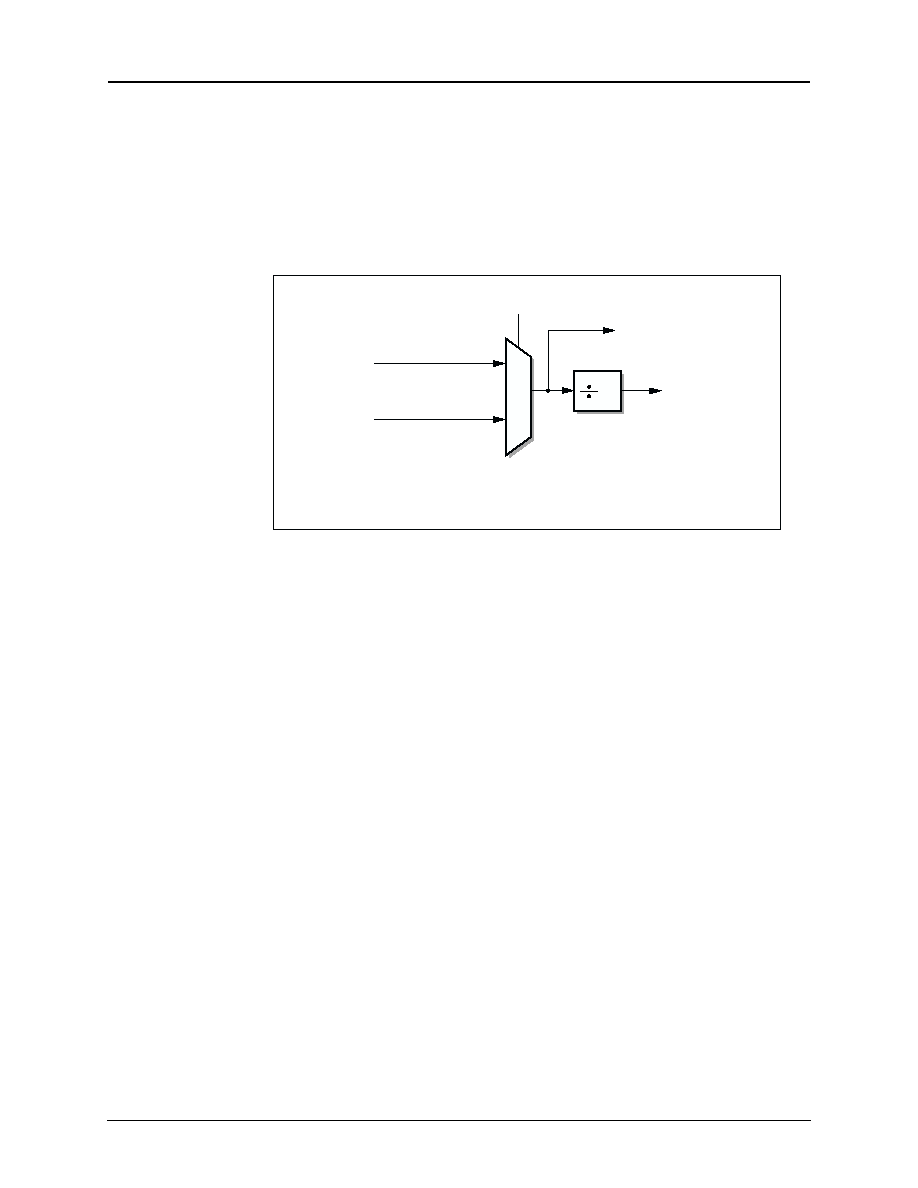

M13/E13 Multiplexer (MUX) Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-28

2.9.1

Operational Features Specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-30

2.10

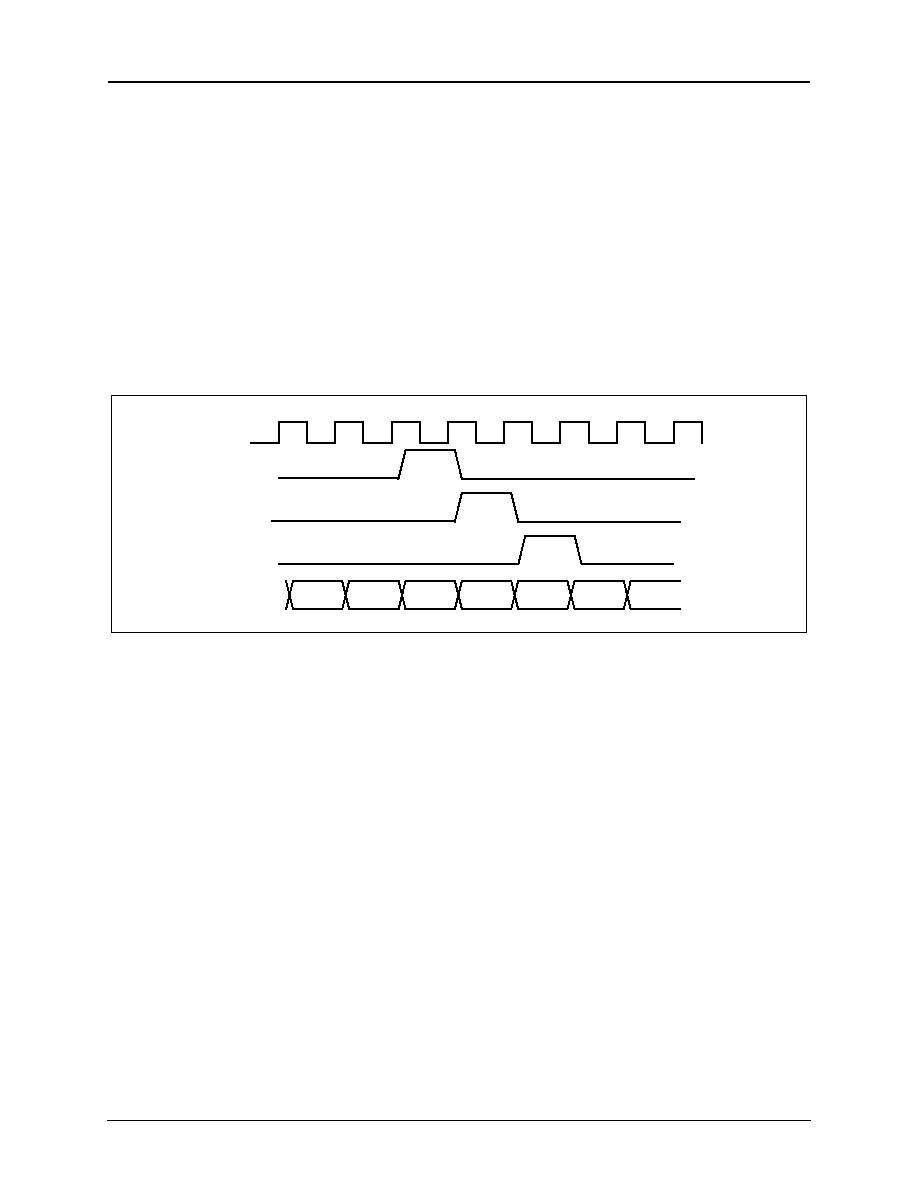

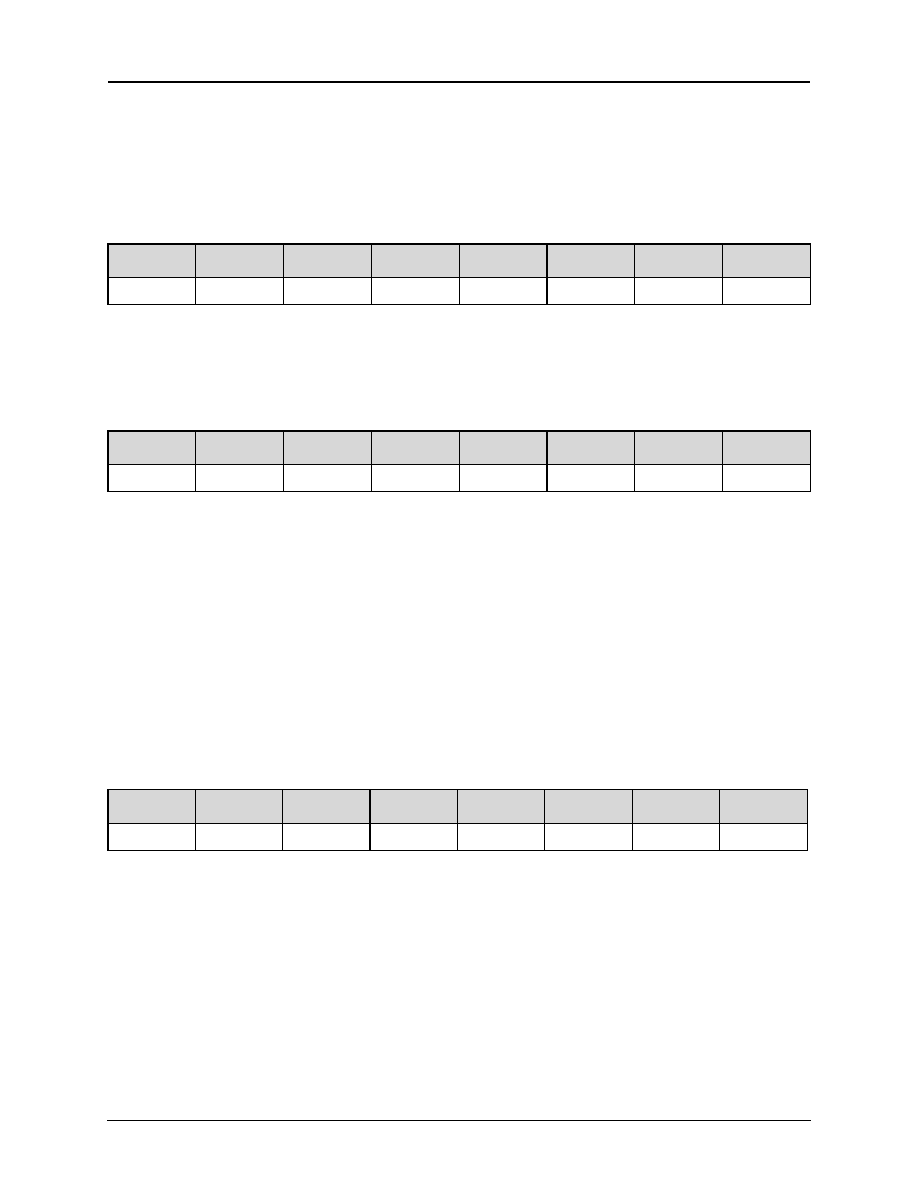

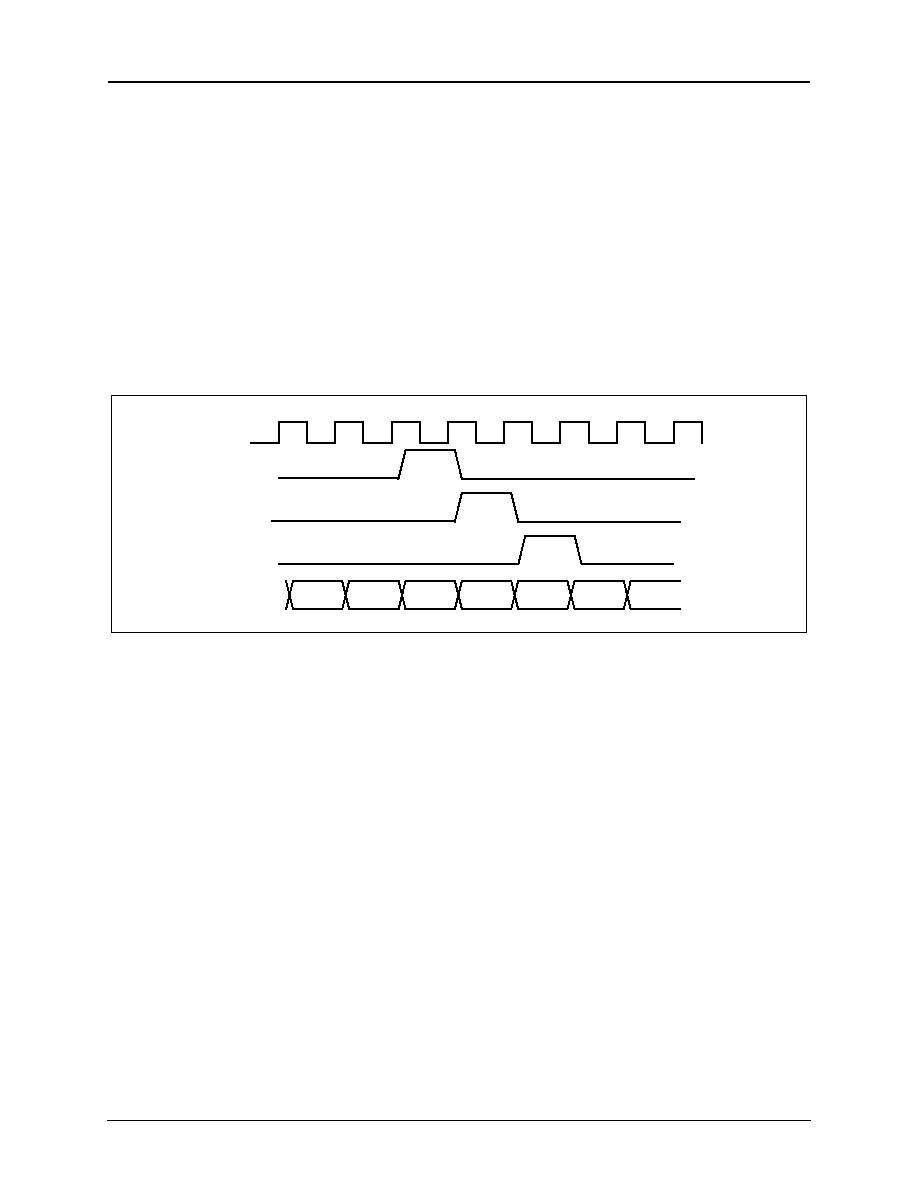

Time Slot Bus (TSB) Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-31

2.10.1

Summary of Payload TSB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-33

2.10.2

Summary of Overhead TSB. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-34

2.10.3

TSB Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-35

2.10.4

Details of Payload TSB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-36

2.10.4.1 Data Path Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-36

2.10.4.2 Stuff Byte Compensation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-36

2.10.4.3 Mapping of Payload to TSB Payload Time Slots . . . . . . . . . . . . . . . . . . . . . . . 2-37

2.10.5

Details of Overhead TSB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-41

2.10.5.1 Overhead Data Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-41

2.10.5.2 Overhead TSB Frame Stuff Byte Compensation. . . . . . . . . . . . . . . . . . . . . . . . 2-41

2.10.5.3 Mapping of Overhead Data to Overhead TSB Time Slots . . . . . . . . . . . . . . . . . 2-42

2.10.5.4 SONET Overhead Communication Channels . . . . . . . . . . . . . . . . . . . . . . . . . . 2-44

2.10.5.5 SDH Overhead Communication Channels . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-45

2.10.5.6 Electrical DS3 Serial Port Overhead Communication Channels . . . . . . . . . . . . 2-45

2.10.5.7 Electrical E3 Serial Port Overhead Communication Channels . . . . . . . . . . . . . 2-45

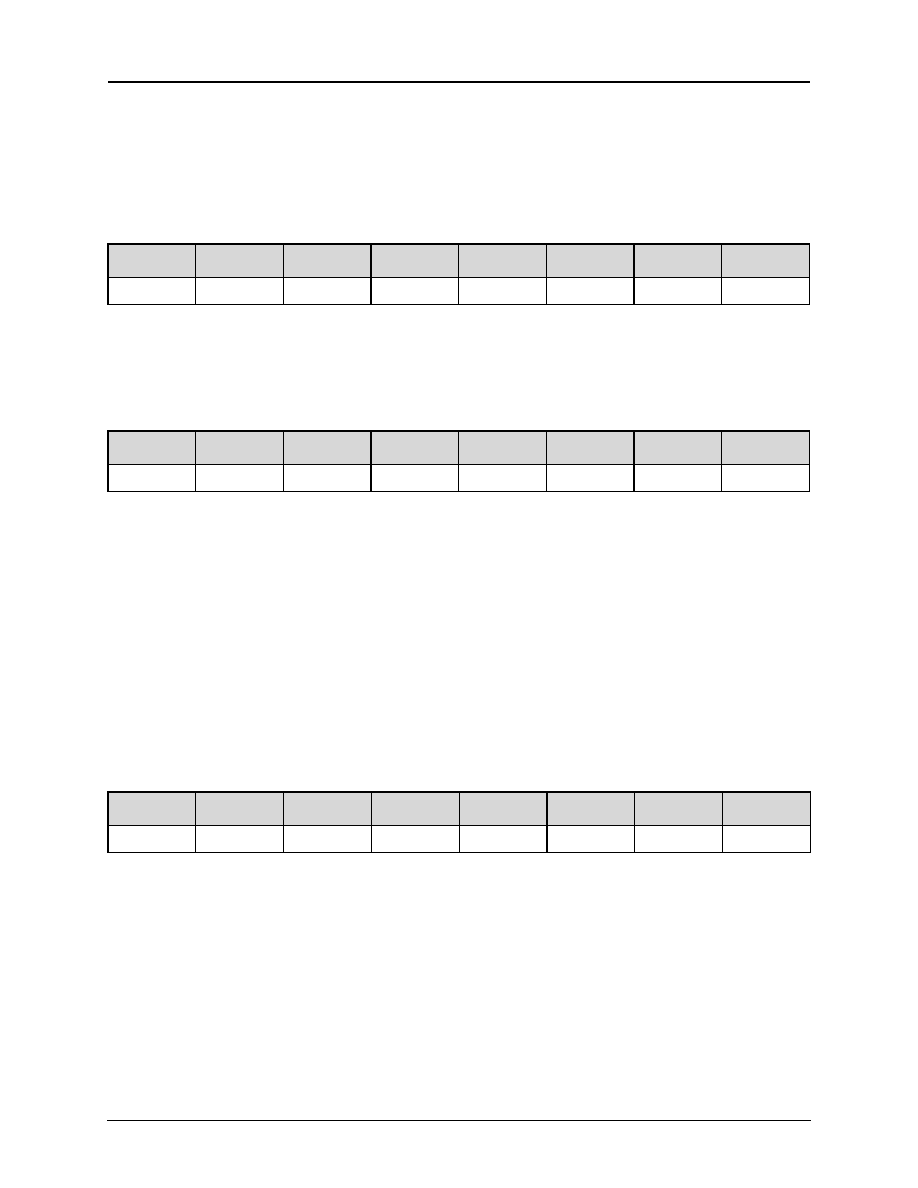

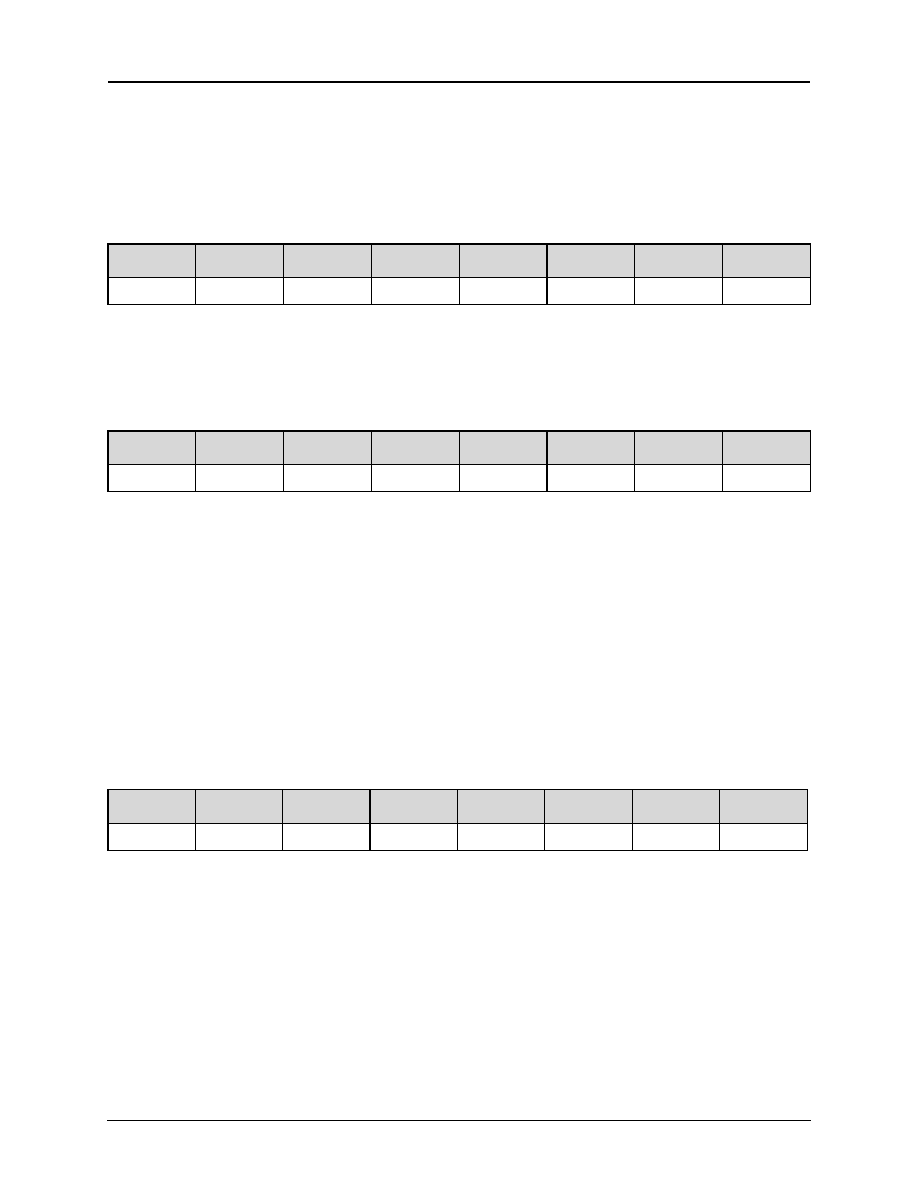

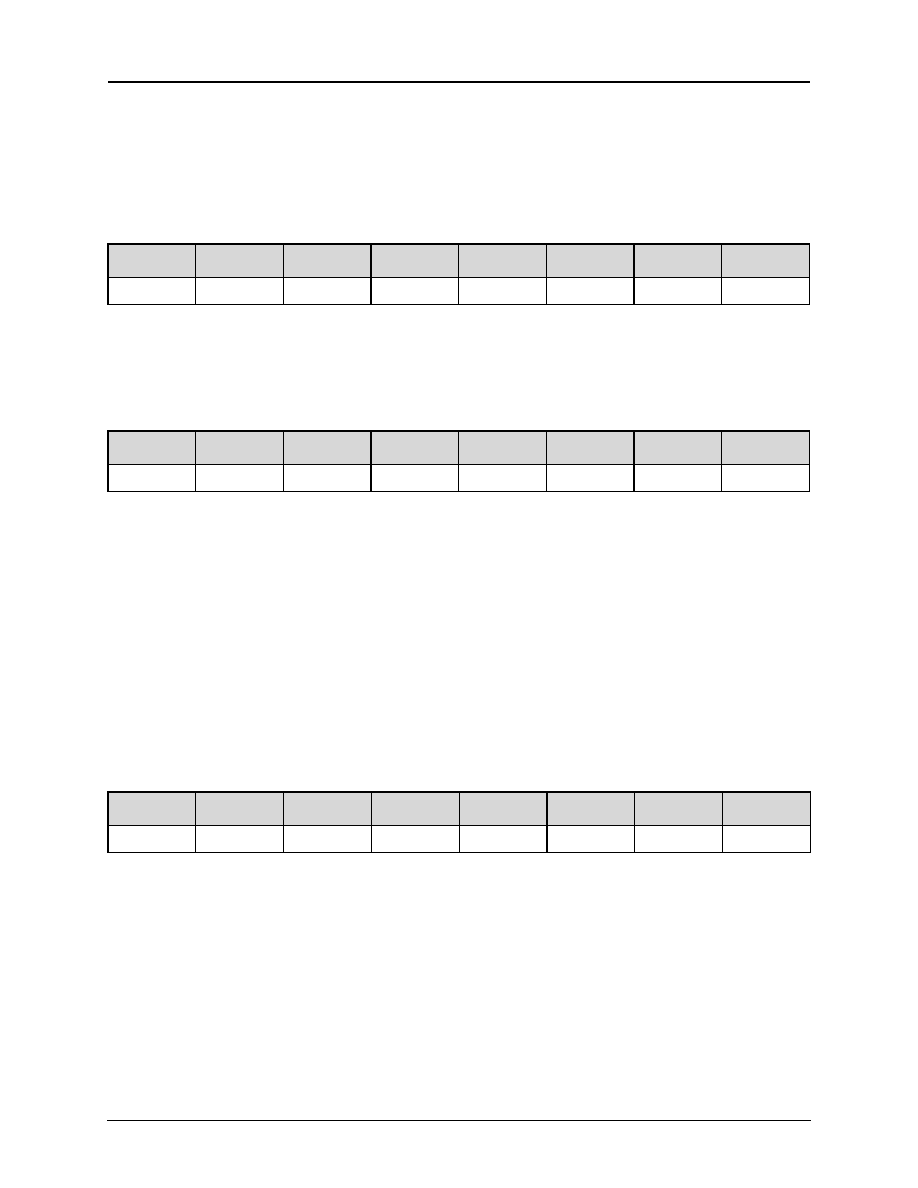

2.10.6

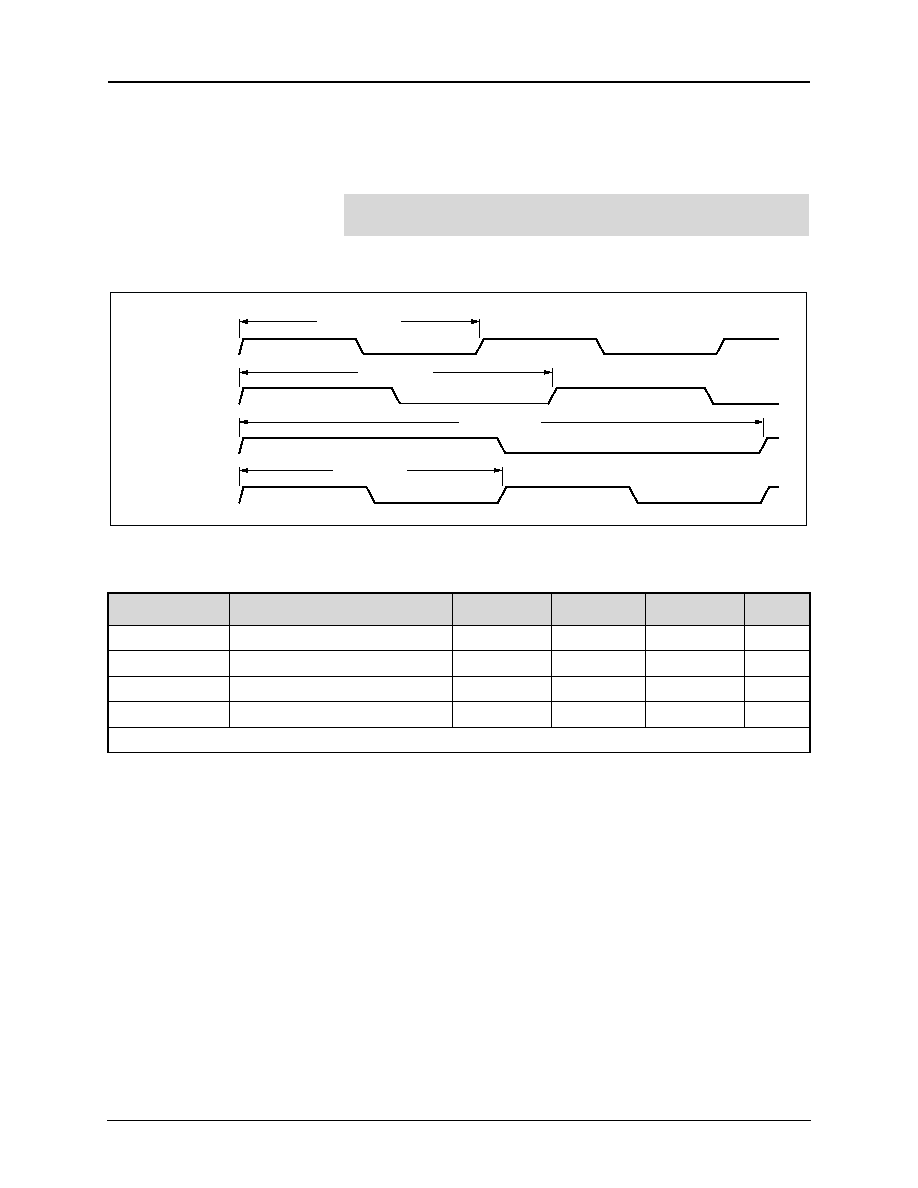

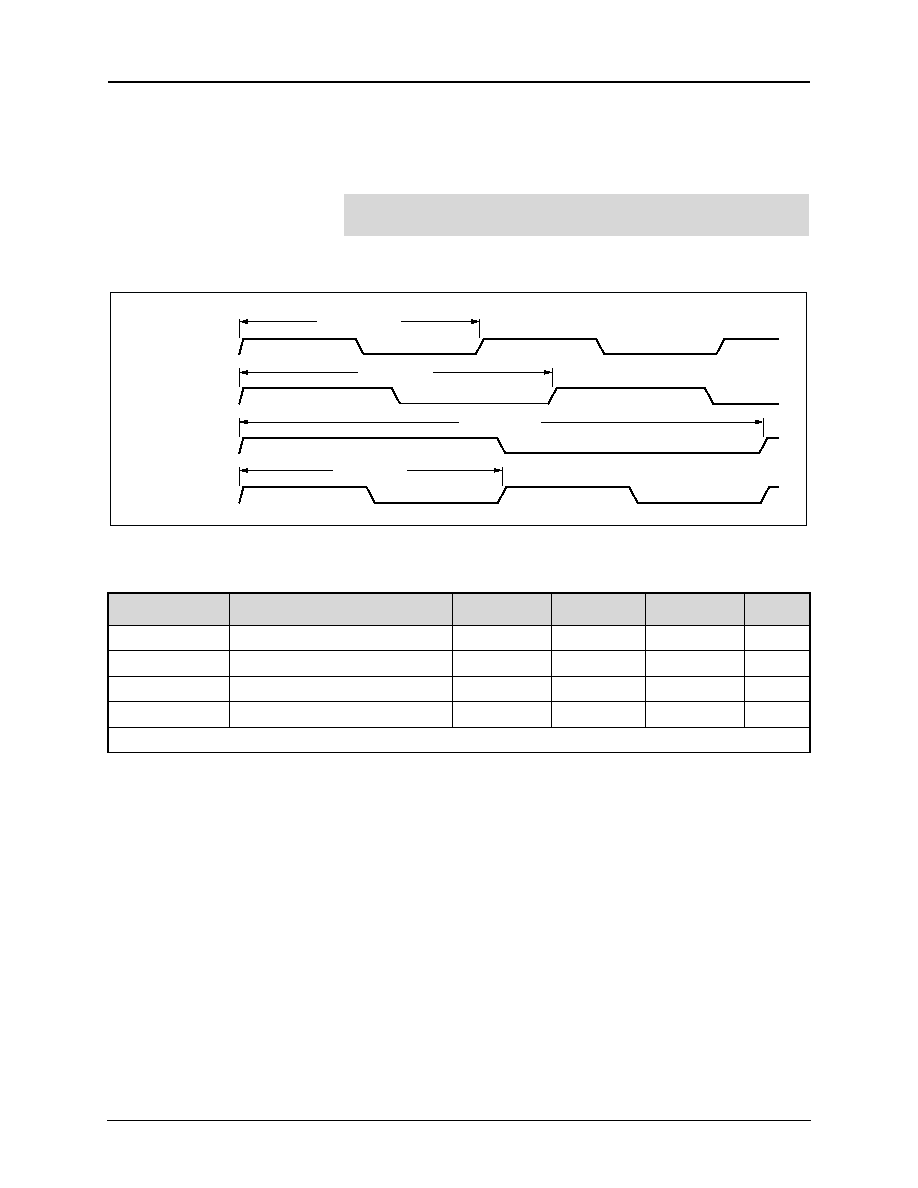

Timing Details . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-46

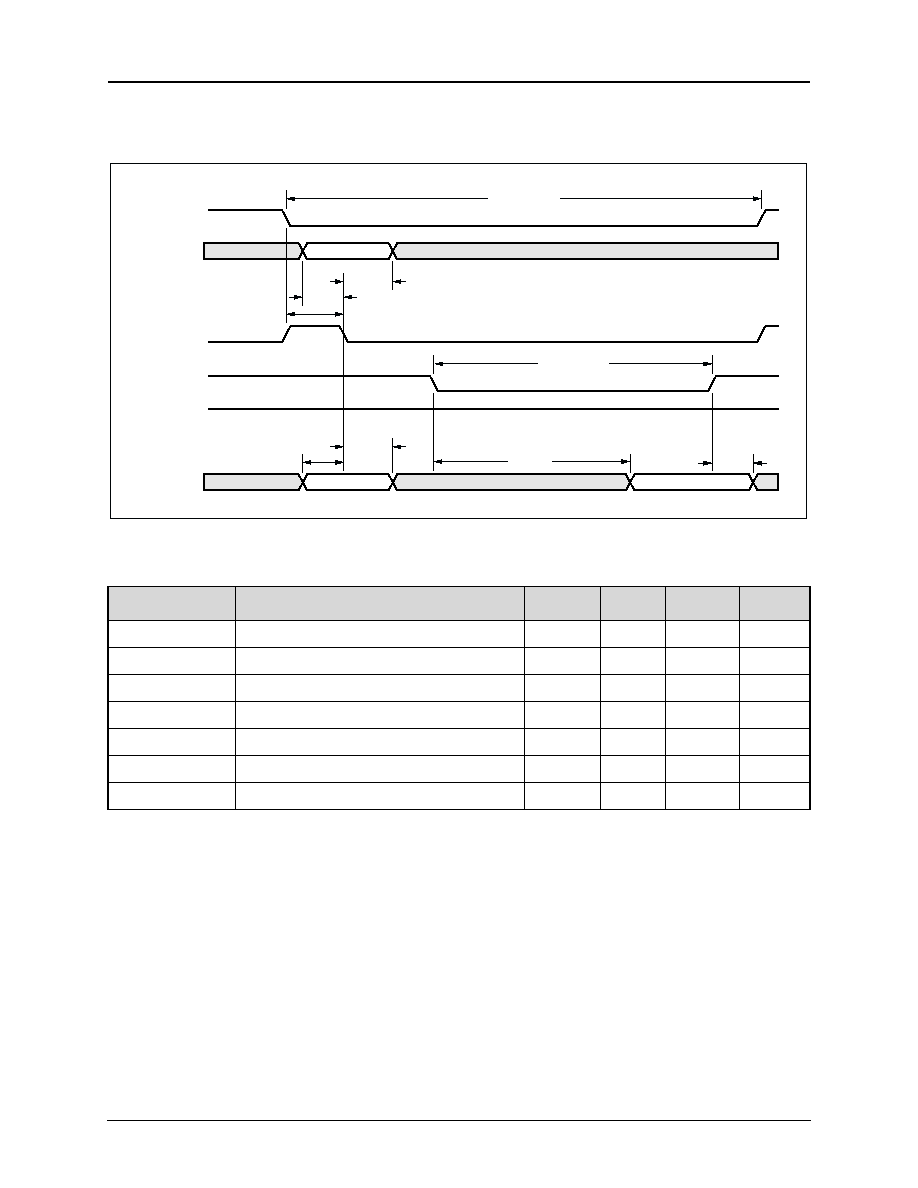

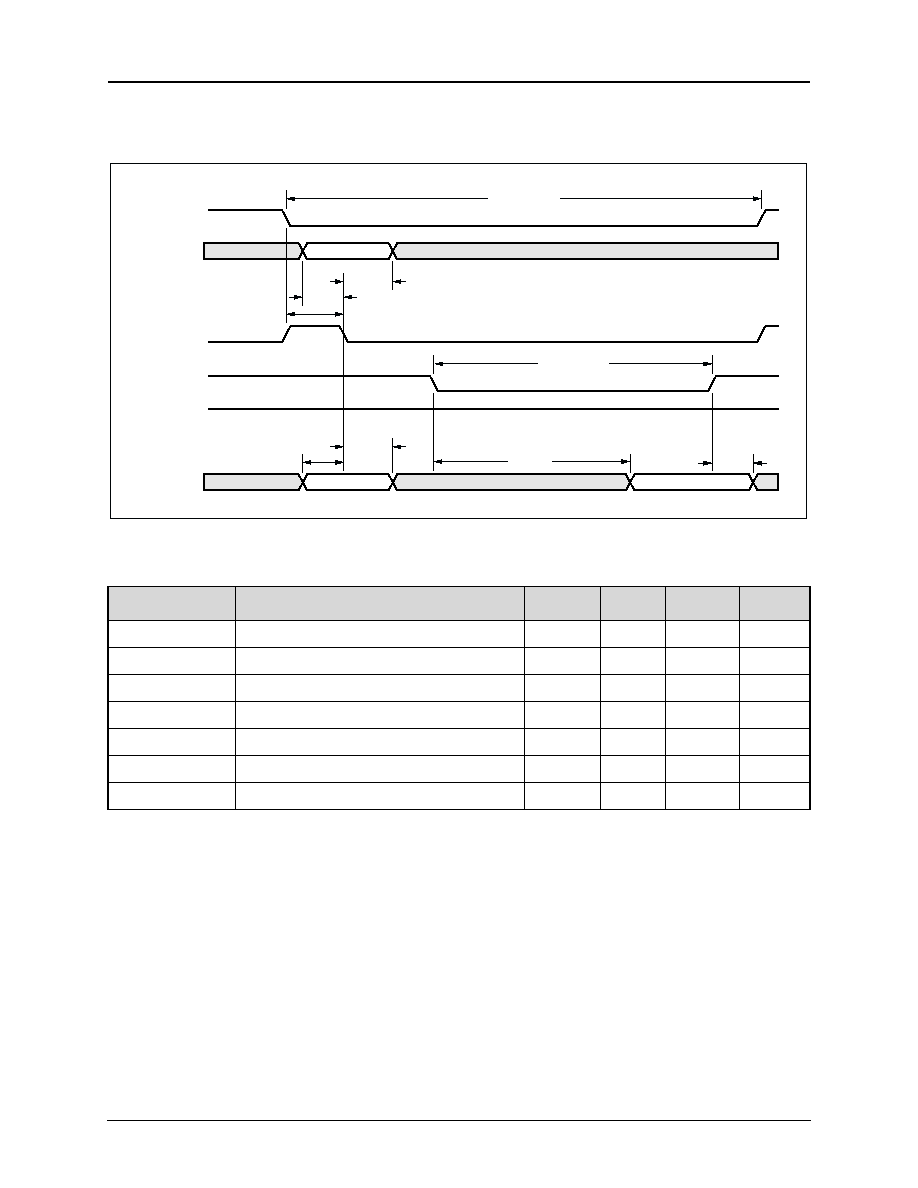

2.10.6.1 Payload Bus, AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-46

2.10.6.2 Overhead Bus, AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-51

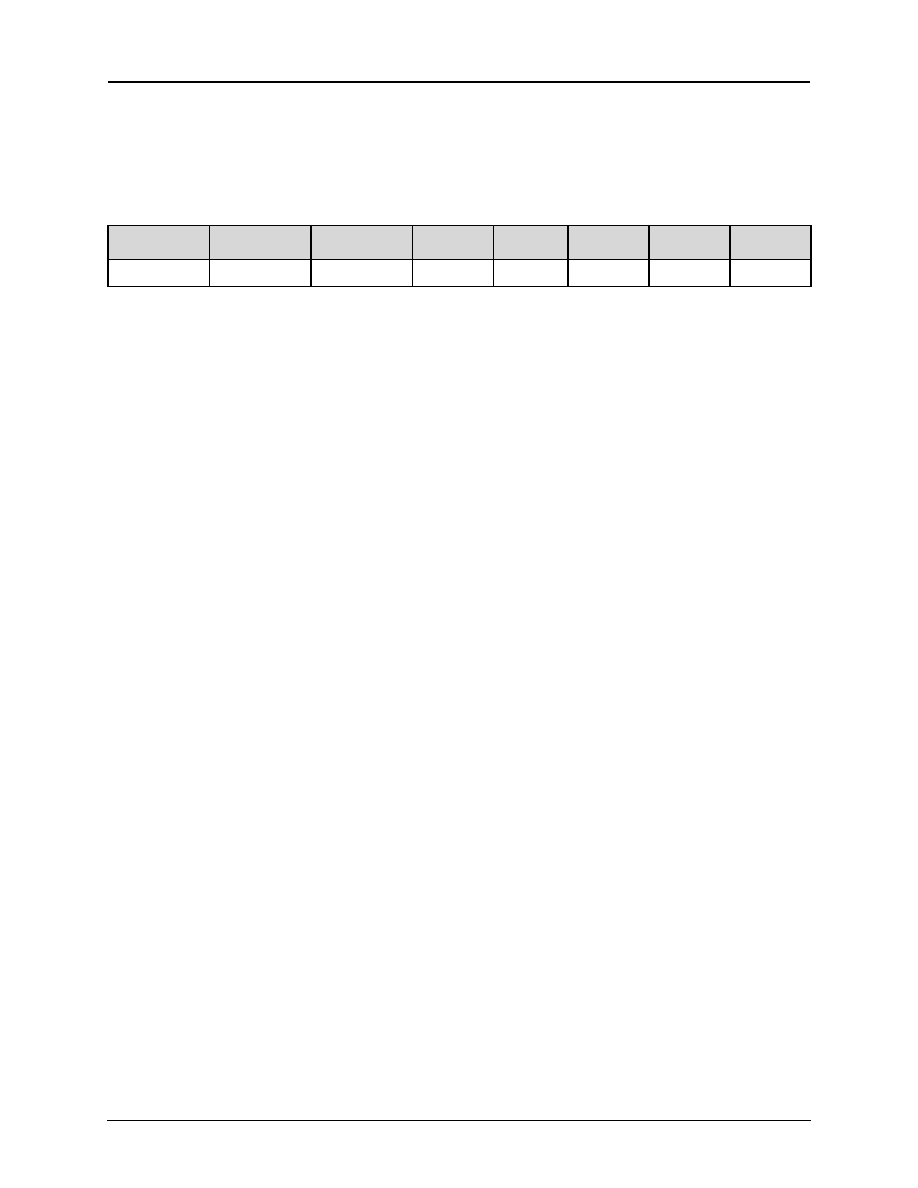

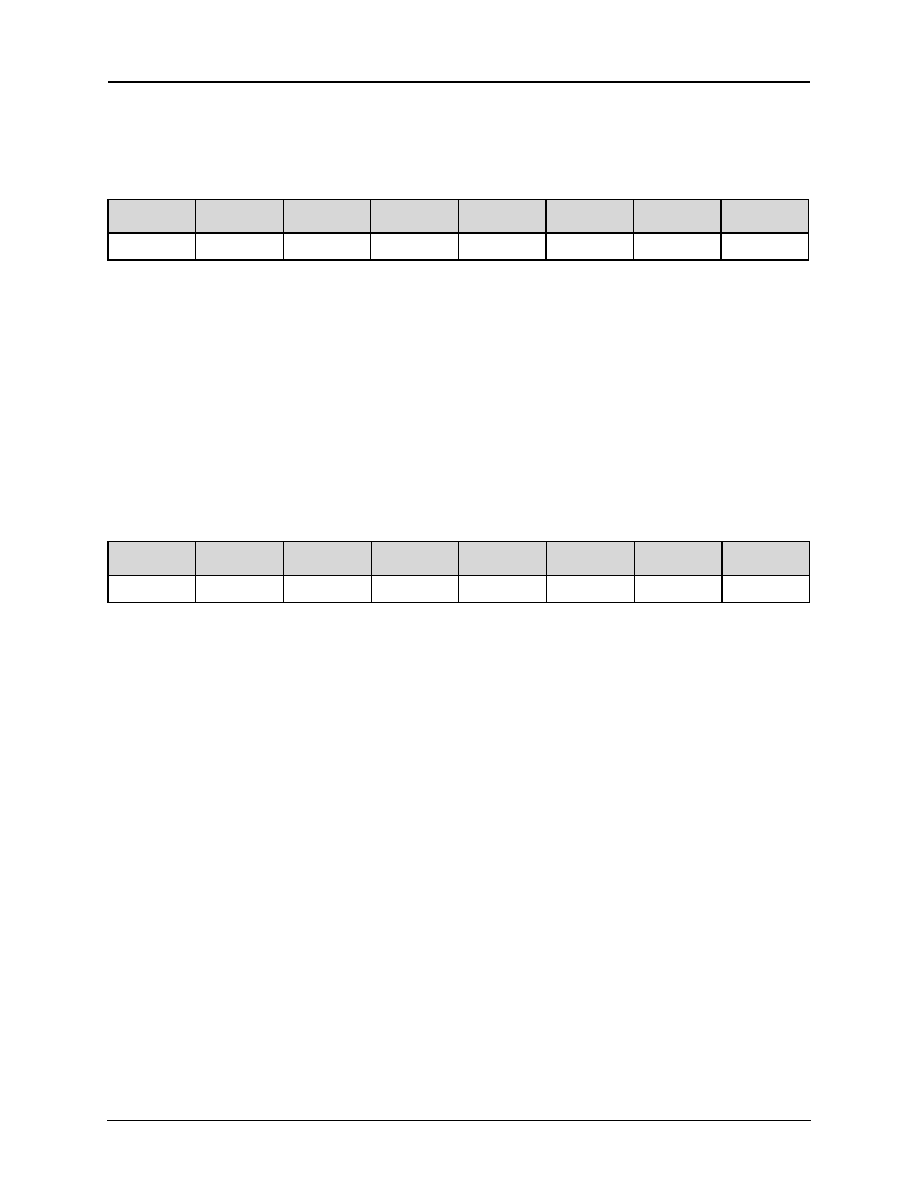

3.0 Parallel Microprocessor Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.1

Address/Data Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.2

Bus Control Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

500238B

Mindspeed TechnologiesTM

iii

Advance Information

CX29503 Data Sheet

Contents

3.3

Interrupt and Control Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

3.4

Command and Status Processor (CSP). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

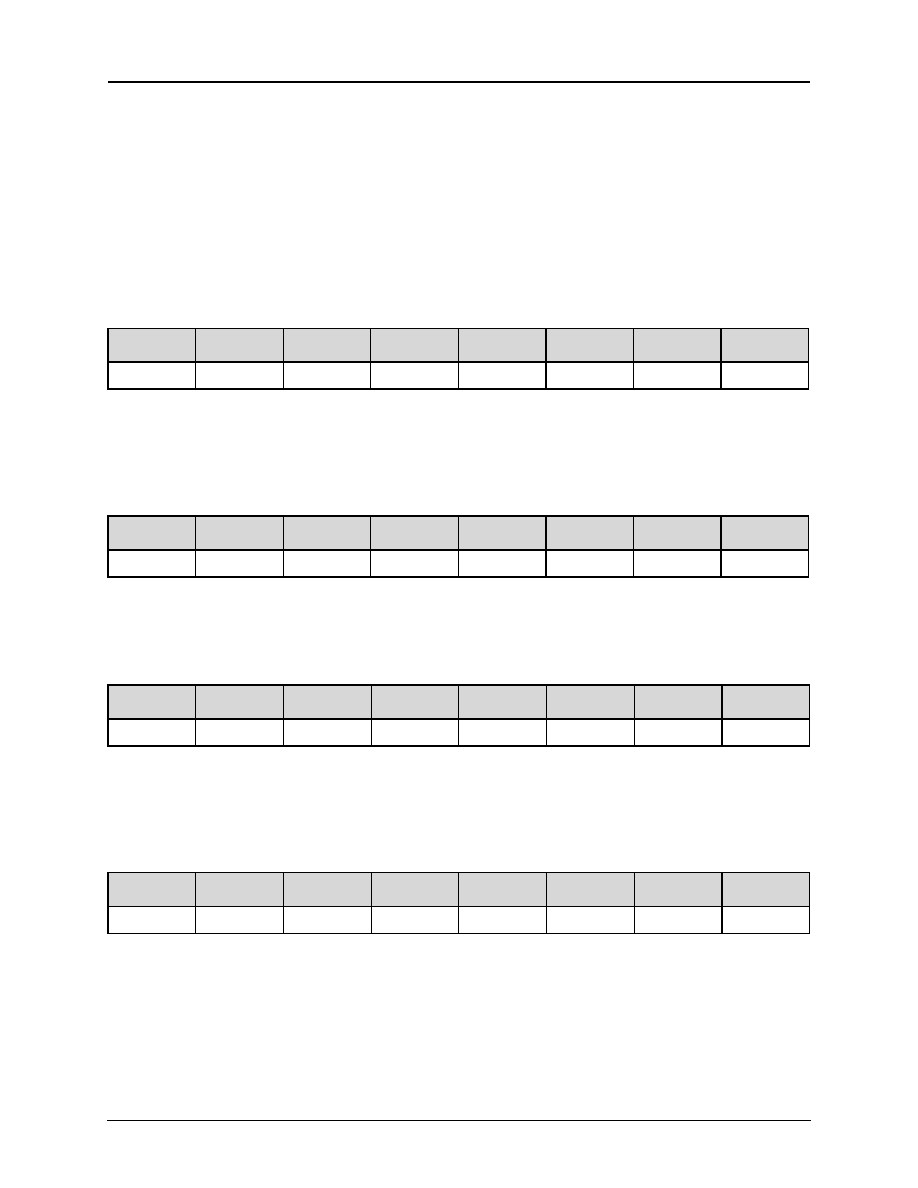

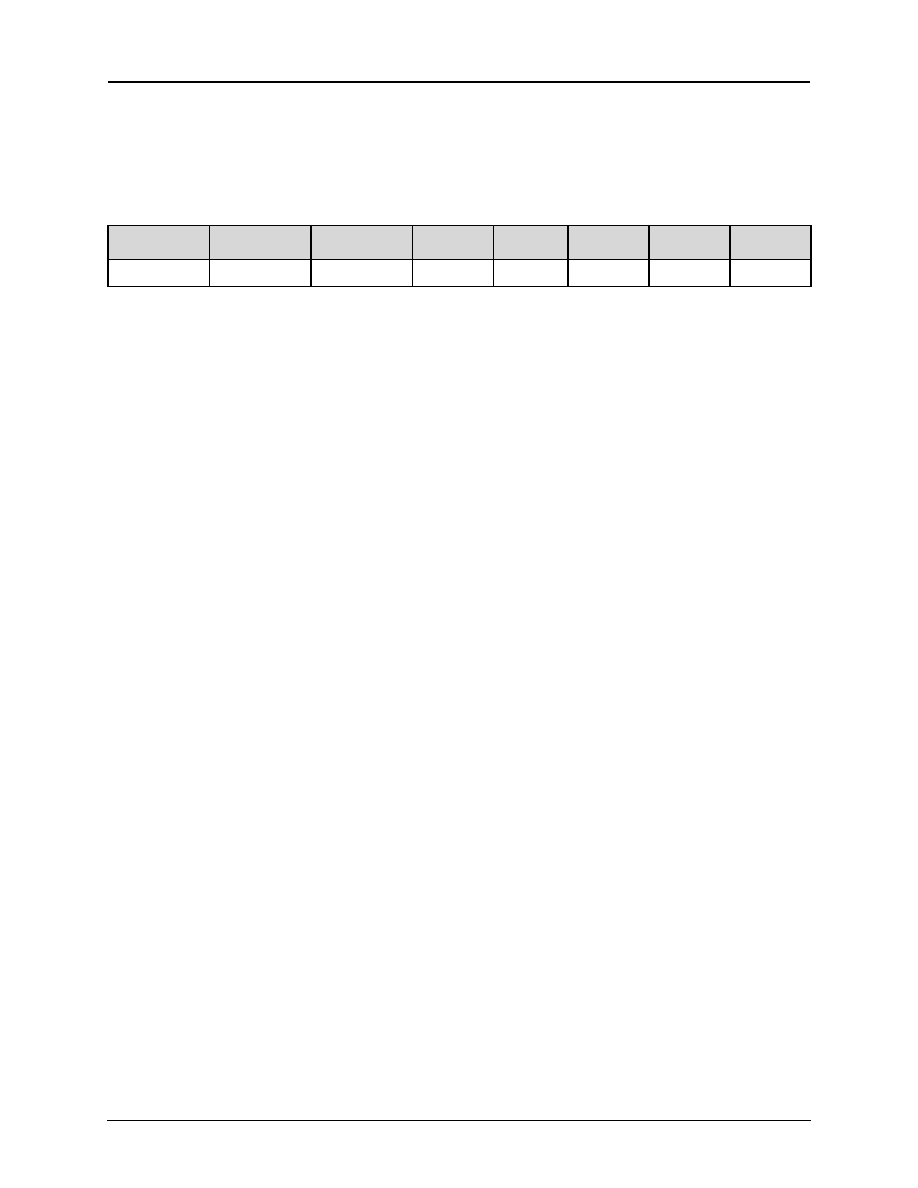

4.0 Clock Sources and Clock Configurations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.1

DS3/E3 Framer Clock and Data Options on the Line Side . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.2

DS1/E1 Clock and Data Options. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

4.3

SI-Bus Interface Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

4.3.1

DS3/E3 Clock and Data Configurations (SI-Bus Interface Mode) . . . . . . . . . . . . . . . . . . . . . . 4-4

4.3.2

DS1/E1 Clock and Data Configurations (SI-Bus Interface Mode) . . . . . . . . . . . . . . . . . . . . . . 4-5

4.4

Serial DS3 Interface Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

4.5

Serial E3 Interface Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

4.6

Payload TSB and Overhead TSB Clocks. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

4.7

Command and Status Processor (CSP) and Microprocessor Clocks. . . . . . . . . . . . . . . . . . . . . . . . . 4-10

4.8

DS1/E1 System and Microprocessor Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-12

4.9

One Hertz Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-13

5.0 Loopbacks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5.1

DS3/E3 Framer and M13 MUX Loopbacks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5.2

DS1/E1 Framer Loopbacks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

5.3

SI-Bus System Side Loopback . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

6.0 Path Conditioning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.1

STS-1 Path Conditioning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.2

DS3 Path Conditioning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

6.3

E3 Path Conditioning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

6.4

DS2 Path Conditioning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

6.5

E2 Path Conditioning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

6.6

VT Path Conditioning. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

6.7

DS1/E1 Path Conditioning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

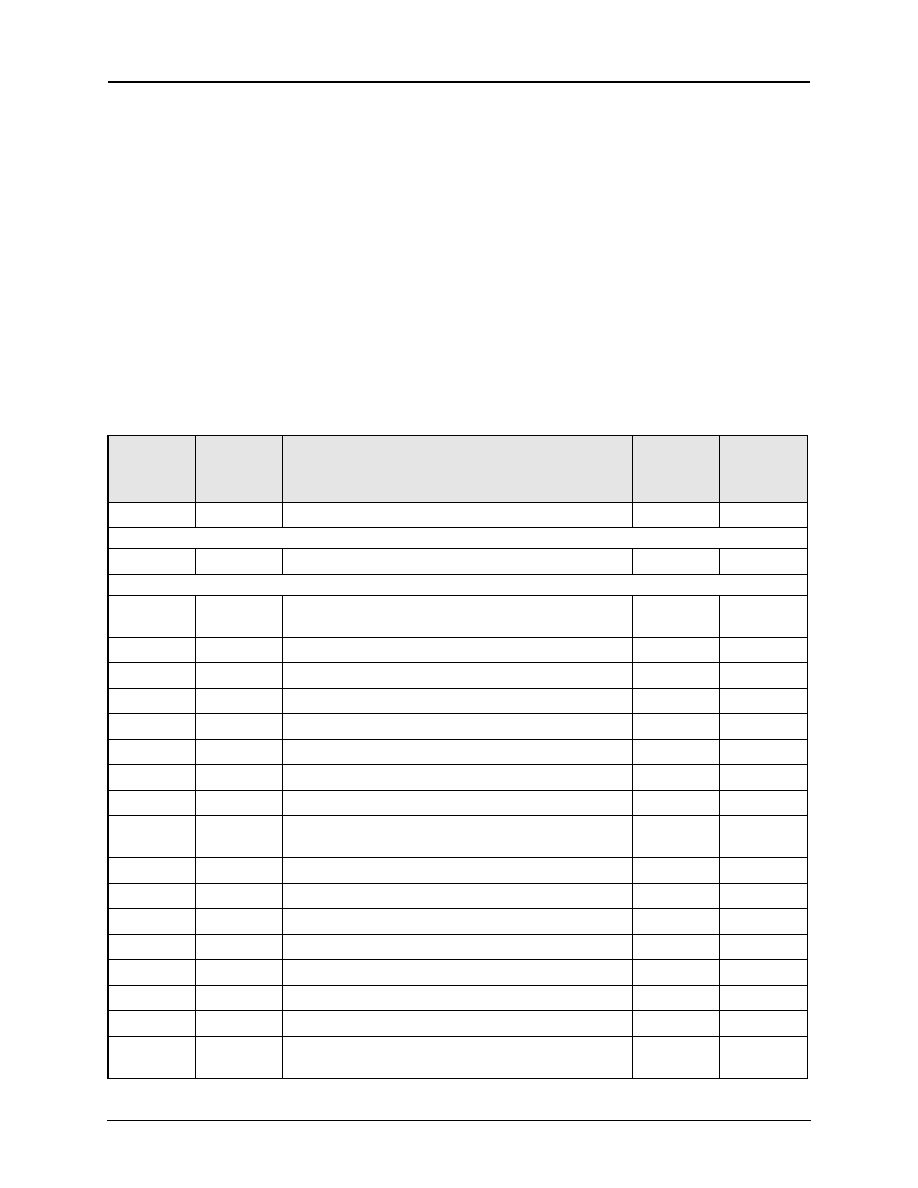

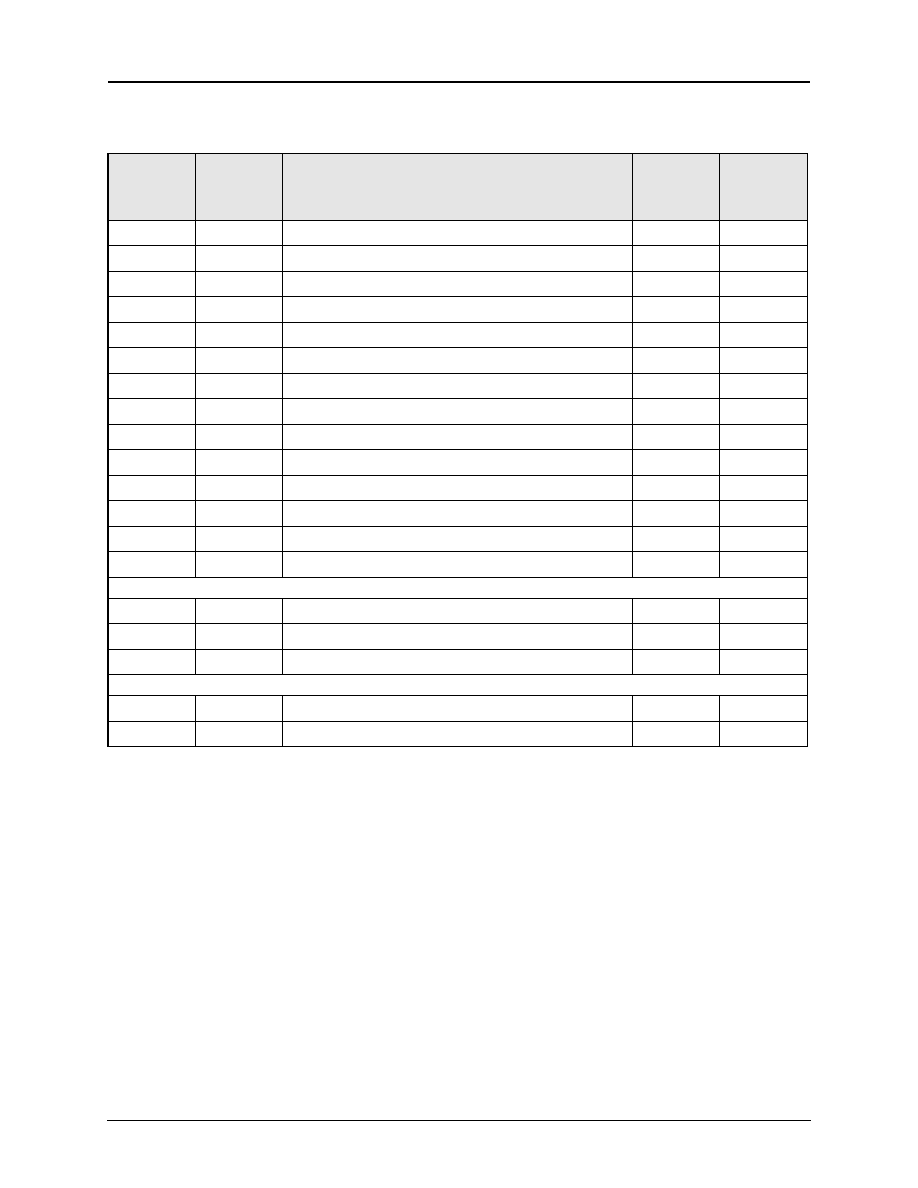

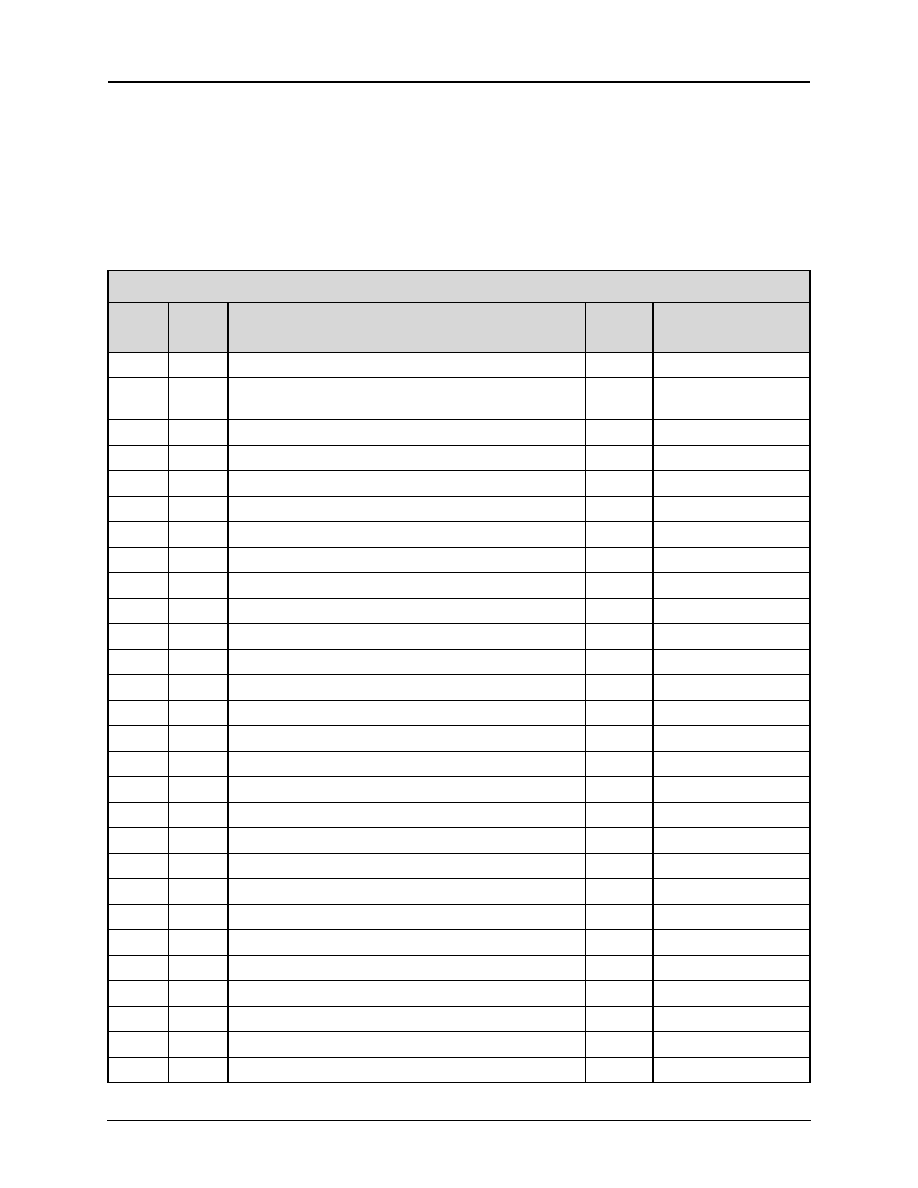

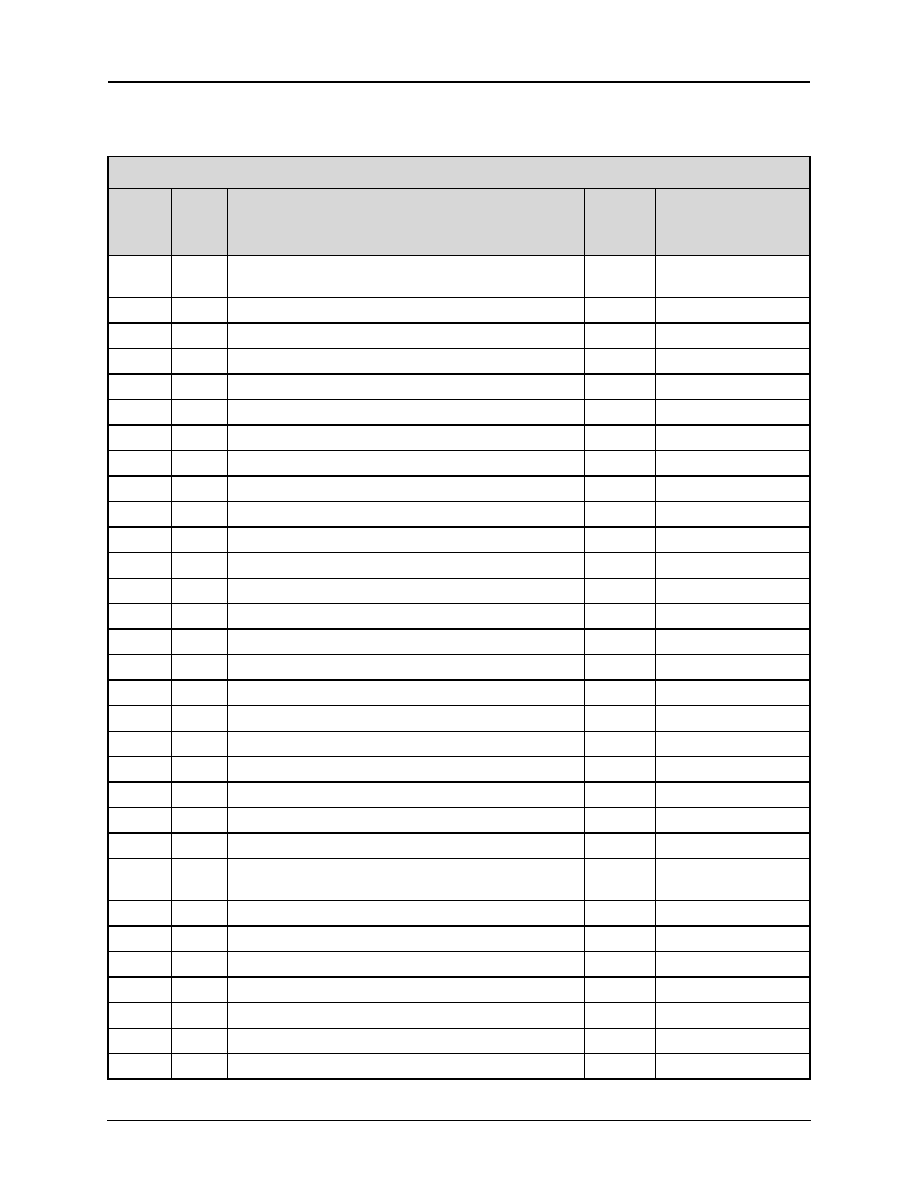

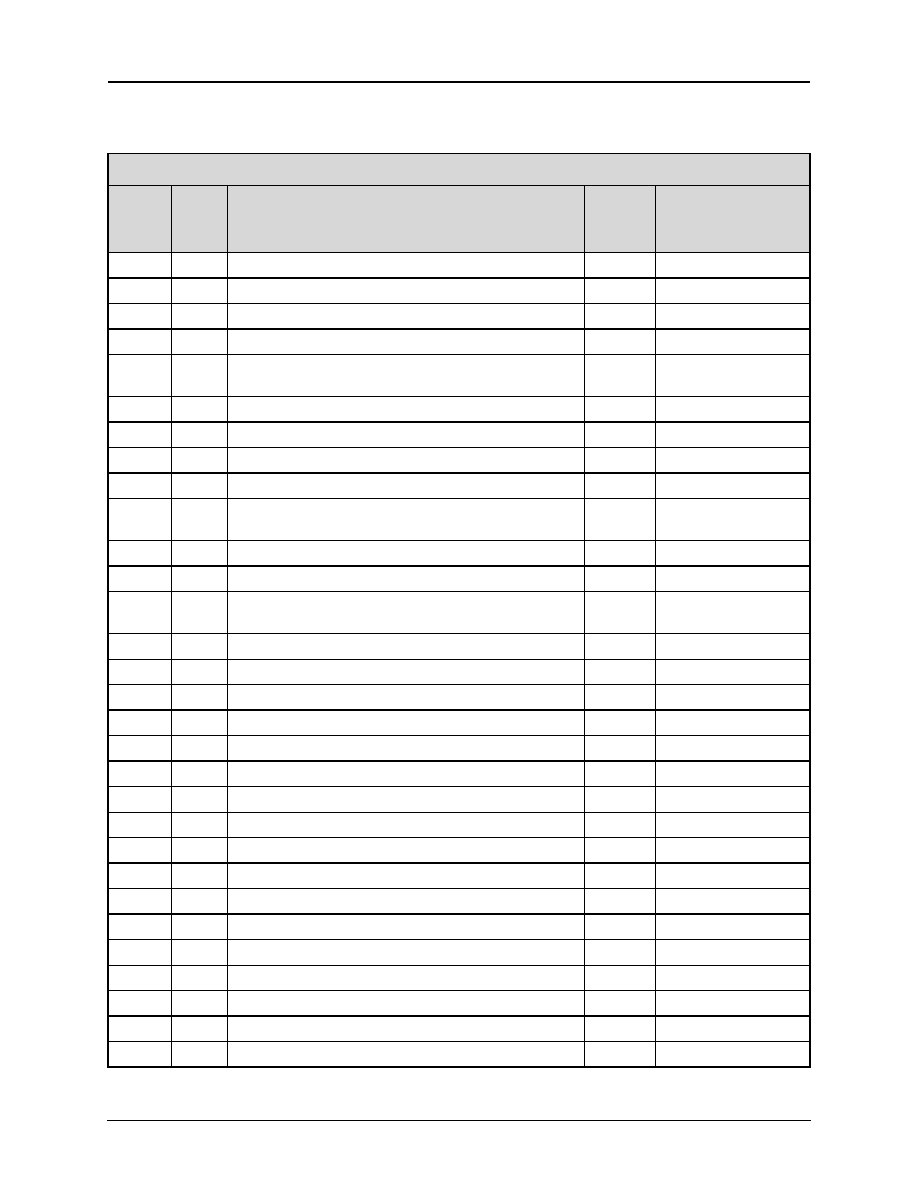

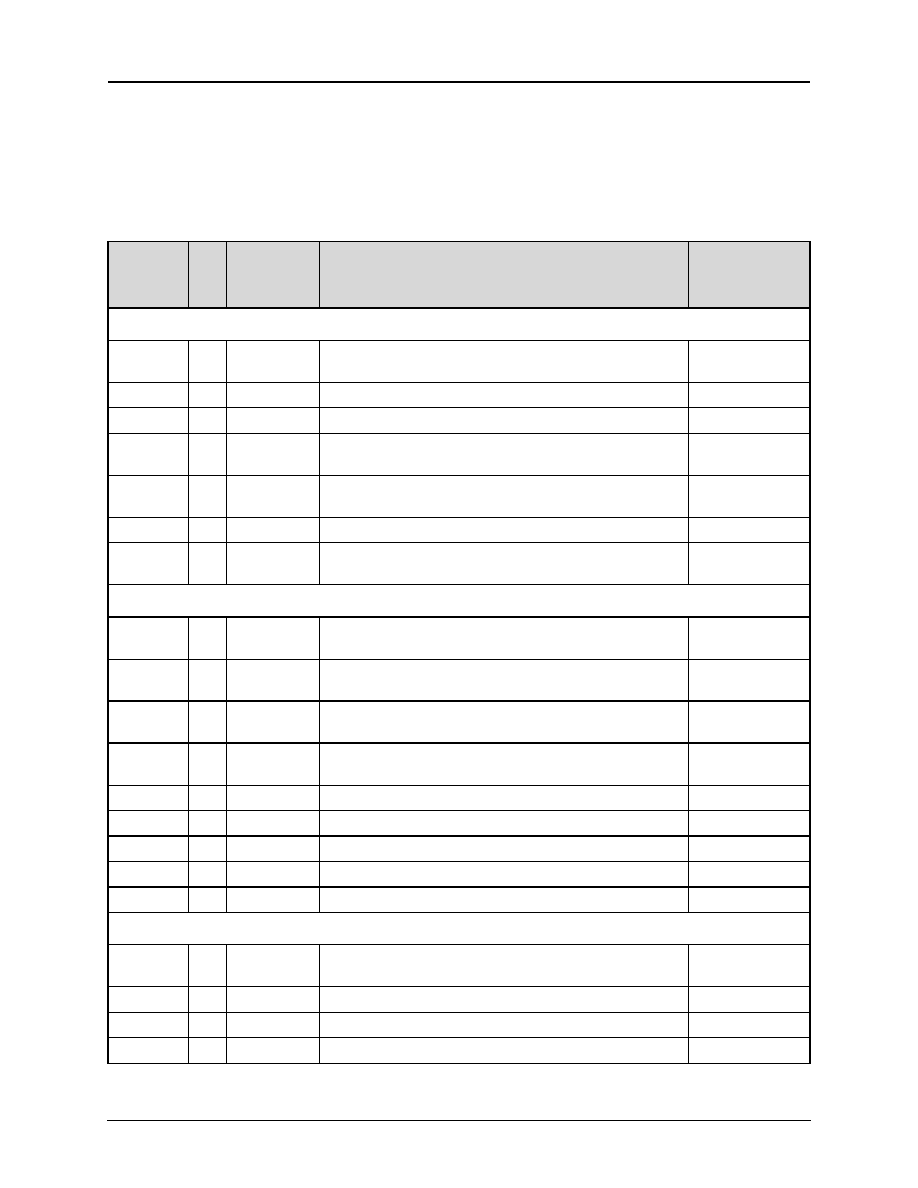

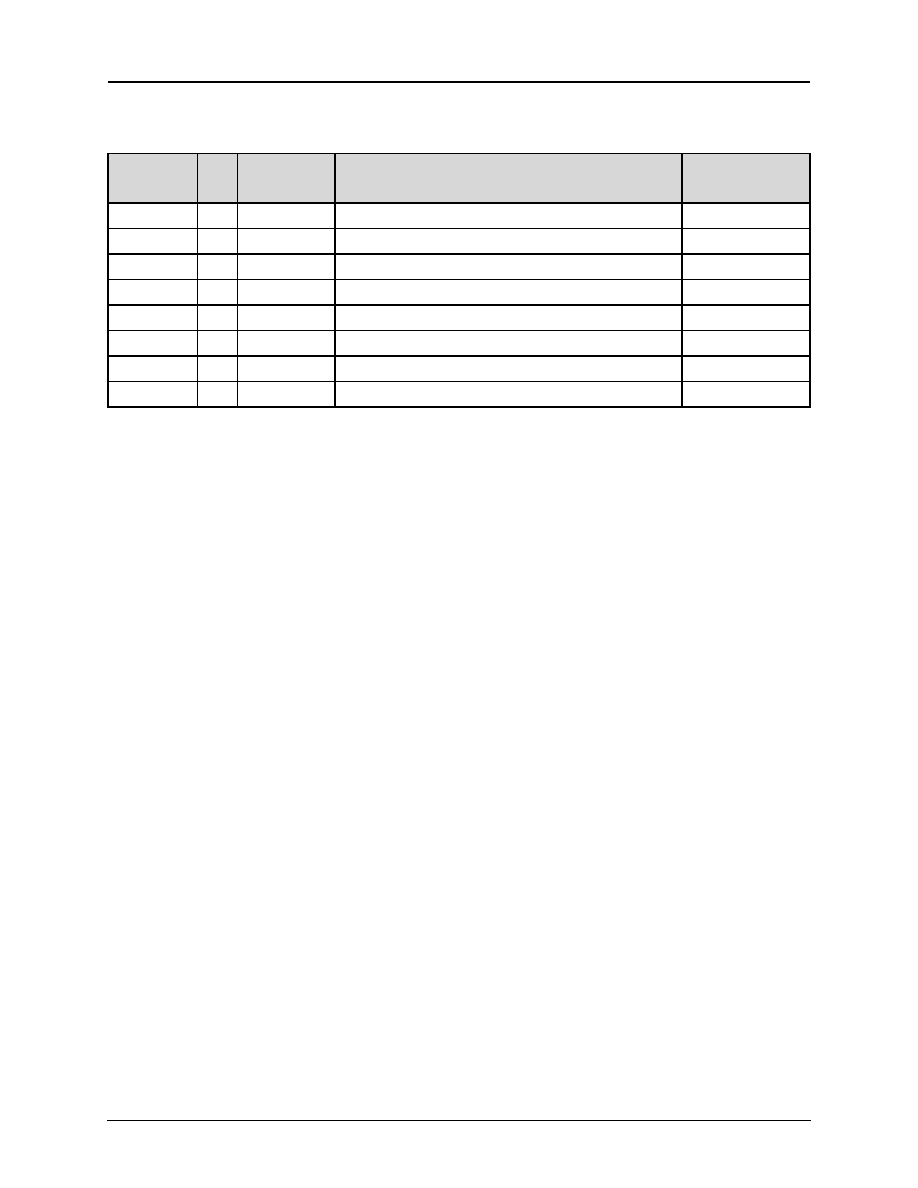

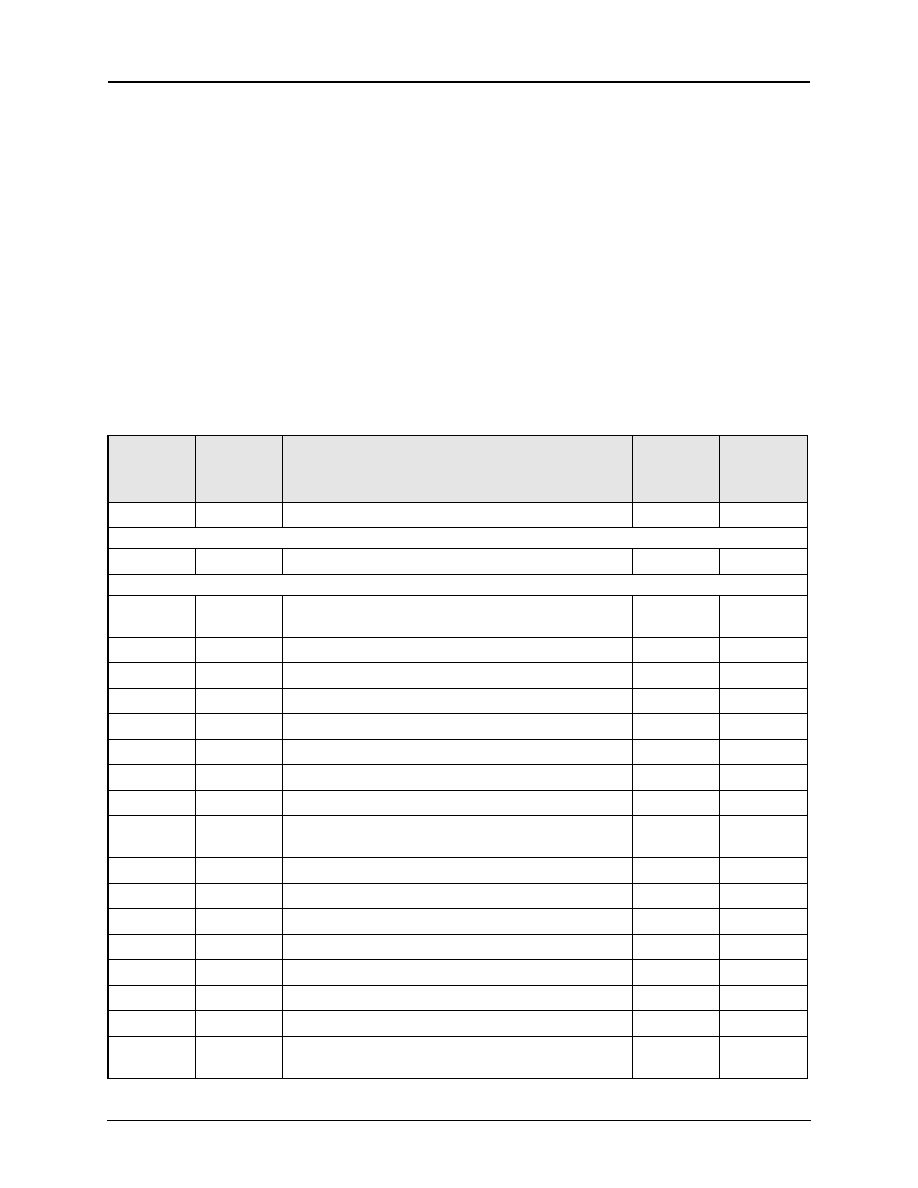

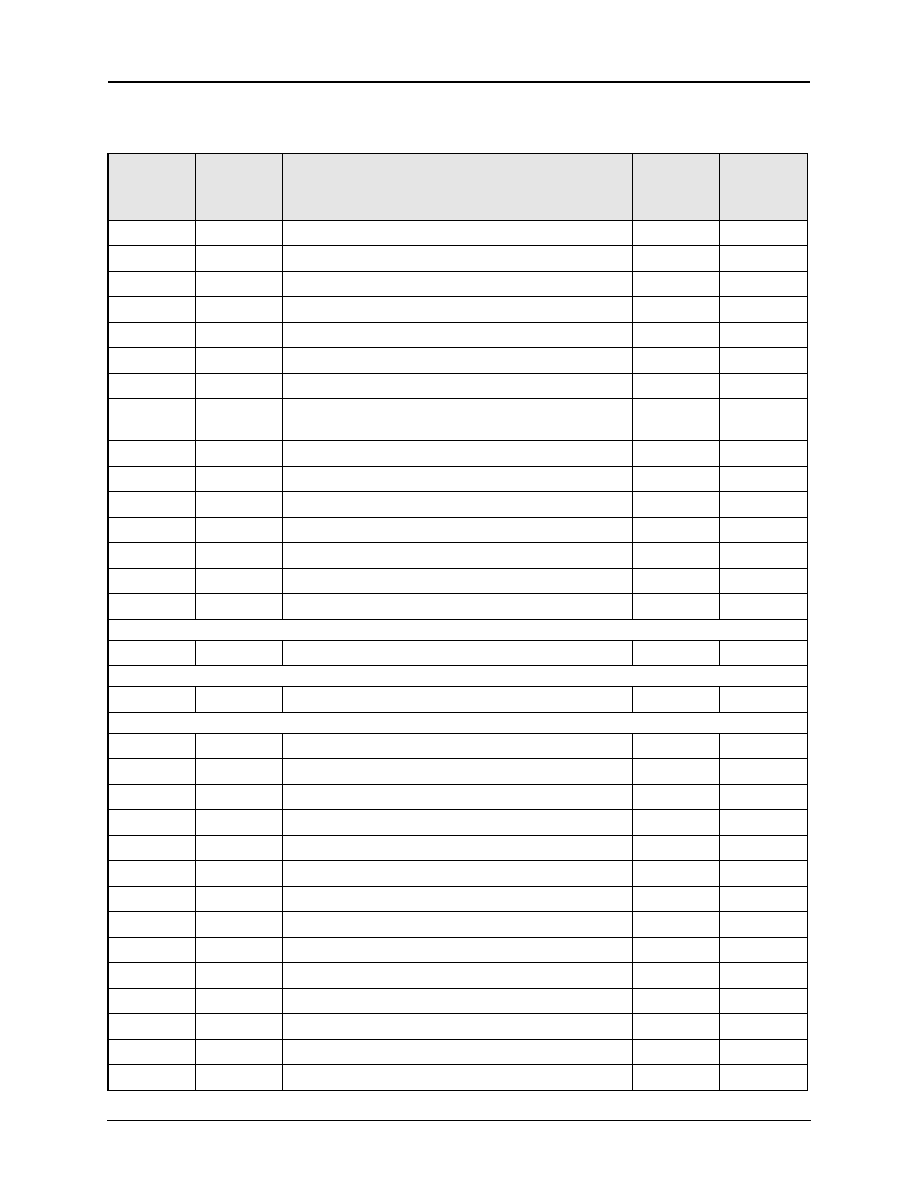

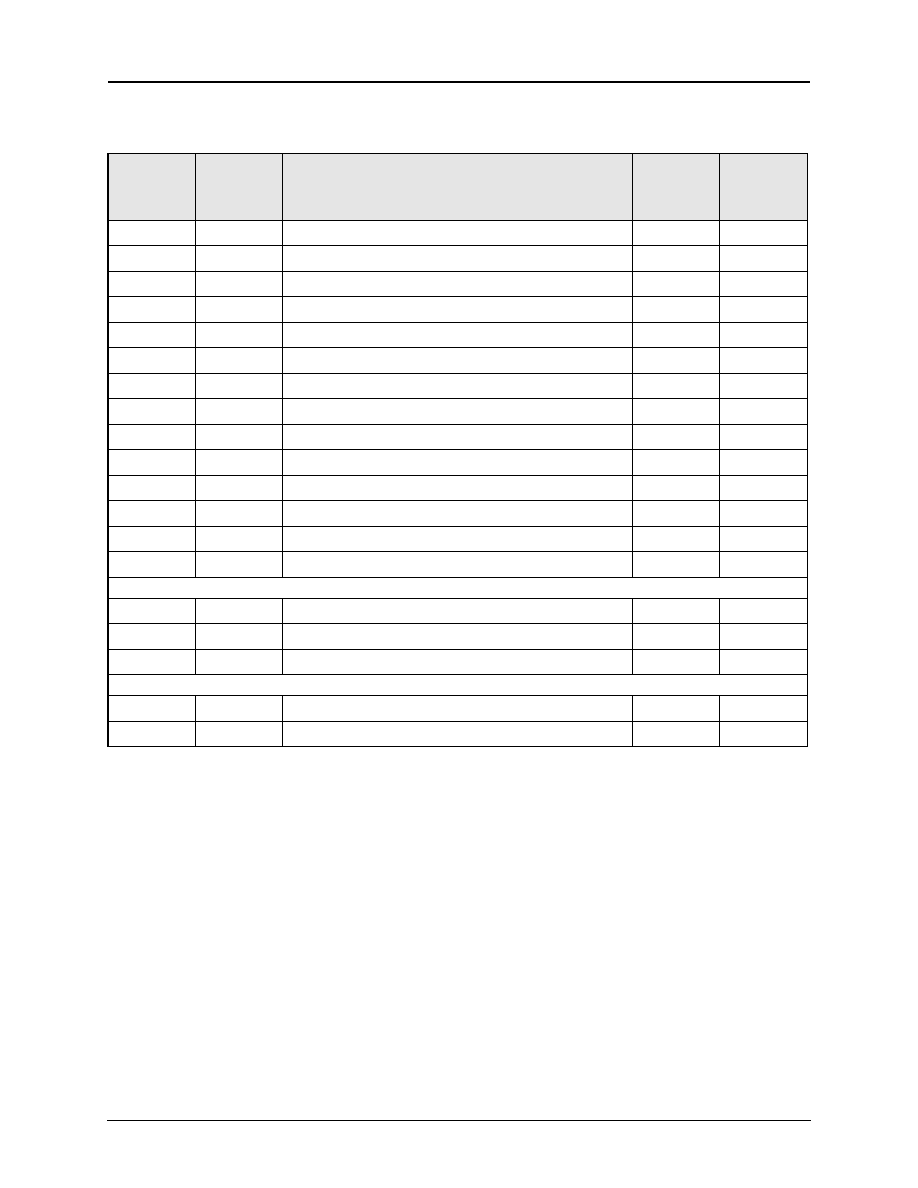

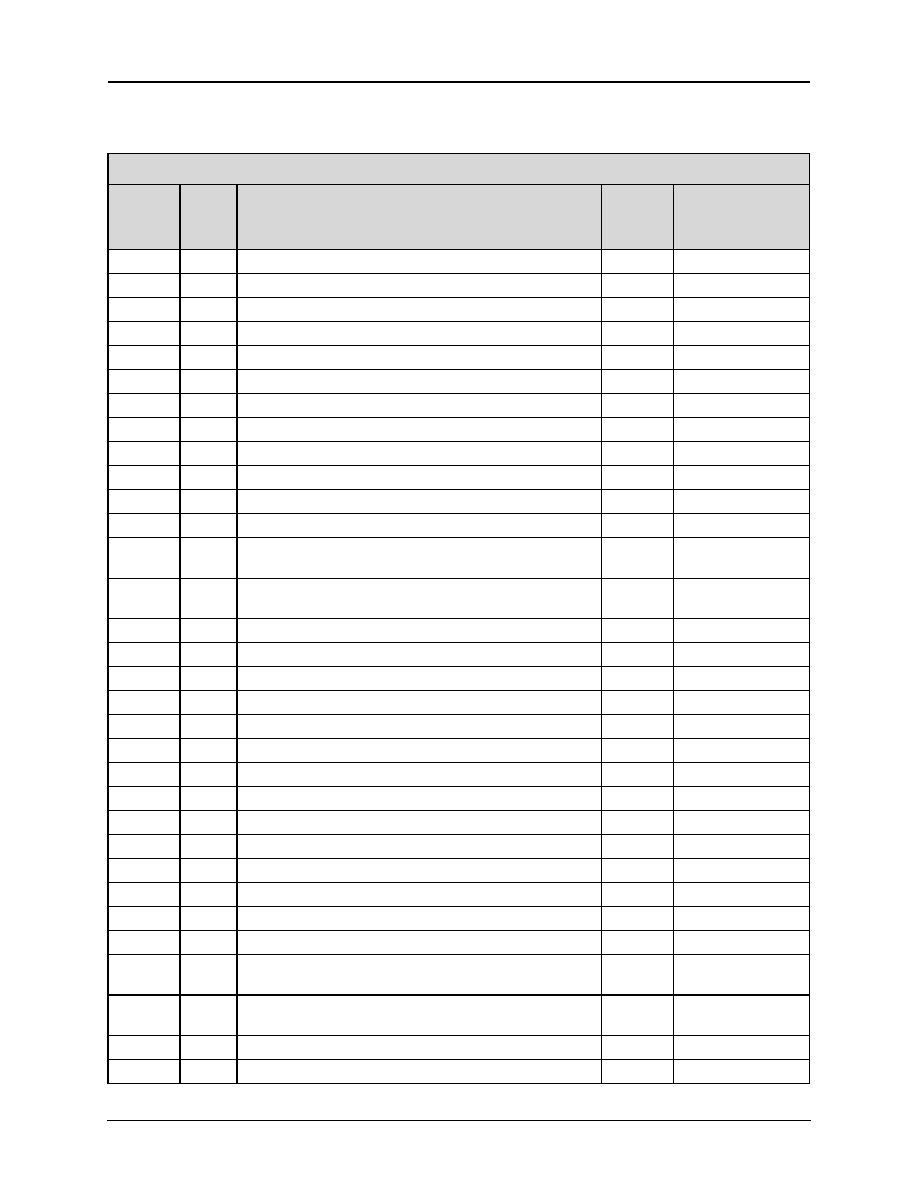

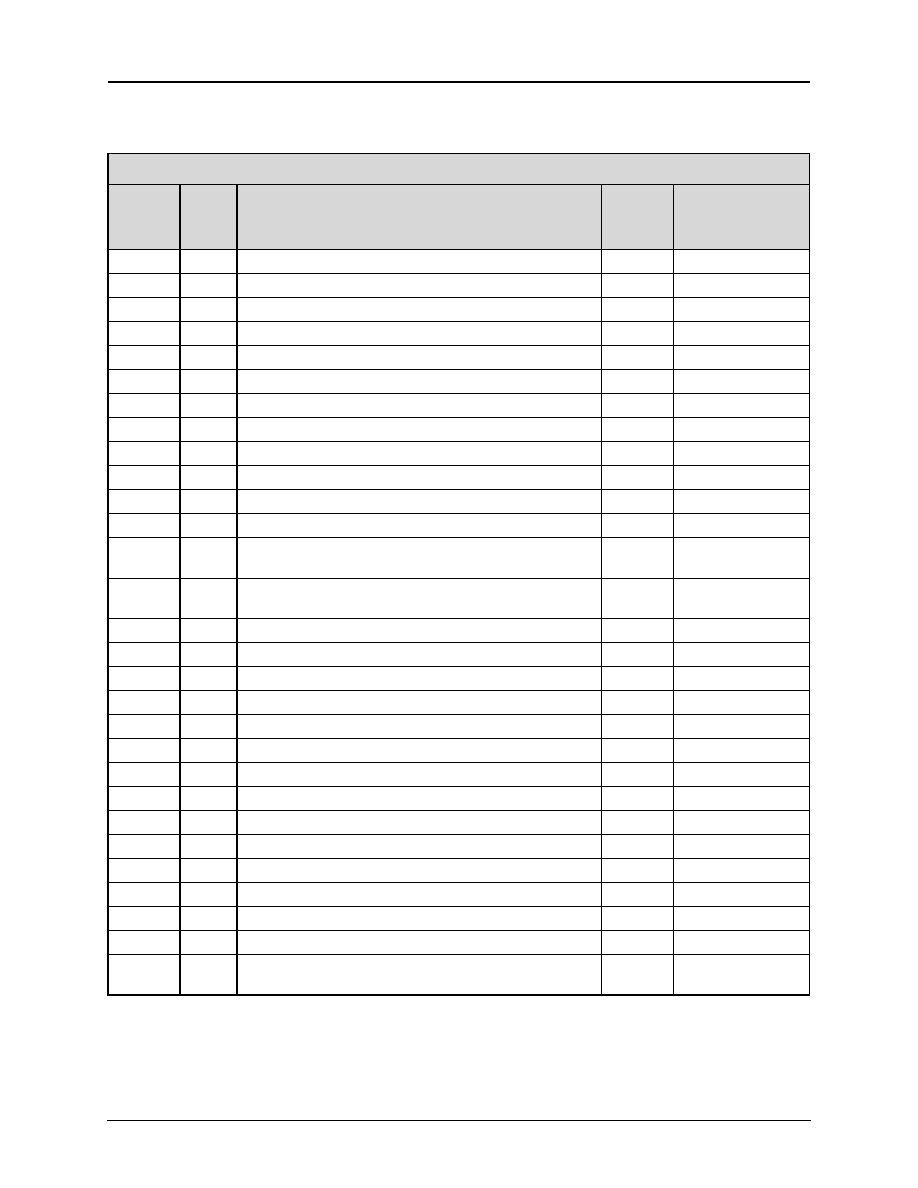

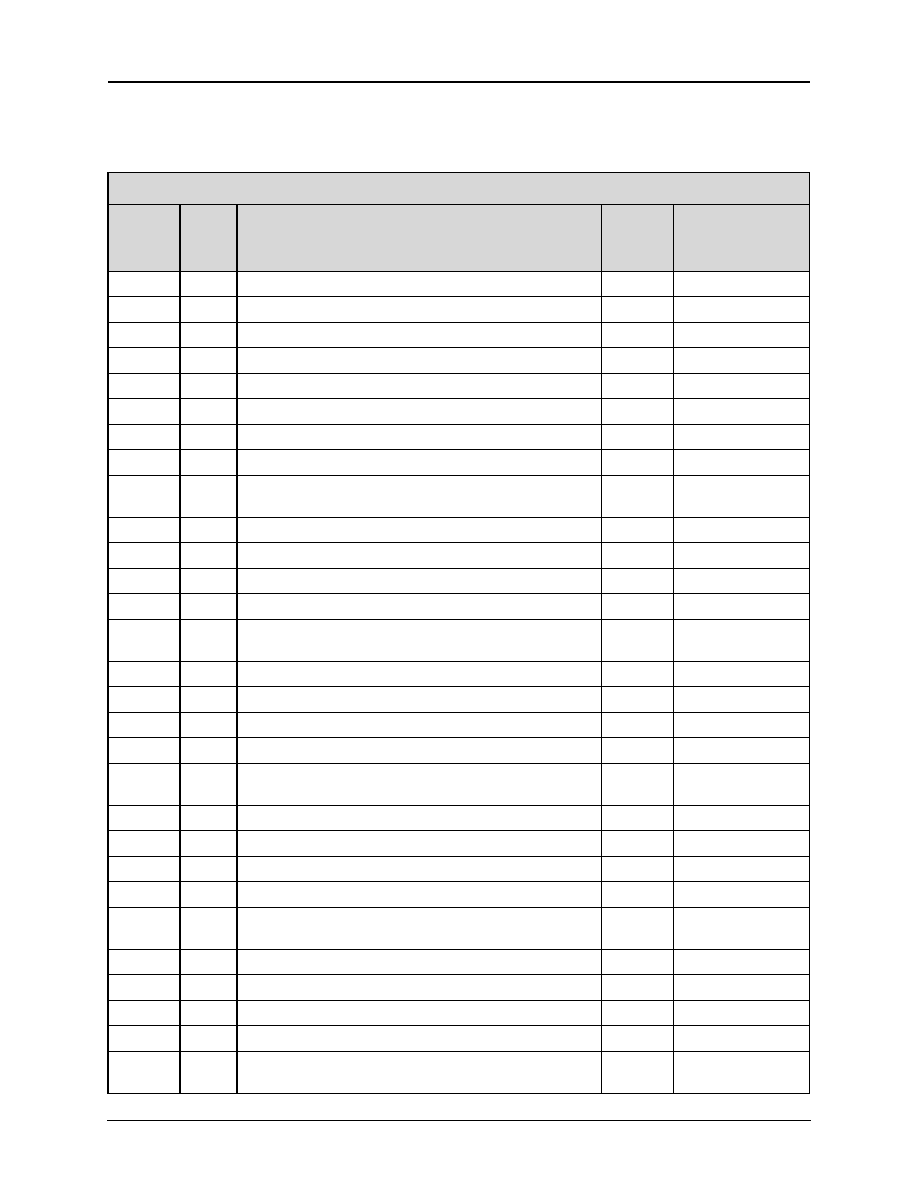

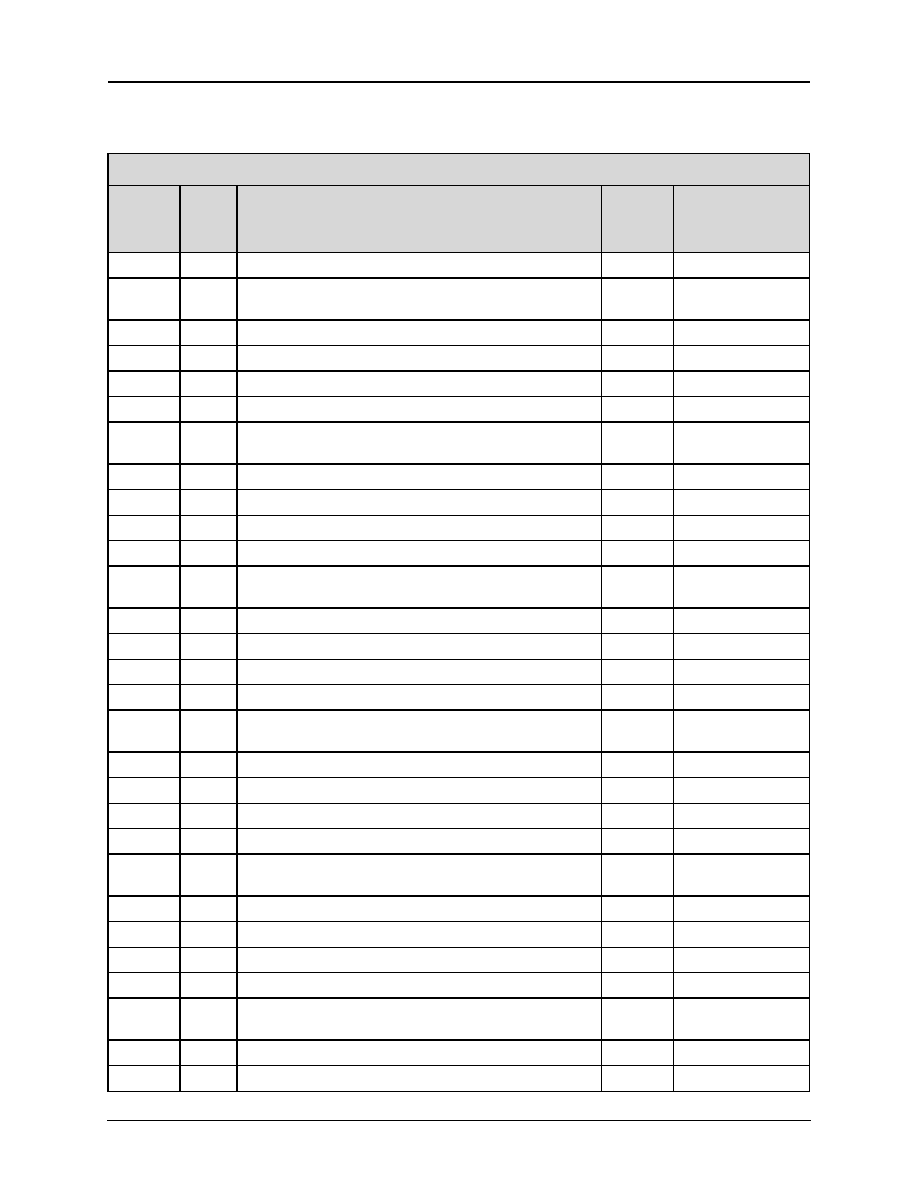

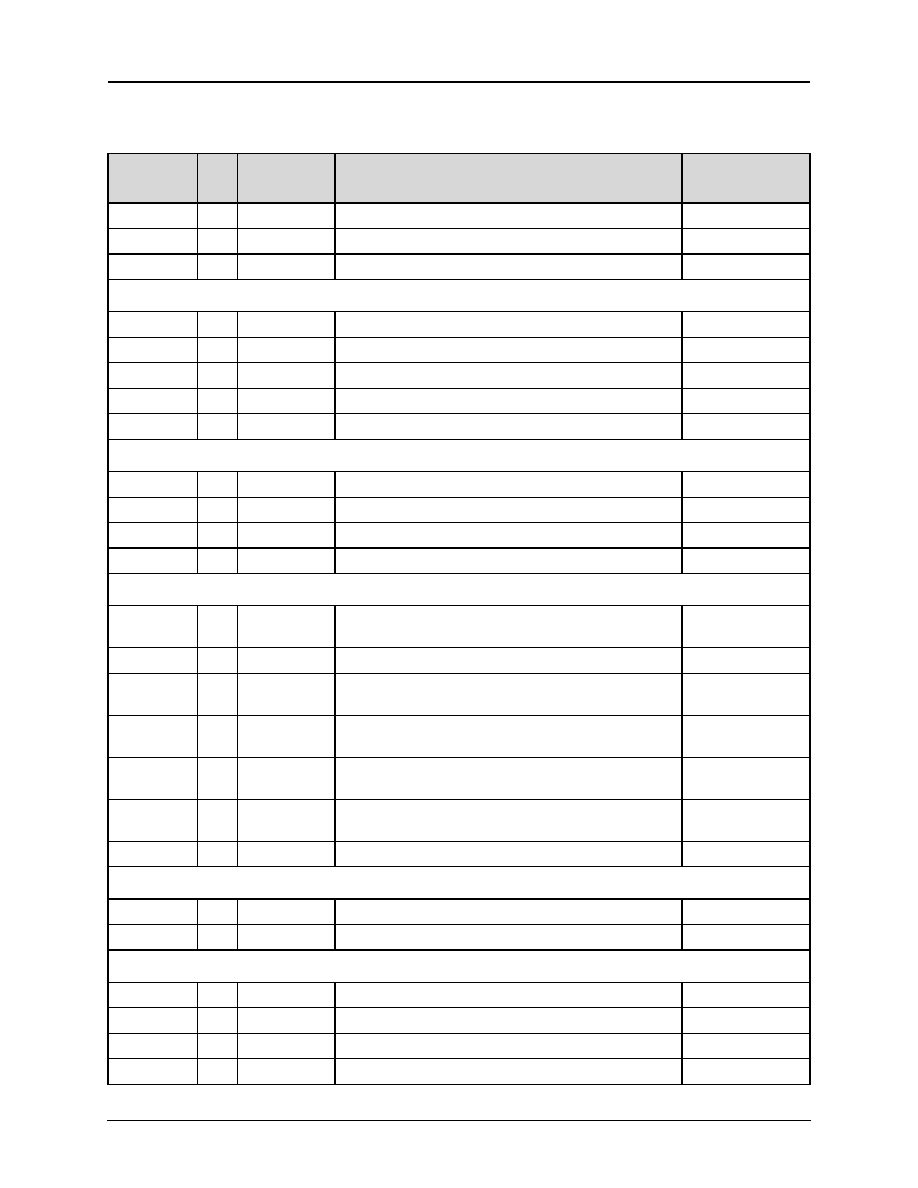

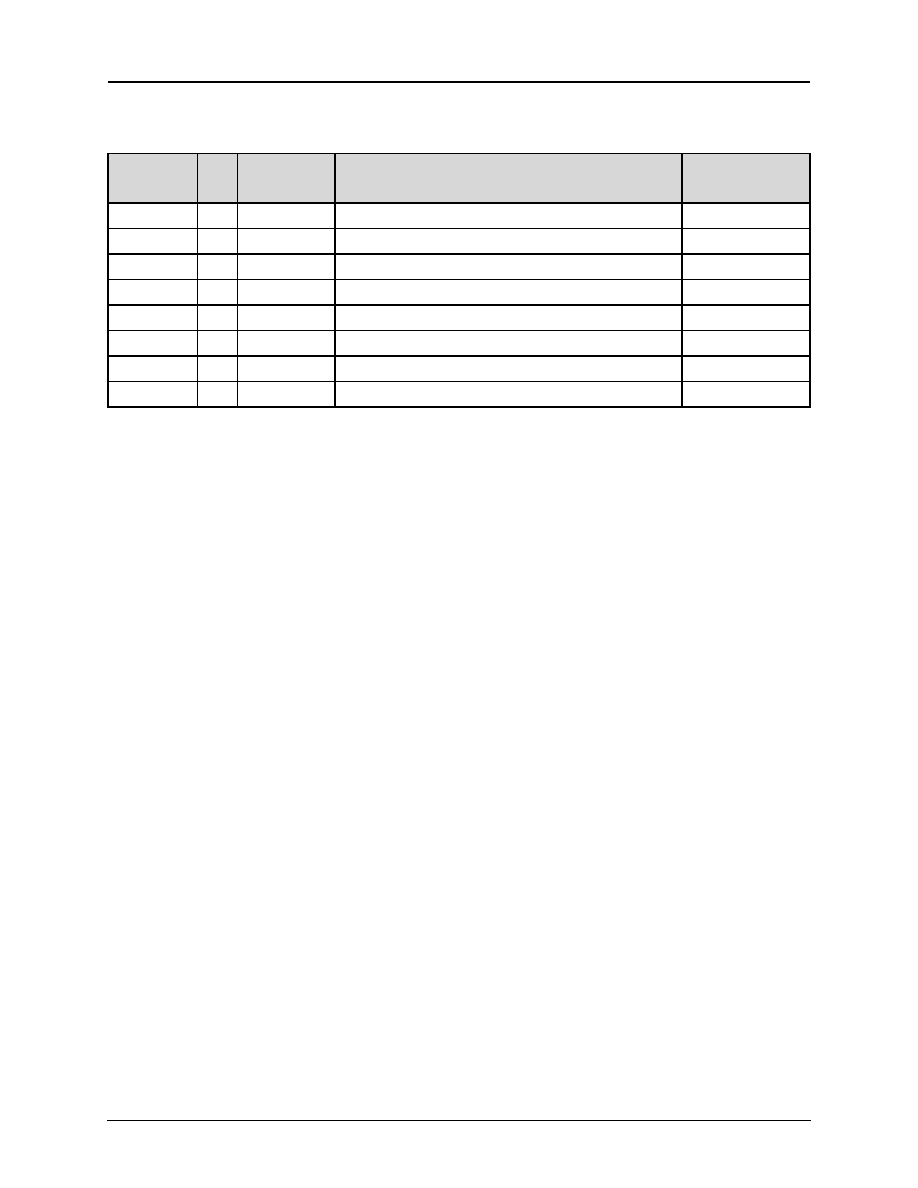

7.0 Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

7.1

Top Level--CX29503 Register Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

7.2

Single Mapper/MUX Block Register Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-2

8.0 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-1

8.1

Global Control and Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-1

0x0000--Device Identification Register (DEV_ID) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-2

Contents

CX29503 Data Sheet

iv

Mindspeed TechnologiesTM

500238B

Advance Information

l

0x0001--Top Level Control Register (TOP_CTL_REG). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-2

0x0002--Top Level Interrupt Status Register (TOP_IRQ_STAT). . . . . . . . . . . . . . . . . . . . . . . 8-2

0x0003--Top Level Interrupt Enable Register (TOP_IRQ_ENB) . . . . . . . . . . . . . . . . . . . . . . . 8-3

0x0004--DS1/E1 Framer Interrupt Request Register 1 (FR_IRR1) . . . . . . . . . . . . . . . . . . . . 8-3

0x0005--DS1/E1 Framer Interrupt Status Register 2 (FR_IRR2) . . . . . . . . . . . . . . . . . . . . . . 8-4

0x0006--DS1/E1 Framer Interrupt Request Register 3 (FR_IRR3) . . . . . . . . . . . . . . . . . . . . 8-4

0x0007--DS1/E1 Framer Interrupt Request Register 4 (FR_IRR4) . . . . . . . . . . . . . . . . . . . . 8-5

0x0008--DS1/E1 Framer Interrupt Enable Register 1 (FR_IE1) . . . . . . . . . . . . . . . . . . . . . . . 8-5

0x0009--DS1/E1 Framer Interrupt Enable Register 2 (FR_IE2) . . . . . . . . . . . . . . . . . . . . . . . 8-6

0x000A--DS1/E1 Framer Interrupt Enable Register 3 (FR_IE3) . . . . . . . . . . . . . . . . . . . . . . . 8-6

0x000B--DS1/E1 Framer Interrupt Enable Register 4 (FR_IE4) . . . . . . . . . . . . . . . . . . . . . . . 8-7

0x000C--Watchdog Interrupt Status Register 4 (WD_INT_STAT) . . . . . . . . . . . . . . . . . . . . . 8-7

0x000D--Watchdog Interrupt Enable Register (WD_INT_ENB). . . . . . . . . . . . . . . . . . . . . . . 8-7

0x000E--Watchdog Control Register (WD_CTL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-7

8.2

Time Slot Bus (TSB) Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-8

0x0100 to 0x01EC--Test Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-8

0x01ED ≠ Unframed Link Control Register 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-8

0x01EE ≠ Unframed Link Control Register 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-9

0x01EF ≠ Unframed Link Control Register 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-9

0x01F0 ≠ Unframed Link Control Register 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-9

0x01F1--Flush FIFO Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-10

0x01F2--TSB FIFO Interrupt Status Register (Used for Diagnostics) . . . . . . . . . . . . . . . . . . 8-10

0x01F3--TSB FIFO Interrupt Enable Register (Used for DS1 Diagnostics) . . . . . . . . . . . . . . 8-11

0x01F4--Overflow Tx Payload FIFO Number Status Register (Used for Diagnostics) . . . . . 8-11

0x01F5--Underflow Tx Payload FIFO Number Status Register (Used for Diagnostics) . . . . 8-12

0x01F6--Overflow Rx Payload FIFO Number Status Register (Used for Diagnostics) . . . . . 8-12

0x01F7--Underflow Rx Payload FIFO Number Status Register (Used for Diagnostics) . . . . 8-12

0x01F8--Overflow Tx Overhead FIFO Number Status Register (Used for Diagnostics) . . . . 8-12

0x01F9--Underflow Tx Overhead FIFO Number Status Register (Used for Diagnostics) . . . 8-13

0x01FA--Overflow Rx Overhead FIFO Number Status Register (Used for Diagnostics) . . . . 8-13

0x01FB--Underflow Rx Overhead FIFO Number Status Register (Used for Diagnostics) . . . 8-13

0x01FC--TSB Module Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-14

0x01FE--Framer Set (FS) Configuration Register 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-14

0x01FF--Framer Set (FS) Configuration Register 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-15

8.3

DS1/E1 Framers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-16

8.3.1

DS1/E1 Framer Set Global Control and Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-16

0x00--Framer Control Register 1 (FCR0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-16

0x01--Framer Control Register 2 (FCR1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-16

8.3.2

DS1/E1 Framer Control and Status Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-17

8.3.2.1 Primary Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-21

0x01--Primary Control Register (CR0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-21

0x03--Interrupt Request Register (IRR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-25

500238B

Mindspeed TechnologiesTM

v

Advance Information

CX29503 Data Sheet

Contents

8.3.2.2 Interrupt Status Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-27

0x04--Alarm 1 Interrupt Status (ISR7) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-28

0x05--Alarm 2 Interrupt Status (ISR6) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-29

0x06--Error Interrupt Status (ISR5). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-29

0x07--Counter Overflow Interrupt Status (ISR4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-30

0x08--Timer Interrupt Status (ISR3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-30

0x09--Data Link 1 Interrupt Status (ISR2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-31

0x0A--Data Link 2 Interrupt Status (ISR1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-31

0x0B--Pattern Interrupt Status (ISR0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-32

8.3.2.3 Interrupt Enable Registers (IER) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-32

0x0C--Alarm 1 Interrupt Enable Register (IER7) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-32

0x0D--Alarm 2 Interrupt Enable Register (IER6) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-33

0x0E--Error Interrupt Enable Register (IER5) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-33

0x0F--Count Overflow Interrupt Enable Register (IER4) . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-33

0x10--Timer Interrupt Enable Register (IER3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-34

0x11--Data Link 1 Interrupt Enable Register (IER2). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-34

0x13--Pattern Interrupt Enable Register (IER0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-35

8.3.2.4 Configuration Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-36

0x14--Loopback Configuration Register (LOOP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-36

0x15--External Data Link Time Slot (DL3_TS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-37

0x16--External Data Link Bit (DL3_BIT). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-38

0x17--Offline Framer Status (FSTAT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-39

0x18--Programmable Input/Output (PIO) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-40

0x19--Programmable Output Enable (POE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-40

8.3.2.5 Digital Receiver Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-41

0x40--Receiver Configuration (RCR0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-41

0x41--Receive Test Pattern Configuration (RPATT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-42

0x42--Receive Loopback Code Detector Configuration (RLB) . . . . . . . . . . . . . . . . . . . . . . . 8-43

0x43--Loopback Activate Code Pattern (LBA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-44

0x44--Loopback Deactivate Code Pattern (LBD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-44

0x45--Receive Alarm Signal Configuration (RALM). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-45

0x46--Alarm/Error/Counter Latch Configuration (LATCH) . . . . . . . . . . . . . . . . . . . . . . . . . . 8-47

0x47--Alarm 1 Status (ALM1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-48

0x48--Alarm 2 Status (ALM2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-49

0x49--Alarm 3 Status (ALM3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-50

8.3.2.6 Performance Monitoring Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-51

0x50--Framing Bit Error Counter LSB (FERR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-51

0x51--Framing Bit Error Counter MSB (FERR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-51

0x52--CRC Error Counter LSB (CERR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-51

0x53--vCRC Error Counter MSB (CERR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-51

0x56--Far End Block Error Counter LSB (FEBE). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-52

0x57--Far End Block Error Counter MSB (FEBE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-52

0x58--PRBS Bit Error Counter LSB (BERR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-52

0x59--PRBS Bit Error Counter MSB (BERR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-52

0x5A--SEF/FRED/COFA Alarm Counter (AERR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-53

Contents

CX29503 Data Sheet

vi

Mindspeed TechnologiesTM

500238B

Advance Information

l

8.3.2.7 Receive Sa-Byte Buffers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-54

0x5B--Receive Sa4 Byte Buffer (RSA4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-54

0x5C--Receive Sa5 Byte Buffer (RSA5) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-54

0x5D--Receive Sa6 Byte Buffer (RSA6) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-55

0x5E--Receive Sa7 Byte Buffer (RSA7) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-55

0x5F--Receive Sa8 Byte Buffer (RSA8) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-56

8.3.2.8 Digital Transmitter Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-57

0x70--Transmit Framer Configuration (TCR0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-57

0x71--Transmitter Configuration (TCR1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-58

0x72--Transmit Frame Format (TFRM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-58

0x73--Transmit Error Insert (TERROR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-60

0x74--Transmit Manual Sa-Byte/FEBE Configuration (TMAN) . . . . . . . . . . . . . . . . . . . . . . . 8-60

0x75--Transmit Alarm Signal Configuration (TALM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-62

0x76--Transmit Test Pattern Configuration (TPATT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-63

0x77--Transmit Inband Loopback Code Configuration (TLB). . . . . . . . . . . . . . . . . . . . . . . . 8-64

0x78--Transmit Inband Loopback Code Pattern (LBP). . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-64

8.3.2.9 Transmit Sa-Byte Buffers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-65

0x7B--Transmit Sa4 Byte Buffer (TSA4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-65

0x7C--Transmit Sa5 Byte Buffer (TSA5) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-65

0x7D--Transmit Sa6 Byte Buffer (TSA6) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-66

0x7E--Transmit Sa7 Byte Buffer (TSA7). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-66

0x7F--Transmit Sa8 Byte Buffer (TSA8). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-67

8.3.2.10 Bit-Oriented Protocol (BOP) Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-68

0xA0--Bit-Oriented Protocol (BOP) Transceiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-68

0xA1--Transmit BOP Code Word (TBOP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-70

0xA2--Receive BOP code word (RBOP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-70

0xA3--BOP Status (BOP_STAT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-71

8.3.2.11 Data Link Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-72

0xA4--DL1 Time Slot Enable (DL1_TS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-72

0xA5--DL1 Bit Enable (DL1_BIT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-73

0xA6--DL1 Control (DL1_CTL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-73

0xA7--RDL 1 FIFO Fill Control (RDL1_FFC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-75

0xA8--Receive Data Link FIFO 1 (RDL1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-76

0xA9--RDL 1 Status (RDL1_STAT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-78

0xAA--Performance Report Message (PRM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-79

0xAB--TDL 1 FIFO Empty Control (TDL1_FEC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-81

0xAC--TDL 1 End Of Message Control (TDL1_EOM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-82

0AD--Transmit Data Link FIFO 1 (TDL1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-82

0xAE--TDL 1 Status (TDL1_STAT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-83

8.3.2.12 Data Link Test Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-84

0xBA--DLINK Test Configuration (DL_TEST1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-84

0xBB--DLINK Test Status (DL_TEST2). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-84

0xBC--DLINK Test Status (DL_TEST3). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-84

0xBD--DLINK Test Control 1 or Configuration 1 (DL_TEST4) . . . . . . . . . . . . . . . . . . . . . . . 8-84

8.3.2.13 Payload Loopback Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-85

0xD9--Payload Loopback Status Register (PLB_STAT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-85

500238B

Mindspeed TechnologiesTM

vii

Advance Information

CX29503 Data Sheet

Contents

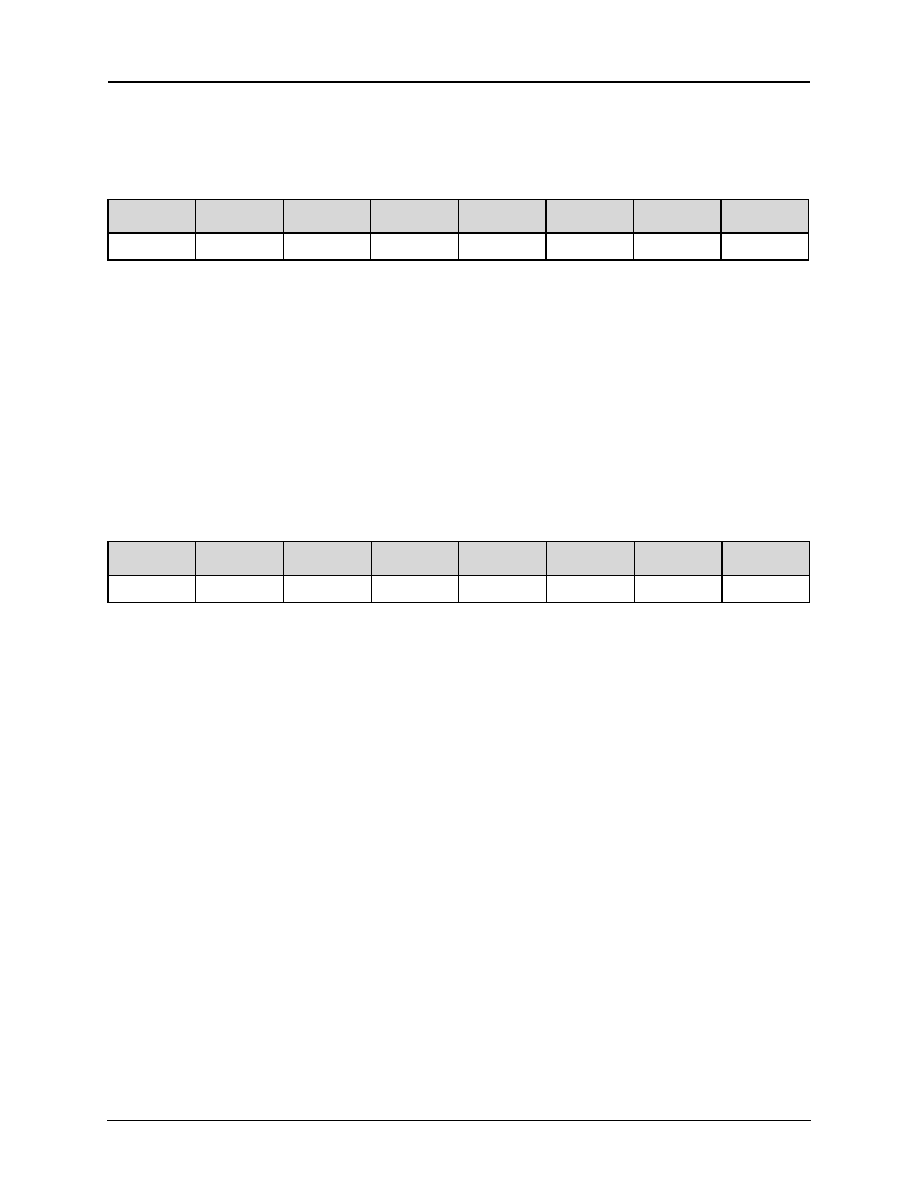

8.4

M13/E13 Multiplexer/Demultiplexer (MUX/DEMUX) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-86

8.4.1

M13/E13 Global Status and Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-100

0x5000--M13/E13 System Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-100

0x5006--DS3/E3 Framer Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-100

0x5007--M13 Interrupt Source Status Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-101

0x500A--DS2/E2 Channel 2 Framer Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-105

0x500B--DS2/E2 Channel 3 Framer Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-105

0x500C--DS2/E2 Channel 4 Framer Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-105

0x500D--DS2/E2 Channel 5 Framer Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-105

0x500E--DS2/E2 Channel 6 Framer Control Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-105

0x500F--DS2/E2 Channel 7 Framer Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-105

0x5010--DS2/E2 Channel 1 Loopback Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . 8-105

0x5011--DS2/E2 Channel 2 Loopback Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . 8-105

0x5012--DS2/E2 Channel 3 Loopback Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . 8-105

0x5013--DS2/E2 Channel 4 Loopback Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . 8-105

0x5014--DS2/E2 Channel 5 Loopback Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . 8-105

0x5015--DS2/E2 Channel 6 Loopback Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . 8-105

0x5016 --DS2/E2 Channel 7 Loopback Control Register

(Loopback Type 2 Control Registers) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-106

0x5017--M13/E13 Group 1 Interrupt Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-106

0x5018--M13/E13 Group 2 Interrupt Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-107

0x5019--M13/E13 Group 3 Interrupt Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-107

0x501A--M13/E13 Group 4 Interrupt Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-108

0x501B to 0x5036--M13/E13 Channel 1≠28 Control Registers . . . . . . . . . . . . . . . . . . . . . 8-108

0x5037 to 0x5052--M13/E13 Channel 1≠28 Line Loopback Control Registers

(Loopback Type 4 Control Registers) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-108

8.4.2

DS3/E3 Framer Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-109

0x5220--Mode Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-109

0x5221--Counter Interrupt Enable Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-110

0x5222--Alarm Start Interrupt Enable Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-111

0x5223--Alarm End Interrupt Enable Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-112

0x5224--Feature1 Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-113

0x5225--Feature2 Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-114

0x5226--Feature3 Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-115

0x5227--Feature4 Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-116

0x5228--Feature5 Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-116

0x5229--Transmit Overhead Insertion1 Control Register. . . . . . . . . . . . . . . . . . . . . . . . . . 8-118

0x522A--Transmit Overhead Insertion2 Control Register . . . . . . . . . . . . . . . . . . . . . . . . . 8-120

0x522B--REXTCK Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-122

0x522C--Receive Overhead Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-123

0x522D--Transmit Data Link Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-124

0x522E--Transmit Data Link Threshold Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . 8-124

0x522F and 0x5230--Transmit Data Link Message Byte

(Lower Address and Higher Address) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-125

0x5231--Receive Data Link Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-125

0x5232--Receive Data Link Threshold Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . 8-126

0x5233--Transmit FEAC Channel Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-126

Contents

CX29503 Data Sheet

viii

Mindspeed TechnologiesTM

500238B

Advance Information

l

0x5240--DS3/E3 Maintenance Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-127

0x5241--Interrupt Request Register (IRR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-127

0x5242--Counter Interrupt Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-129

0x5243--Alarm Start Interrupt Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-130

0x5244--Alarm End Interrupt Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-131

0x5246--E3-G.832 MA Fields Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-131

0x5247--E3-G.832 SSM Field Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-131

0x5248--Transmit Data Link FEAC Interrupt Status Register (ISR) . . . . . . . . . . . . . . . . . . 8-132

0x524B--Receive Data Link Interrupt Status Register (ISR) . . . . . . . . . . . . . . . . . . . . . . . 8-133

0x524C--Receive Data Link Message Byte. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-134

0x524F--Receive FEAC Byte. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-135

0x5250--Receive FEAC Stack Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-135

0x5251--Receive FEAC Interrupt Status Register (SR17i) . . . . . . . . . . . . . . . . . . . . . . . . . 8-136

0x5252--Receive AIC Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-137

0x5260 and 0x5261--DS3/E3 Parity (P bits) Error Counter . . . . . . . . . . . . . . . . . . . . . . . . 8-138

0x5262 and 0x5263--DS3 Parity Disagreement Counter . . . . . . . . . . . . . . . . . . . . . . . . . . 8-138

0x5264 and 0x5265--DS3 X-Bit Disagreement Counter. . . . . . . . . . . . . . . . . . . . . . . . . . . 8-139

0x5266 and 0x5267--DS3/E3 Frame Error Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-139

0x5268 and 0x5269--DS3 Path Parity (CP bits) Error Counter . . . . . . . . . . . . . . . . . . . . . 8-140

0x526A and 0x526B--DS3/E3 FEBE Event Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-140

0x526C and 0x526D--DS3/E3 Excessive Zeros Counter (Ctr06i) . . . . . . . . . . . . . . . . . . . . 8-141

0x526E, 0x526F, and 0x5270--DS3/E3 LCV Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-141

8.4.3

DS2/E2 Framer/MUX Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-142

0x5400--DS2/E2 Receiver Interrupt Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-142

0x5401--DS2/E2 Interrupt Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-142

0x5402--DS2/E2 Framer Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-143

0x5403--DS2/E2 Framer 1 Transmit Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-143

0x5423--DS2/E2 Framer 2 Transmit Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-143

0x5443--DS2/E2 Framer 3 Transmit Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-143

0x5463--DS2/E2 Framer 4 Transmit Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-143

0x5483--DS2/E2 Framer 5 Transmit Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-143

0x54A3--DS2/E2 Framer 6 Transmit Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-143

0x54C3--DS2/E2 Framer 7 Transmit Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-144

0x5404--DS2/E2 Framer 1 Receive Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-144

0x5424--DS2/E2 Framer 2 Receive Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-144

0x5444--DS2/E2 Framer 3 Receive Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-144

0x5464--DS2/E2 Framer 4 Receive Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-144

0x5484--DS2/E2 Framer 5 Receive Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-144

0x54A4--DS2/E2 Framer 6 Receive Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-144

0x54C4--DS2/E2 Framer 7 Receive Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-144

0x5405--DS2/E2 Framer 1 Counter/Loopback Interrupt Enable . . . . . . . . . . . . . . . . . . . . . 8-145

0x5425--DS2/E2 Framer 2 Counter/Loopback Interrupt Enable . . . . . . . . . . . . . . . . . . . . . 8-145

0x5445--DS2/E2 Framer 3 Counter/Loopback Interrupt Enable . . . . . . . . . . . . . . . . . . . . . 8-145

0x5465--DS2/E2 Framer 4 Counter/Loopback Interrupt Enable . . . . . . . . . . . . . . . . . . . . . 8-145

0x5485--DS2/E2 Framer 5 Counter/Loopback Interrupt Enable . . . . . . . . . . . . . . . . . . . . . 8-145

0x54A5--DS2/E2 Framer 6 Counter/Loopback Interrupt Enable. . . . . . . . . . . . . . . . . . . . . 8-145

500238B

Mindspeed TechnologiesTM

ix

Advance Information

CX29503 Data Sheet

Contents

0x54C5--DS2/E2 Framer 7 Counter/Loopback Interrupt Enable. . . . . . . . . . . . . . . . . . . . . 8-146

0x5406--DS2/E2 Framer 1 Alarm Start Interrupt Enable . . . . . . . . . . . . . . . . . . . . . . . . . . 8-146

0x5426--DS2/E2 Framer 2 Alarm Start Interrupt Enable . . . . . . . . . . . . . . . . . . . . . . . . . . 8-146

0x5446--DS2/E2 Framer 3 Alarm Start Interrupt Enable . . . . . . . . . . . . . . . . . . . . . . . . . . 8-146

0x5466--DS2/E2 Framer 4 Alarm Start Interrupt Enable . . . . . . . . . . . . . . . . . . . . . . . . . . 8-146

0x5486--DS2/E2 Framer 5 Alarm Start Interrupt Enable . . . . . . . . . . . . . . . . . . . . . . . . . . 8-146

0x54A6--DS2/E2 Framer 6 Alarm Start Interrupt Enable . . . . . . . . . . . . . . . . . . . . . . . . . . 8-146

0x54C6--DS2/E2 Framer 7 Alarm Start Interrupt Enable . . . . . . . . . . . . . . . . . . . . . . . . . . 8-147

0x5407--DS2/E2 Framer 1 Alarm End Interrupt Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-147

0x5427--DS2/E2 Framer 2 Alarm End Interrupt Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-147

0x5447--DS2/E2 Framer 3 Alarm End Interrupt Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-147

0x5467--DS2/E2 Framer 4 Alarm End Interrupt Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-147

0x5487--DS2/E2 Framer 5 Alarm End Interrupt Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-147

0x54A7--DS2/E2 Framer 6 Alarm End Interrupt Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-147

0x54C7--DS2/E2 Framer 7 Alarm End Interrupt Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-148

0x5408--DS2/E2 Framer 1 Transmit FIFO Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-148

0x5428--DS2/E2 Framer 2 Transmit FIFO Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-148

0x5448--DS2/E2 Framer 3 Transmit FIFO Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-148

0x5468--DS2/E2 Framer 4 Transmit FIFO Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-148

0x5488--DS2/E2 Framer 5 Transmit FIFO Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-148

0x54A8--DS2/E2 Framer 6 Transmit FIFO Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-148

0x54C8--DS2/E2 Framer 7 Transmit FIFO Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-149

0x5409--DS2/E2 Framer 1 Counter/Loopback Interrupt Status . . . . . . . . . . . . . . . . . . . . . 8-149

0x5429--DS2/E2 Framer 2 Counter/Loopback Interrupt Status . . . . . . . . . . . . . . . . . . . . . 8-149

0x5449--DS2/E2 Framer 3 Counter/Loopback Interrupt Status . . . . . . . . . . . . . . . . . . . . . 8-149

0x5469--DS2/E2 Framer 4 Counter/Loopback Interrupt Status . . . . . . . . . . . . . . . . . . . . . 8-149

0x5489--DS2/E2 Framer 5 Counter/Loopback Interrupt Status . . . . . . . . . . . . . . . . . . . . . 8-149

0x54A9--DS2/E2 Framer 6 Counter/Loopback Interrupt Status . . . . . . . . . . . . . . . . . . . . . 8-149

0x54C9--DS2/E2 Framer 7 Counter/Loopback Interrupt Status . . . . . . . . . . . . . . . . . . . . . 8-150

0x540A--DS2/E2 Framer 1 Alarm Start Interrupt Status . . . . . . . . . . . . . . . . . . . . . . . . . . 8-150

0x542A--DS2/E2 Framer 2 Alarm Start Interrupt Status . . . . . . . . . . . . . . . . . . . . . . . . . . 8-150

0x544A--DS2/E2 Framer 3 Alarm Start Interrupt Status . . . . . . . . . . . . . . . . . . . . . . . . . . 8-150

0x546A--DS2/E2 Framer 4 Alarm Start Interrupt Status . . . . . . . . . . . . . . . . . . . . . . . . . . 8-150

0x548A--DS2/E2 Framer 5 Alarm Start Interrupt Status . . . . . . . . . . . . . . . . . . . . . . . . . . 8-150

0x54AA--DS2/E2 Framer 6 Alarm Start Interrupt Status . . . . . . . . . . . . . . . . . . . . . . . . . . 8-150

0x54CA--DS2/E2 Framer 7 Alarm Start Interrupt Status . . . . . . . . . . . . . . . . . . . . . . . . . . 8-151

0x540B--DS2/E2 Framer 1 Alarm End Interrupt Status . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-151

0x542B--DS2/E2 Framer 2 Alarm End Interrupt Status . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-151

0x544B--DS2/E2 Framer 3 Alarm End Interrupt Status . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-151

0x546B--DS2/E2 Framer 4 Alarm End Interrupt Status . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-151

0x548B--DS2/E2 Framer 5 Alarm End Interrupt Status . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-151

0x54AB--DS2/E2 Framer 6 Alarm End Interrupt Status . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-151

0x54CB--DS2/E2 Framer 7 Alarm End Interrupt Status . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-152

0x540C--DS2/E2 Framer 1 Receive Frame Error Counter . . . . . . . . . . . . . . . . . . . . . . . . . 8-152

0x542C--DS2/E2 Framer 2 Receive Frame Error Counter . . . . . . . . . . . . . . . . . . . . . . . . . 8-152

0x544C--DS2/E2 Framer 3 Receive Frame Error Counter . . . . . . . . . . . . . . . . . . . . . . . . . 8-152

Contents

CX29503 Data Sheet

x

Mindspeed TechnologiesTM

500238B

Advance Information

l

0x546C--DS2/E2 Framer 4 Receive Frame Error Counter . . . . . . . . . . . . . . . . . . . . . . . . . 8-152

0x548C--DS2/E2 Framer 5 Receive Frame Error Counter . . . . . . . . . . . . . . . . . . . . . . . . . 8-152

0x54AC--DS2/E2 Framer 6 Receive Frame Error Counter . . . . . . . . . . . . . . . . . . . . . . . . . 8-152

0x54CC--DS2/E2 Framer 7 Receive Frame Error Counter . . . . . . . . . . . . . . . . . . . . . . . . . 8-153

0x540D--DS2/E2 Framer 1 Receive M-Bit Error Counter . . . . . . . . . . . . . . . . . . . . . . . . . . 8-153

0x542D--DS2/E2 Framer 2 Receive M-Bit Error Counter . . . . . . . . . . . . . . . . . . . . . . . . . . 8-153

0x544D--DS2/E2 Framer 3 Receive M-Bit Error Counter . . . . . . . . . . . . . . . . . . . . . . . . . . 8-153

0x546D--DS2/E2 Framer 4 Receive M-Bit Error Counter . . . . . . . . . . . . . . . . . . . . . . . . . . 8-153

0x548D--DS2/E2 Framer 5 Receive M-Bit Error Counter . . . . . . . . . . . . . . . . . . . . . . . . . . 8-153

0x54AD--DS2/E2 Framer 6 Receive M-Bit Error Counter . . . . . . . . . . . . . . . . . . . . . . . . . . 8-153

0x54CD--DS2/E2 Framer 7 Receive M-Bit Error Counter . . . . . . . . . . . . . . . . . . . . . . . . . . 8-154

0x540E--DS2/E2 Framer 1≠7 Receive LOS Counter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-154

0x542E--DS2/E2 Framer 1≠7 Receive LOS Counter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-154

0x544E--DS2/E2 Framer 1≠7 Receive LOS Counter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-154

0x546E--DS2/E2 Framer 1≠7 Receive LOS Counter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-154

0x548E--DS2/E2 Framer 1≠7 Receive LOS Counter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-154

0x54AE--DS2/E2 Framer 1≠7 Receive LOS Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-154

0x54CE--DS2/E2 Framer 1≠7 Receive LOS Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-154

0x540F--DS2/E2 Framer 1 Receive Parity Error Counter (Lower Byte) . . . . . . . . . . . . . . . 8-155

0x542F--DS2/E2 Framer 2 Receive Parity Error Counter (Lower Byte) . . . . . . . . . . . . . . . 8-155

0x544F--DS2/E2 Framer 3 Receive Parity Error Counter (Lower Byte) . . . . . . . . . . . . . . . 8-155

0x546F--DS2/E2 Framer 4 Receive Parity Error Counter (Lower Byte) . . . . . . . . . . . . . . . 8-155

0x548F--DS2/E2 Framer 5 Receive Parity Error Counter (Lower Byte) . . . . . . . . . . . . . . . 8-155

0x54AF--DS2/E2 Framer 6 Receive Parity Error Counter (Lower Byte) . . . . . . . . . . . . . . . 8-155

0x54CF--DS2/E2 Framer 7 Receive Parity Error Counter (Lower Byte) . . . . . . . . . . . . . . . 8-155

0x5410--DS2/E2 Framer 1 Receive Parity Error Counter (Upper Byte) . . . . . . . . . . . . . . . 8-155

0x5430--DS2/E2 Framer 2 Receive Parity Error Counter (Upper Byte) . . . . . . . . . . . . . . . 8-155

0x5450--DS2/E2 Framer 3 Receive Parity Error Counter (Upper Byte) . . . . . . . . . . . . . . . 8-155

0x5470--DS2/E2 Framer 4 Receive Parity Error Counter (Upper Byte) . . . . . . . . . . . . . . . 8-155

0x5490--DS2/E2 Framer 5 Receive Parity Error Counter (Upper Byte) . . . . . . . . . . . . . . . 8-155

0x54B0--DS2/E2 Framer 6 Receive Parity Error Counter (Upper Byte) . . . . . . . . . . . . . . . 8-155

0x54D0--DS2/E2 Framer 7 Receive Parity Error Counter (Upper Byte) . . . . . . . . . . . . . . . 8-156

0x5411--DS2/E2 Framer 1 National Use Bit Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-156

0x5431--DS2/E2 Framer 2 National Use Bit Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-156

0x5451--DS2/E2 Framer 3 National Use Bit Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-156

0x5471--DS2/E2 Framer 4 National Use Bit Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-156

8.4.4

M13/E13 Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-157

0x5500≠ M13/E13 Interrupt Status Register 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-157

0x5501--DS1/E1 MUX Interrupt Status Register 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-158

0x5502--DS1/E1 MUX Interrupt Status Register 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-159

0x5503--DS1/E1 MUX Interrupt Status Register 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-159

8.4.4.1 DS1/E1 MUX Channel 1≠28 Receive Interrupt Enable . . . . . . . . . . . . . . . . . . 8-160

8.4.4.2 DS1/E1 MUX Channel 1≠28 Transmit FIFO Status . . . . . . . . . . . . . . . . . . . . . 8-161

8.4.4.3 DS1/E1 MUX Channel 1≠28 Receive Interrupt Status . . . . . . . . . . . . . . . . . . 8-162

8.5

SONET/SDH Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-163

8.5.1

Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-163

8.5.2

Software Configuration/Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-163

500238B

Mindspeed TechnologiesTM

xi

Advance Information

CX29503 Data Sheet

Contents

8.5.2.1 DS3 and E3 Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-163

8.5.2.2 Unchannelized STS-1/AU-3 or TUG-3 Mode . . . . . . . . . . . . . . . . . . . . . . . . . 8-164

8.5.2.3 DS1 or E1 Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-164

8.5.3

Interrupt Structures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-165

8.5.4

General Control and Status Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-167

8.5.4.1 SONET/SDH Top Level Transmitter Control . . . . . . . . . . . . . . . . . . . . . . . . . . 8-169

0x6000--Transmit SI-Bus Interrupt Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-169

0x6001--Transmit SI-Bus Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-169

0x6004--BIP2 Error Pattern (Used for Diagnostics) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-169

0x6005--Transmit Microprocessor Interface Fast Access Control . . . . . . . . . . . . . . . . . . . 8-170

0x6007--SI-Bus Transmit to Receive Loopback Control . . . . . . . . . . . . . . . . . . . . . . . . . . 8-170

8.5.4.2 SONET/SDH Level 3 Transmitter Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . 8-171

0x6008--Transmit Channel Interrupt Enable (Channels 1≠8) . . . . . . . . . . . . . . . . . . . . . . . 8-171

0x6009--Transmit Channel Interrupt Enable (Channels 9≠16) . . . . . . . . . . . . . . . . . . . . . . 8-171

0x600A--Transmit Channel Interrupt Enable (Channels 17≠24) . . . . . . . . . . . . . . . . . . . . . 8-172

0x600B--Transmit Channel Interrupt Enable (Channels 17≠24, STS, General). . . . . . . . . . 8-172

0x600C--Transmit Channel Status (Channels 1≠8) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-173

0x600D--Transmit Channel Status (Channels 9≠16) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-173

0x600E--Transmit Channel Status (Channels 17≠24) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-174

0x600F--Transmit Channel Status (Channels 17≠24, STS, General) . . . . . . . . . . . . . . . . . 8-174

8.5.4.3 SONET/SDH Top Level Receiver Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-175

0x6080--Receive SI-Bus Interrupt Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-175

0x6081--Receive SI-Bus Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-175

0x6082--SI-Bus Phase Identifier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-175

0x6084--Receive Status/Counter Latching Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-176

0x6085--Receive Microprocessor Interface Fast Access Control. . . . . . . . . . . . . . . . . . . . 8-176

8.5.4.4 SONET/SDH Level 3 Receiver Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-177

0x6088--Receive Channel Interrupt Enable (Channels 1≠8). . . . . . . . . . . . . . . . . . . . . . . . 8-177

0x6089--Receive Channel Interrupt Enable (Channels 9≠16). . . . . . . . . . . . . . . . . . . . . . . 8-177

0x608A--Receive Channel Interrupt Enable (Channels 17≠24) . . . . . . . . . . . . . . . . . . . . . 8-178

0x608B--Receive Channel Interrupt Enable (Channels 25≠28, STS, General) . . . . . . . . . . 8-178

0x608C--Receive Channel Status (Channels 1≠8) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-179

0x608D--Receive Channel Status (Channels 9≠16) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-179

0x608E--Receive Channel Status (Channels 17≠24) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-180

0x608F--Receive Channel Status (Channels 25≠28, STS, General) . . . . . . . . . . . . . . . . . . 8-180

8.5.5

STS-1 Framer Section/Line Control/Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-181

0x6100--Transmit Transport Overhead Byte Insertion Control (TXTOHINS) . . . . . . . . . . . 8-181

0x6180--Receive Transport Overhead Byte Drop Control (RXTOHDROP) . . . . . . . . . . . . . 8-181

8.5.6

STS-1/AU≠4/AU-3 and TU-3 Path Control/Status Registers . . . . . . . . . . . . . . . . . . . . . . . . 8-182

8.5.6.1 Transmit STS-1/AU≠4/AU-3 Overhead. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-186

0x6200--Transmit Path Overhead Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-186

Contents

CX29503 Data Sheet

xii

Mindspeed TechnologiesTM

500238B

Advance Information

l

0x6202--Transmit Path Overhead Byte Insertion Control (TXPOHINS) . . . . . . . . . . . . . . . 8-186

0x6207--Transmit Path F2 Overhead Byte (TXF2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-186

0x6209--Transmit Path Z3/F3 Overhead Byte (TXF3). . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-187

0x620A--Transmit Path Z4/K3 Overhead Byte (TXK3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-187

0x620B--Transmit Path Z5/N1 Overhead Byte (TXN1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-187

8.5.6.2 Transmit DS3/E3 Mapping FIFO. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-188

0x620E--Transmit DS3/E3 Mapping FIFO Minimum Level (TXL3MAPMIN) . . . . . . . . . . . . 8-188

0x620F--Transmit DS3/E3 Mapping FIFO Reset (TXL3MAPRST). . . . . . . . . . . . . . . . . . . . 8-188

0x6237--Transmit DS3/E3 Mapping FIFO Interrupt Enable . . . . . . . . . . . . . . . . . . . . . . . . 8-188

0x623F--Transmit DS3/E3 Mapping FIFO Status, Diagnostic Only . . . . . . . . . . . . . . . . . . . 8-188

8.5.6.3 Transmit TU-3 Overhead . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-189

0x6240--Transmit TU-3 Overhead Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-189

0x6242--Transmit TU-3 Overhead Byte Insertion Control (TXTU3INS) . . . . . . . . . . . . . . . 8-189

0x6247--Transmit TU-3 F2 Overhead Byte (TXTRF2). . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-189

0x6249--Transmit TU-3 Z3/F3 Overhead Byte (TXTRF3) . . . . . . . . . . . . . . . . . . . . . . . . . . 8-190

0x624A--Transmit TU-3 Z4/K3 Overhead Byte (TXTRK3). . . . . . . . . . . . . . . . . . . . . . . . . . 8-190

0x624B--Transmit TU-3 Z5/N1 Overhead Byte (TXTRN1) . . . . . . . . . . . . . . . . . . . . . . . . . 8-190

8.5.6.4 Receive STS-1/AU-4/AU-3 Overhead . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-191

0x6282--Receive Path Overhead Byte Drop Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-191

8.5.6.5 Receive DS3/E3 Demapping FIFO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-191

0x628E--Receive DS3/E3 Demapping FIFO Minimum Level (RXL3DEMMIN) . . . . . . . . . . 8-191

0x628F--Receive DS3/E3 Demap FIFO Reset (RXL3DEMRST) . . . . . . . . . . . . . . . . . . . . . 8-191

8.5.6.6 STS-1/AU-4/AU-3 Pointer Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-192

0x6294--Receive STS-1/AU-4/AU-3 Pointer Value (8 LSBits) . . . . . . . . . . . . . . . . . . . . . . 8-192

0x6295--Receive STS-1/AU-4/AU-3 Pointer Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-192

0x6296--Receive STS-1/AU-4/AU-3 Pointer Increment Counter LSB . . . . . . . . . . . . . . . . 8-192

0x6297--Receive STS-1/AU-4/AU-3 Pointer Increment Counter MSB . . . . . . . . . . . . . . . . 8-193

0x6298--Receive STS-1/AU-4/AU-3 Pointer Decrement Counter LSB . . . . . . . . . . . . . . . . 8-193

0x6299--Receive STS-1/AU-4/AU-3 Pointer Decrement Counter MSB . . . . . . . . . . . . . . . 8-193

8.5.6.7 STS Path Level 2 Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-194

0x62B0--Receive STS Path Interrupt Source . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-194

8.5.6.8 STS Path Level 1 Interrupts--STS-1/AU≠4/AU-3 . . . . . . . . . . . . . . . . . . . . . 8-195

0x62B3--Receive Path Start of Status Interrupt Enable 1 . . . . . . . . . . . . . . . . . . . . . . . . . 8-195

0x62B4--Receive Path Start of Status Interrupt Enable 2 . . . . . . . . . . . . . . . . . . . . . . . . . 8-195

0x62B5--Receive Path End of Status Interrupt Enable 1 . . . . . . . . . . . . . . . . . . . . . . . . . . 8-195

0x62B6--Receive Path End of Status Interrupt Enable 2 . . . . . . . . . . . . . . . . . . . . . . . . . . 8-195

0x62B7--Receive Path Event Status Interrupt Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-196

0x62B9--Receive Path Current Status 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-196

0x62BA--Receive Path Current Status 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-196

0x62BB--Receive Path Start of Status 1 (RXPSSTAT1) . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-196

0x62BC--Receive Path Start of Status 2 (RXPSSTAT2) . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-197

0x62BD--Receive Path End of Status 1 (RXPESTAT1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-197

0x62BE--Receive Path End of Status 2 (RXPESTAT2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-197

0x62BF--Receive Path Event Status (RXPEVSTAT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-197

8.5.6.9 Receive TU-3 Overhead . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-198

0x62C2--Receive TU-3 Overhead Byte Drop Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-198

8.5.6.10 Receive TU-3 Pointer Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-199

500238B

Mindspeed TechnologiesTM

xiii

Advance Information

CX29503 Data Sheet

Contents

0x62D4--Receive TU-3 Pointer Value (8 LSBits) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-199

0x62D5--Receive TU-3 Pointer Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-199

0x62D6--Receive TU-3 Pointer Increment Counter LSB . . . . . . . . . . . . . . . . . . . . . . . . . . 8-199

0x62D7--Receive TU-3 Pointer Increment Counter MSB . . . . . . . . . . . . . . . . . . . . . . . . . . 8-200

0x62D8--Receive TU-3 Pointer Decrement Counter LSB . . . . . . . . . . . . . . . . . . . . . . . . . . 8-200

0x62D9--Receive TU-3 Pointer Decrement Counter MSB . . . . . . . . . . . . . . . . . . . . . . . . . 8-200

8.5.6.11 STS Path Level 1 Interrupts--TU-3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-201

0x62F3--Receive TU-3 Start of Status Interrupt Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-201

0x62F5--Receive TU-3 End of Status Interrupt Enable. . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-201

0x62F7--Receive TU-3 Event Status Interrupt Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-201

0x62F9--Receive TU-3 Current Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-201

0x62FB--Receive TU-3 Start of Status (RXTSSTAT). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-202

0x62FD--Receive TU-3 End of Status (RXTESTAT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-202

0x62FF--Receive TU-3 Event Status (RXTEVSTAT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-202

8.5.7

Mapping Control/Status Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-203

0x6380--Level 3 Mapping Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-203

0x6388, 0x6389, 0x638A, 0x638B, 0x638C, 0x638D, and 0x638E--Group n Mapping Control 8-

205

8.6

VT/VC Mapper Control and Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-206

8.6.1

Transmit Tributary Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-208

0x00--VT#n Transmit Overhead Control 1 (TXVTCTL1) . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-208

0x01--VT#n Transmit Overhead Control 2 (TXVTCTL2) . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-209

0x02--VT#n Transmit Signal Label Control (TXVTLAB) . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-209

0x03--VT#n Transmit J2 Trace Circular Buffer Address (TXJ2ADD) . . . . . . . . . . . . . . . . . 8-209

0x04--VT#n Transmit J2 Trace Circular Buffer Data (TXJ2DAT) . . . . . . . . . . . . . . . . . . . . . 8-209

0x05--VT#n Transmit Z6/N2 Overhead Byte (TXN2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-210

0x06--VT#n Transmit Z7/K4 Overhead Byte (TXK4). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-210

0x0E--VT#n Transmit Mapping FIFO Minimum Level (TXL1MAPMIN). . . . . . . . . . . . . . . . 8-210

0x0F--VT#n Transmit Mapping FIFO Reset (TXL1MAPRST) . . . . . . . . . . . . . . . . . . . . . . . 8-210

0x37--VT#n Transmit Mapping FIFO Interrupt Enable (TXL1MAPINTEN) . . . . . . . . . . . . . 8-211

0x3F--VT#n Transmit Mapping FIFO Status (TXL1MAPINTEN), Diagnostic Only . . . . . . . . 8-211

8.6.2

Receive Tributary Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-212

0x80--VT#n Receive Control (RXVTCTL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-212

0x82--VT#n Receive Signal Label Status (RXVTLAB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-212

0x83--VT#n Receive J2 Trace Circular Buffer Address (RXJ2ADD. . . . . . . . . . . . . . . . . . . 8-212

0x84--VT#n Receive J2 Trace Circular Buffer Data (RXJ2DAT) . . . . . . . . . . . . . . . . . . . . . 8-212

0x85--VT#n Receive Z6/N2 Overhead Status (RXN2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-213