| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: M62356P | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

( / 6 )

ELECTRIC

MITSUBISHI

M62356P

MITSUBISHI<Dig.Ana.INTERFACE>

8-BIT 8CH D-A CONVERTER

10

9

DESCRIPTION

The M62356P is an integrated circuit semiconductor of C-MOS

structure with 8 channels of built-in D-A converters.

The input data is a easy-to-use 3-wires serial data transfer

method and it is able to cascading serial use with Do terminal.

FEATURES

∑Digital data transfer format

3-wires serial data transfer method

∑Output voltage range 0V to 12V

∑Short setting time

∑D-A converter high level reference voltage is possess two input

terminal then two reference voltage is possible to input.

Digital voltage supply........................V

DD

=5V±10%

BLOCK DIAGRAM

APPLICATION

Conversion from digital control data to analog control data

for home-use and industrial equipment.

Automatic adjustment by combination with EEPROM and

microcomputer(replacement of conventional half-fixed

resistor).

Signal gain control of DISPLAY-MONITOR or CTV.

1

PIN CONFIGURATION (TOP VIEW)

18

15

16

17

1

4

3

2

14

5

13

6

12

7

11

8

Ao3

Ao4

Ao5

Ao6

V

DD

GND

Ao1

DI

CLK

LD

DO

Ao2

Outline 18P4

7

16

6

5

4

3

2

1

13

14

15

12

Ao3

Ao4

Ao5

Ao6

V

DD

R

Ao2

Ao1

DI

CLK

LD

Do

17

18

Ao7

Ao8

VrefL

VrefU2

VrefU1

R

11

8

GND

10

9

Ao7

Ao8

VrefL

VrefU1

VrefU2

8-BIT

LATCH

D-A

CONVERTER

8-BIT

LATCH

D-A

CONVERTER

8-BIT

LATCH

D-A

CONVERTER

8-BIT

LATCH

D-A

CONVERTER

8-BIT

LATCH

D-A

CONVERTER

8-BIT

LATCH

D-A

CONVERTER

8-BIT

LATCH

D-A

CONVERTER

8-BIT

LATCH

D-A

CONVERTER

( / 6 )

ELECTRIC

MITSUBISHI

M62356P

MITSUBISHI<Dig.Ana.INTERFACE>

8-BIT 8CH D-A CONVERTER

2

EXPLANATION OF TERMINALS

Pin No.

Symbol

Function

3

16

2

1

17

11

8

10

9

18

12

13

14

15

DI

DO

CLK

LD

Ao1

Ao2

Ao3

Ao4

Ao5

Ao6

VrefU1

GND

V

DD

Serial data input terminal

Serial data output terminal

Serial clock input terminal

LD terminal input high level than latch circuit data load

Reset terminal

Digital power supply terminal

D-A converter upper reference voltage input terminal(CH1~CH4)

D-A converter lower reference voltage input terminal

V

ABSOLUTE MAXIMUM RATINGS(Ta=25∞C, unless otherwise noted)

Symbol

Ratings

Unit

Supply voltage

-0.3~7.0

V

IN

Input voltage

Parameter

Conditions

V

DD

-0.3~Vcc+0.3

I

AO

T

opr

D-A converter output current

Operating temperature

T

stg

Storage temperature

D-A converter upper reference voltage

Output current

-5~+5

µA

V

V

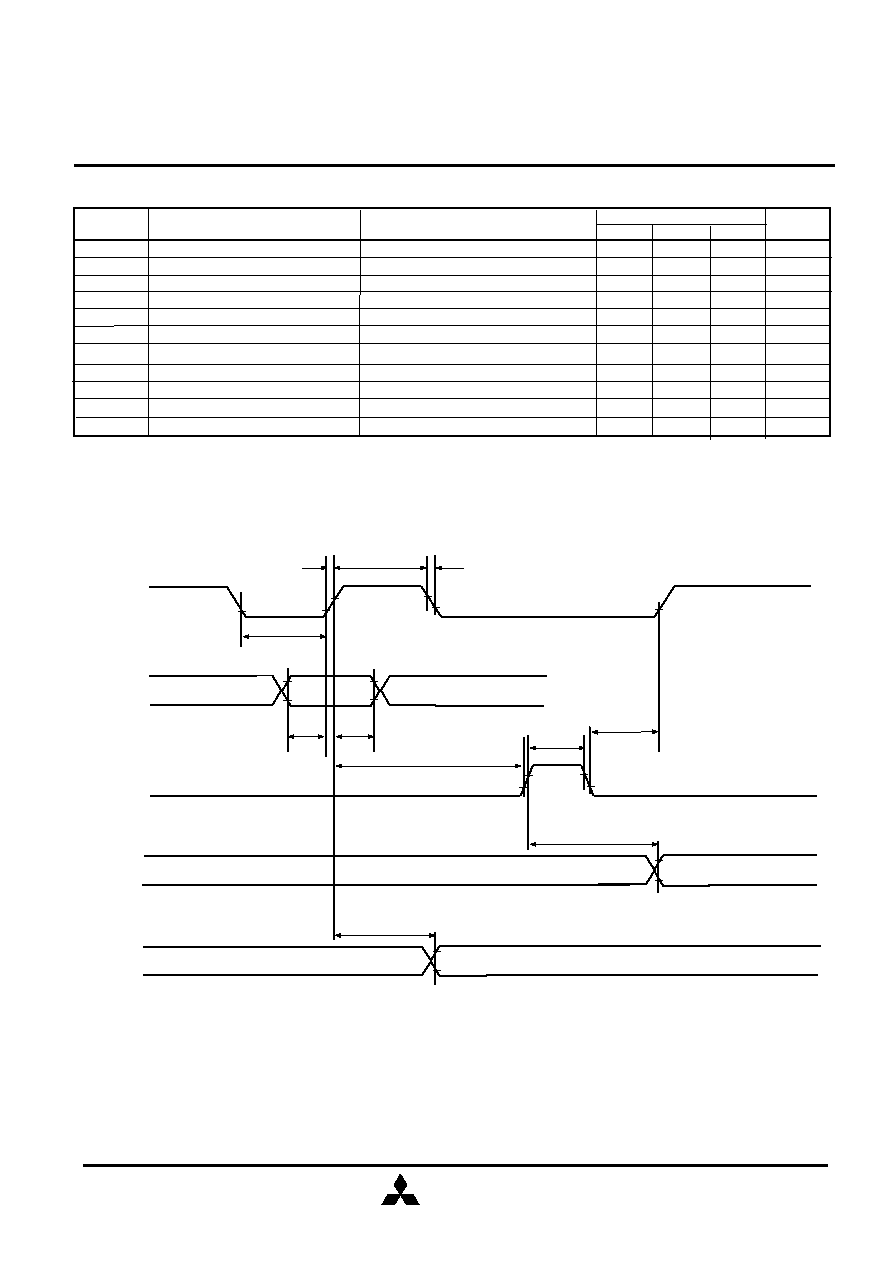

ELECTRICAL CHARACTERISTICS

Digital part(Ta=25∞C,V

DD

=5V, unless otherwise noted)

Symbol

Test conditions

Limits

Unit

Parameter

Min.

Typ.

Max.

V

4.5

Supply voltage

5.5

0.4

Output low voltage

V

DD

-0.4

0.8V

DD

0.2V

DD

1

V

I

DD

Circuit current

∞C

∞C

12.5

10

-20~+75

-40~+125

V

IL

V

IH

V

OL

V

OH

mA

V

V

V

Input low voltage

Input high voltage

Output high voltage

CLK=1MHz operation

I

OL

=1.0mA

I

OH

=-400µA

4

5

6

7

8-bit D-A converter output terminal

VrefU2

VrefL

R

Ao7

Ao8

GND

D-A converter upper reference voltage input terminal(CH5~CH8)

RECOMMENDED OPERATING CONDITIONS

∑Digital voltage supply V

DD

5V±10%

mA

VrefU

I

DO

V

DD

( / 6 )

ELECTRIC

MITSUBISHI

M62356P

MITSUBISHI<Dig.Ana.INTERFACE>

8-BIT 8CH D-A CONVERTER

3

TIMING CHART (MODEL)

LD

AO

CLK

DI

D11

D10

D9

D0

LSB

MSB

Symbol

Test conditions

Limits

Unit

Parameter

Min.

Typ.

Max.

1.2

V

2.5

IrefU

3.5

12

1.5

V

refU

D-A converter upper reference

voltage range

V

refL

V

AO

mA

V

Analog part(V

DD

=+5V,VrefU=12V,VrefL=0V,Ta=-20∞C~+85∞C, unless otherwise noted)

D-A converter lower reference

voltage range

D-A converter output

voltage range

V

All ch`s set up at 107/256

DNL

NL

D-A converter upper reference

input current max

Differential nonlinearity

Nonrineality

Guaranteed monotonic

±1.0

±1.5

VrefL

VrefU

+2.5LSB

-1.5LSB

LSB

LSB

R

Input data is carried out LD signal Low besides CLK signal positive edge.

CLK,LD is keep generally High level.

( / 6 )

ELECTRIC

MITSUBISHI

M62356P

MITSUBISHI<Dig.Ana.INTERFACE>

8-BIT 8CH D-A CONVERTER

4

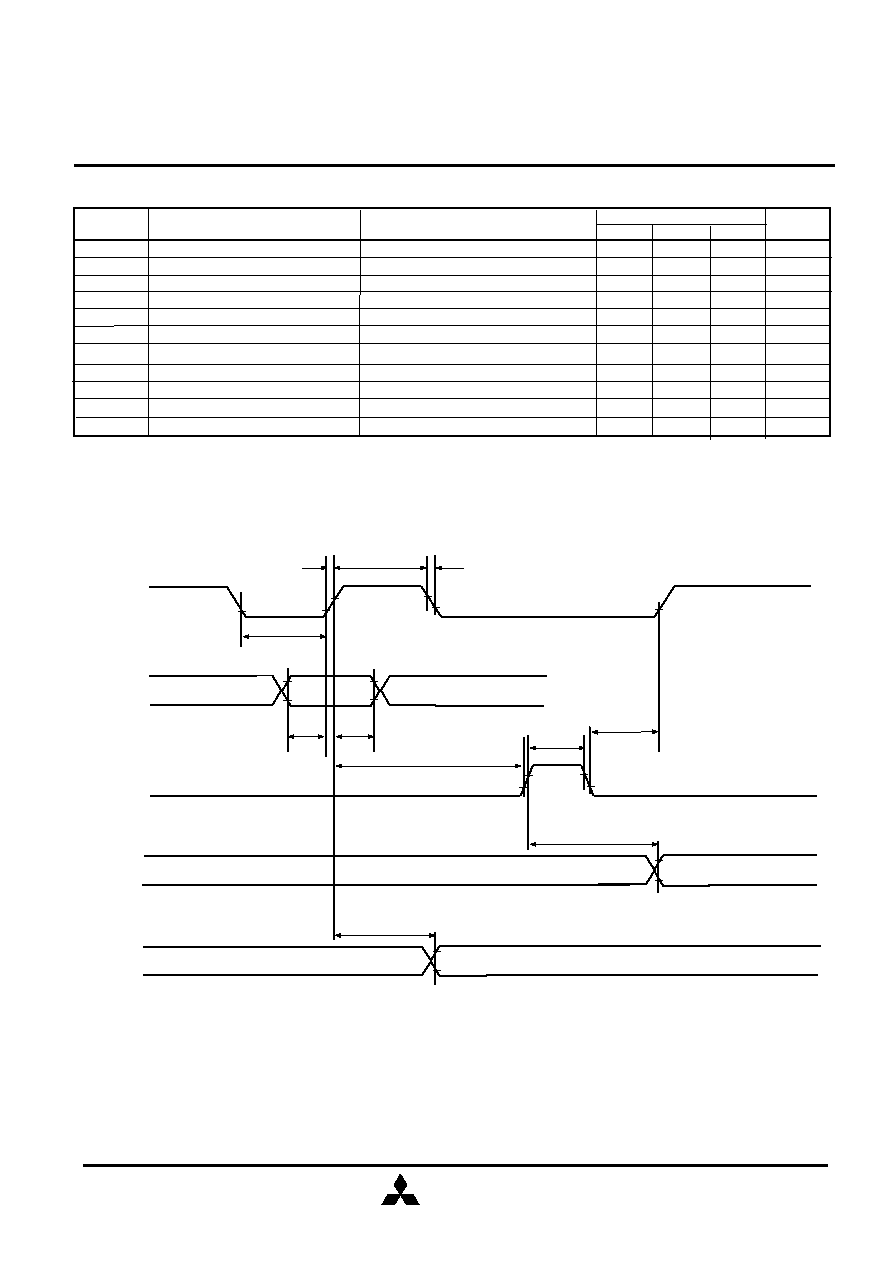

TIMING CHART

t

DCH

t

CHD

t

CKL

t

CKH

t

CR

t

CF

t

LDC

t

LDH

t

CHL

t

LDD

t

DO

CLK

DI

LD

D-A

OUTPUT

DO

OUTPUT

ns

AC CHARACTERISTICS(Ta=25∞C,V

DD

=+5V,VrefU=12V,VrefL=0V, unless otherwise noted)

Symbol

Unit

Clock "L"pulse width

t

CR

Clock rise time

t

CKL

Parameter

Test conditions

t

CKH

t

CF

t

DCH

t

CHD

t

CHL

Limits

Min

Typ

Max

t

LDC

t

LDH

t

DO

LD "H" pulse width

Data output delay time

t

LDD

Data output setting time

ns

ns

ns

ns

ns

ns

ns

ns

ns

200

200

200

200

60

100

200

100

100

70

350

Clock "H"pulse width

Clock fall time

Data set up time

Data hold time

LD set up time

LD hold time

C

L

100pF

Without load

20

µs

( / 6 )

ELECTRIC

MITSUBISHI

M62356P

MITSUBISHI<Dig.Ana.INTERFACE>

8-BIT 8CH D-A CONVERTER

5

DIGITAL FORMAT

1.12-bit shift register

D0

D1

D2

D3

D4

D5

D6

D7

Output voltage

0

1

0

1

0

1

0

0

1

1

1

1

0

0

0

0

1

1

0

0

0

0

1

1

0

0

0

0

1

1

0

0

0

0

1

1

0

0

0

0

1

1

0

0

0

0

1

1

1/256∑(VrefU-VrefL)+VrefL

2/256∑(VrefU-VrefL)+VrefL

To set DAC,12-bit data is input in series at CLK signal"positive"

edges while the LD pin status is "Low".

DATA

(LSB)

∑12 bit serial data

CK

∑Data assignment

∑DAC set up data

DAC select data

DAC set up data

(MSB)

(LSB)

D8

D9

D10

D11

DAC selection

0

0

0

0

0

0

1

1

2.Decoder(DAC select data)

One DAC circuit is selected from among 8 circuits according

to the DAC select data(4-bits:D8,D9,D11 and D14).

∑DAC select data

0

1

1

0

0

0

0

1

1

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Don`t care

Ao1 selection

Ao2 selection

Ao3 selection

Ao4 selection

Ao5 selection

Ao6 selection

Ao7 selection

Ao8 selection

Don`t care

Don`t care

Don`t care

Don`t care

Don`t care

Don`t care

Don`t care

Ao=

2 X D0 + 2 X D1 + 2 X D2 +∑∑∑∑∑∑∑∑+ 2 X D6 + 2 X D7 + 1

∑ (VrefU - VrefL) + VrefL

0

1

2

6

7

256

(LSB)

(MSB)

3/256∑(VrefU-VrefL)+VrefL

4/256∑(VrefU-VrefL)+VrefL

255/256∑(VrefU-VrefL)+VrefL

256/256∑(VrefU-VrefL)+VrefL