| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: ADC1251 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

TL H 11024

ADC1251

Self-Calibrating

12-Bit

Plus

Sign

AD

Converter

with

Sample-and-Hold

December 1994

ADC1251 Self-Calibrating 12-Bit Plus Sign

A D Converter with Sample-and-Hold

General Description

The ADC1251 is a CMOS 12-bit plus sign successive ap-

proximation analog-to-digital converter

On request

the

ADC1251 goes through a self-calibration cycle that adjusts

for any zero full scale or linearity errors The ADC1251 also

has the ability to go through an Auto-Zero cycle that cor-

rects the zero error during every conversion

The analog input to the ADC1251 is tracked and held by the

internal circuitry so an external sample-and-hold is not re-

quired The ADC1251 has an S H control input which direct-

ly controls the track-and-hold state of the A D A unipolar

analog input voltage range (0 to

a

5V) or a bipolar range

(

b

5V to

a

5V) can be accommodated with

g

5V supplies

The 13-bit data result is available on the eight outputs of the

ADC1251 in two bytes high-byte first and sign extended

The digital inputs and outputs are compatible with TTL or

CMOS logic levels

Features

Y

Self-calibration provides excellent temperature stability

Y

Internal sample-and-hold

Y

8-bit mP DSP interface

Y

Bipolar input range with a single

a

5V reference

Y

No missing codes over temperature

Y

TTL MOS input output compatible

Key Specifications

Y

Resolution

12 bits plus sign

Y

Conversion Time

8 ms (max)

Y

Sampling Rate

83 kHz (max)

Y

Linearity Error

g

0 6 LSB (

g

0 0146%) (max)

Y

Zero Error

g

1 LSB (max)

Y

Full Scale Error

g

1 5 LSB (max)

Y

Power Consumption

g

5V

113 mW (max)

Applications

Y

Digital signal processing

Y

High resolution process control

Y

Instrumentation

Simplified Block Diagram

TL H 11024 ≠ 1

Connection Diagram

Dual-In-Line Package

TL H 11024 ≠ 2

Top View

Ordering Information

Industrial

Package

(

b

40 C

s

T

A

s

a

85 C)

ADC1251BIJ

J24A

ADC1251CIJ

Military

Package

(

b

55 C

s

T

A

s

a

125 C)

ADC1251CMJ

J24A

ADC1251CMJ 883

TRI-STATE

is a registered trademark of National Semiconductor Corporation

C1995 National Semiconductor Corporation

RRD-B30M115 Printed in U S A

Absolute Maximum Ratings

(Notes 1

2)

If Military Aerospace specified devices are required

please contact the National Semiconductor Sales

Office Distributors for availability and specifications

Supply Voltage (V

CC

e

DV

CC

e

AV

CC

)

6 5V

Negative Supply Voltage (V

b

)

b

6 5V

Voltage at Logic Control Inputs

b

0 3V to (V

CC

a

0 3V)

Voltage at Analog Inputs

(V

REF

V

IN

)

(V

b

b

0 3V) to (V

CC

a

0 3V)

AV

CC

-DV

CC

(Note 7)

0 3V

Input Current at Any Pin (Note 3)

g

5 mA

Package Input Current (Note 3)

g

20 mA

Power Dissipation at 25 C (Note 4)

875 mW

Storage Temperature Range

b

65 C to

a

150 C

ESD Susceptability (Note 5)

2000V

Soldering Information

J Package (10 sec )

300 C

Operating Ratings

(Notes 1

2)

Temperature Range

T

MIN

s

T

A

s

T

MAX

ADC1251BIJ ADC1251CIJ

b

40 C

s

T

A

s

a

85 C

ADC1251CMJ

b

55 C

s

T

A

s

a

125 C

ADC1251CMJ 883

b

55 C

s

T

A

s

a

125 C

DV

CC

and AV

CC

Voltage

(Notes 6

7)

4 5V to 5 5V

Negative Supply Voltage (V

b

)

b

4 5V to

b

5 5V

Reference Voltage

(V

REF

Notes 6

7)

3 5V to AV

CC

a

50 mV

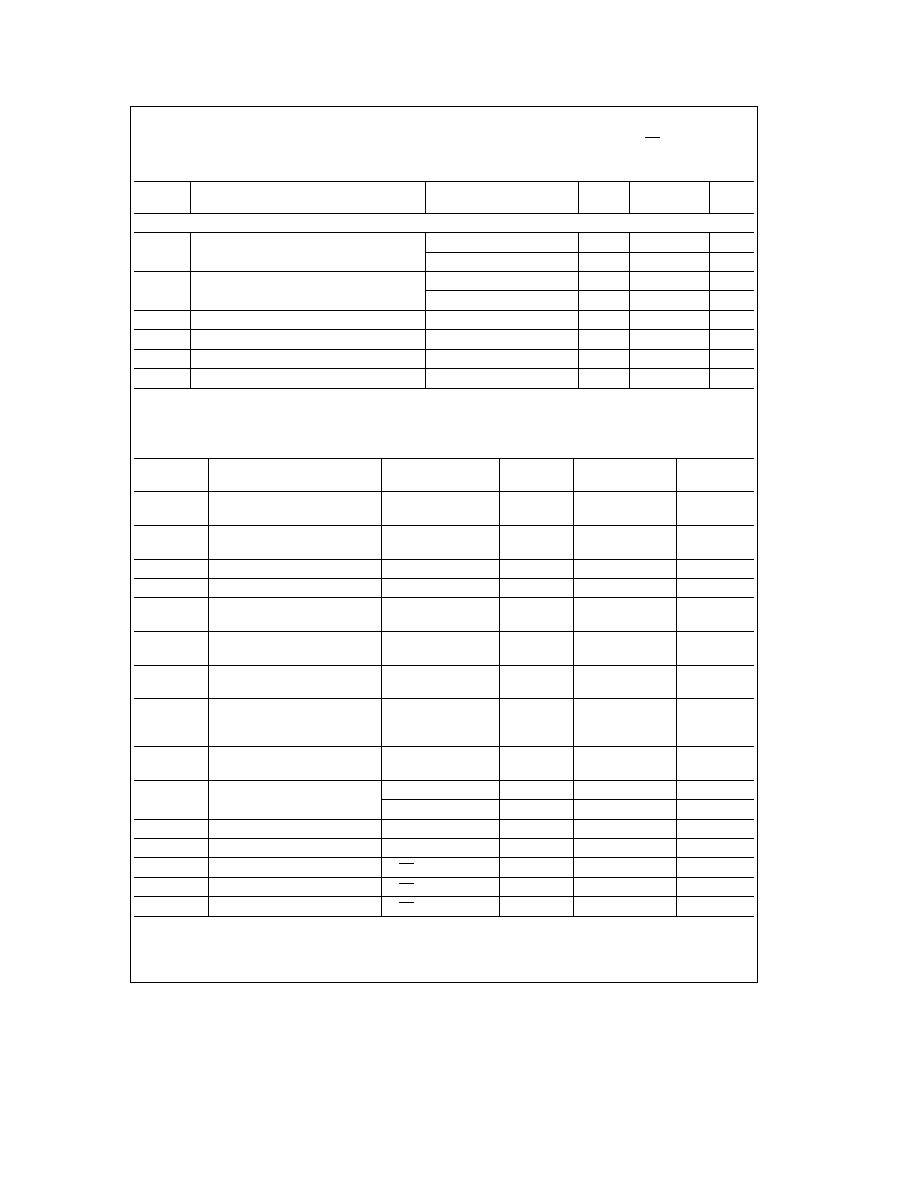

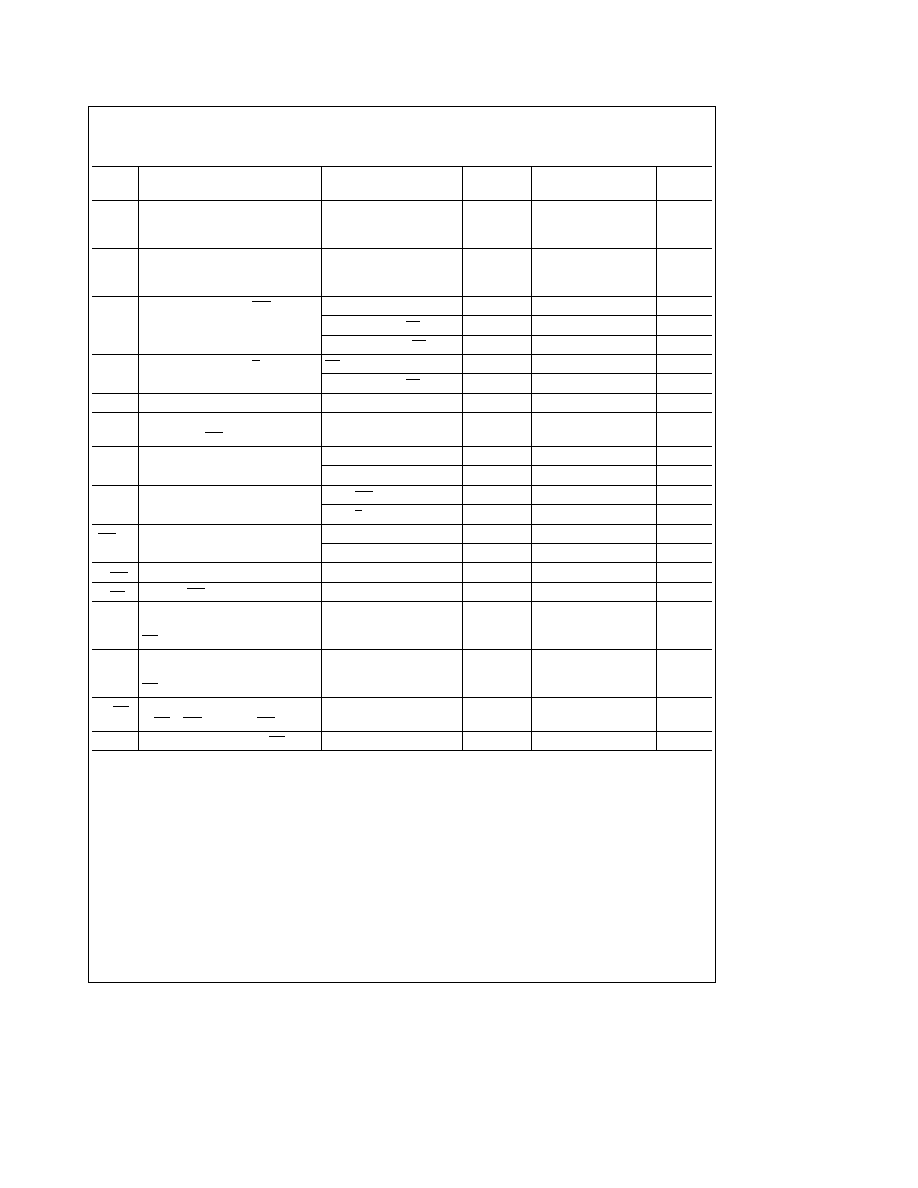

Converter Electrical Characteristics

The following specifications apply for V

CC

e

DV

CC

e

AV

CC

e

a

5 0V V

b

e b

5 0V V

REF

e

a

5 0V AZ

e

``1'' f

CLK

e

3 5 MHz and tested using WR control unless otherwise specified Boldface limits apply for T

A

e

T

J

e

T

MIN

to T

MAX

all other

limits T

A

e

T

J

e

25 C (Notes 6 7 and 8)

Symbol

Parameter

Conditions

Typical

Limit

Units

(Note 9) (Notes 10 19)

(Limit)

STATIC CHARACTERISTICS

Positive Integral

ADC1251BIJ

After Auto-Cal

g

0 6

LSB(max)

Linearity Error

ADC1251CIJ

(Notes 11

12)

g

1

LSB(max)

ADC1251CMJ

g

1

LSB(max)

Negative Integral

ADC1251BIJ

After Auto-Cal

g

0 6

LSB(max)

Linearity Error

ADC1251CIJ

(Notes 11 and 12)

g

1

LSB(max)

ADC1251CMJ

g

1

LSB(max)

Missing Codes

After Auto-Cal (Notes 11 and 12)

0

Zero Error (Notes 12 and 13)

AZ

e

``0'' and f

CLK

e

1 75 MHz

g

2

LSB(max)

After Auto-Cal Only

g

2 0

g

3 0

LSB(max)

Positive Full-Scale Error (Note 12)

AZ

e

``0'' and f

CLK

e

1 75 MHz

g

1 5

LSB(max)

After Auto-Cal Only

g

1 5

g

2 0

LSB(max)

Negative Full-Scale Error (Note 12)

AZ

e

``0'' and f

CLK

e

1 75 MHz

g

1 5

LSB(max)

After Auto-Cal Only

g

1 5

g

2 0

LSB(max)

C

REF

V

REF

Input Capacitance (Note 18)

80

pF

C

IN

Analog Input Capacitance

65

pF

V

IN

Analog Input Voltage

V

b

b

0 05

V(min)

V

CC

a

0 05

V(max)

Power Supply Sensitivity

Zero Error (Note 14) AV

CC

e

DV

CC

e

5V

g

5%

g

LSB

Full-Scale Error

V

REF

e

4 75V V

b

e b

5V

g

5%

g

LSB

Linearity Error

g

LSB

2

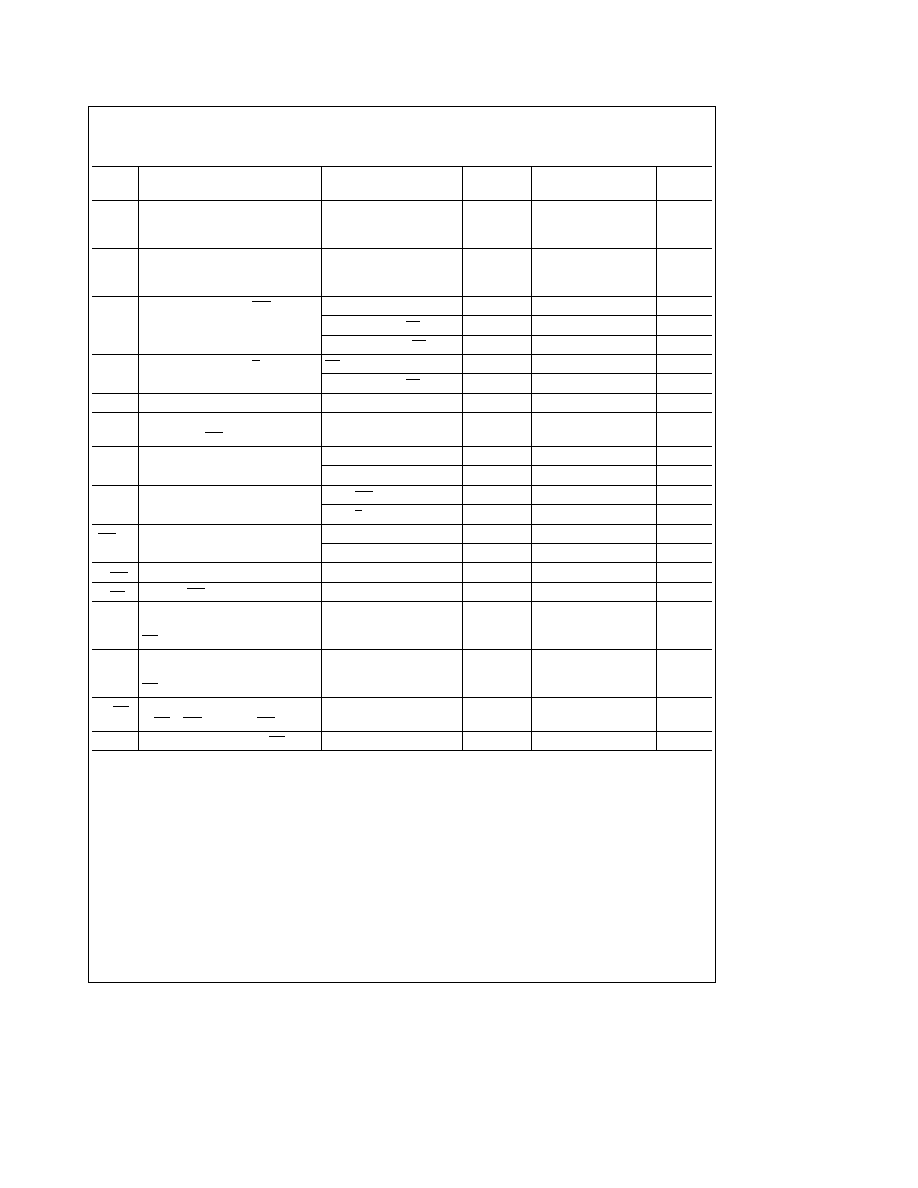

Converter Electrical Characteristics

(Continued)

The following specifications apply for V

CC

e

DV

CC

e

AV

CC

e

a

5 0V V

b

e b

5 0V V

REF

e

a

5 0V AZ

e

``1'' and f

CLK

e

3 5 MHz unless otherwise specified Boldface limits apply for T

A

e

T

J

e

T

MIN

to T

MAX

all other limits T

A

e

T

J

e

25 C

(Notes 6 7 and 8)

Symbol

Parameter

Conditions

Typical

Limit

Units

(Note 9)

(Notes 10 19)

(Limit)

DYNAMIC CHARACTERISTICS

S (N

a

D)

Unipolar Signal-to-Noise

a

Distortion

f

IN

e

1 kHz V

IN

e

4 85 V

p-p

72

dB

Ratio (Note 17)

f

IN

e

20 kHz V

IN

e

4 85 V

p-p

72

dB

S (N

a

D)

Bipolar Signal-to-Noise

a

Distortion

f

IN

e

1 kHz V

IN

e

g

4 85V

76

dB

Ratio (Note 17)

f

IN

e

20 kHz V

IN

e

g

4 85V

76

dB

b

3 dB Unipolar Full Power Bandwidth

V

IN

e

4 85V (Note 17)

32

kHz

b

3 dB Bipolar Full Power Bandwidth

V

IN

e

g

4 85V (Note 17)

25

kHz

t

Ap

Aperture Time

100

ns

Aperture Jitter

100

ps

rms

Digital and DC Electrical Characteristics

The following specifications apply for DV

CC

e

AV

CC

e a

5 0V V

b

e b

5 0V V

REF

e a

5 0V and f

CLK

e

3 5 MHz unless

otherwise specified Boldface limits apply for T

A

e

T

J

e

T

MIN

to T

MAX

all other limits T

A

e

T

J

e

25 C (Notes 6 and 7)

Symbol

Parameter

Conditions

Typical

Limit

Units

(Note 9)

(Notes 10 19)

(Limit)

V

IN(1)

Logical ``1'' Input Voltage for

V

CC

e

5 25V

2 0

V(min)

All Inputs except CLK IN

V

IN(0)

Logical ``0'' Input Voltage for

V

CC

e

4 75V

0 8

V(max)

All Inputs except CLK IN

I

IN(1)

Logical ``1'' Input Current

V

IN

e

5V

0 005

1

m

A(max)

I

IN(0)

Logical ``0'' Input Current

V

IN

e

0V

b

0 005

b

1

m

A(max)

V

T

a

CLK IN Positive-Going

2 8

2 7

V(min)

Threshold Voltage

V

T

b

CLK IN Negative-Going

2 1

2 3

V(max)

Threshold Voltage

V

H

CLK IN Hysteresis

0 7

0 4

V(min)

V

T

a

(min)

b

V

T

b

(max)

V

OUT(1)

Logical ``1'' Output Voltage

V

CC

e

4 75V

I

OUT

e b

360 mA

2 4

V(min)

I

OUT

e b

10 mA

4 5

V(min)

V

OUT(0)

Logical ``0'' Output Voltage

V

CC

e

4 75V

0 4

V(max)

I

OUT

e

1 6 mA

I

OUT

TRI-STATE Output Leakage

V

OUT

e

0V

b

0 01

b

3

m

A(max)

Current

V

OUT

e

5V

0 01

3

m

A(max)

I

SOURCE

Output Source Current

V

OUT

e

0V

b

20

b

6 0

mA(min)

I

SINK

Output Sink Current

V

OUT

e

5V

20

8 0

mA(min)

DI

CC

DV

CC

Supply Current

CS

e

``1''

1

2 5

mA(max)

AI

CC

AV

CC

Supply Current

CS

e

``1''

4

10

mA(max)

I

b

V

b

Supply Current

CS

e

``1''

2 8

10

mA(max)

3

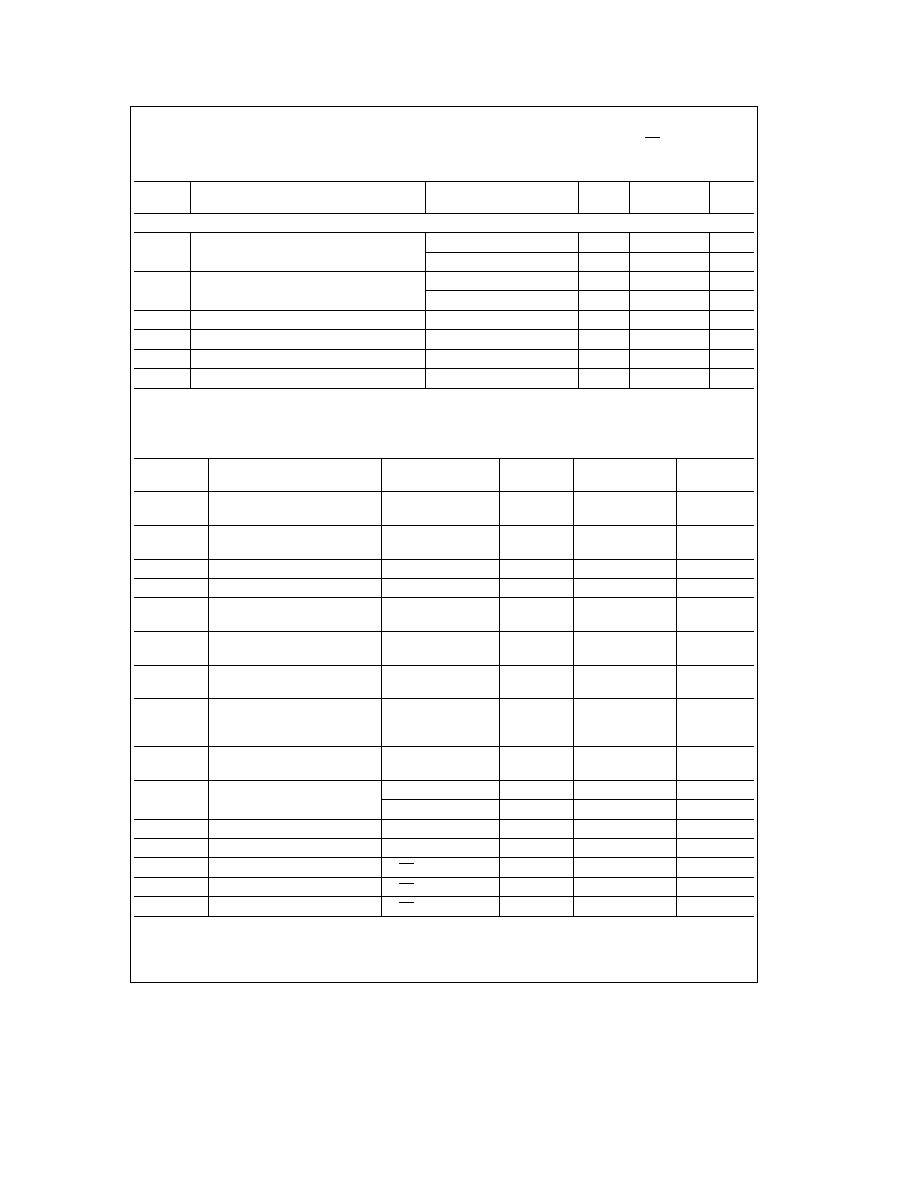

AC Electrical Characteristics

The following specifications apply for DV

CC

e

AV

CC

e

a

5 0V V

b

e

b

5 0V t

r

e

t

f

e

20 ns unless otherwise specified

Boldface limits apply for T

A

e

T

J

e

T

MIN

to T

MAX

all other limits T

A

e

T

J

e

25 C (Notes 6 and 7)

Symbol

Parameter

Conditions

Typical

Limit

Units

(Note 9)

(Notes 10 19)

(Limit)

f

CLK

Clock Frequency

MHz

0 5

MHz(min)

6 0

3 5

MHz(max)

Clock Duty Cycle

50

%

40

%(min)

60

%(max)

t

C

Conversion Time Using WR

27(1 f

CLK

)

27(1 f

CLK

)

a

250 ns

(max)

to Start a Conversion

f

CLK

e

3 5 MHz AZ

e

``1''

7 7

7 95

m

s(max)

f

CLK

e

1 75 MHz AZ

e

``0''

15 4

15 65

m

s(max)

t

C

Conversion Time Using S H

AZ

e

``1''

34(1 f

CLK

)

34(1 f

CLK

)

a

250 ns

(max)

to Start a Conversion

f

CLK

e

3 5 MHz AZ

e

``1''

9 7

9 95

m

s(max)

t

A

Acquisition Time (Note 15)

R

SOURCE

e

50X

3 5

3 5

m

s(min)

t

IA

Internal Acquisition Time

7(1 f

CLK

)

7(1 f

CLK

)

(max)

(When Using WR Control Only)

t

ZA

Auto Zero Time

a

Acquisition Time

33(1 f

CLK

)

33(1 f

CLK

)

a

250 ns

(max)

f

CLK

e

1 75 MHz

18 8

19 05

m

s(max)

t

D(EOC)L

Delay from Hold Command

Using WR Control

200

350

ns(max)

to Falling Edge of EOC

Using S H Control

100

150

ns(max)

t

CAL

Calibration Time

1399(1 f

CLK

)

1399 (1 f

CLK

)

(max)

f

CLK

e

3 5 MHz

399

400

m

s(max)

t

W(CAL)L

Calibration Pulse Width

(Note 16)

60

200

ns(min)

t

W(WR)L

Minimum WR Pulse Width

60

200

ns(min)

t

ACC

Maximum Access Time

C

L

e

100 pF

(Delay from Falling Edge of

50

95

ns(max)

RD to Output Data Valid)

t

0H

t

1H

TRI-STATE Control

R

L

e

1 kX C

L

e

100 pF

(Delay from Rising Edge of

30

70

ns(max)

RD to Hi-Z State)

t

PD(INT)

Maximum Delay from Falling Edge

100

175

ns(max)

of RD or WR to Reset of INT

t

RR

Delay between Successive RD Pulses

30

60

ns(min)

Note 1

Absolute Maximum Ratings indicate limits beyond which damage to the device may occur Operating Ratings indicate conditions for which the device is

functional but do not guarantee specific performance limits For guaranteed specifications and test conditions see the Electrical Characteristics The guaranteed

specifications apply only for the test conditions listed Some performance characteristics may degrade when the device is not operated under the listed test

conditions

Note 2

All voltages are measured with respect to AGND and DGND unless otherwise specified

Note 3

When the input voltage (V

IN

) at any pin exceeds the power supply rails (V

IN

k

V

b

or V

IN

l

(AV

CC

or DV

CC

) the current at that pin should be limited to

5 mA The 20 mA maximum package input current rating allows the voltage at any four pins with an input current limit of 5 mA to simultaneously exceed the power

supply voltages

Note 4

The power dissipation of this device under normal operation should never exceed 191 mW (Quiescent Power Dissipation

a

1 TTL Load on each digital

output) Caution should be taken not to exceed absolute maximum power rating when the device is operating in severe fault condition (ex when any inputs or

outputs exceed the power supply) The maximum power dissipation must be derated at elevated temperatures and is dictated by T

Jmax

(maximum junction

temperature) i

JA

(package junction to ambient thermal resistance) and T

A

(ambient temperature) The maximum allowable power dissipation at any temperature

is P

Dmax

e

(T

Jmax

b

T

A

) i

JA

or the number given in the Absolute Maximum Ratings whichever is lower For this device T

Jmax

e

150 C and the typical thermal

resistance (i

JA

) of the ADC1251 with CMJ BIJ and CIJ suffixes when board mounted is 51 C W

Note 5

Human body model 100 pF discharged through a 1 5 kX resistor

4

Electrical Characteristics

(Continued)

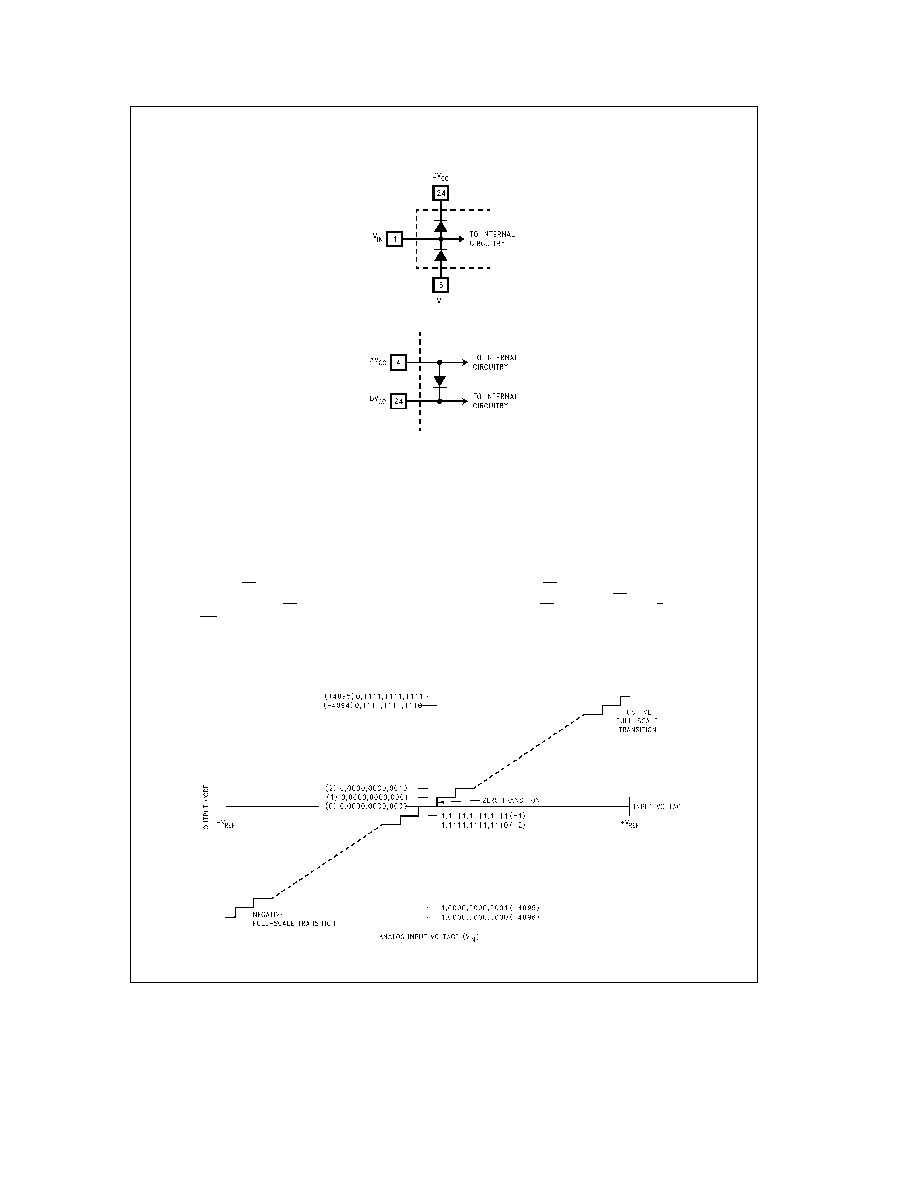

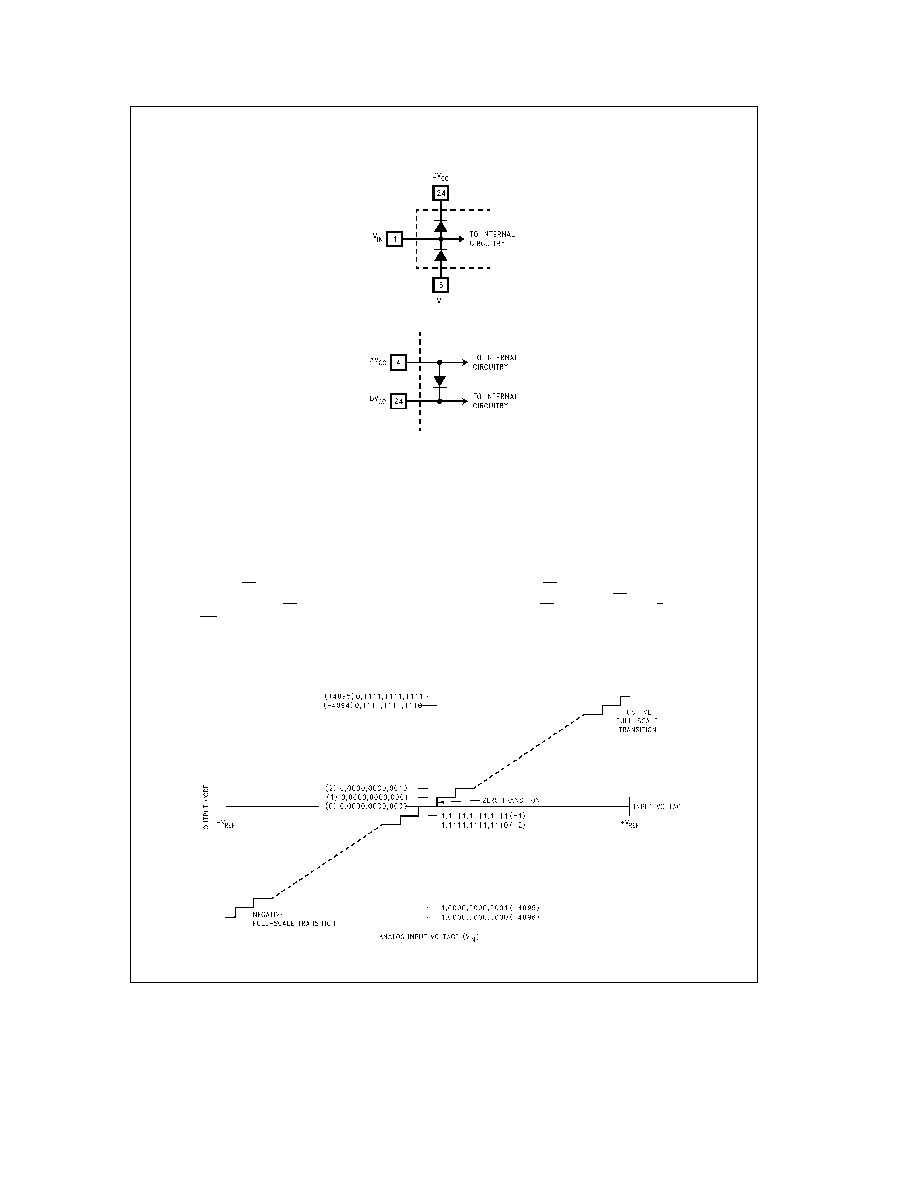

Note 6

Two on-chip diodes are tied to the analog input as shown below Errors in the A D conversion can occur if these diodes are forward biased more than

50 mV This means that if AV

CC

and DV

CC

are minimum (4 75 V

DC

) and V

b

is maximum (

b

4 75 V

DC

) the analog input full-scale voltage must be

s g

4 8 V

DC

TL H 11024 ≠ 4

Note 7

A diode exists between AV

CC

and DV

CC

as shown below

TL H 11024 ≠ 5

To guarantee accuracy it is required that the AV

CC

and DV

CC

be connected together to a power supply with separate bypass filters at each V

CC

pin

Note

8

Accuracy is guaranteed at f

CLK

e

3 5 MHz At higher or lower clock frequencies accuracy may degrade See the Typical Performance Characteristics

curves

Note

9

Typicals are at T

J

e

25 C and represent most likely parametric norm

Note 10

Limits are guaranteed to National's AOQL (Average Outgoing Quality Level)

Note 11

Positive linearity error is defined as the deviation of the analog value expressed in LSBs from the straight line that passes through positive full scale and

zero For negative linearity error the straight line passes through negative full scale and zero (See

Figures 1b and 1c )

Note 12

The ADC1251's self-calibration technique ensures linearity full scale and offset errors as specified but noise inherent in the self-calibration process will

result in a repeatability uncertainty of

g

0 20 LSB

Note 13

If T

A

changes then an Auto-Zero or Auto-Cal cycle will have to be re-started See the typical performance characteristic curves

Note 14

After an Auto-Zero or Auto-Cal cycle at the specified power supply extremes

Note 15

When using the WR control to start a conversion if the clock is asynchronous to the rising edge of WR an uncertainty of one clock period will exist in the

end of the interval t

A

therefore making t

A

end a minimum 6 clock periods or a maximum 7 clock periods after the rising edge of WR If the falling edge of the clock

is synchronous to the rising edge of WR then t

A

will end exactly 6 5 clock periods after the rising edge of WR This does not occur when S H control is used

Note 16

The CAL line must be high before a conversion is started

Note 17

The specifications for these parameters are valid after an Auto-Cal cycle has been completed

Note 18

The ADC1251 reference ladder is composed solely of capacitors

Note 19

A Military RETS Electrical Test Specification is available on request At time of printing the ADC1251CMJ 883 RETS specification complies fully with the

boldface

limits in this column

TL H 11024 ≠ 6

FIGURE 1a Transfer Characteristic

5