TL H 12814

LM9801

8-Bit

Greyscale24-Bit

Color

Linear

CCD

Sensor

Processor

June 1996

LM9801 8-Bit Greyscale 24-Bit Color Linear

CCD Sensor Processor

General Description

The LM9801 is a high performance integrated signal proc-

essor digitizer for linear CCD image scanners The LM9801

performs all the analog processing (correlated double sam-

pling for black level and offset compensation pixel-by-pixel

gain (shading) correction and 8-bit analog-to-digital conver-

sion) necessary to maximize the performance of a wide

range of linear CCD sensors

The LM9801 can be digitally programmed to work with a

wide variety of CCDs from different manufacturers An inter-

nal configuration register sets CCD and sampling timing to

maximize performance simplifying the design and manufac-

turing processes

The LM9801 can be used with parallel output color CCDs A

signal inversion mode eases use with CIS sensors For com-

plementary voltage reference see the LM4041

Applications

Y

Color and Greyscale Flatbed and Sheetfed Scanners

Y

Fax and Multifunction Peripherals

Y

Digital Copiers

Y

General Purpose Linear CCD Imaging

Features

Y

2 5 Million pixels s conversion rate

Y

Pixel-rate shading correction for individual pixels maxi-

mizes dynamic range and resolution even on ``weak''

pixels

Y

Implements Correlated Double Sampling for minimum

noise and offset error

Y

Reference and signal sampling points digitally con-

trolled in 25 ns increments for maximum performance

Y

Generates all necessary CCD clock signals

Y

Compatible with a wide range of linear CCDs

Y

Supports some Contact Image Sensors (CIS)

Y

TTL CMOS input output compatible

Key Specifications

Y

Resolution

8 Bits

Y

Pixel Conversion Rate

2 5 MHz

Y

Supply Voltage

a

5V

g

5%

Y

Supply Voltage (Digital I O)

a

3 3V

g

10% or

a

5V

g

5%

Y

Power Dissipation

230 mW (max)

Connection Diagrams

TL H 12814 � 1

TL H 12814 � 2

Ordering Information

Commercial (0 C

s

T

A

s

a

70 C)

Package

LM9801CCV

V52A 52-Pin Plastic Leaded Chip Carrier

LM9801CCVF

VEG52A 52-Pin Thin Quad Flatpack

TRI-STATE

is a registered trademark of National Semiconductor Corporation

MICROWIRE

TM

is a trademark of National Semiconductor Corporation

SPI

TM

is a trademark of Motorola Inc

C1996 National Semiconductor Corporation

RRD-B30M96 Printed in U S A

http

www national com

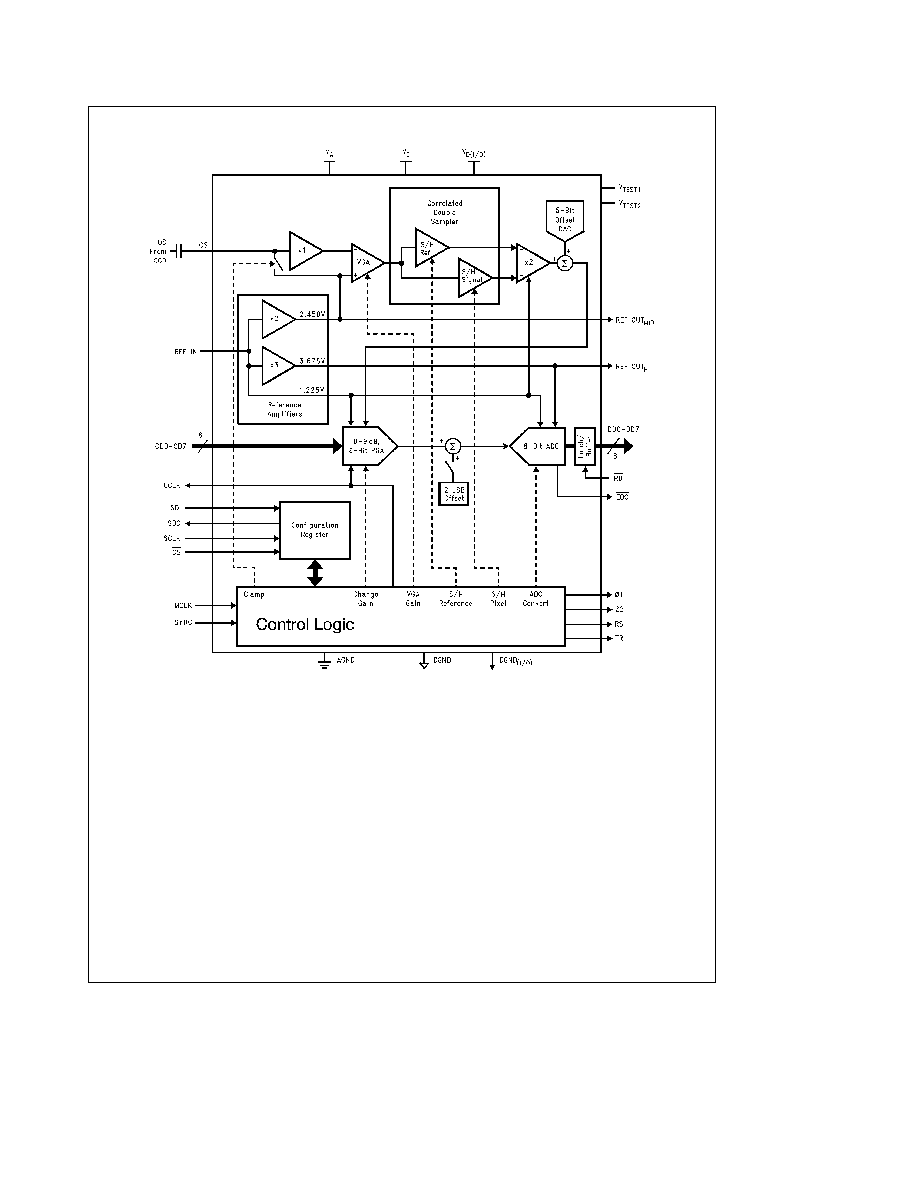

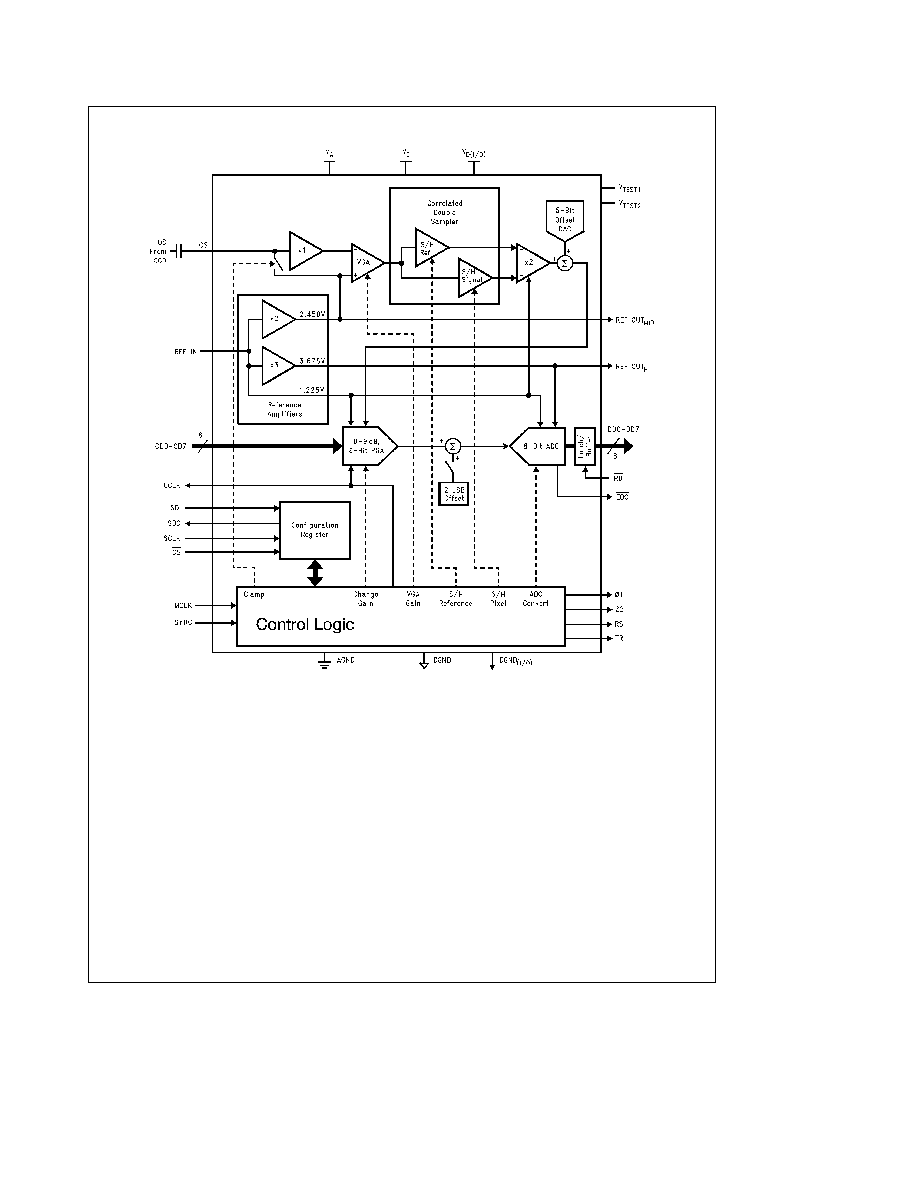

Block Diagram

TL H 12814 � 3

http

www national com

2

Absolute Maximum Ratings

(Notes 1 and 2)

Positive Supply Voltage (V

a

e

V

A

e

V

D

e

V

D(I O)

)

with Respect to GND

e

AGND

e

DGND

e

DGND

(I O)

6 5V

Voltage on any Input or Output Pin

0 3V to V

a

a

0 3V

Input Current at any Pin (Note 3)

g

25 mA

Package Input Current (Note 3)

g

50 mA

Package Dissipation at T

A

e

25 C

(Note 4)

ESD Susceptibility (Note 5)

Human Body Model

2000V

Soldering Information

Infrared 10 seconds (Note 6)

300 C

Storage Temperature

b

65 C to

a

150 C

Operating Ratings

(Notes 1 and 2)

Operating Temperature Range

T

MIN

s

T

A

s

T

MAX

LM9801CCV LM9801CCVF

0 C

s

T

A

s

a

70 C

V

A

Supply Voltage

a

4 75V to

a

5 25V

V

D

Supply Voltage

a

4 75V to

a

5 25V

V

D(I O)

Supply Voltage

a

2 7V to

a

5 25V

l

V

A

� V

D

l

s

100 mV

V

A

� V

D(I O)

t

b

100 mV

OS REF IN Voltage Range

b

0 05V to V

A

a

0 05V

CD0 � CD7 MCLK SYNC SDI SCLK

CS RD Voltage Range

b

0 05V to V

D(I O)

a

0 05V

Electrical Characteristics

The following specifications apply for AGND

e

DGND

e

DGND(I O)

e

0V V

A

e

V

D

e

a

5 0V

DC

V

D(I O)

e

a

5 0 or

a

3 0V

DC

REF IN

e

a

1 225V

DC

f

MCLK

e

20 MHz R

S

e

25X All LSB units are ADC LSBs unless otherwise specified

Boldface limits apply for T

A

e

T

J

e

T

MIN

to T

MAX

all other limits T

A

e

T

J

e

25 C (Notes 7 8 and 11)

Symbol

Parameter

Conditions

Typical

Limits

Units

(Note 9)

(Note 10)

(Limits)

CCD SOURCE REQUIREMENTS FOR FULL SPECIFIED ACCURACY AND DYNAMIC RANGE (Note 11)

V

WHITE

Maximum Peak CCD Differential

VGA Gain

e

0 dB

1 1

V (min)

Signal Range

VGA Gain

e

9 dB

0 4

V (min)

V

RFT

Maximum CCD Reset FeedThrough Amplitude

2

V (min)

ADC CHARACTERISTICS

Resolution with No Missing Codes

8

Bits (min)

ILE

Integral Linearity Error (Note 12)

g

1 5

LSB (max)

DNL

Differential Non-Linearity

g

1 0

LSB (max)

PGA CHARACTERISTICS

Monotonicity

8

Bits (min)

PGA Adjustment Range

Gain

PGA e 255

Gain

PGA e 0

2 95

2 8

V V (min)

Gain Error at any Gain (Note 14)

1 4

% (max)

VGA CHARACTERISTICS

Monotonicity

4

Bits (min)

VGA Adjustment Range

20log

Gain

VGA e 15

Gain

VGA e 0

J

8 95

8 5

dB (min)

Gain Error at any Gain (Note 15)

g

0 15

dB (max)

OFFSET TRIM CHARACTERISTICS

Offset DAC LSB Size

In Units of ADC LSBs

0 42

LSB

Offset DAC DNL

In Units of Offset DAC LSBs

g

0 25

g

0 9

LSB (max)

Offset Add Magnitude

In Units of ADC LSBs

2 0

1 6

LSB (min)

2 5

LSB (max)

http

www national com

3

Electrical Characteristics

(Continued)

The following specifications apply for AGND

e

DGND

e

DGND(I O)

e

0V V

A

e

V

D

e

a

5 0V

DC

V

D(I O)

e

a

5 0 or

a

3 0V

DC

REF IN

e

a

1 225V

DC

f

MCLK

e

20 MHz R

S

e

25X All LSB units are ADC LSBs unless otherwise specified

Boldface limits apply for T

A

e

T

J

e

T

MIN

to T

MAX

all other limits T

A

e

T

J

e

25 C (Notes 7 8 and 11)

Symbol

Parameter

Conditions

Typical

Limits

Units

(Note 9)

(Note 10)

(Limits)

SYSTEM CHARACTERISTICS

Full Channel Gain Error

VGA Gain

e

1 PGA Gain

e

1

g

0 6

g

3 0

% (max)

V

OS1

Pre-PGA Offset Error

VGA Gain

e

1 Offset DAC

e

0

g

1

LSB

V

OS2

Post-PGA Offset Error

Offset Add

e

0

g

1

LSB

REFERENCE AND ANALOG INPUT CHARACTERSTICS

OS Input Capacitance

5

pF

OS Input Leakage Current

Measured with OS

e

2 45V

DC

2

20

nA (max)

R

REF

ADC Reference Ladder (REF OUT

HI

to

950

500

X

(min)

REF IN) Impedance

1400

X

(max)

REF IN

Reference Voltage (Note 13)

1 225

1 19

V (min)

1 26

V (max)

DC and Logic Electrical Characteristics

The following specifications apply for AGND

e

DGND

e

DGND

(I O)

e

0V V

A

e

V

D

e

a

5 0V

DC

V

D(I O)

e

a

5 0 or

a

3 0V

DC

REF IN

e a

1 225V

DC

f

MCLK

e

20 MHz R

s

e

25X Boldface limits apply for T

A

e

T

J

e

T

MIN

to T

MAX

all

other limits T

A

e

T

J

e

25 C (Notes 7 and 8)

Symbol

Parameter

Conditions

Typical

Limits

Units

(Note 9)

(Note 10)

(Limits)

CD0 � CD7 MCLK SYNC SDI SCLK CS RD DIGITAL INPUT CHARACTERISTICS

V

IN(1)

Logical ``1'' Input Voltage

V

D(I O)

e

5 25V

2 0

V (min)

V

D(I O)

e

3 6V

2 0

V (min)

V

IN(0)

Logical ``0'' Input Voltage

V

D(I O)

e

4 75V

0 8

V (max)

V

D(I O)

e

2 7V

0 7

V (max)

I

IN

Input Leakage Current

V

IN

e

V

D

0 1

m

A

V

IN

e

DGND

b

0 1

m

A

C

IN

Input Capacitance

5

pF

DD0 � DD7 EOC CCLK SDO DIGITAL OUTPUT CHARACTERISTICS

V

OUT(1)

Logical ``1'' Output Voltage

V

D(I O)

e

4 75V I

OUT

e b

360 mA

2 4

V (min)

V

D(I O)

e

4 75V I

OUT

e b

10 mA

4 4

V (min)

V

D(I O)

e

2 7V I

OUT

e b

360 mA

2 1

V (min)

V

D(I O)

e

2 7V I

OUT

e b

10 mA

2 5

V (min)

V

OUT(0)

Logical ``0'' Output Voltage

V

D(I O)

e

5 25V I

OUT

e

1 6 mA

0 4

V (max)

V

D(I O)

e

3 6V I

OUT

e

1 6 mA

0 4

V (max)

I

OUT

TRI-STATE Output Current

V

OUT

e

DGND

0 1

m

A

(DD0 � DD7 only)

V

OUT

e

V

D

b

0 1

m

A

C

OUT

TRI-STATE Output Capacitance

5

pF

w1 w2 RS TR DIGITAL OUTPUT CHARACTERISTICS

V

OUT(1)

Logical ``1'' Output Voltage

V

D

e

4 75V I

OUT

e b

360 mA

2 4

V (min)

V

D

e

4 75V I

OUT

e b

10 mA

4 4

V (min)

V

OUT(0)

Logical ``0'' Output Voltage

V

D

e

5 25V I

OUT

e

1 6 mA

0 4

V (max)

http

www national com

4

DC and Logic Electrical Characteristics

(Continued)

The following specifications apply for AGND

e

DGND

e

DGND

(I O)

e

0V V

A

e

V

D

e

a

5 0V

DC

V

D(I O)

e

a

5 0 or

a

3 0V

DC

REF IN

e a

1 225V

DC

f

MCLK

e

20 MHz R

s

e

25X Boldface limits apply for T

A

e

T

J

e

T

MIN

to T

MAX

all

other limits T

A

e

T

J

e

25 C (Notes 7 and 8)

Symbol

Parameter

Conditions

Typical

Limits

Units

(Note 9)

(Note 10)

(Limits)

POWER SUPPLY CHARACTERISTICS

I

A

Analog Supply Current

Operating

25

32

mA (max)

Standby

50

m

A

I

D

Digital Supply Current

Operating

6

8

mA (max)

MCLK

e

0

65

m

A

I

D(I O)

Digital I O Supply Current

Operating V

D(I O)

e

5 0V

3 1

6

mA (max)

Operating V

D(I O)

e

3 0V

1 6

4

mA (max)

MCLK

e

0 V

D(I O)

e

5 0V or 3 0V

1 7

mA

AC Electrical Characteristics MCLK Independent

The following specifications apply for AGND

e

DGND

e

DGND

(I O)

e

0V V

A

e

V

D

e

V

D(I O)

e

a

5 0V

DC

REF IN

e

a

1 225V

DC

f

MCLK

e

20 MHz t

MCLK

e

1 f

MCLK

t

r

e

t

f

e

5 ns R

s

e

25X C

L

(databus loading)

e

50 pF pin Boldface

limits apply for T

A

e

T

J

e

T

MIN

to T

MAX

all other limits T

A

e

T

J

e

25 C (Notes 7 and 8)

Symbol

Parameter

Conditions

Typical

Limits

Units

(Note 9)

(Note 10)

(Limits)

f

MCLK

Maximum MCLK Frequency

20

MHz (min)

Minimum MCLK Frequency

1

MHz (max)

MCLK Duty Cycle

30

40

% (min)

70

60

% (max)

t

A

SYNC Setup of MCLK

5

10

ns (min)

t

CDSETUP

Correction Data Valid to CLK Setup

14

20

ns (min)

t

CDHOLD

Correction Data Valid to CLK Hold

b

12

0

ns (min)

t

D1H

t

D0H

RD High to DD0 � DD7 TRI-STATE

5

15

ns (max)

t

DACC

Access Time Delay from RD Low to

15

30

ns (max)

DD0 � DD7 Data Valid

f

SCLK

Maximum SCLK Frequency

20

MHz (min)

SCLK Duty Cycle

40

% (min)

60

% (max)

t

SDI

SDI Set-Up Time from SCLK

3

10

ns (min)

Rising Edge

t

HDI

SDI Hold Time from SCLK

2

15

ns (min)

Rising Edge

t

DDO

Delay from SCLK Falling Edge to

25

50

ns (max)

SDO Data Valid

t

HDO

SDO Hold Time from SCLK

R

L

e

3k C

L

e

50 pF

30

50

ns (max)

Falling Edge

5

ns (min)

t

DELAY

DELAY from SCLK Falling Edge to

5

10

ns (min)

CS Rising or Falling Edge

t

SETUP

Set-Up Time of CS Rising or Falling

0

10

ns (min)

Edge to SCLK Rising Edge

http

www national com

5