Oki Electric Industry

Co.,Ltd.

No.

GTD-18373

Electronic Components

KGL4223 5-Gbps 8:1 MUX

1. SCOPE

This document describes the electrical characteristics of the KGL4223.

2. PRODUCT NAME

KGL4223

3.

FUNCTIONS

This device converts 8bit parallel streams into one stream up to 5GHz clock frequency.

Complementary output data are synchronized with an input clock. Parallel data

loading is accomplished synchronously with an internal 1/8 clock, which is generated

by dividing the input clock on chip.

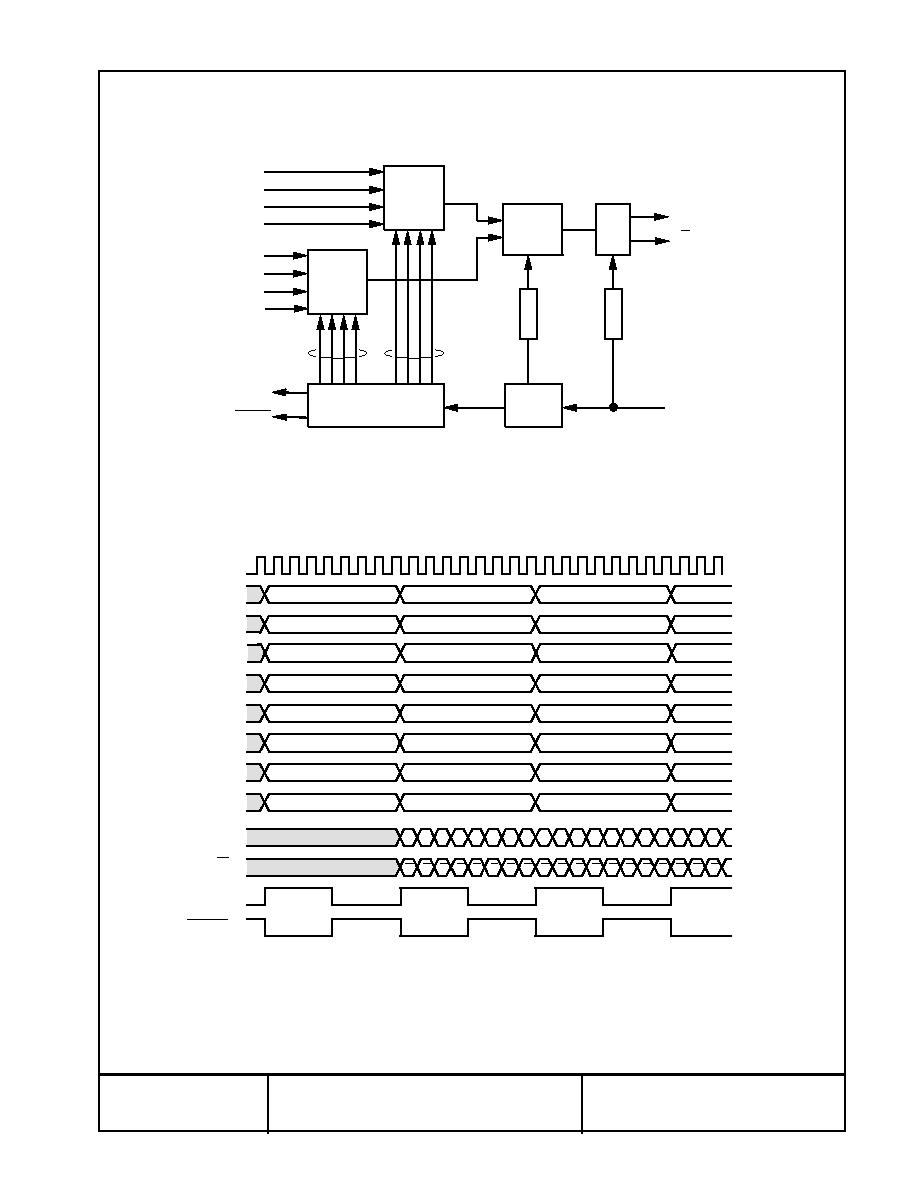

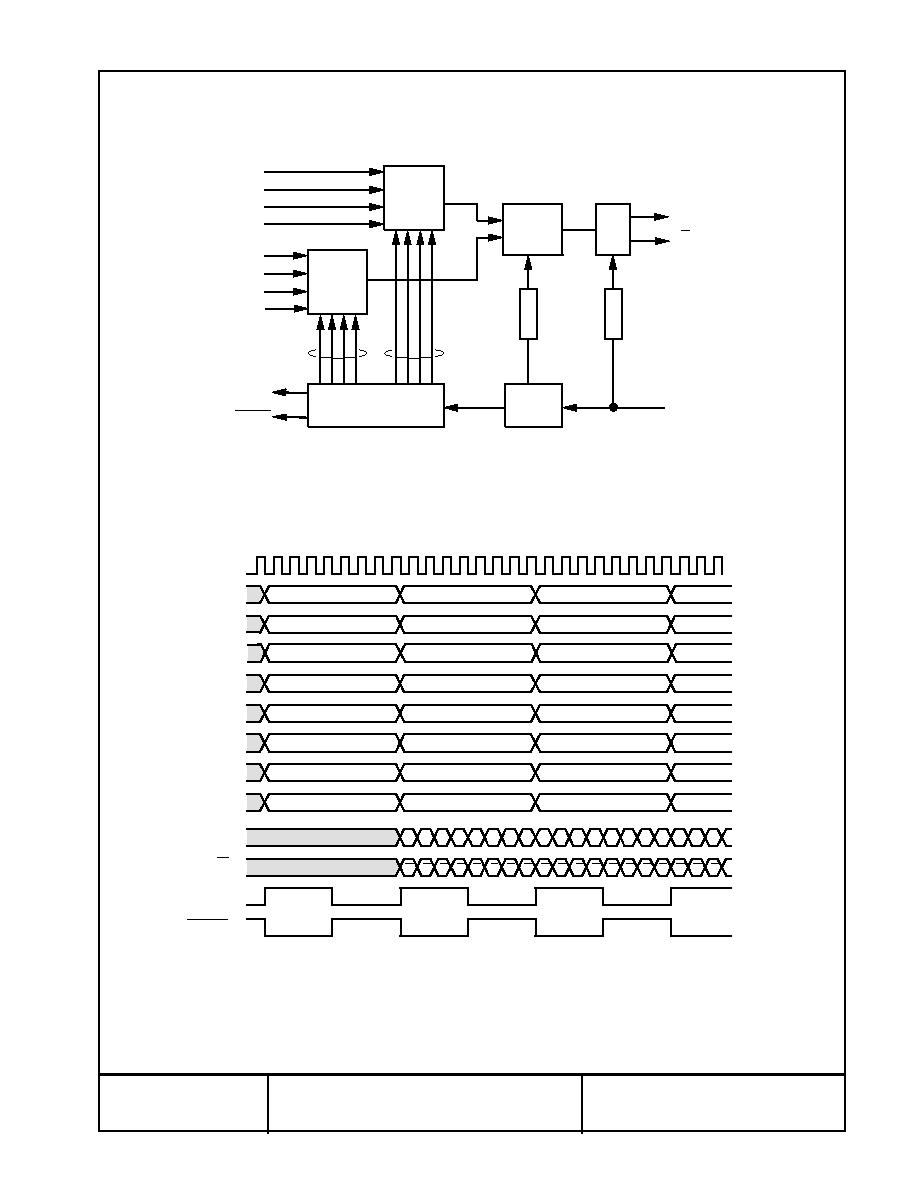

Functional diagram and time chart are indicated Figure1 and Figure2.

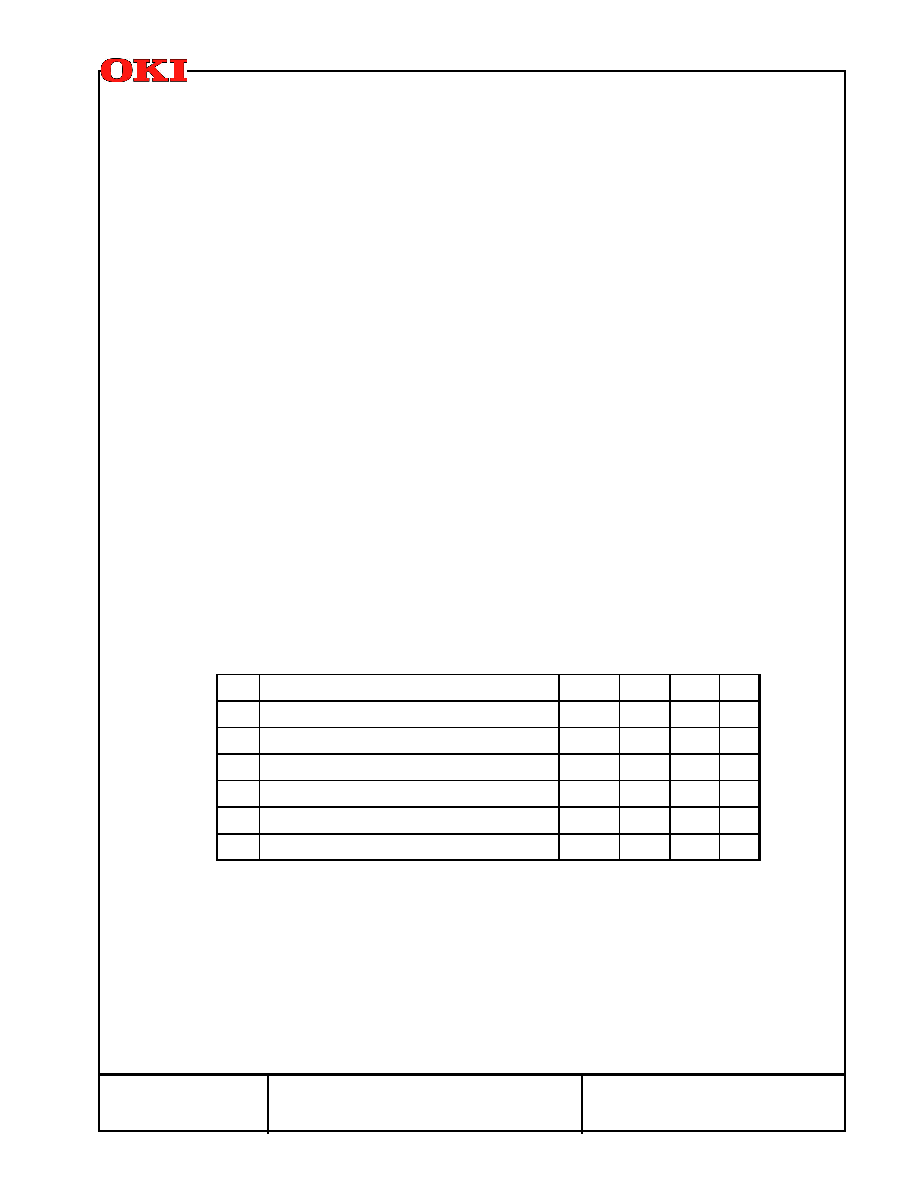

4. ABSOLUTE MAXIMUM RATINGS

No.

Item

Symbol Min. Max. Unit

1 Supply Voltage for Internal Logic

VDD

-0.3

2.3

V

2 Supply Voltage for Output Buffer

VB

-0.3

2.3

V

3 Clock Input

CK

-0.3

1.5

V

4 Data Inputs

D0

�`

7 -0.3

1.5

V

6 Temperature at Package Base under Bias

Ts

-45

100

�

7 Storage Temperature

Tst

-45

125

�

Oki Electric Industry

Co.,Ltd.

No.

GTD-18373

1/2

divider

4:1

MUX

4:1

MUX

1/4 divider

2:1

MUX

Output Latch

delay

delay

Figure 1 Block Diagram of KGL4223

D0

D2

D4

D6

1/2CK

1/2CK

1/8CK

1/8CK

CK

Q

Q

D1

D3

D5

D7

1/8CK

1/8CK

Figure 2 Time Chart of KGL4223

A4

A3

A2

A1

B4

B3

B2

B1

C4

C3

C2

C1

D4

D3

D2

D1

E4

E3

E2

E1

F4

F3

F2

F1

G4

G3

G2

G1

H4

H3

H2

H1

A1

B1

C1

D1

E1

F1

G1

H1

A2

B2

C2

D2

E2

F2

G2

H2

A3

B3

C3

A1

B1

C1

D1

E1

F1

G1

H1

A2

B2

C2

D2

E2

F2

G2

H2

A3

B3

C3

CK

D0

D1

D2

D3

D4

D5

D6

D7

Q

Q

1/8 CK

1/8 CK

2/6

Oki Electric Industry

Co.,Ltd.

No.

GTD-18373

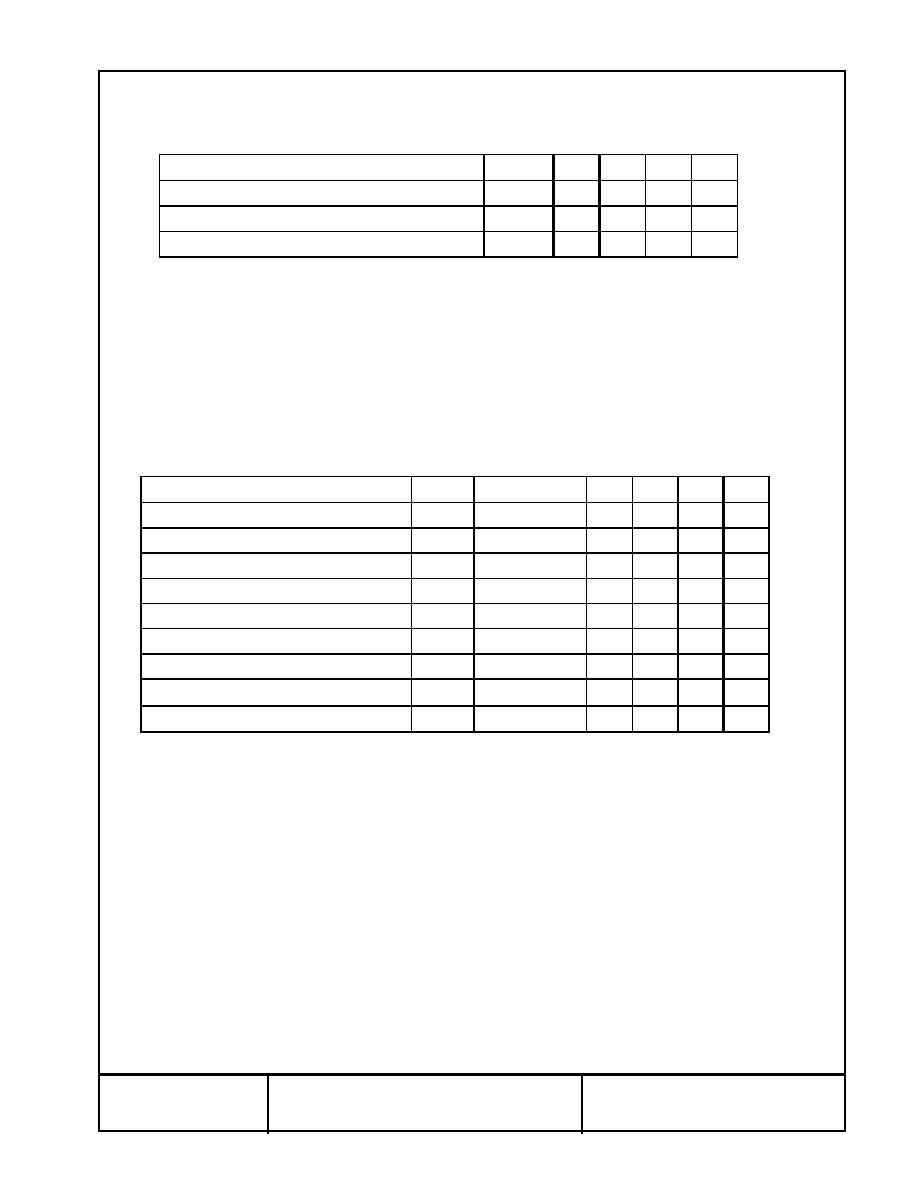

5. RRECOMMENDED OPERATING CONDITIONS

Item

Symbol

Min.

Typ.

Max.

Unit

Power Supply Voltage for Internal Logic

V D D

1.9

2.0

2.1

V

Power Supply Voltage for Output Buffer

VB

1.9

2.0

2.1

V

Operating Temperature Range at Package Base

Ts

0

70

�

6. ELECTRICAL CHARACTERISTICS

6-1 DC CHARATERISTICS

V D D = 2 V

�}

0.1V, VB=2V

�}

0.1V ,Ts = 0

�`

70

�

Item

Symbol Test Condition

Min.

Typ.

Max.

Unit

Power Dissipation

P

---

3.0

W

High-level 1/8CK Output Voltage

V O H

50

�

Load

0.85

1.3

V

Low-level 1/8CK Output Voltage

VOL

50

�

Load

0

0.3

V

High-level Data Output Voltage

V O D H

50

�

Load

0.85

1.3

V

Low-level Data Output Voltage

VODL

50

�

Load

0

0.3

V

Data & 1/8CK Outputs Voltage Swing

V O D

50

�

Load

0.7

1.2

Vpp

Clock Input Voltage Swing

VIC

0.5

0.9

Vpp

High-level Data Input Voltage

VIDH

0.8

1.3

V

low -level Data Input Voltage

VIDL

0

0.3

V

3/6

Oki Electric Industry

Co.,Ltd.

No.

GTD-18373

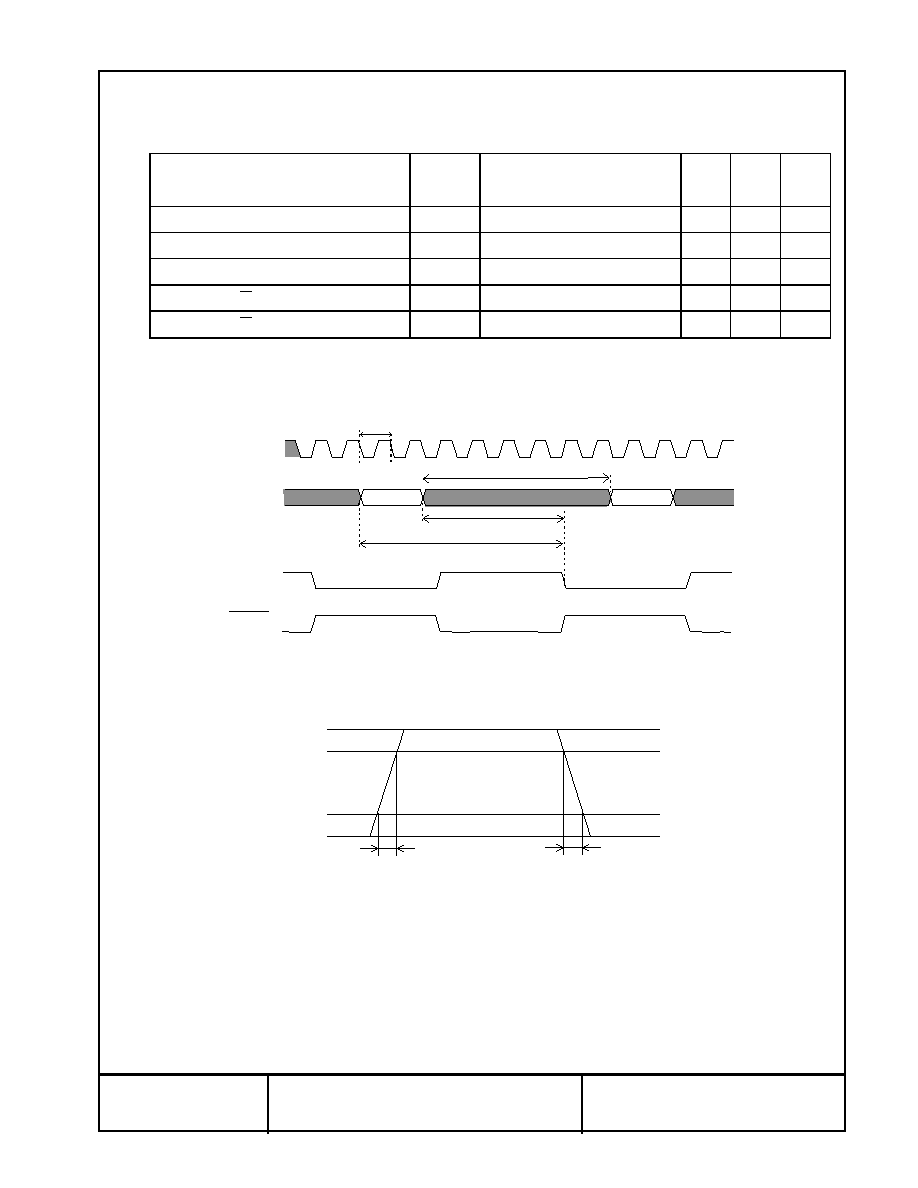

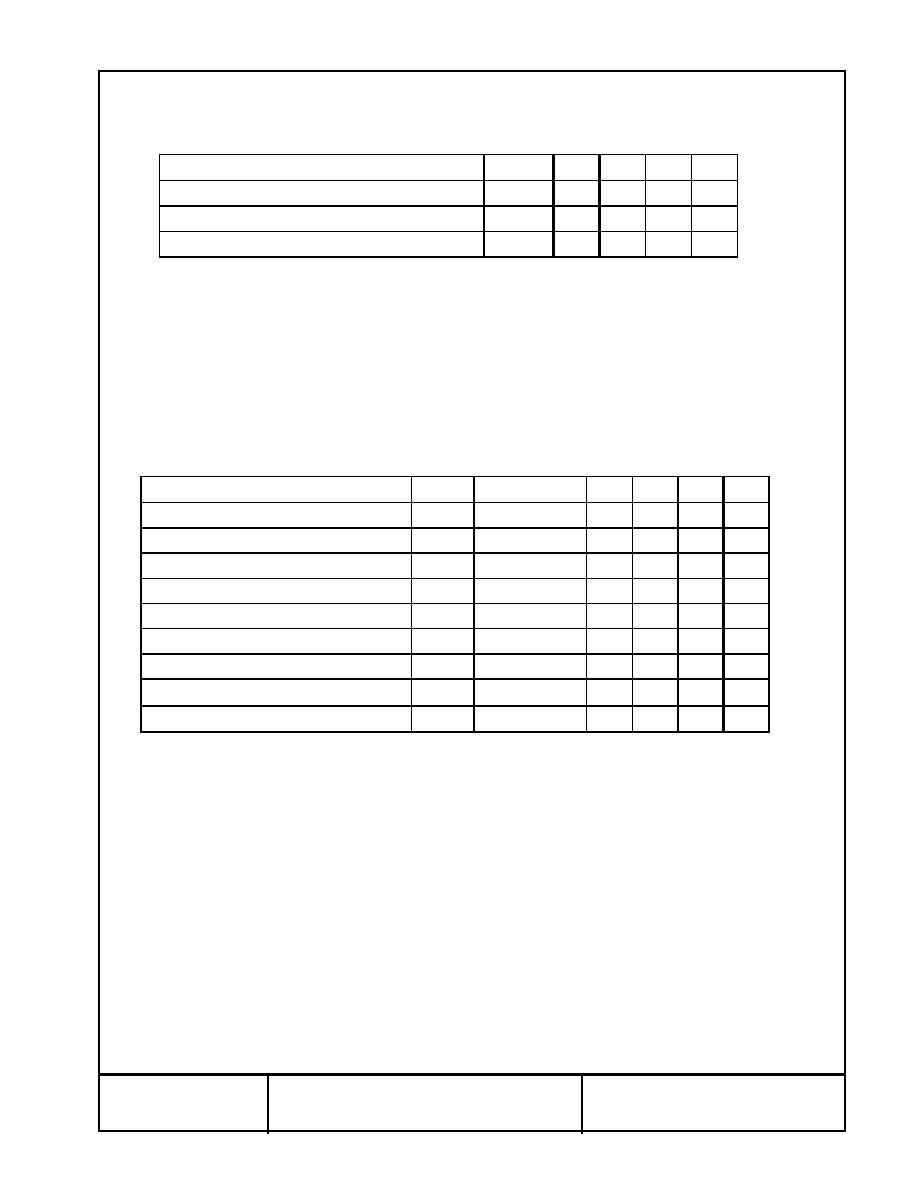

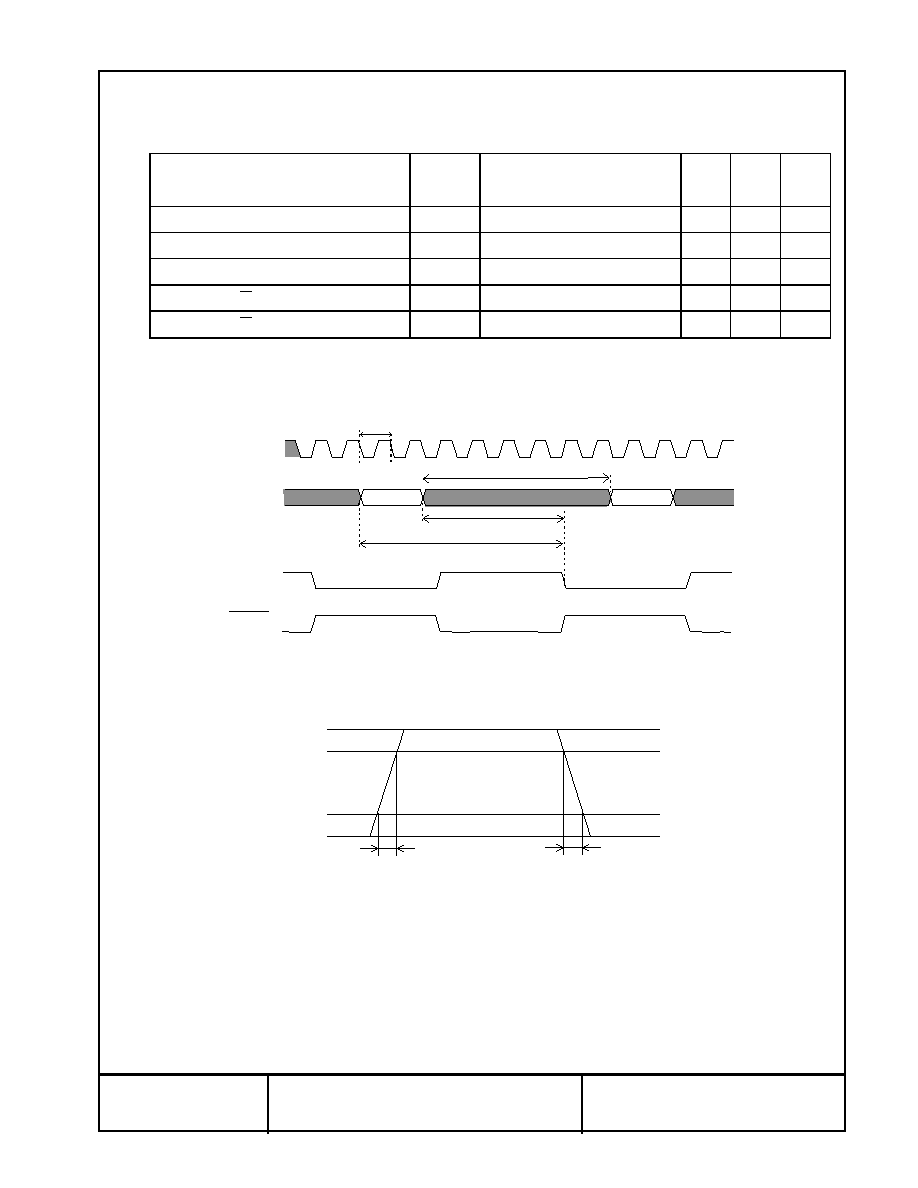

6-2. AC CHARACTERISTICS

VDD=2V�0.1V, VB=2V�0.1V, Ts=0~70

Item

Symbol

Test Condition

Min.

Typ. Max.

Unit

Maximum Operating Clock Frequency

fo

---

---

5

GHz

Set-up time (Data to 1/8CK )

t

DS

fo=5GHz

450

500

600

ps

Hold time (1/8CK to Data)

t

DH

fo=5GHz

-250

-350

-450

ps

CK-D0~7 Phase Margin

t

M

fo=5GHz

1300

1400

ps

Rise Time (Q,Q)

tr

fo=5GHz

20

30

50

ps

Fall Time (Q,Q)

tf

fo=5GHz

20

30

50

ps

Valid

Valid

�

t

M

t

DS

�

t

C

CK

D0

�`

D7

1/8CK

1/8CK

t

DH

Figure 3 Waveforms of KGL4223

100%

80%

20%

0%

Figure 4 Rise and Fall Times

tr

tf

4/6

fo=1/

tc

Oki Electric Industry

Co.,Ltd.

No.

GTD-18373

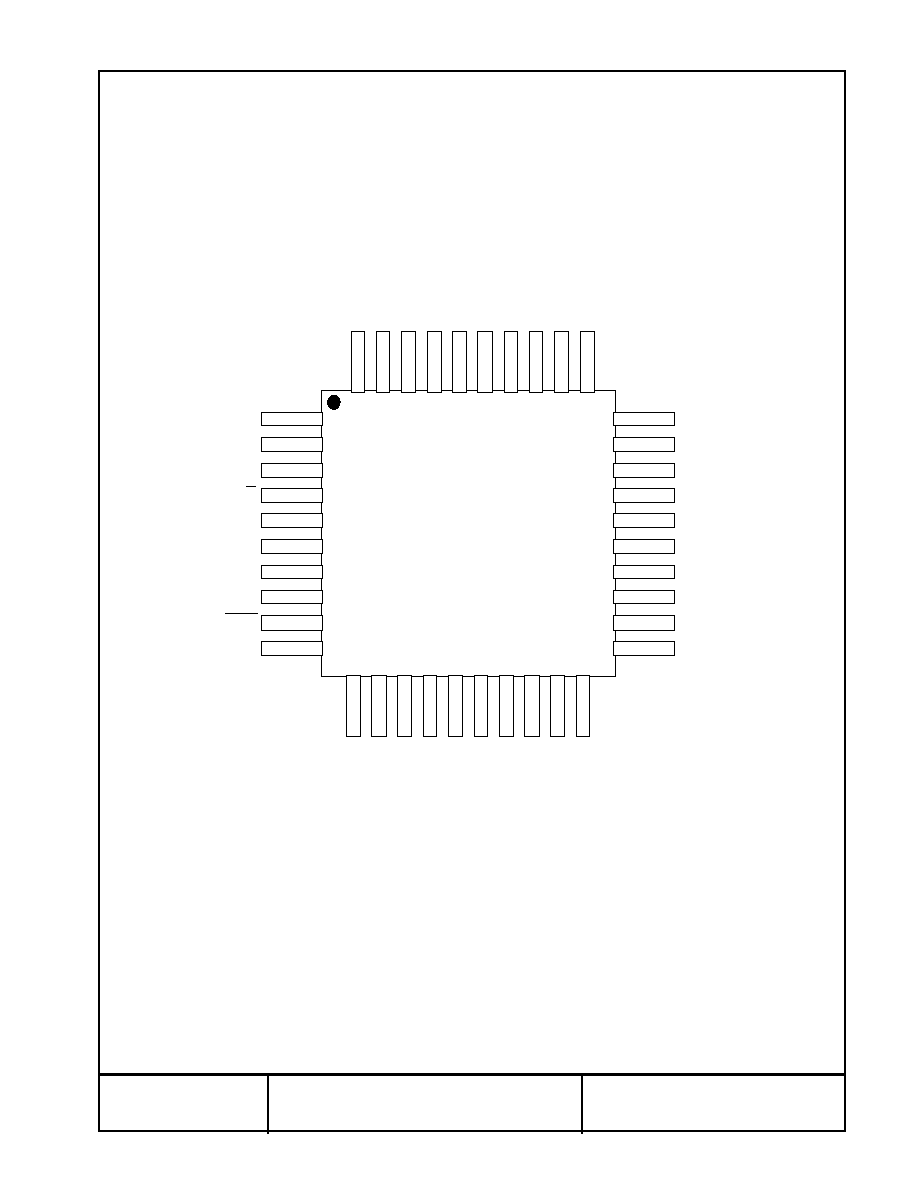

7.

DEVICE ACCEPT/REJECT CRITERIA

Each device must meet all parameters listed in Paragraph 6. A device is rejected if it fails to

meet one or any combination of parameters.

8.

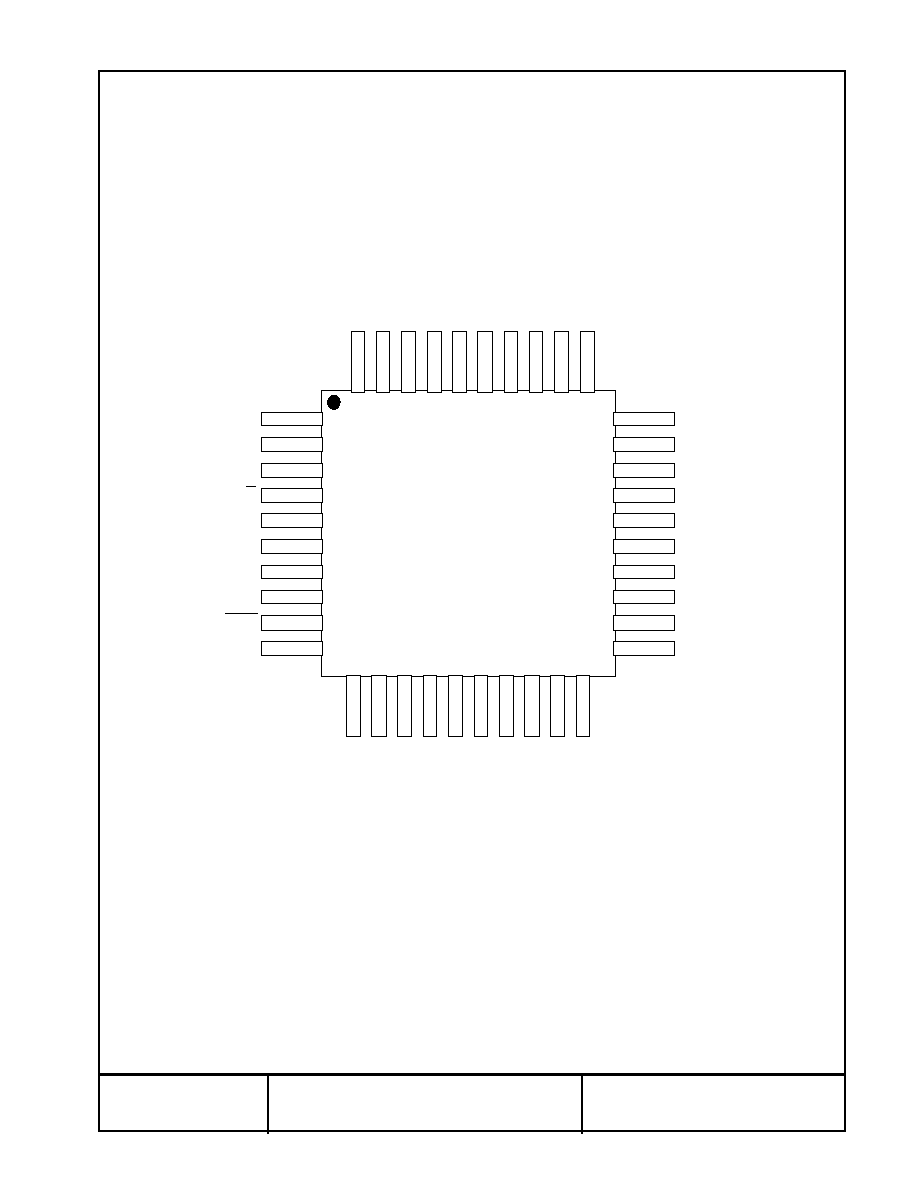

PIN ARRANGEMENT

40

39

38

37

36

35

34

33

32

31

1

2

3

4

5

6

7

8

9

10

30

29

28

27

26

25

24

23

22

21

11

12

13

14

15

16

17

18

19

20

VDD

VB D1

G D3

D5

G D7

VDD

G

G VDD D0 G D2 D4

G

D6

G

G

G

Q

G

Q

G

G

1/8CK

G

1/8CK

VB

G

G

G

RCK

G

G

CK

G

G

VDD

(Top View)

Note: 1. G is a ground terminal.

2 . RCK is a clock reference terminal. Usually RCK is connected to

ground through a capacitor ( 100nF ).

Figure 5 PIN Arrangement of KGL4223

5/6

VDD VB D1 G D3 D5 G D7 VDD G

G VDD D0 G D2 D4 G D6 G G

Q

1/8CK