| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: MC74VHC00 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

©

Semiconductor Components Industries, LLC, 2003

July, 2003 - Rev. 4

1

Publication Order Number:

MC74VHC00/D

MC74VHC00

Quad 2-Input NAND Gate

The MC74VHC00 is an advanced high speed CMOS 2-input

NAND gate fabricated with silicon gate CMOS technology. It

achieves high speed operation similar to equivalent Bipolar Schottky

TTL while maintaining CMOS low power dissipation.

The internal circuit is composed of three stages, including a buffer

output which provides high noise immunity and stable output. The

inputs tolerate voltages up to 7 V, allowing the interface of 5 V

systems to 3 V systems.

∑

High Speed: t

PD

= 3.7 ns (Typ) at V

CC

= 5 V

∑

Low Power Dissipation: I

CC

= 2

mA (Max) at T

A

= 25

∞

C

∑

High Noise Immunity: V

NIH

= V

NIL

= 28% V

CC

∑

Power Down Protection Provided on Inputs

∑

Balanced Propagation Delays

∑

Designed for 2 V to 5.5 V Operating Range

∑

Low Noise: V

OLP

= 0.8 V (Max)

∑

Pin and Function Compatible with Other Standard Logic Families

∑

Latchup Performance Exceeds 300 mA

∑

ESD Performance: HBM > 2000 V; Machine Model > 200 V

∑

Chip Complexity: 32 FETs or 8 Equivalent Gates

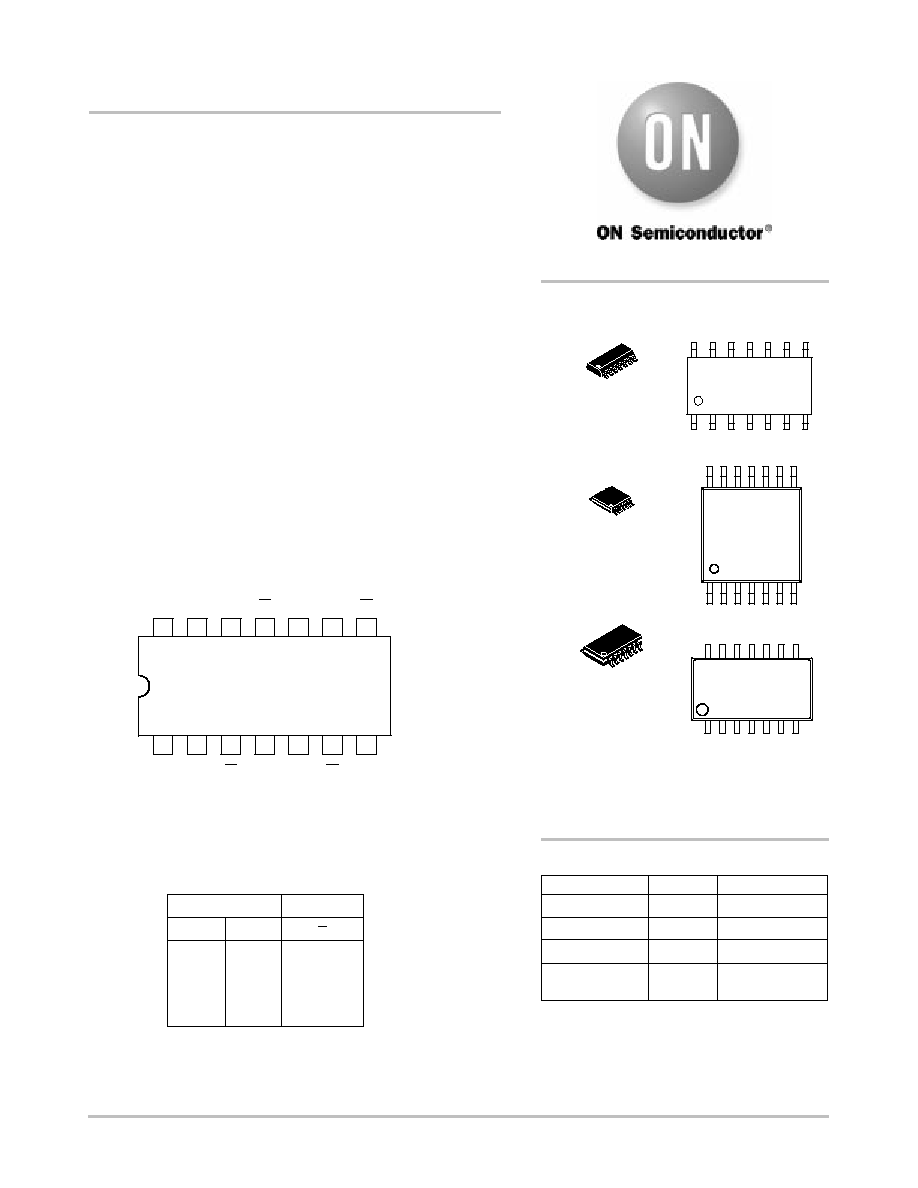

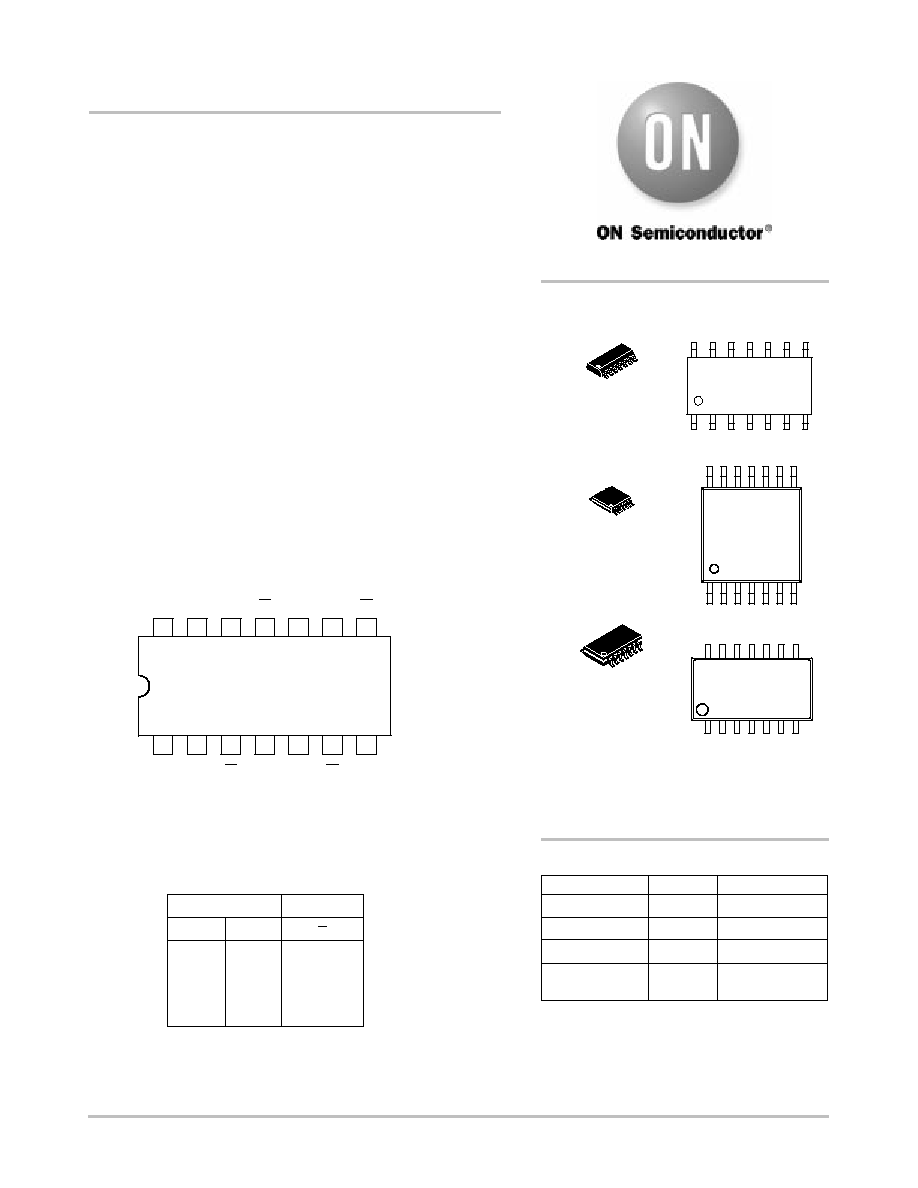

Figure 1. Pinout: 14 - Lead Packages

(Top View)

13

14

12

11

10

9

8

2

1

3

4

5

6

7

V

CC

B4

A4

Y4

B3

A3

Y3

A1

B1

Y1

A2

B2

Y2

GND

L

L

H

H

L

H

L

H

FUNCTION TABLE

Inputs

Output

A

B

H

H

H

L

Y

A

= Assembly Location

L, WL

= Wafer Lot

Y

= Year

W, WW = Work Week

MARKING DIAGRAMS

Device

Package

Shipping

ORDERING INFORMATION

MC74VHC00DR2

SO-14

2500 Tape & Reel

MC74VHC00DT

TSSOP-14

96 Units/Rail

MC74VHC00DTR2

TSSOP-14 2500 Tape & Reel

MC74VHC00MEL

EIAJ

SO-14

2000 Tape & Reel

SO - 14

D SUFFIX

CASE 751A - 03

TSSOP - 14

DT SUFFIX

CASE 948G - 01

EIAJ SO - 14

M SUFFIX

CASE 965 - 01

14

1

14

1

1

14

VHC00

AWLYWW

VHC00

AWLYWW

VHC00

ALYW

http://onsemi.com

MC74VHC00

http://onsemi.com

2

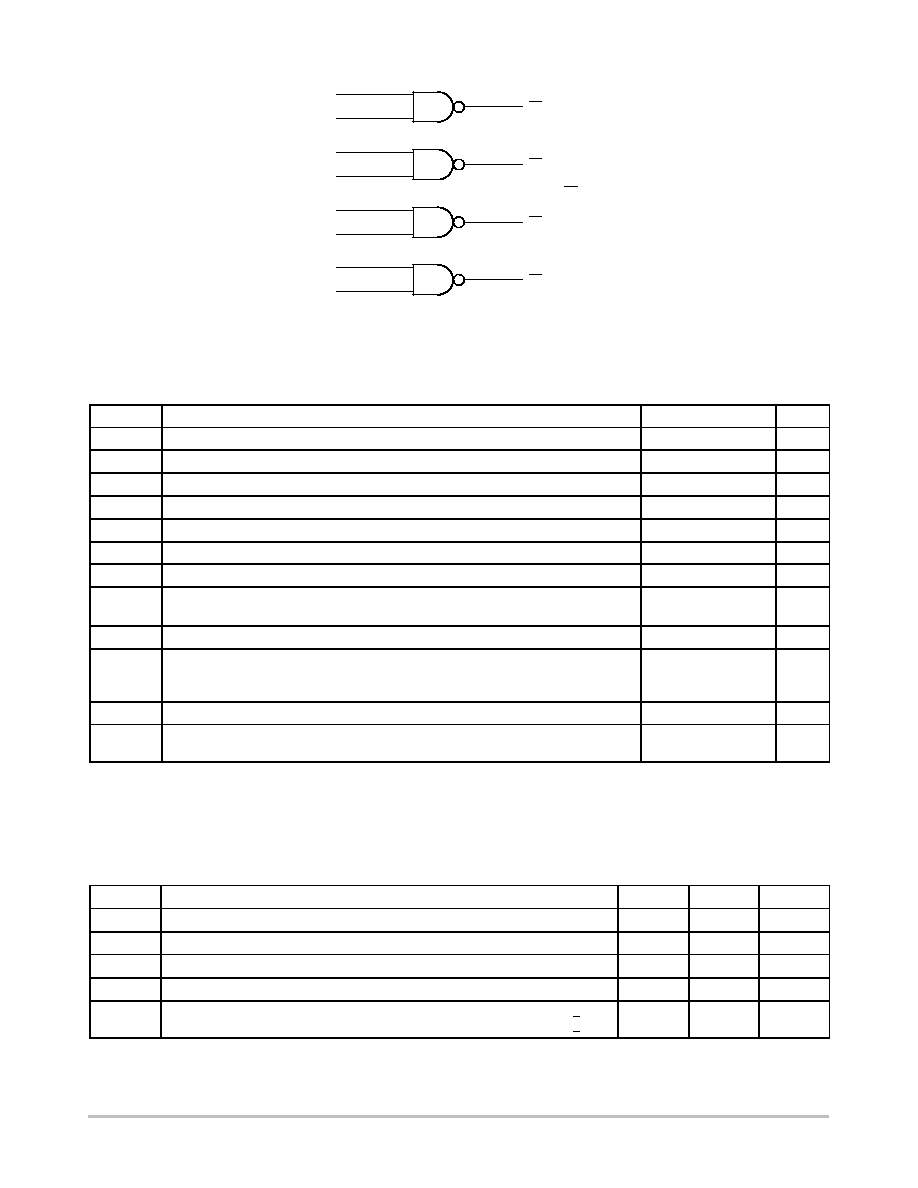

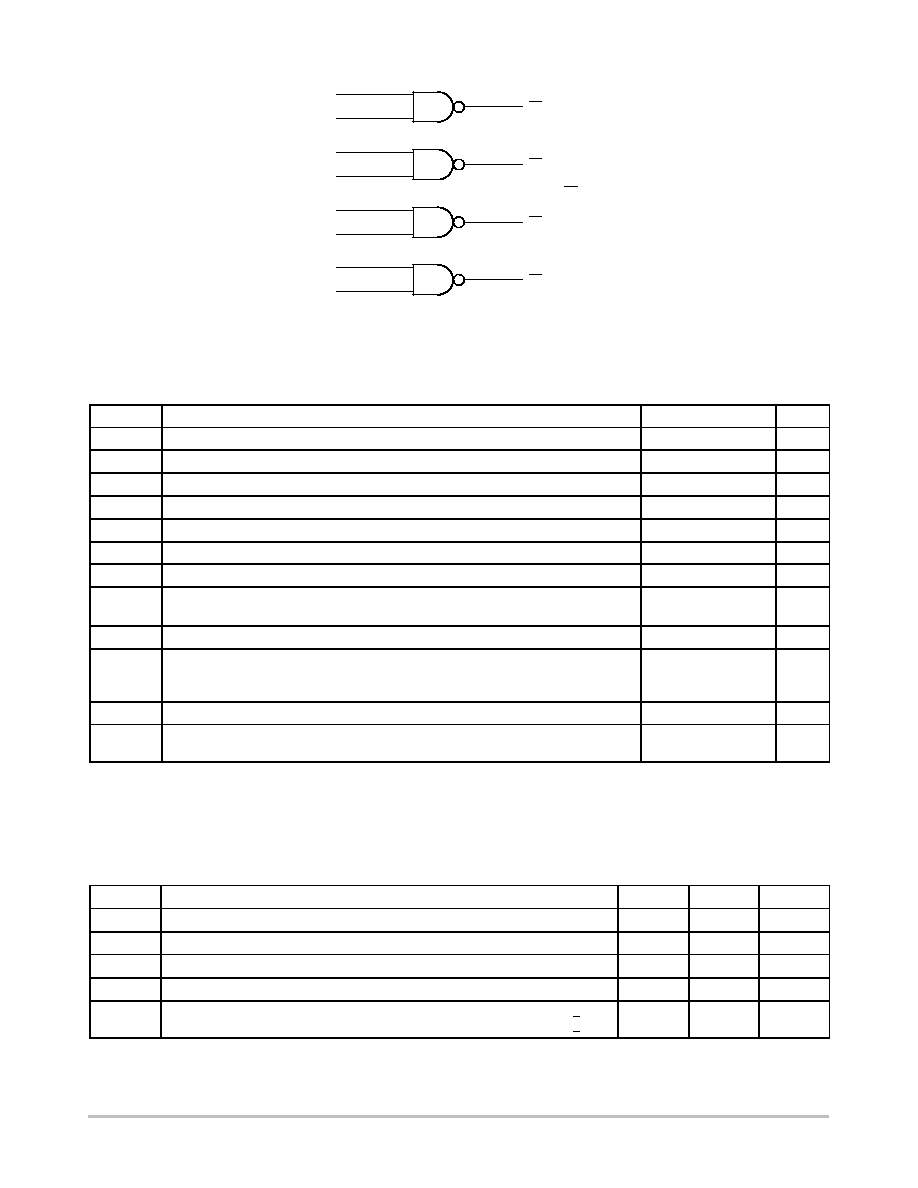

3

Y1

1

A1

Figure 2. Logic Diagram

2

B1

6

Y2

4

A2

5

B2

8

Y3

9

A3

10

B3

11

Y4

12

A4

13

B4

Y = AB

MAXIMUM RATINGS

(Note 1)

Symbol

Parameter

Value

Unit

V

CC

Positive DC Supply Voltage

- 0.5 to +7.0

V

V

IN

Digital Input Voltage

- 0.5 to +7.0

V

V

OUT

DC Output Voltage

- 0.5 to V

CC

+0.5

V

I

IK

Input Diode Current

- 20

mA

I

OK

Output Diode Current

$

20

mA

I

OUT

DC Output Current, per Pin

$

25

mA

I

CC

DC Supply Current, V

CC

and GND Pins

$

75

mA

P

D

Power Dissipation in Still Air

SOIC Package

TSSOP

200

180

mW

T

STG

Storage Temperature Range

- 65 to +150

∞

C

V

ESD

ESD Withstand Voltage

Human Body Model (Note 2)

Machine Model (Note 3)

Charged Device Model (Note 4)

>2000

>200

N/A

V

I

LATCH-UP

Latch - Up Performance

Above V

CC

and Below GND at 125

∞

C (Note 5)

$

300

mA

q

JA

Thermal Resistance, Junction to Ambient

SOIC Package

TSSOP

143

164

∞

C/W

1. Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the

Recommended Operating Conditions.

2. Tested to EIA/JESD22 - A114 - A

3. Tested to EIA/JESD22 - A115 - A

4. Tested to JESD22 - C101 - A

5. Tested to EIA/JESD78

RECOMMENDED OPERATING CONDITIONS

Symbol

Characteristics

Min

Max

Unit

V

CC

DC Supply Voltage

2.0

5.5

V

V

IN

DC Input Voltage

0

5.5

V

V

OUT

DC Output Voltage

0

V

CC

V

T

A

Operating Temperature Range, All Package Types

- 55

125

∞

C

t

r

, t

f

Input Rise or Fall Time

V

CC

= 3.3 V + 0.3 V

V

CC

= 5.0 V + 0.5 V

0

0

100

20

ns/V

MC74VHC00

http://onsemi.com

3

ŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒ

ŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒ

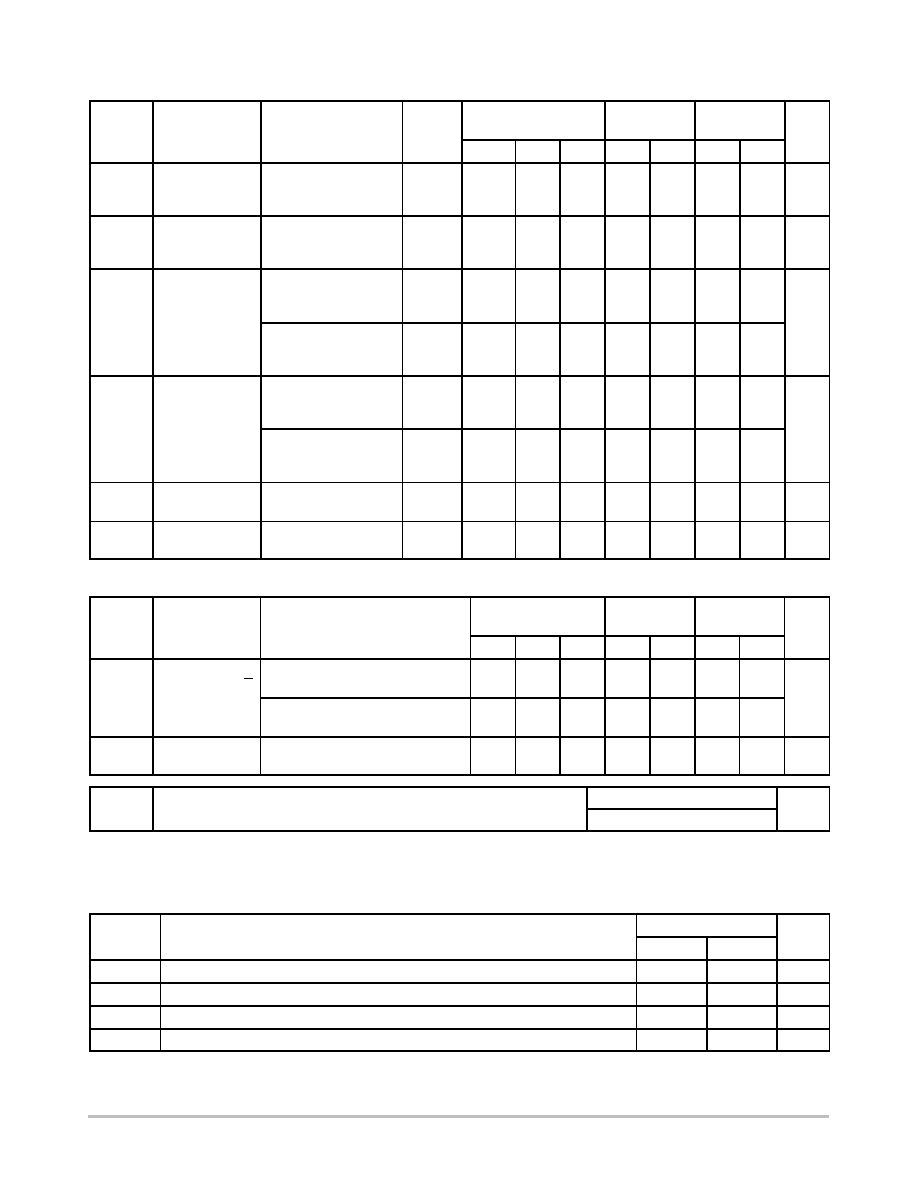

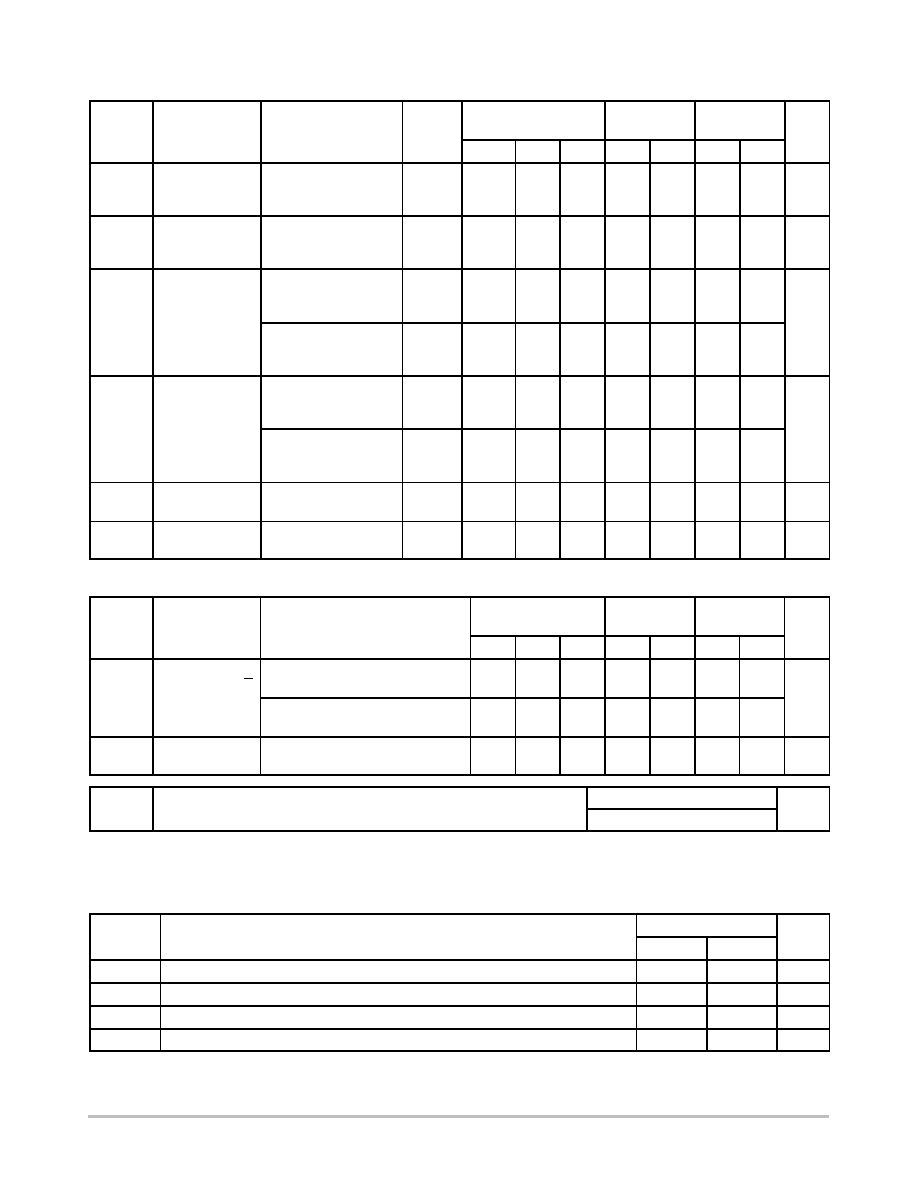

DC ELECTRICAL CHARACTERISTICS

ŒŒŒŒ

Œ

ŒŒ

Œ

ŒŒŒŒ

ŒŒŒŒŒŒ

Œ

ŒŒŒŒ

Œ

ŒŒŒŒŒŒ

ŒŒŒŒŒŒŒ

Œ

ŒŒŒŒŒ

Œ

ŒŒŒŒŒŒŒ

ŒŒŒŒ

Œ

ŒŒ

Œ

ŒŒŒŒ

V

CC

ŒŒŒŒŒŒŒ

ŒŒŒŒŒŒ

Œ

ŒŒŒŒŒŒŒ

T

A

= 25

∞

C

ŒŒŒŒŒ

Œ

ŒŒŒ

Œ

ŒŒŒŒŒ

T

A

= - 40 to

85

∞

C

ŒŒŒŒŒ

Œ

ŒŒŒ

Œ

ŒŒŒŒŒ

T

A

= - 55 to

+125

∞

C

ŒŒ

ŒŒ

ŒŒ

ŒŒŒŒ

ŒŒŒŒ

Symbol

ŒŒŒŒŒŒ

ŒŒŒŒŒŒ

Parameter

ŒŒŒŒŒŒŒ

ŒŒŒŒŒŒŒ

Test Conditions

ŒŒŒŒ

ŒŒŒŒ

V

CC

V

ŒŒŒ

ŒŒŒ

Min

ŒŒŒ

ŒŒŒ

Typ

ŒŒŒ

ŒŒŒ

Max

ŒŒŒ

ŒŒŒ

Min

ŒŒŒ

ŒŒŒ

Max

ŒŒŒ

ŒŒŒ

Min

ŒŒŒ

ŒŒŒ

Max

ŒŒ

ŒŒ

Unit

ŒŒŒŒ

Œ

ŒŒ

Œ

ŒŒŒŒ

V

IH

ŒŒŒŒŒŒ

Œ

ŒŒŒŒ

Œ

ŒŒŒŒŒŒ

High - Level Input

Voltage

ŒŒŒŒŒŒŒ

Œ

ŒŒŒŒŒ

Œ

ŒŒŒŒŒŒŒ

ŒŒŒŒ

Œ

ŒŒ

Œ

ŒŒŒŒ

2.0

3.0 to

5.5

ŒŒŒ

ŒŒ

Œ

ŒŒŒ

1.50

V

CC

x

0.7

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

1.50

V

CC

x

0.7

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

1.50

V

CC

x

0.7

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

ŒŒ

ŒŒ

ŒŒ

V

ŒŒŒŒ

Œ

ŒŒ

Œ

ŒŒŒŒ

V

IL

ŒŒŒŒŒŒ

Œ

ŒŒŒŒ

Œ

ŒŒŒŒŒŒ

Low - Level Input

Voltage

ŒŒŒŒŒŒŒ

Œ

ŒŒŒŒŒ

Œ

ŒŒŒŒŒŒŒ

ŒŒŒŒ

Œ

ŒŒ

Œ

ŒŒŒŒ

2.0

3.0 to

5.5

ŒŒŒ

ŒŒ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

0.50

V

CC

x

0.3

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

0.50

V

CC

x

0.3

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

0.50

V

CC

x

0.3

ŒŒ

ŒŒ

ŒŒ

V

ŒŒŒŒ

Œ

ŒŒ

Œ

Œ

ŒŒ

Œ

ŒŒŒŒ

V

OH

ŒŒŒŒŒŒ

Œ

ŒŒŒŒ

Œ

Œ

ŒŒŒŒ

Œ

ŒŒŒŒŒŒ

High - Level

Output Voltage

ŒŒŒŒŒŒŒ

Œ

ŒŒŒŒŒ

Œ

Œ

ŒŒŒŒŒ

Œ

ŒŒŒŒŒŒŒ

V

in

= V

IH

or V

IL

I

OH

= - 50

m

A

ŒŒŒŒ

Œ

ŒŒ

Œ

Œ

ŒŒ

Œ

ŒŒŒŒ

2.0

3.0

4.5

ŒŒŒ

ŒŒ

Œ

ŒŒ

Œ

ŒŒŒ

1.9

2.9

4.4

ŒŒŒ

Œ

Œ

Œ

Œ

Œ

Œ

ŒŒŒ

2.0

3.0

4.5

ŒŒŒ

Œ

Œ

Œ

Œ

Œ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

Œ

Œ

Œ

ŒŒŒ

1.9

2.9

4.4

ŒŒŒ

Œ

Œ

Œ

Œ

Œ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

Œ

Œ

Œ

ŒŒŒ

1.9

2.9

4.4

ŒŒŒ

Œ

Œ

Œ

Œ

Œ

Œ

ŒŒŒ

ŒŒ

ŒŒ

ŒŒ

ŒŒ

V

ŒŒŒŒ

Œ

ŒŒ

Œ

Œ

ŒŒ

Œ

ŒŒŒŒ

ŒŒŒŒŒŒ

Œ

ŒŒŒŒ

Œ

Œ

ŒŒŒŒ

Œ

ŒŒŒŒŒŒ

ŒŒŒŒŒŒŒ

Œ

ŒŒŒŒŒ

Œ

Œ

ŒŒŒŒŒ

Œ

ŒŒŒŒŒŒŒ

V

in

= V

IH

or V

IL

I

OH

= - 4 mA

I

OH

= - 8 mA

ŒŒŒŒ

Œ

ŒŒ

Œ

Œ

ŒŒ

Œ

ŒŒŒŒ

3.0

4.5

ŒŒŒ

ŒŒ

Œ

ŒŒ

Œ

ŒŒŒ

2.58

3.94

ŒŒŒ

Œ

Œ

Œ

Œ

Œ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

Œ

Œ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

Œ

Œ

Œ

ŒŒŒ

2.48

3.80

ŒŒŒ

Œ

Œ

Œ

Œ

Œ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

Œ

Œ

Œ

ŒŒŒ

2.40

3.70

ŒŒŒ

Œ

Œ

Œ

Œ

Œ

Œ

ŒŒŒ

ŒŒ

ŒŒ

ŒŒ

ŒŒ

ŒŒŒŒ

Œ

ŒŒ

Œ

ŒŒŒŒ

V

OL

ŒŒŒŒŒŒ

Œ

ŒŒŒŒ

Œ

ŒŒŒŒŒŒ

Low - Level

Output Voltage

ŒŒŒŒŒŒŒ

Œ

ŒŒŒŒŒ

Œ

ŒŒŒŒŒŒŒ

V

in

= V

IH

or V

IL

I

OL

= 50

m

A

ŒŒŒŒ

Œ

ŒŒ

Œ

ŒŒŒŒ

2.0

3.0

4.5

ŒŒŒ

ŒŒ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

0.0

0.0

0.0

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

0.1

0.1

0.1

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

0.1

0.1

0.1

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

0.1

0.1

0.1

ŒŒ

ŒŒ

ŒŒ

V

ŒŒŒŒ

Œ

ŒŒ

Œ

ŒŒŒŒ

ŒŒŒŒŒŒ

Œ

ŒŒŒŒ

Œ

ŒŒŒŒŒŒ

ŒŒŒŒŒŒŒ

Œ

ŒŒŒŒŒ

Œ

ŒŒŒŒŒŒŒ

V

in

= V

IH

or V

IL

I

OL

= 4 mA

I

OL

= 8 mA

ŒŒŒŒ

Œ

ŒŒ

Œ

ŒŒŒŒ

3.0

4.5

ŒŒŒ

ŒŒ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

0.36

0.36

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

0.44

0.44

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

0.55

0.55

ŒŒ

ŒŒ

ŒŒ

ŒŒŒŒ

Œ

ŒŒ

Œ

ŒŒŒŒ

I

in

ŒŒŒŒŒŒ

Œ

ŒŒŒŒ

Œ

ŒŒŒŒŒŒ

Input Leakage

Current

ŒŒŒŒŒŒŒ

Œ

ŒŒŒŒŒ

Œ

ŒŒŒŒŒŒŒ

V

in

= 5.5 V or GND

ŒŒŒŒ

Œ

ŒŒ

Œ

ŒŒŒŒ

0 to 5.5

ŒŒŒ

ŒŒ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

$

0.1

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

$

1.0

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

$

2.0

ŒŒ

ŒŒ

ŒŒ

m

A

ŒŒŒŒ

Œ

ŒŒ

Œ

ŒŒŒŒ

I

CC

ŒŒŒŒŒŒ

Œ

ŒŒŒŒ

Œ

ŒŒŒŒŒŒ

Quiescent Supply

Current

ŒŒŒŒŒŒŒ

Œ

ŒŒŒŒŒ

Œ

ŒŒŒŒŒŒŒ

V

in

= V

CC

or GND

ŒŒŒŒ

Œ

ŒŒ

Œ

ŒŒŒŒ

5.5

ŒŒŒ

ŒŒ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

2.0

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

20

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

40

ŒŒ

ŒŒ

ŒŒ

m

A

ŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒ

AC ELECTRICAL CHARACTERISTICS

(Input t

r

= t

f

= 3.0 ns)

ŒŒŒŒ

Œ

ŒŒ

Œ

ŒŒŒŒ

ŒŒŒŒŒŒ

Œ

ŒŒŒŒ

Œ

ŒŒŒŒŒŒ

ŒŒŒŒŒŒŒŒŒŒ

Œ

ŒŒŒŒŒŒŒŒ

Œ

ŒŒŒŒŒŒŒŒŒŒ

ŒŒŒŒŒŒŒ

Œ

ŒŒŒŒŒ

Œ

ŒŒŒŒŒŒŒ

T

A

= 25

∞

C

ŒŒŒŒŒ

Œ

ŒŒŒ

Œ

ŒŒŒŒŒ

T

A

= - 40 to

85

∞

C

ŒŒŒŒŒ

Œ

ŒŒŒ

Œ

ŒŒŒŒŒ

T

A

= - 55 to

+125

∞

C

ŒŒ

ŒŒ

ŒŒ

ŒŒŒŒ

ŒŒŒŒ

Symbol

ŒŒŒŒŒŒ

ŒŒŒŒŒŒ

Parameter

ŒŒŒŒŒŒŒŒŒŒ

ŒŒŒŒŒŒŒŒŒŒ

Test Conditions

ŒŒŒ

ŒŒŒ

Min

ŒŒŒ

ŒŒŒ

Typ

ŒŒŒ

ŒŒŒ

Max

ŒŒŒ

ŒŒŒ

Min

ŒŒŒ

ŒŒŒ

Max

ŒŒŒ

ŒŒŒ

Min

ŒŒŒ

ŒŒŒ

Max

ŒŒ

ŒŒ

Unit

ŒŒŒŒ

Œ

ŒŒ

Œ

ŒŒŒŒ

t

PLH

,

t

PHL

ŒŒŒŒŒŒ

Œ

ŒŒŒŒ

Œ

ŒŒŒŒŒŒ

Propagation

Delay, A or B to Y

ŒŒŒŒŒŒŒŒŒŒ

Œ

ŒŒŒŒŒŒŒŒ

Œ

ŒŒŒŒŒŒŒŒŒŒ

V

CC

= 3.3

±

0.3 V

C

L

= 15 pF

C

L

= 50 pF

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

5.5

8.0

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

7.9

11.4

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

1.0

1.0

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

9.5

13.0

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

1.0

1.0

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

10

14.5

ŒŒ

ŒŒ

ŒŒ

ns

ŒŒŒŒ

ŒŒŒŒ

ŒŒŒŒŒŒ

ŒŒŒŒŒŒ

ŒŒŒŒŒŒŒŒŒŒ

ŒŒŒŒŒŒŒŒŒŒ

V

CC

= 5.0

±

0.5 V

C

L

= 15 pF

C

L

= 50 pF

ŒŒŒ

ŒŒŒ

ŒŒŒ

ŒŒŒ

3.7

5.2

ŒŒŒ

ŒŒŒ

5.5

7.5

ŒŒŒ

ŒŒŒ

1.0

1.0

ŒŒŒ

ŒŒŒ

6.5

8.5

ŒŒŒ

ŒŒŒ

1.0

1.0

ŒŒŒ

ŒŒŒ

7.0

9.5

ŒŒ

ŒŒ

ŒŒŒŒ

Œ

ŒŒ

Œ

ŒŒŒŒ

C

in

ŒŒŒŒŒŒ

Œ

ŒŒŒŒ

Œ

ŒŒŒŒŒŒ

Input

Capacitance

ŒŒŒŒŒŒŒŒŒŒ

Œ

ŒŒŒŒŒŒŒŒ

Œ

ŒŒŒŒŒŒŒŒŒŒ

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

4.0

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

10

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

10

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

ŒŒŒ

Œ

Œ

Œ

ŒŒŒ

10

ŒŒ

ŒŒ

ŒŒ

pF

Typical @ 25

∞

C, V

CC

= 5.0 V

C

PD

Power Dissipation Capacitance (Note 6)

19

pF

6. C

PD

is defined as the value of the internal equivalent capacitance which is calculated from the operating current consumption without load.

Average operating current can be obtained by the equation: I

CC(OPR

)

= C

PD

V

CC

f

in

+ I

CC

/ 4 (per gate). C

PD

is used to determine the

no - load dynamic power consumption; P

D

= C

PD

V

CC

2

f

in

+ I

CC

V

CC

.

NOISE CHARACTERISTICS

(Input t

r

= t

f

= 3.0 ns, C

L

= 50 pF, V

CC

= 5.0 V, Measured in SOIC Package)

T

A

= 25

∞

C

Symbol

Characteristic

Typ

Max

Unit

V

OLP

Quiet Output Maximum Dynamic V

OL

0.3

0.8

V

V

OLV

Quiet Output Minimum Dynamic V

OL

- 0.3

- 0.8

V

V

IHD

Minimum High Level Dynamic Input Voltage

3.5

V

V

ILD

Maximum Low Level Dynamic Input Voltage

1.5

V

MC74VHC00

http://onsemi.com

4

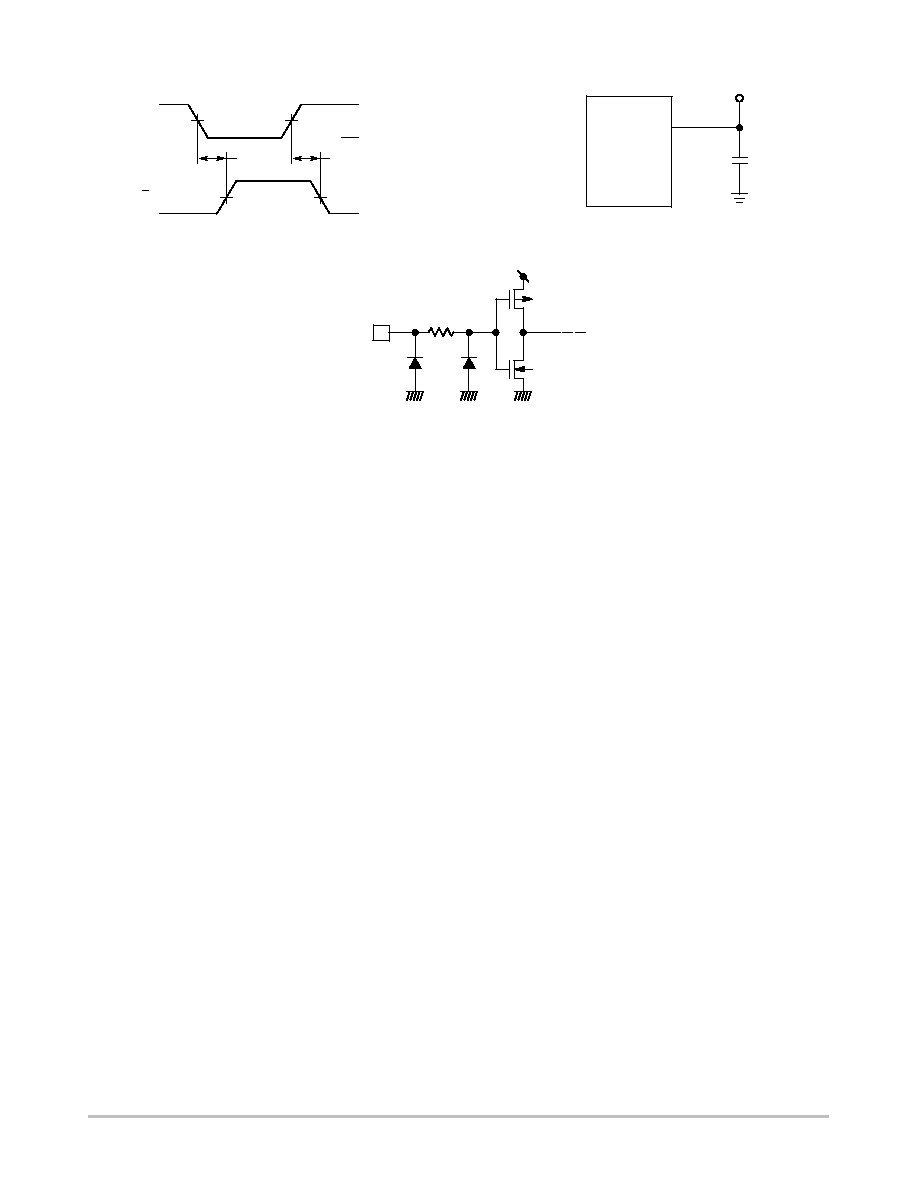

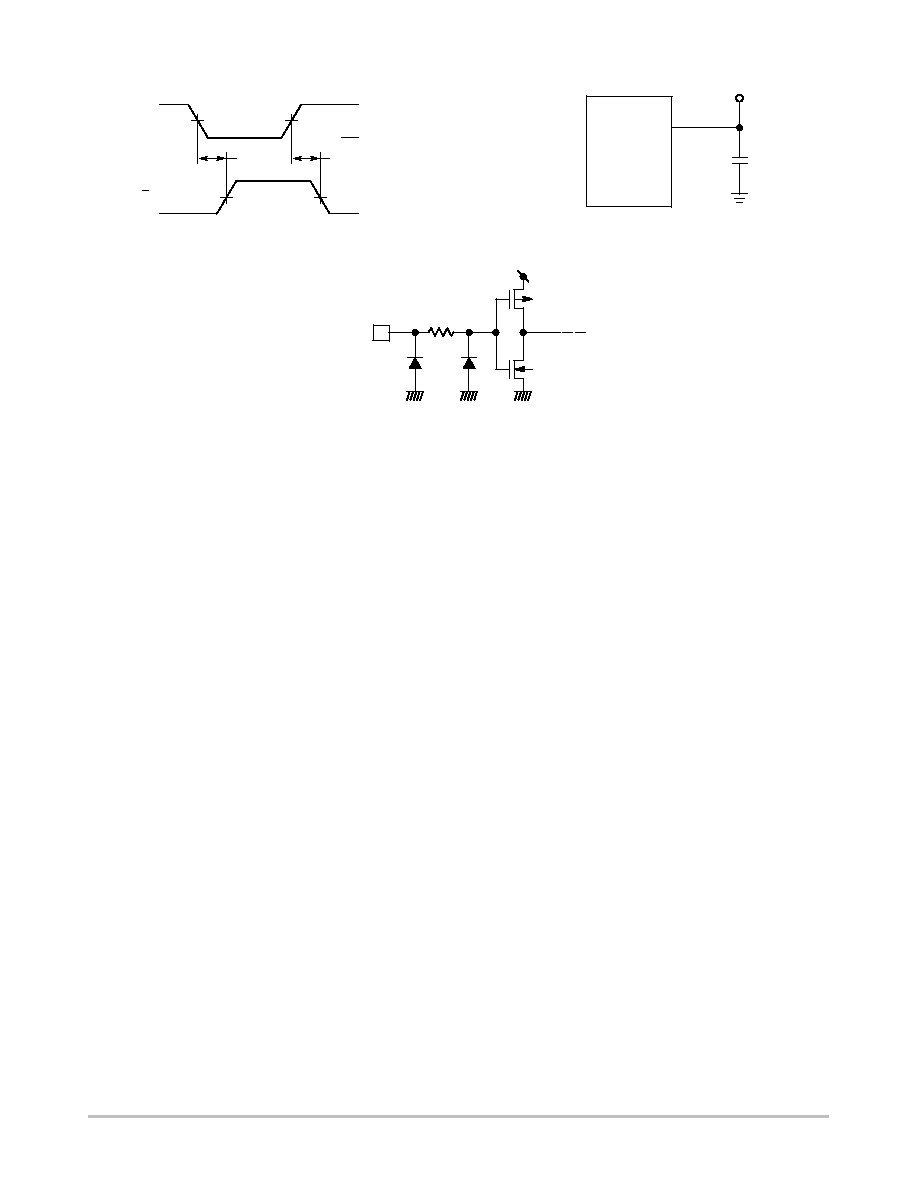

Figure 3. Switching Waveforms

V

CC

GND

50%

50% V

CC

A or B

Y

t

PHL

t

PLH

*Includes all probe and jig capacitance

Figure 4. Test Circuit

C

L

*

TEST POINT

DEVICE

UNDER

TEST

OUTPUT

Figure 5. Input Equivalent Circuit

INPUT

MC74VHC00

http://onsemi.com

5

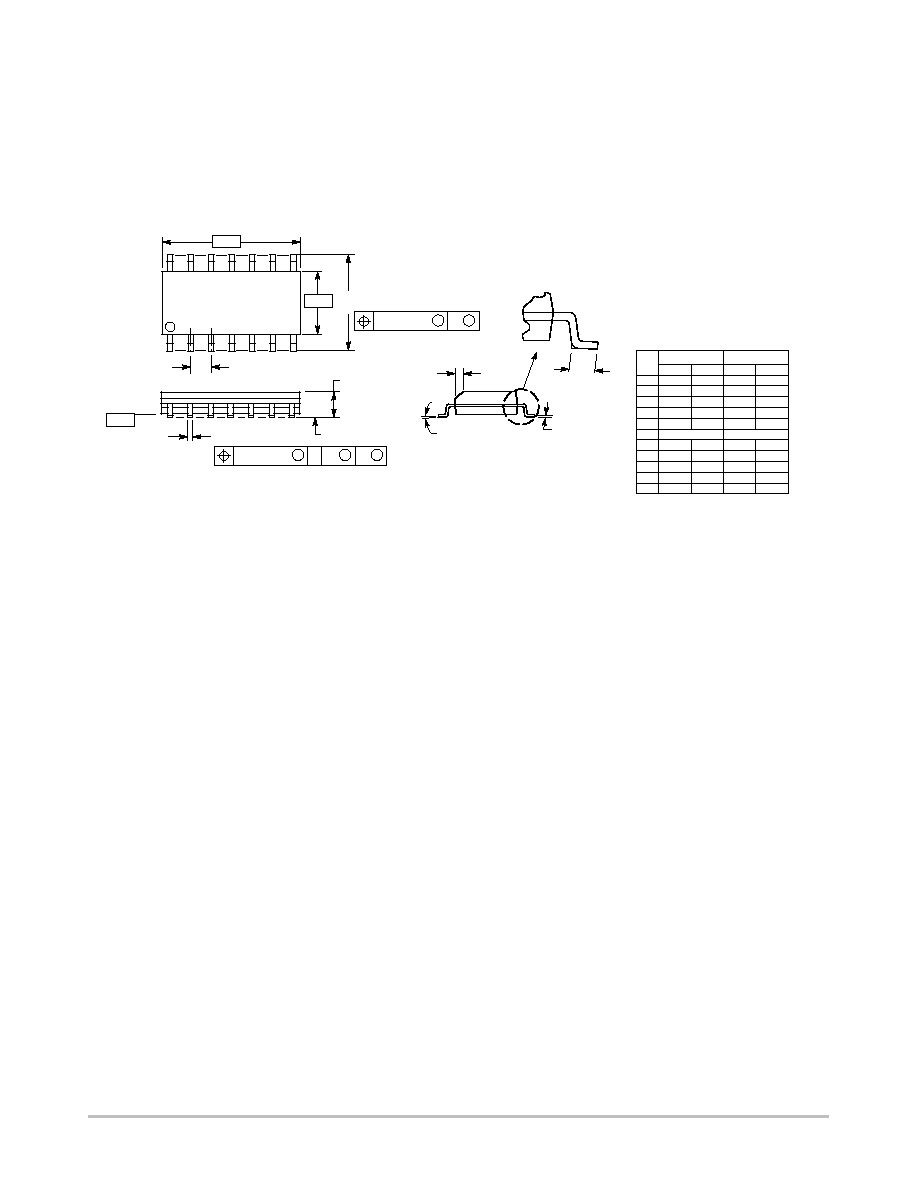

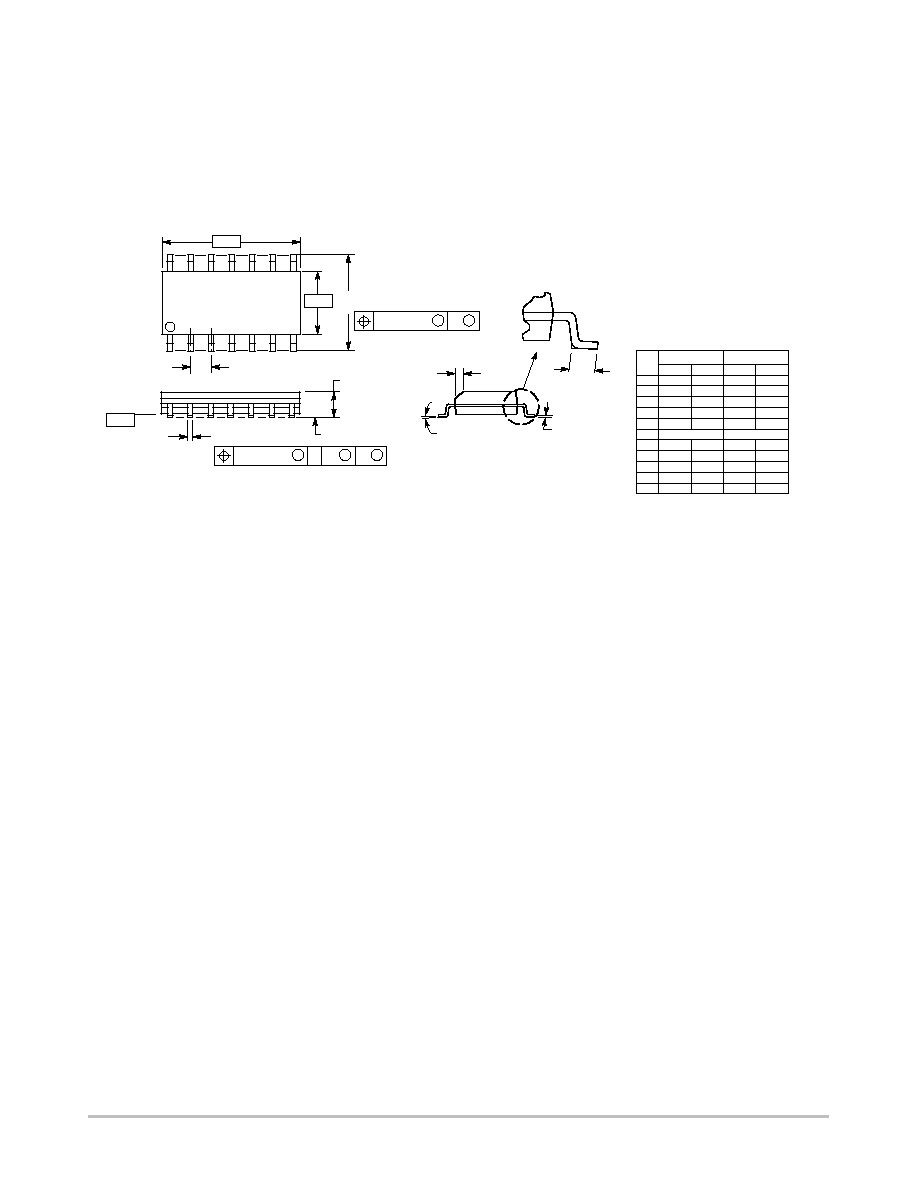

PACKAGE DIMENSIONS

NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSIONS A AND B DO NOT INCLUDE

MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 (0.006)

PER SIDE.

5. DIMENSION D DOES NOT INCLUDE DAMBAR

PROTRUSION. ALLOWABLE DAMBAR

PROTRUSION SHALL BE 0.127 (0.005) TOTAL

IN EXCESS OF THE D DIMENSION AT

MAXIMUM MATERIAL CONDITION.

- A -

- B -

G

P

7 PL

14

8

7

1

M

0.25 (0.010)

B

M

S

B

M

0.25 (0.010)

A

S

T

- T -

F

R

X 45

SEATING

PLANE

D

14 PL

K

C

J

M

_

DIM

MIN

MAX

MIN

MAX

INCHES

MILLIMETERS

A

8.55

8.75

0.337

0.344

B

3.80

4.00

0.150

0.157

C

1.35

1.75

0.054

0.068

D

0.35

0.49

0.014

0.019

F

0.40

1.25

0.016

0.049

G

1.27 BSC

0.050 BSC

J

0.19

0.25

0.008

0.009

K

0.10

0.25

0.004

0.009

M

0

7

0

7

P

5.80

6.20

0.228

0.244

R

0.25

0.50

0.010

0.019

_

_

_

_

SOIC - 14

D SUFFIX

CASE 751A - 03

ISSUE F