| ÐлекÑÑоннÑй компоненÑ: HEF4035B | СкаÑаÑÑ:  PDF PDF  ZIP ZIP |

Äîêóìåíòàöèÿ è îïèñàíèÿ www.docs.chipfind.ru

DATA SHEET

Product specification

File under Integrated Circuits, IC04

January 1995

INTEGRATED CIRCUITS

HEF4035B

MSI

4-bit universal shift register

For a complete data sheet, please also download:

·

The IC04 LOCMOS HE4000B Logic

Family Specifications HEF, HEC

·

The IC04 LOCMOS HE4000B Logic

Package Outlines/Information HEF, HEC

January 1995

2

Philips Semiconductors

Product specification

4-bit universal shift register

HEF4035B

MSI

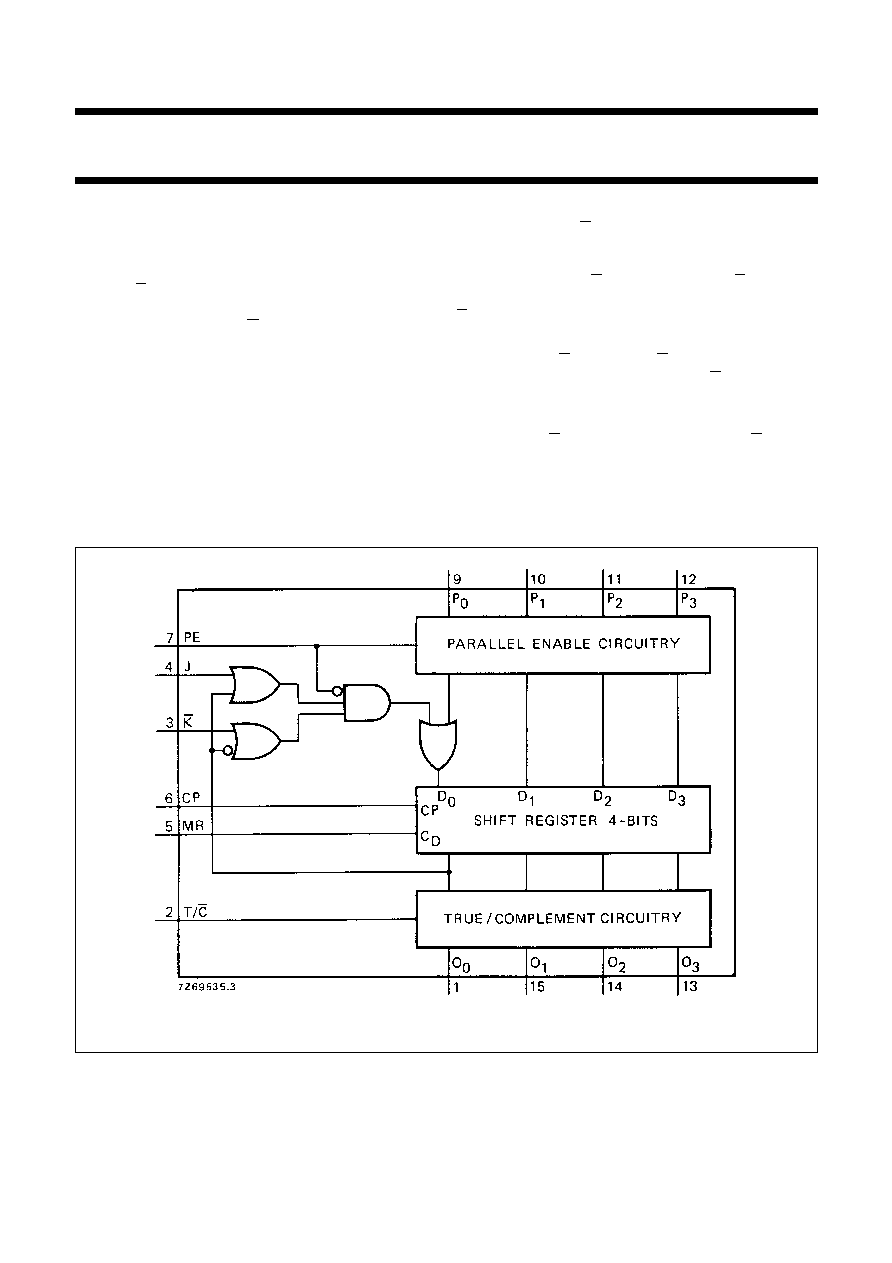

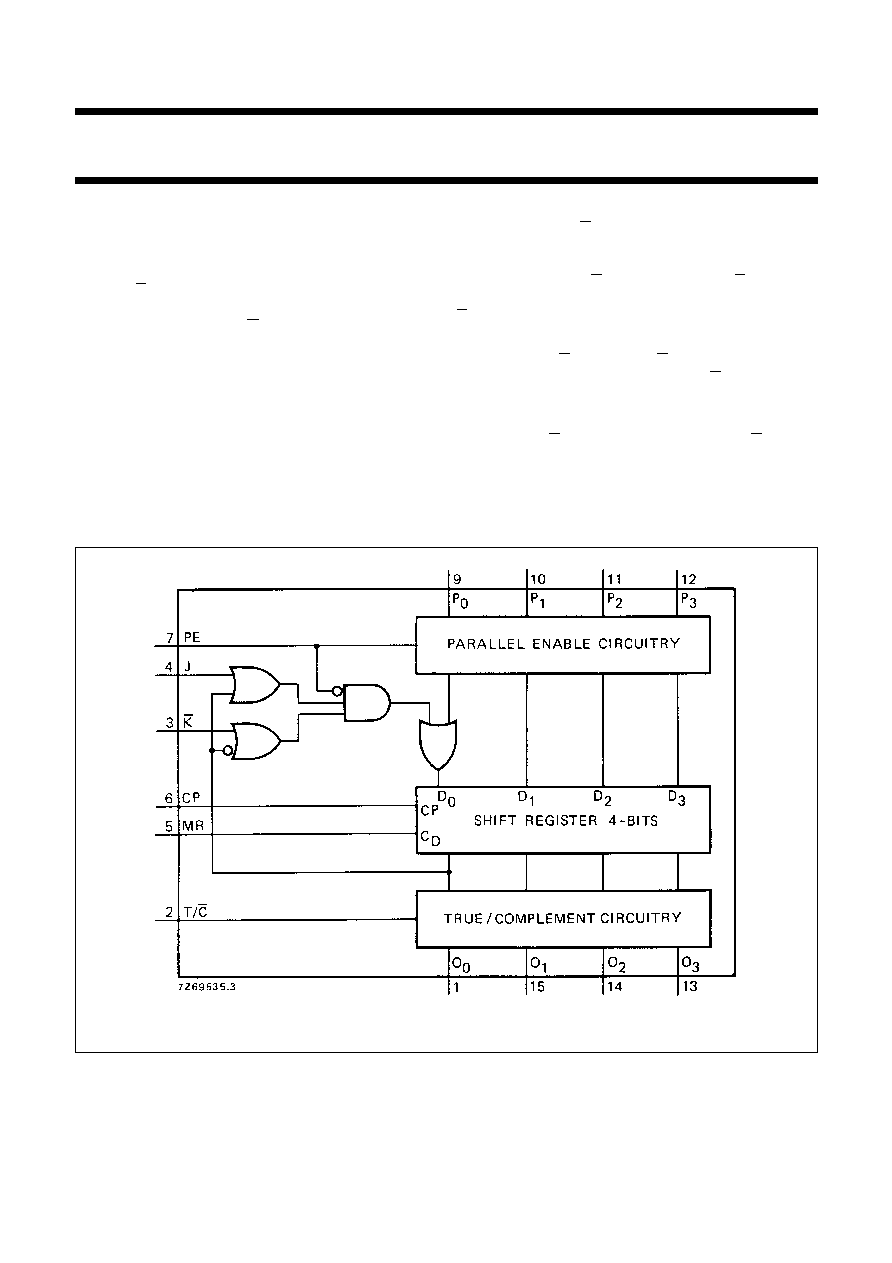

DESCRIPTION

The HEF4035B is a fully synchronous edge-triggered 4-bit

shift register with a clock input (CP), four synchronous

parallel data inputs (P

0

to P

3

), two synchronous serial data

inputs (J, K), a synchronous parallel enable input (PE),

buffered parallel outputs from all 4-bit positions (O

0

to O

3

),

a true/complement input (T/C) and an overriding

asynchronous master reset input (MR). Each register is of

a D-type master-slave flip-flop.

Operation is synchronous (except for MR) and is

edge-triggered on the LOW to HIGH transition of the CP

input. When PE is HIGH, data is loaded into the register

from P

0

to P

3

on the LOW to HIGH transition of CP.

When PE is LOW, data is shifted into the first register

position from J and K and all the data in the register is

shifted one position to the right on the LOW to HIGH

transition of CP. D-type entry is obtained by

interconnecting J and K. When J = HIGH and K = LOW the

first stage is in the toggle mode. When J = LOW and

K = HIGH the first stage is in the hold mode.

The outputs (O

0

to O

3

) are either inverting or non-inverting,

depending on T/C state. With T/C HIGH, O

0

to O

3

are

non-inverting (active HIGH) and when T/C is LOW, O

0

to

O

3

are inverting (active LOW).

A HIGH on MR resets all four bit positions (O

0

to

O

3

= LOW if T/C = HIGH, O

0

to O

3

= HIGH if T/C = LOW)

independent of all other input conditions.

Schmitt-trigger action in the clock input makes the circuit

highly tolerant to slower clock rise and fall times.

FAMILY DATA, I

DD

LIMITS category MSI

See Family Specifications

Fig.1 Functional diagram.

January 1995

3

Philips Semiconductors

Product specification

4-bit universal shift register

HEF4035B

MSI

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

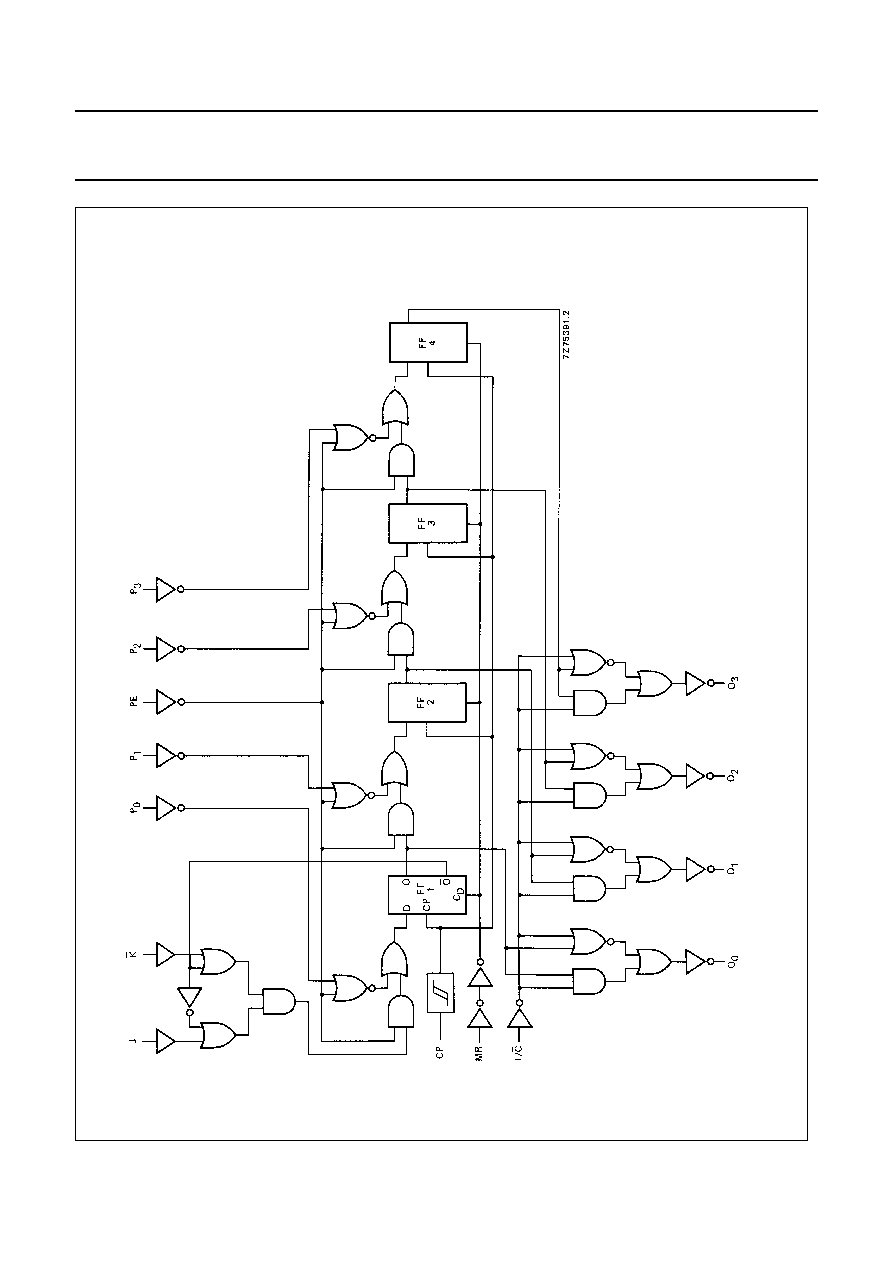

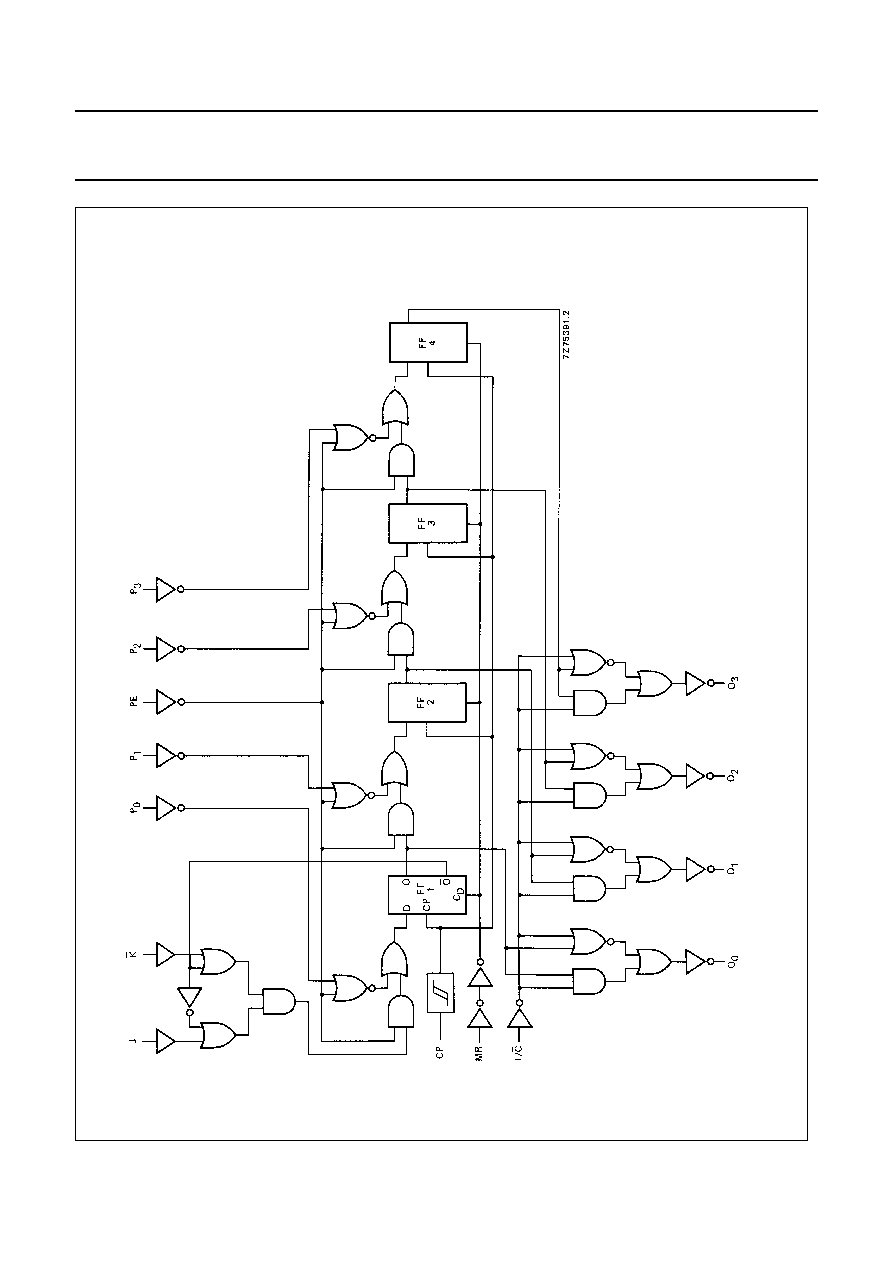

Fig.2 Logic diagram.

January 1995

4

Philips Semiconductors

Product specification

4-bit universal shift register

HEF4035B

MSI

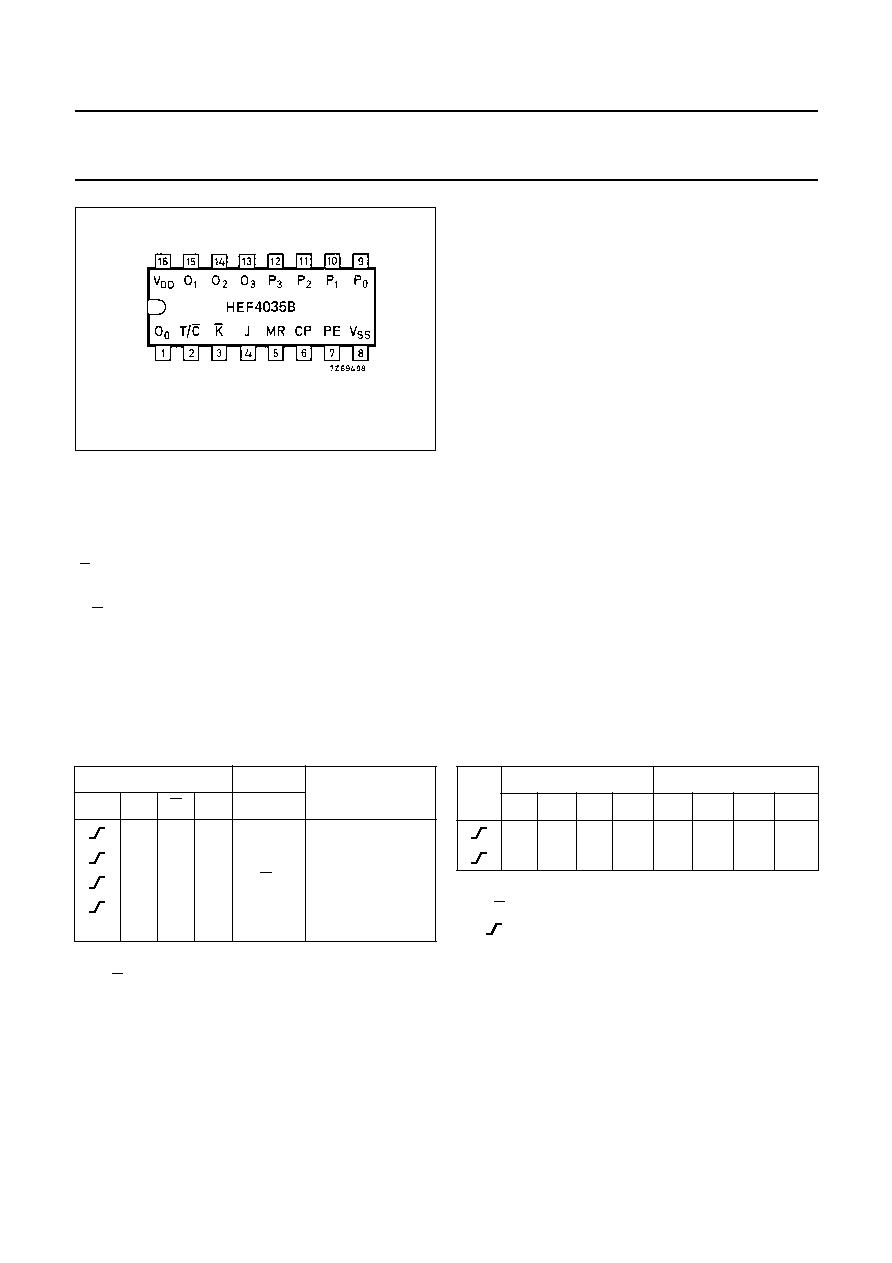

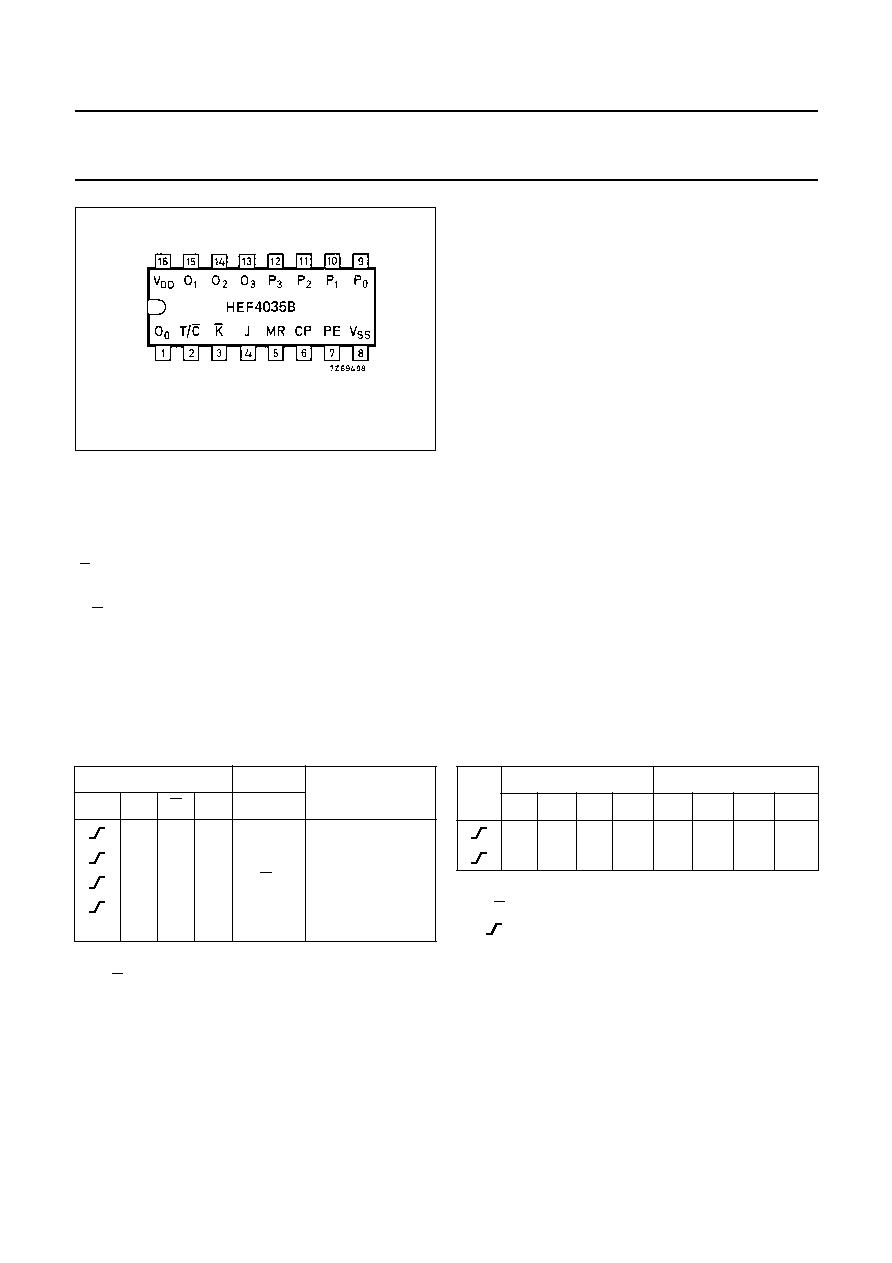

Fig.3 Pinning diagram.

HEF4035BP(N):

16-lead DIL; plastic

(SOT38-1)

HEF4035BD(F):

16-lead DIL; ceramic (cerdip)

(SOT74)

HEF4035BT(D):

16-lead SO; plastic

(SOT109-1)

( ): Package Designator North America

PINNING

PE

parallel enable input

P

0

to P

3

parallel data inputs

J

first stage J-input (active HIGH)

K

first stage K-input (active LOW)

CP

clock input (LOW to HIGH edge-triggered)

T/C

true/complement input

MR

master reset input

O

0

to O

3

buffered parallel outputs

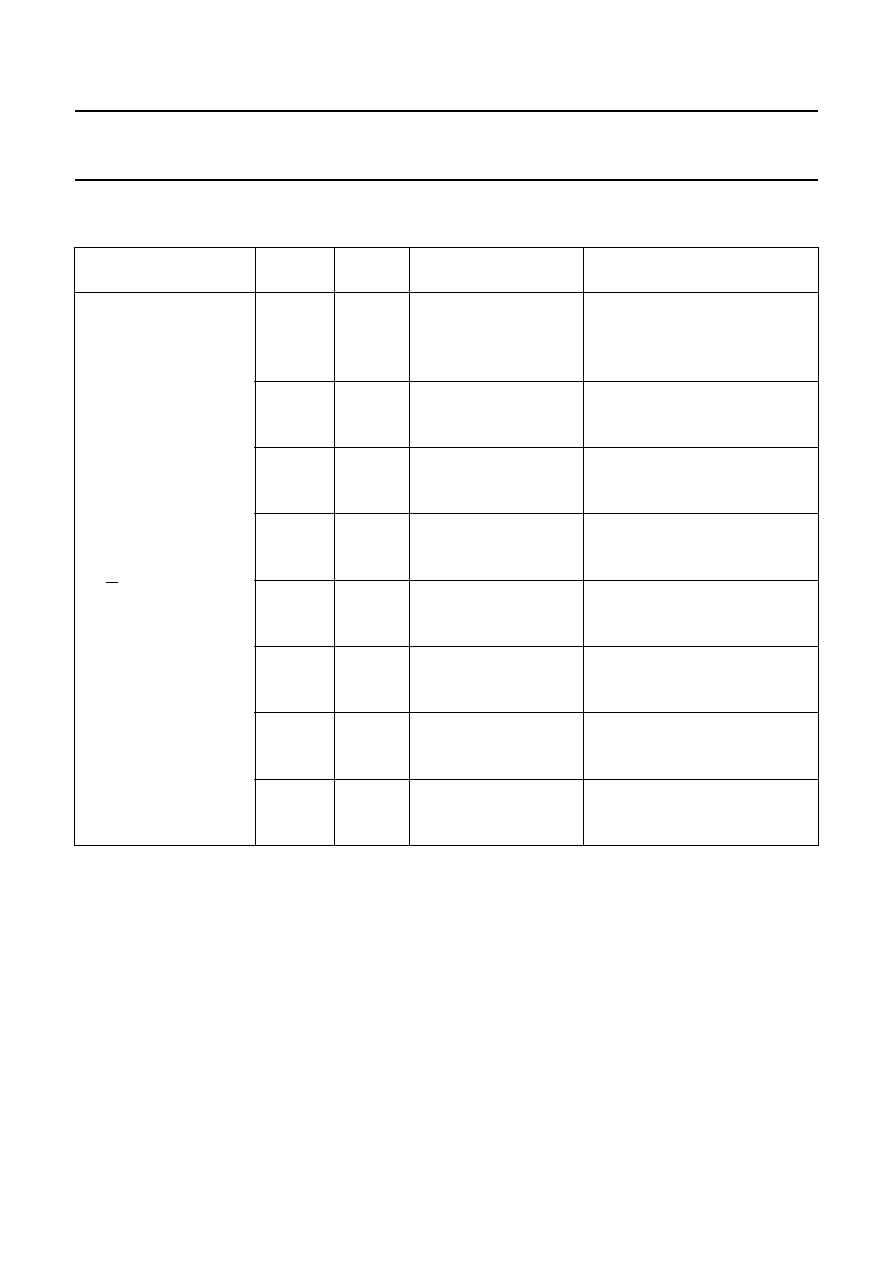

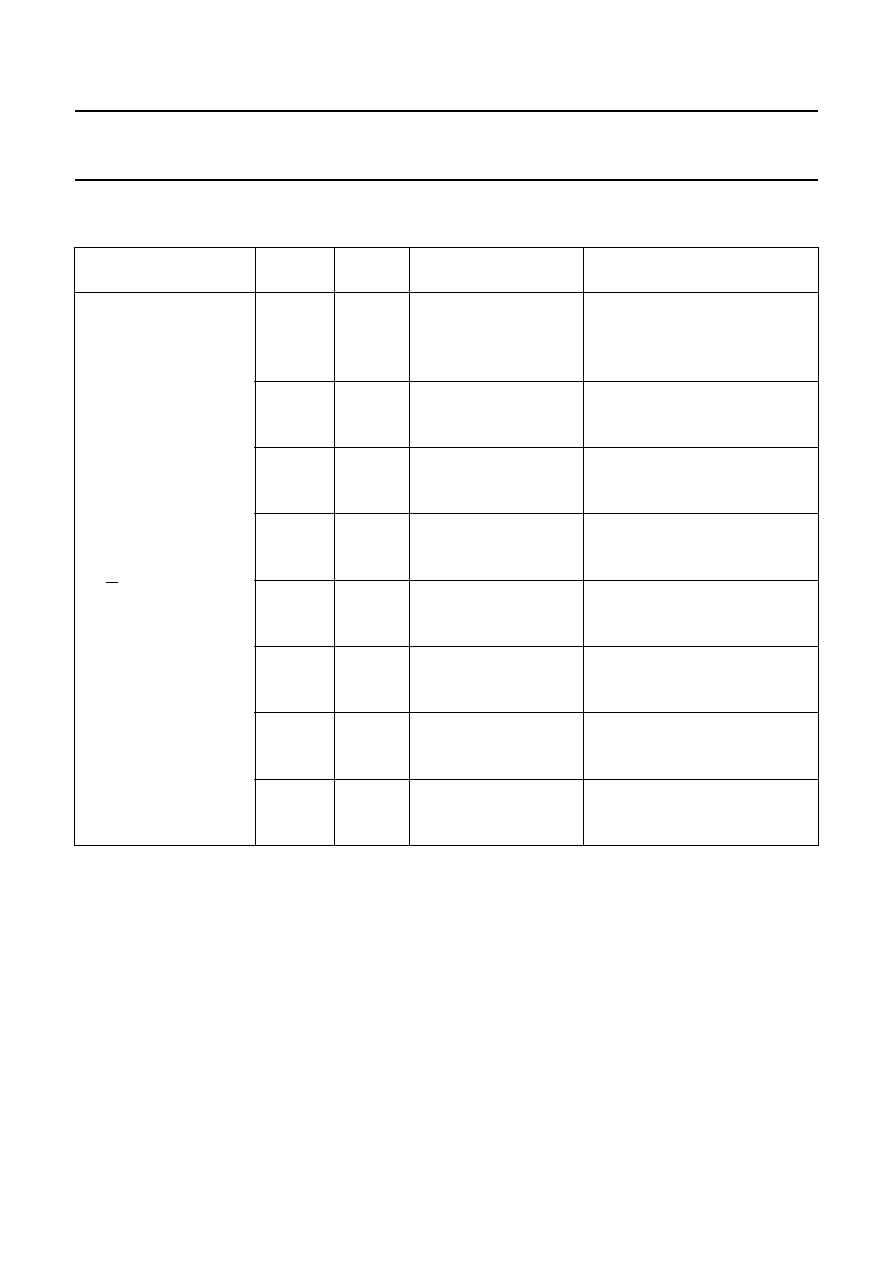

FUNCTION TABLES

Serial operation first stage

Note

1. T/C = HIGH; PE = LOW

INPUTS

OUTPUT

MODE OF

OPERATION

CP

J

K

MR

O

0 + 1

H

H

L

H

D flip-flop

L

L

L

L

D flip-flop

H

L

L

O

0

toggle

L

H

L

O

0

no change

X

X

X

H

L

reset

Parallel operation

Notes

1. T/C = HIGH; PE = HIGH; MR = LOW

= positive-going transition

H = HIGH state (the more positive voltage)

L = LOW state (the less positive voltage)

X = state is immaterial

CP

INPUTS

OUTPUTS

P

0

P

1

P

2

P

3

O

0

O

1

O

2

O

3

H

H

H

H

H

H

H

H

L

L

L

L

L

L

L

L

January 1995

5

Philips Semiconductors

Product specification

4-bit universal shift register

HEF4035B

MSI

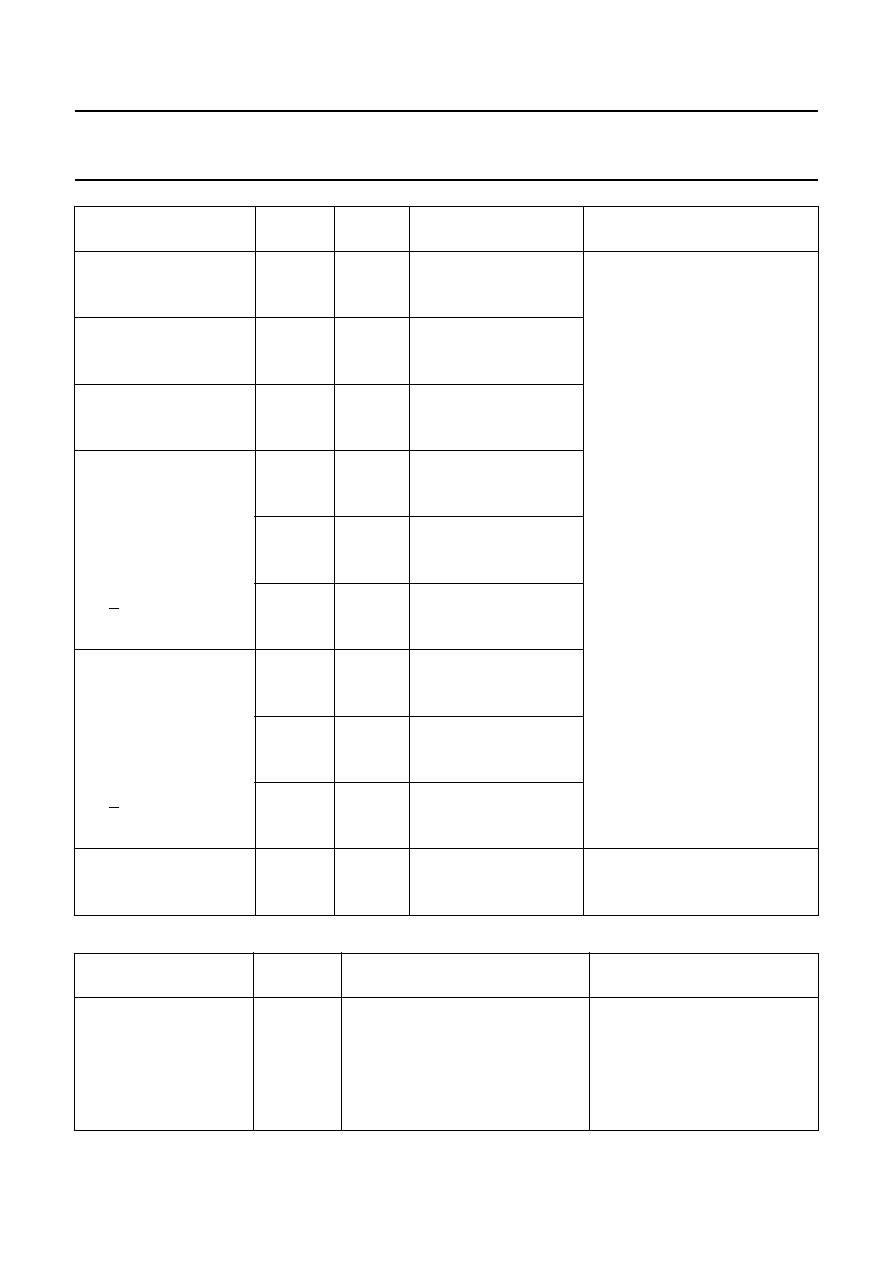

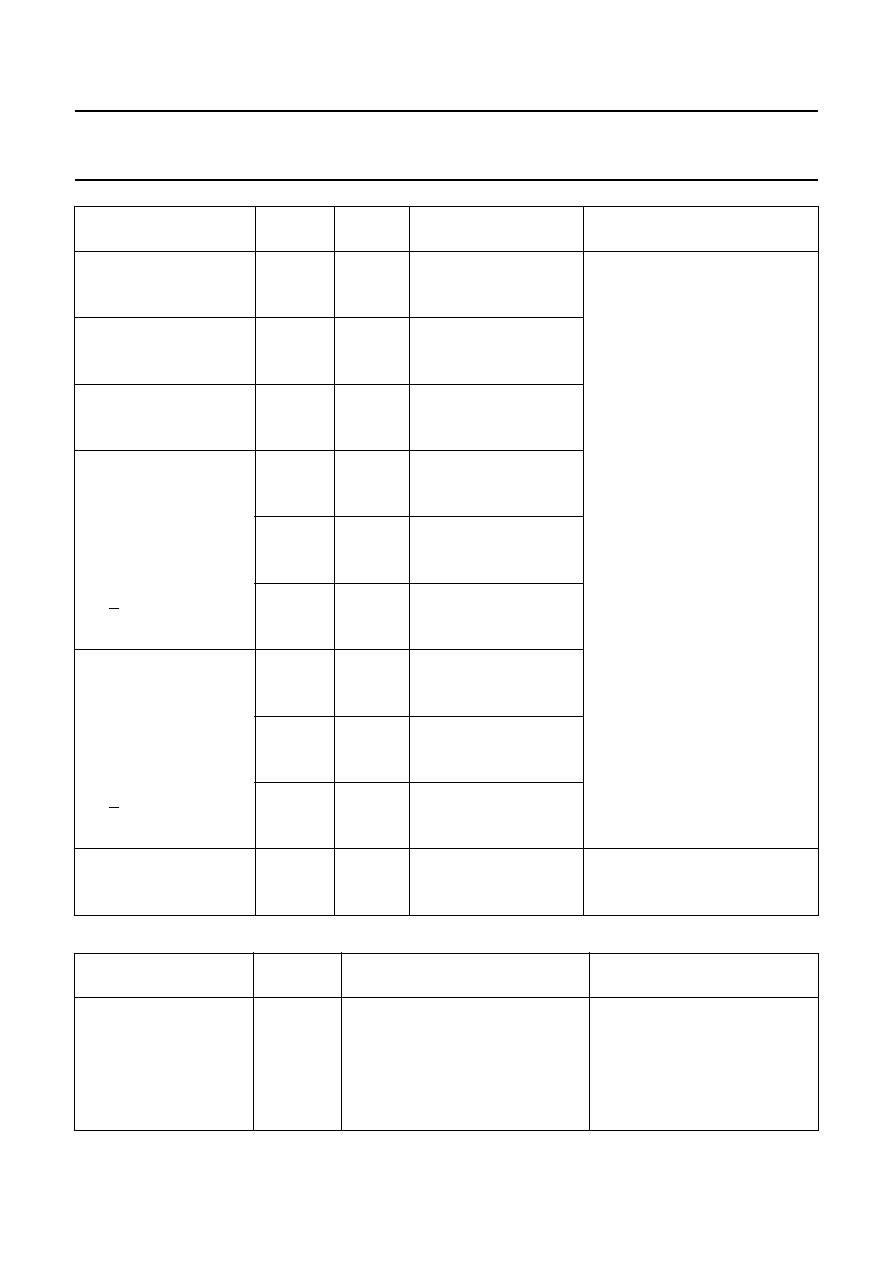

AC CHARACTERISTICS

V

SS

= 0 V; T

amb

= 25

°

C; C

L

= 50 pF; input transition times

20 ns

V

DD

V

SYMBOL MIN.

TYP.

MAX.

TYPICAL EXTRAPOLATION

FORMULA

Propagation delays

CP

O

n

5

170

340

ns

143 ns

+

(0,55 ns/pF) C

L

HIGH to LOW

10

t

PHL

70

140

ns

59 ns

+

(0,23 ns/pF) C

L

15

50

100

ns

42 ns

+

(0,16 ns/pF) C

L

5

150

300

ns

123 ns

+

(0,55 ns/pF) C

L

LOW to HIGH

10

t

PLH

65

130

ns

54 ns

+

(0,23 ns/pF) C

L

15

50

100

ns

42 ns

+

(0,16 ns/pF) C

L

MR

O

n

5

115

230

ns

88 ns

+

(0,55 ns/pF) C

L

HIGH to LOW

10

t

PHL

50

100

ns

39 ns

+

(0,23 ns/pF) C

L

15

40

80

ns

32 ns

+

(0,16 ns/pF) C

L

5

115

230

ns

88 ns

+

(0,55 ns/pF) C

L

LOW to HIGH

10

t

PLH

50

100

ns

39 ns

+

(0,23 ns/pF) C

L

15

40

80

ns

32 ns

+

(0,16 ns/pF) C

L

T/C

O

n

5

105

210

ns

78 ns

+

(0,55 ns/pF) C

L

HIGH to LOW

10

t

PHL

50

100

ns

39 ns

+

(0,23 ns/pF) C

L

15

35

70

ns

27 ns

+

(0,16 ns/pF) C

L

5

85

170

ns

58 ns

+

(0,55 ns/pF) C

L

LOW to HIGH

10

t

PLH

45

90

ns

34 ns

+

(0,23 ns/pF) C

L

15

35

70

ns

27 ns

+

(0,16 ns/pF) C

L

Output transition times

5

60

120

ns

10 ns

+

(1,0 ns/pF) C

L

HIGH to LOW

10

t

THL

30

60

ns

9 ns

+

(0,42 ns/pF) C

L

15

20

40

ns

6 ns

+

(0,28 ns/pF) C

L

5

60

120

ns

10 ns

+

(1,0 ns/pF) C

L

LOW to HIGH

10

t

TLH

30

60

ns

9 ns

+

(0,42 ns/pF) C

L

15

20

40

ns

6 ns

+

(0,28 ns/pF) C

L

January 1995

6

Philips Semiconductors

Product specification

4-bit universal shift register

HEF4035B

MSI

Minimum clock

5

80

40

ns

see also waveforms Figs 4

and 5

pulse width; LOW

10

t

WCPL

40

20

ns

15

30

15

ns

Minimum MR

5

50

25

ns

pulse width; HIGH

10

t

WMRH

30

15

ns

15

20

10

ns

Recovery time

5

50

20

ns

for MR

10

t

RMR

40

15

ns

15

25

10

ns

Set-up times

5

40

5

ns

P

n

CP

10

t

su

25

0

ns

15

15

0

ns

5

50

25

ns

PE

CP

10

t

su

35

15

ns

15

30

10

ns

5

55

40

ns

J, K

CP

10

t

su

35

15

ns

15

25

10

ns

Hold times

5

25

10

ns

P

n

CP

10

t

hold

20

10

ns

15

20

10

ns

5

15

-

5

ns

PE

CP

10

t

hold

10

-

5

ns

15

5

-

5

ns

5

10

-

5

ns

J, K

CP

10

t

hold

10

0

ns

15

10

0

ns

Maximum clock

5

5

10

MHz

pulse frequency

10

f

max

12

25

MHz

15

15

30

MHz

V

DD

V

TYPICAL FORMULA FOR P (

µ

W)

Dynamic power

5

1 000 f

i

+

(f

o

C

L

)

×

V

DD

2

where

dissipation per

10

6 000 f

i

+

(f

o

C

L

)

×

V

DD

2

f

i

= input freq. (MHz)

package (P)

15

20 000 f

i

+

(f

o

C

L

)

×

V

DD

2

f

o

= output freq. (MHz)

C

L

= load cap. (pF)

(f

o

C

L

) = sum of outputs

V

DD

= supply voltage (V)

V

DD

V

SYMBOL MIN.

TYP.

MAX.

TYPICAL EXTRAPOLATION

FORMULA

January 1995

7

Philips Semiconductors

Product specification

4-bit universal shift register

HEF4035B

MSI

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

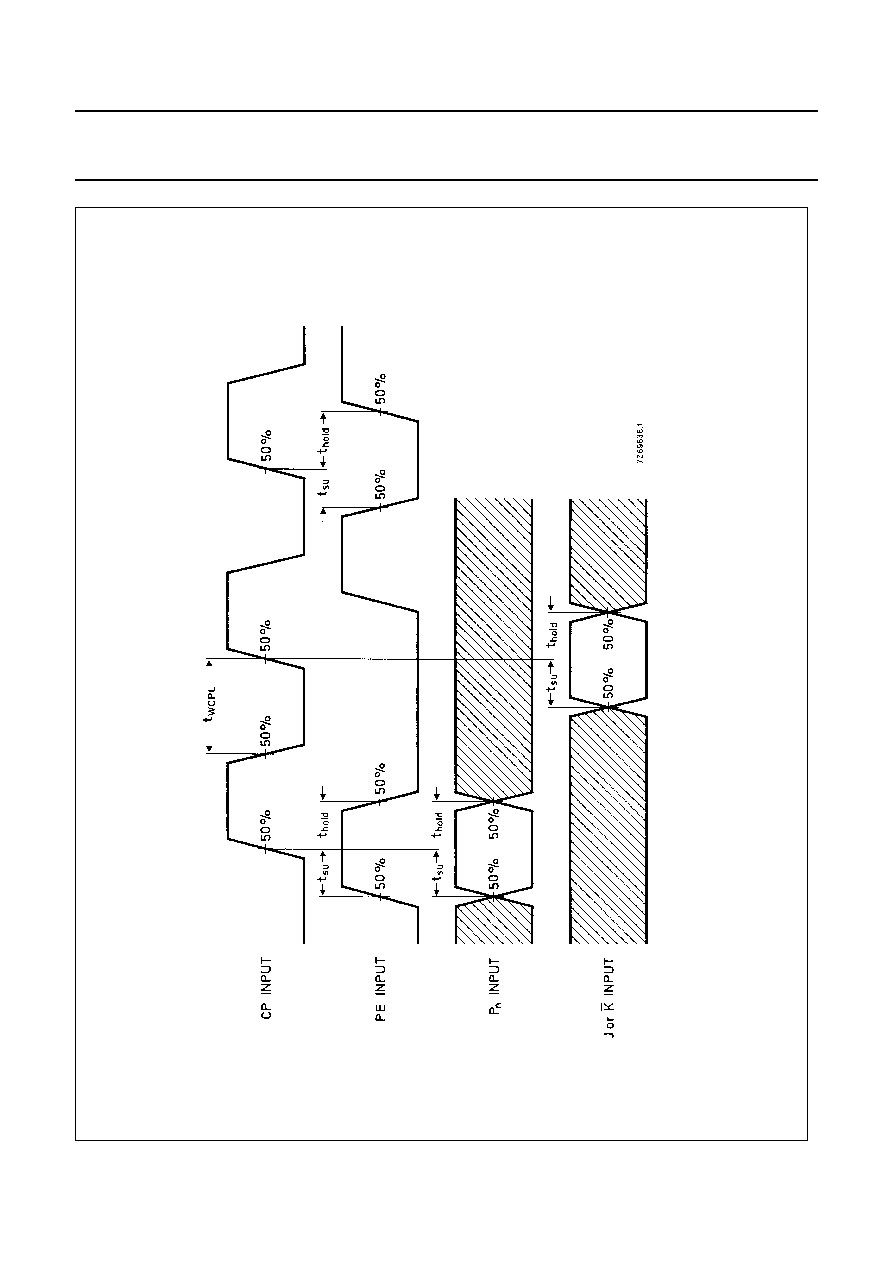

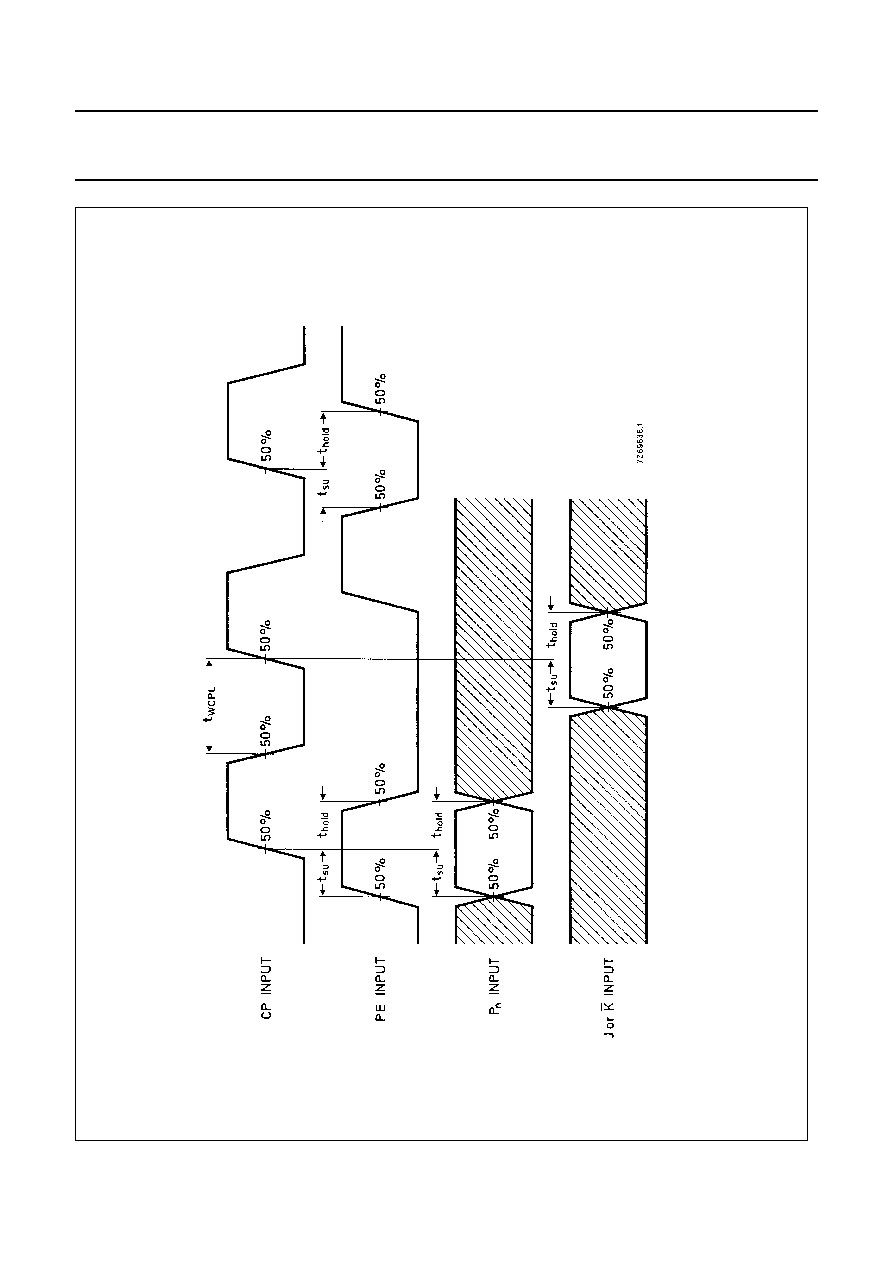

Fig.4

Waveforms showing minimum clock pulse width, set-up times, hold times. Set-up times and hold times are shown as positive values but

may be specified as negative values.

January 1995

8

Philips Semiconductors

Product specification

4-bit universal shift register

HEF4035B

MSI

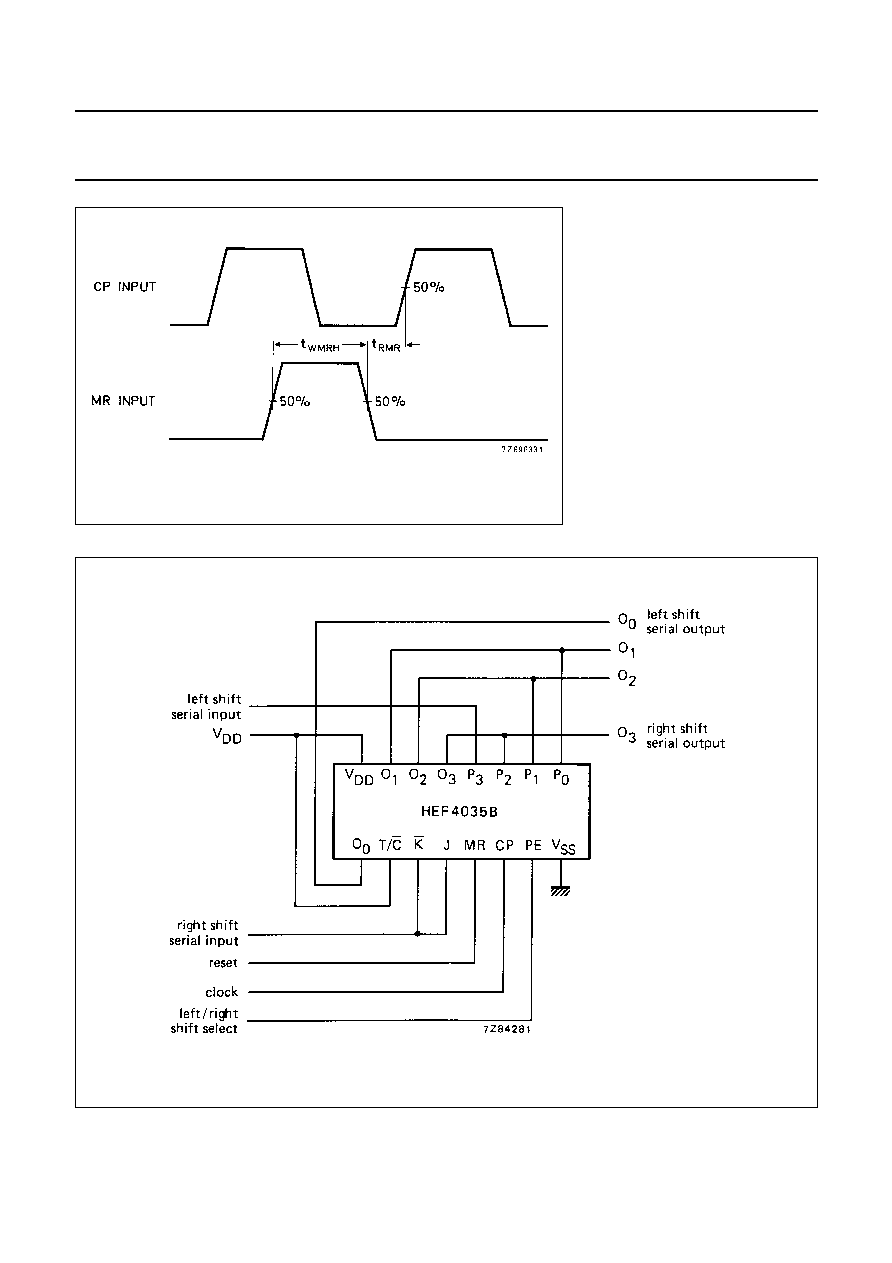

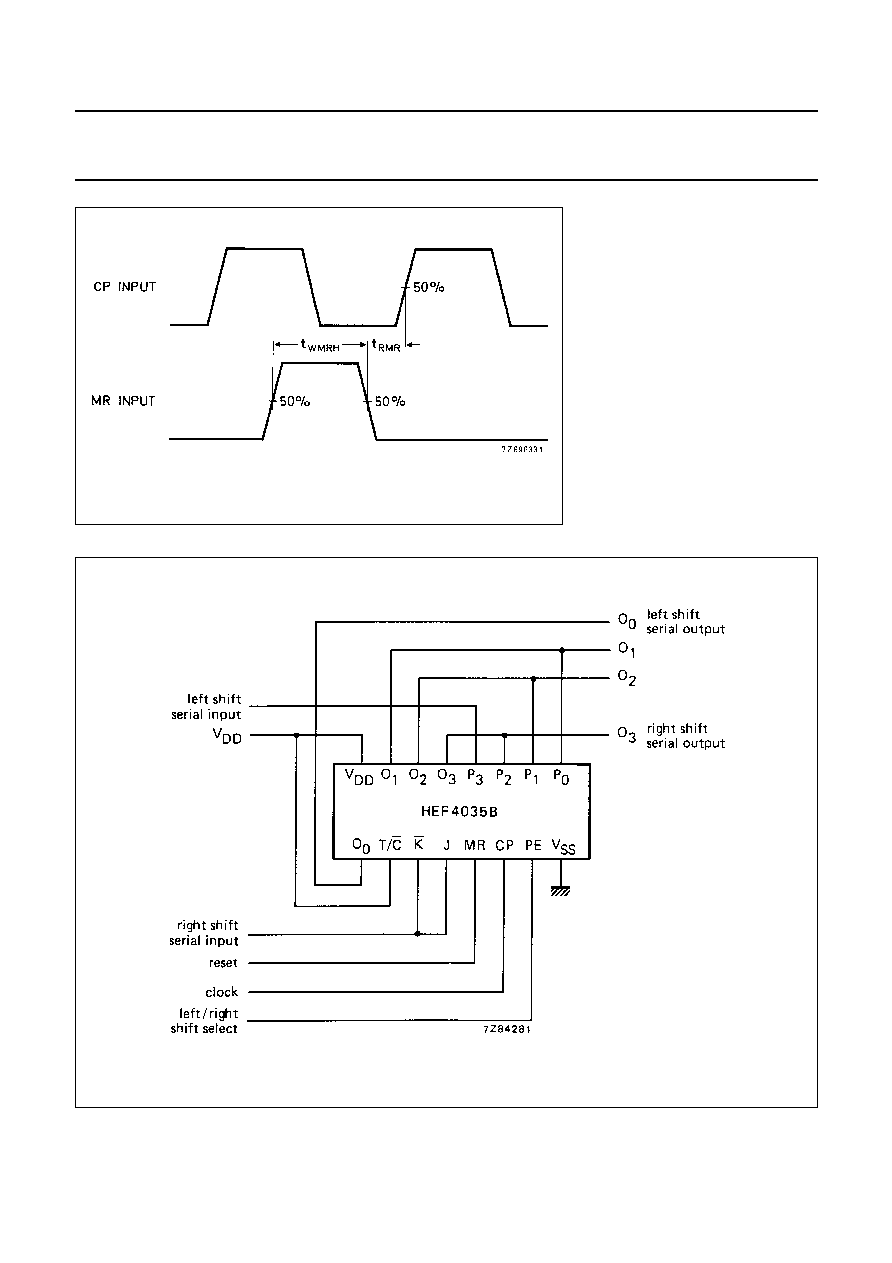

Fig.5

Waveforms showing minimum MR pulse width and MR recovery

time.

APPLICATION INFORMATION

Some examples of applications for

the HEF4035B are:

·

Counters, registers, arithmetic-unit

registers, shift-left/shift-right

registers.

·

Serial-to-parallel/parallel-to-serial

conversions.

·

Sequence generation.

·

Control circuits.

·

Code conversion.

Fig.6 Shift-left/shift-right register.

Document Outline

- DESCRIPTION

- FAMILY DATA, IDD LIMITS category MSI

- PINNING

- FUNCTION TABLES

- Serial operation first stage

- Parallel operation

- AC CHARACTERISTICS

- APPLICATION INFORMATION