PSMN005-30K

TrenchMOSTM logic level FET

Rev. 01 -- 6 March 2002

Product data

1.

Description

SiliconMAXTM products use the latest Philips TrenchMOSTM technology to achieve

the lowest possible on-state resistance in a SOT96-1 (SO8) package.

Product availability:

PSMN005-30K in SOT96-1 (SO8).

2.

Features

s

Very low on-state resistance

s

Fast switching

s

TrenchMOSTM technology.

3.

Applications

s

DC to DC convertors

s

Computer motherboards

s

Switch mode power supplies.

4.

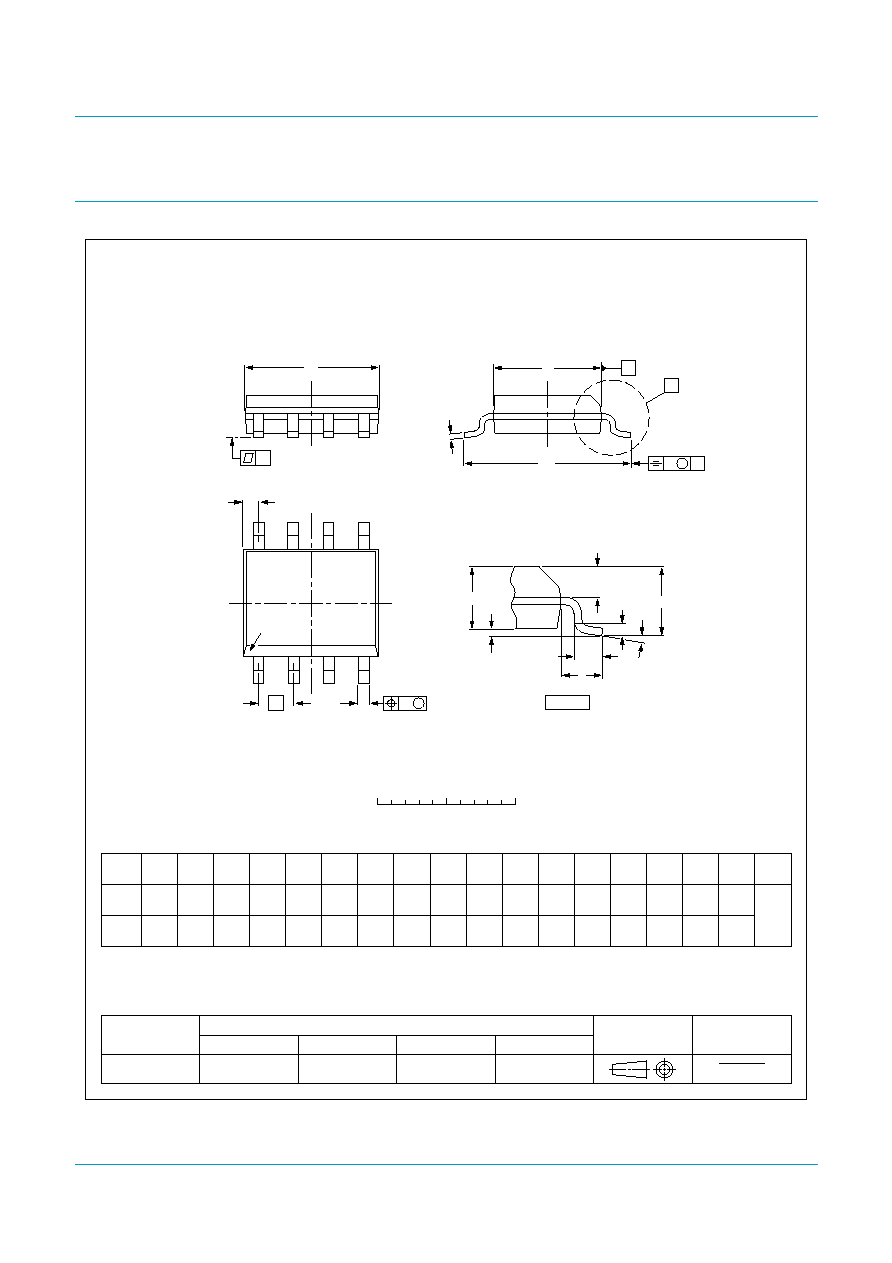

Pinning information

Table 1:

Pinning - SOT96-1, simplified outline and symbol

Pin

Description

Simplified outline

Symbol

1,2,3

source (s)

SOT96-1 (SO8)

4

gate (g)

5,6,7,8

drain (d)

4

5

1

8

Top view

MBK187

s

d

g

MBB076

Philips Semiconductors

PSMN005-30K

TrenchMOSTM logic level FET

Product data

Rev. 01 -- 6 March 2002

2 of 12

9397 750 09334

� Koninklijke Philips Electronics N.V. 2002. All rights reserved.

5.

Quick reference data

6.

Limiting values

Table 2:

Quick reference data

Symbol Parameter

Conditions

Typ

Max

Unit

V

DS

drain-source voltage (DC)

T

j

= 25 to 150

�

C

-

30

V

I

D

drain current (DC)

T

sp

= 80

�

C

-

20

A

P

tot

total power dissipation

T

sp

= 80

�

C

-

3.5

W

T

j

junction temperature

-

150

�

C

R

DSon

drain-source on-state resistance

V

GS

= 10 V; I

D

= 15 A; T

j

= 25

�

C

4.4

5.5

m

Table 3:

Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

Symbol Parameter

Conditions

Min

Max

Unit

V

DS

drain-source voltage (DC)

T

j

= 25 to 150

�

C

-

30

V

V

GS

gate-source voltage (DC)

-

�

20

V

I

D

drain current (DC)

T

sp

= 80

�

C; V

GS

= 10V

-

20

A

I

DM

peak drain current

T

sp

= 25

�

C; pulsed; t

p

10

�

s

-

60

A

P

tot

total power dissipation

T

sp

= 80

�

C

-

3.5

W

T

stg

storage temperature

-

55

+150

�

C

T

j

operating junction temperature

-

55

+150

�

C

Source-drain diode

I

S

source (diode forward) current (DC)

T

sp

= 80

�

C

-

20

A

I

SM

peak source (diode forward) current T

sp

= 25

�

C; pulsed; t

p

10

�

s

-

60

A

Philips Semiconductors

PSMN005-30K

TrenchMOSTM logic level FET

Product data

Rev. 01 -- 6 March 2002

3 of 12

9397 750 09334

� Koninklijke Philips Electronics N.V. 2002. All rights reserved.

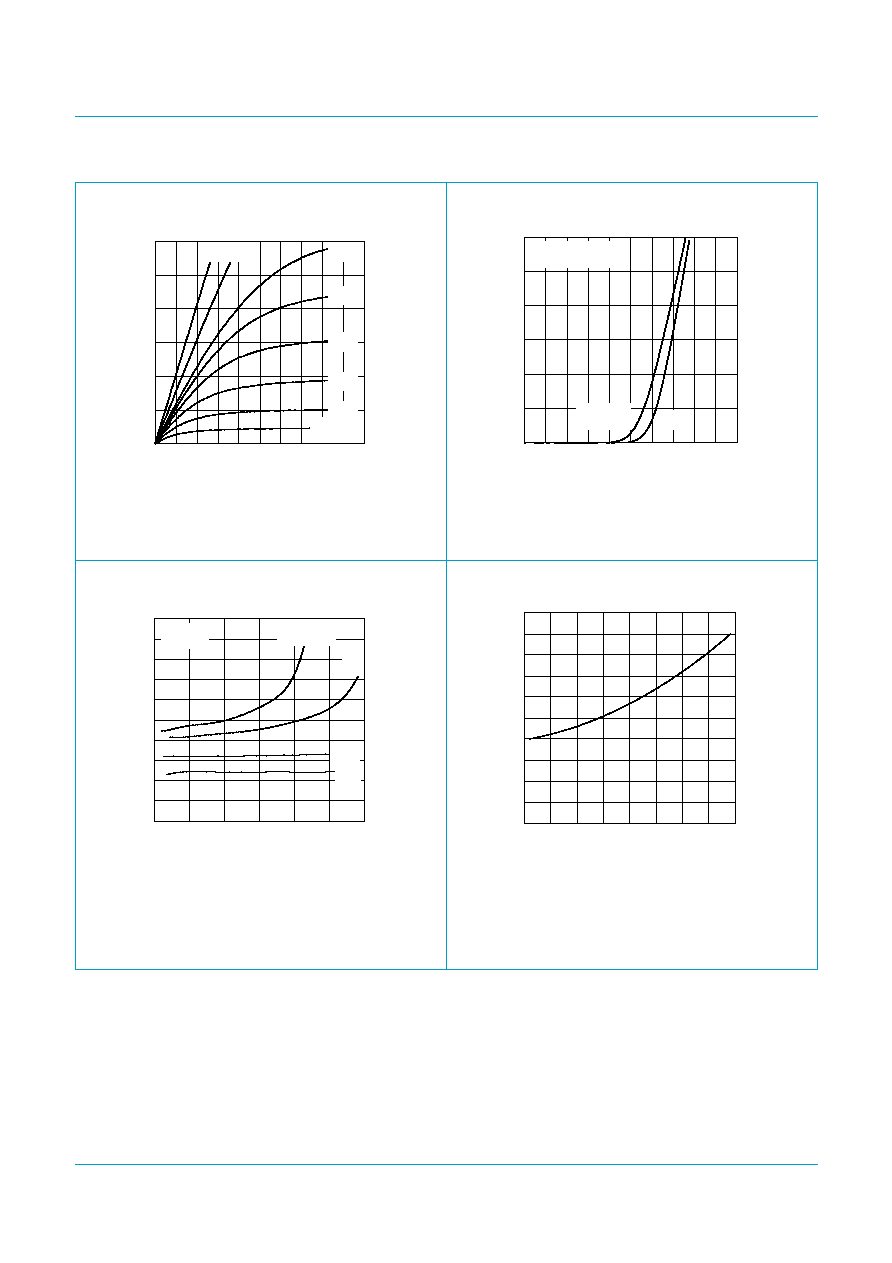

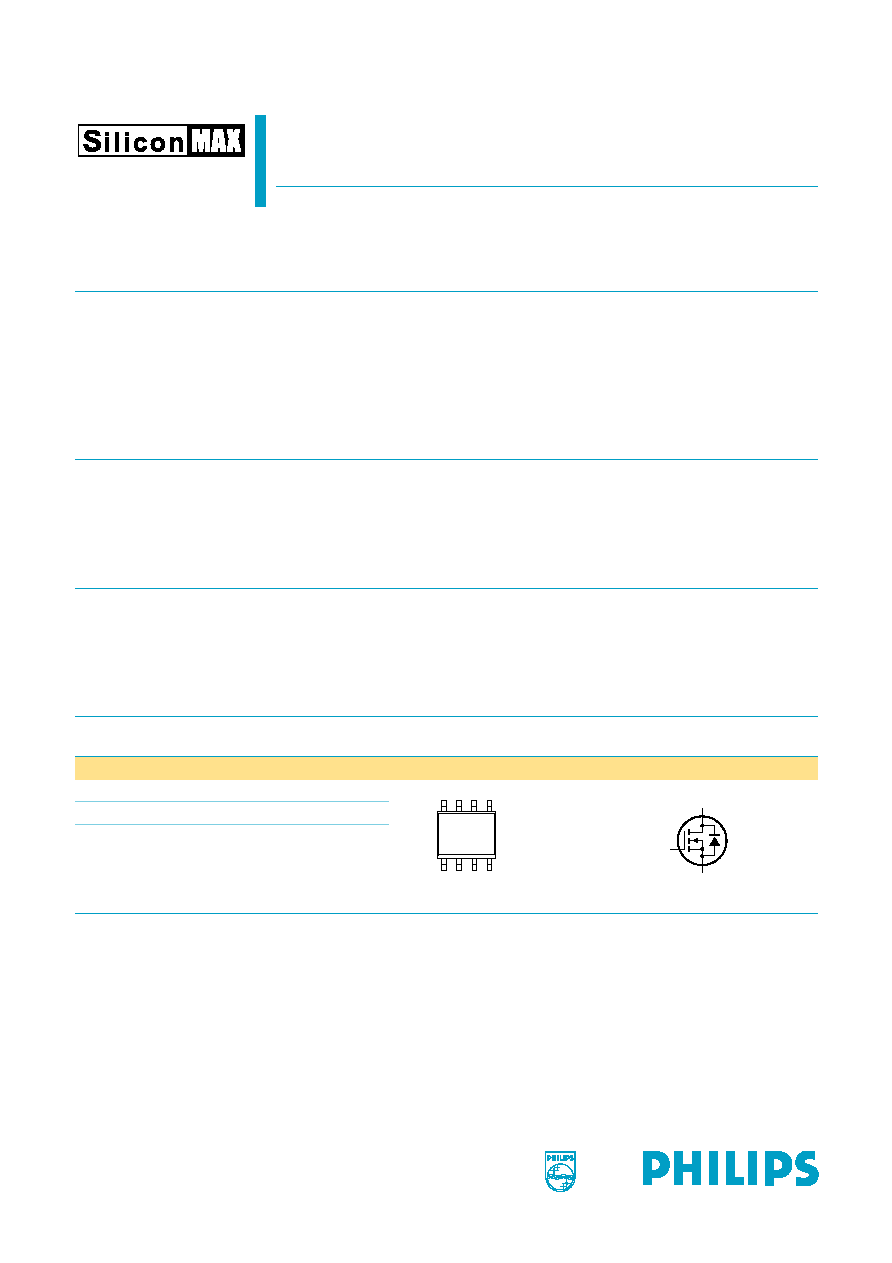

Fig 1.

Normalized total power dissipation as a

function of mounting base temperature.

Fig 2.

Normalized continuous drain current as a

function of mounting base temperature.

T

sp

= 25

�

C; I

DM

is single pulse.

Fig 3.

Safe operating area; continuous and peak drain currents as a function of drain-source voltage.

03aa17

0

40

80

Pder

120

0

50

100

150

200

Tsp (�C)

(%)

03aa25

0

40

80

120

0

50

100

150

200

Tsp

(

o

C)

Ider

(%)

P

der

P

tot

P

tot 25 C

�

(

)

-----------------------

100%

�

=

I

der

I

D

I

D 25 C

�

(

)

-------------------

100%

�

=

03ah05

10-2

10-1

1

10

102

103

10-1

1

10

102

V

DS

(V)

I

D

(A)

DC

100 ms

10 ms

R

DSon

= V

DS

/ I

D

1 ms

t

p

= 10 �s

100 �s

Philips Semiconductors

PSMN005-30K

TrenchMOSTM logic level FET

Product data

Rev. 01 -- 6 March 2002

4 of 12

9397 750 09334

� Koninklijke Philips Electronics N.V. 2002. All rights reserved.

7.

Thermal characteristics

7.1 Transient thermal impedance

Table 4:

Thermal characteristics

Symbol Parameter

Conditions

Min Typ Max Unit

R

th(j-sp)

thermal resistance from junction to solder point mounted on a metal clad board;

Figure 4

-

-

20

K/W

Fig 4.

Transient thermal impedance from junction to mounting base as a function of pulse duration.

03ah04

10-1

1

10

102

10-4

10-3

10-2

10-1

1

10

t

p

(s)

Z

th(j-sp)

(K/W)

single pulse

= 0.5

0.2

0.1

0.05

0.02

tp

tp

T

P

t

T

=

Philips Semiconductors

PSMN005-30K

TrenchMOSTM logic level FET

Product data

Rev. 01 -- 6 March 2002

5 of 12

9397 750 09334

� Koninklijke Philips Electronics N.V. 2002. All rights reserved.

8.

Characteristics

Table 5:

Characteristics

T

j

= 25

�

C unless otherwise specified

Symbol Parameter

Conditions

Min

Typ

Max

Unit

Static characteristics

V

(BR)DSS

drain-source breakdown voltage

I

D

= 250

�

A; V

GS

= 0 V

30

-

-

V

V

GS(th)

gate-source threshold voltage

I

D

= 1 mA; V

DS

= V

GS

T

j

= 25

�

C

1

-

3

V

T

j

= 150

�

C

0.5

-

-

V

T

j

=

-

55

�

C

-

-

3.4

V

I

DSS

drain-source leakage current

V

DS

= 30 V; V

GS

= 0 V

T

j

= 25

�

C

-

-

1

�

A

T

j

= 150

�

C

-

-

0.5

mA

I

GSS

gate-source leakage current

V

GS

=

�

20 V; V

DS

= 0 V

-

-

100

nA

R

DSon

drain-source on-state resistance

V

GS

= 10 V; I

D

= 15 A

T

j

= 25

�

C

-

4.4

5.5

m

V

GS

= 4.5 V; I

D

= 13 A

T

j

= 25

�

C

-

6.6

8

m

Dynamic characteristics

g

fs

forward transconductance

V

DS

= 15 V; I

D

= 20 A

-

60

-

S

Q

g(tot)

total gate charge

I

D

= 20 A; V

DD

= 15 V; V

GS

= 4.5 V

-

34

-

nC

Q

gs

gate-source charge

-

15

-

nC

Q

gd

gate-drain (Miller) charge

-

14

-

nC

C

iss

input capacitance

V

GS

= 0 V; V

DS

= 25 V; f = 1 MHz

-

3100 -

pF

C

oss

output capacitance

-

605

-

pF

C

rss

reverse transfer capacitance

-

405

-

pF

t

d(on)

turn-on delay time

V

DD

= 15 V; R

L

= 15

; V

GS

= 10 V; R

G

= 6

-

18

-

ns

t

r

rise time

-

16

-

ns

t

d(off)

turn-off delay time

-

65

-

ns

t

f

fall time

-

45

-

ns

Source-drain (reverse) diode

V

SD

source-drain (diode forward) voltage I

S

= 15 A; V

GS

= 0 V

-

0.81

1.3

V

t

rr

reverse recovery time

I

S

= 10 A; dI

S

/dt =

-

100 A/

�

s; V

GS

= 0 V

-

35

-

ns

Q

r

recovery charge

-

20

-

nC

Philips Semiconductors

PSMN005-30K

TrenchMOSTM logic level FET

Product data

Rev. 01 -- 6 March 2002

6 of 12

9397 750 09334

� Koninklijke Philips Electronics N.V. 2002. All rights reserved.

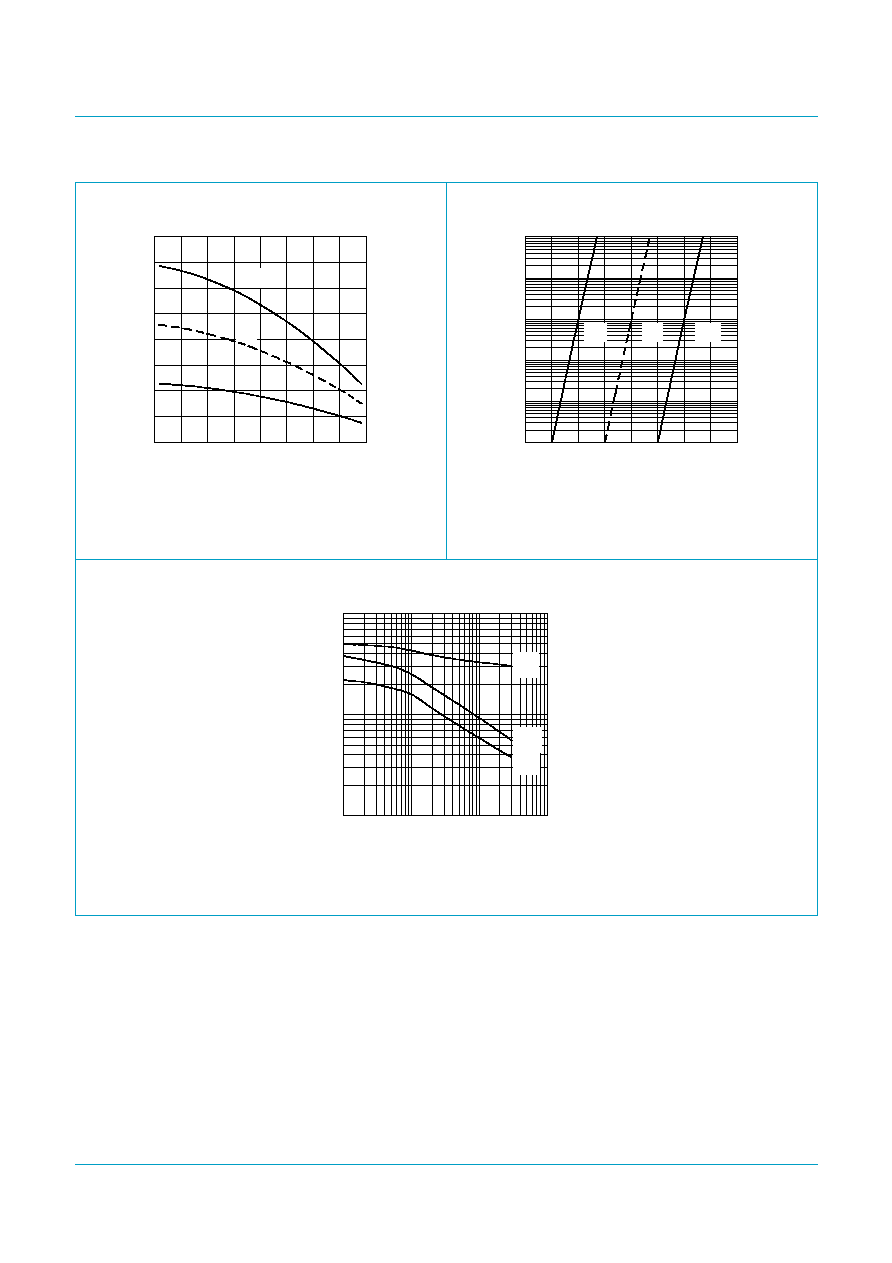

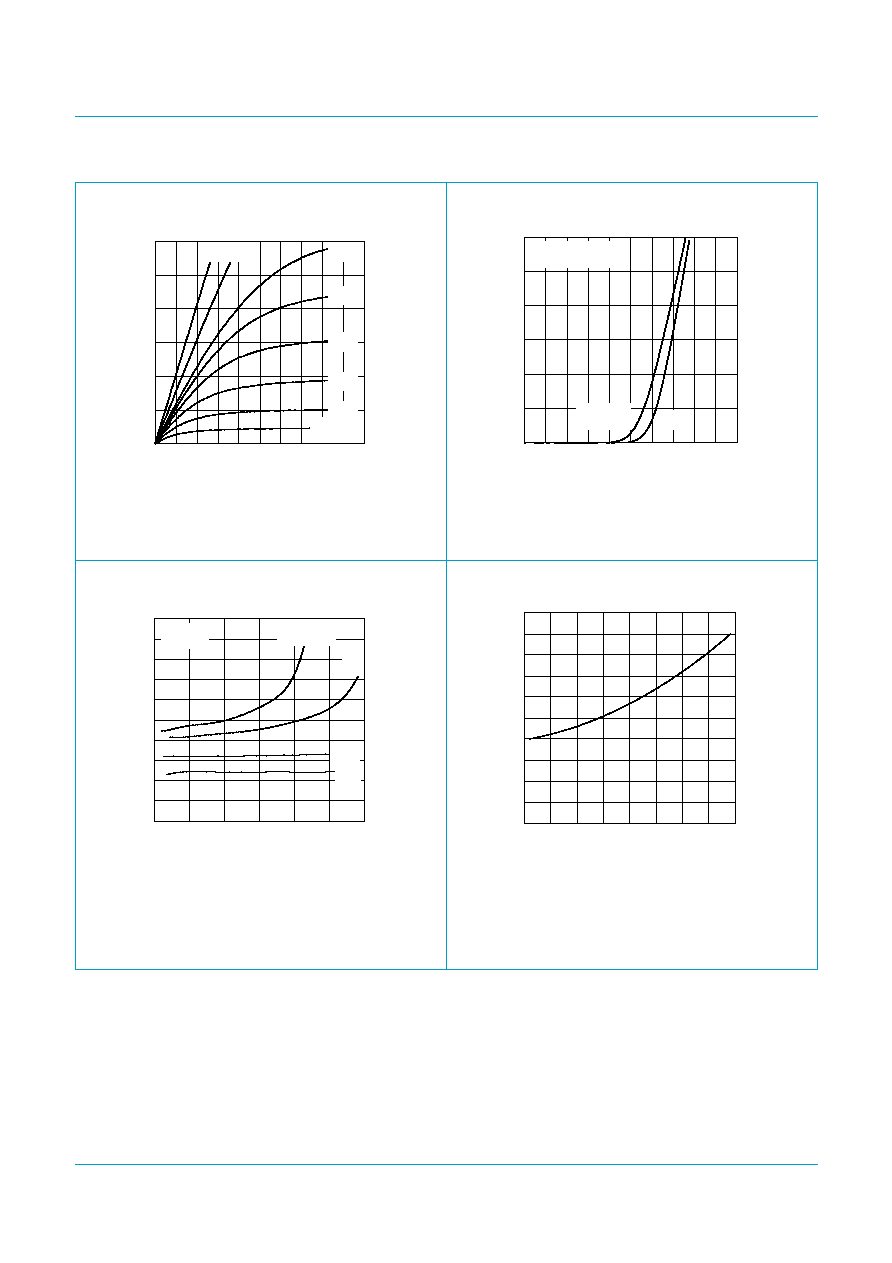

T

j

= 25

�

C

T

j

= 25

�

C and 175

�

C; V

DS

> I

D

x R

DSon

Fig 5.

Output characteristics: drain current as a

function of drain-source voltage; typical values.

Fig 6.

Transfer characteristics: drain current as a

function of gate-source voltage; typical values.

T

j

= 25

�

C

Fig 7.

Drain-source on-state resistance as a function

of drain current; typical values.

Fig 8.

Normalized drain-source on-state resistance

factor as a function of junction temperature.

03ah06

0

20

40

60

0

0.2

0.4

0.6

0.8

1

V

DS

(V)

I

D

(A)

4.5 V

4 V

V

GS

= 3 V

3.8 V

3.6 V

3.4 V

3.2 V

10 V

03ah08

0

20

40

60

0

1

2

3

4

5

VGS (V)

ID

(A)

VDS > ID x R DSon

Tj

= 150 �C

25 �C

03ah07

0

0.004

0.008

0.012

0.016

0.02

0

20

40

60

I

D

(A)

R

DSon

(

)

T

j

= 25 �C

V

GS

= 3.8 V

4.5 V

10 V

4 V

03af18

0

0.4

0.8

1.2

1.6

2

-60

0

60

120

180

Tj (�C)

a

a

R

DSon

R

DSon 25 C

�

(

)

-----------------------------

=

Philips Semiconductors

PSMN005-30K

TrenchMOSTM logic level FET

Product data

Rev. 01 -- 6 March 2002

7 of 12

9397 750 09334

� Koninklijke Philips Electronics N.V. 2002. All rights reserved.

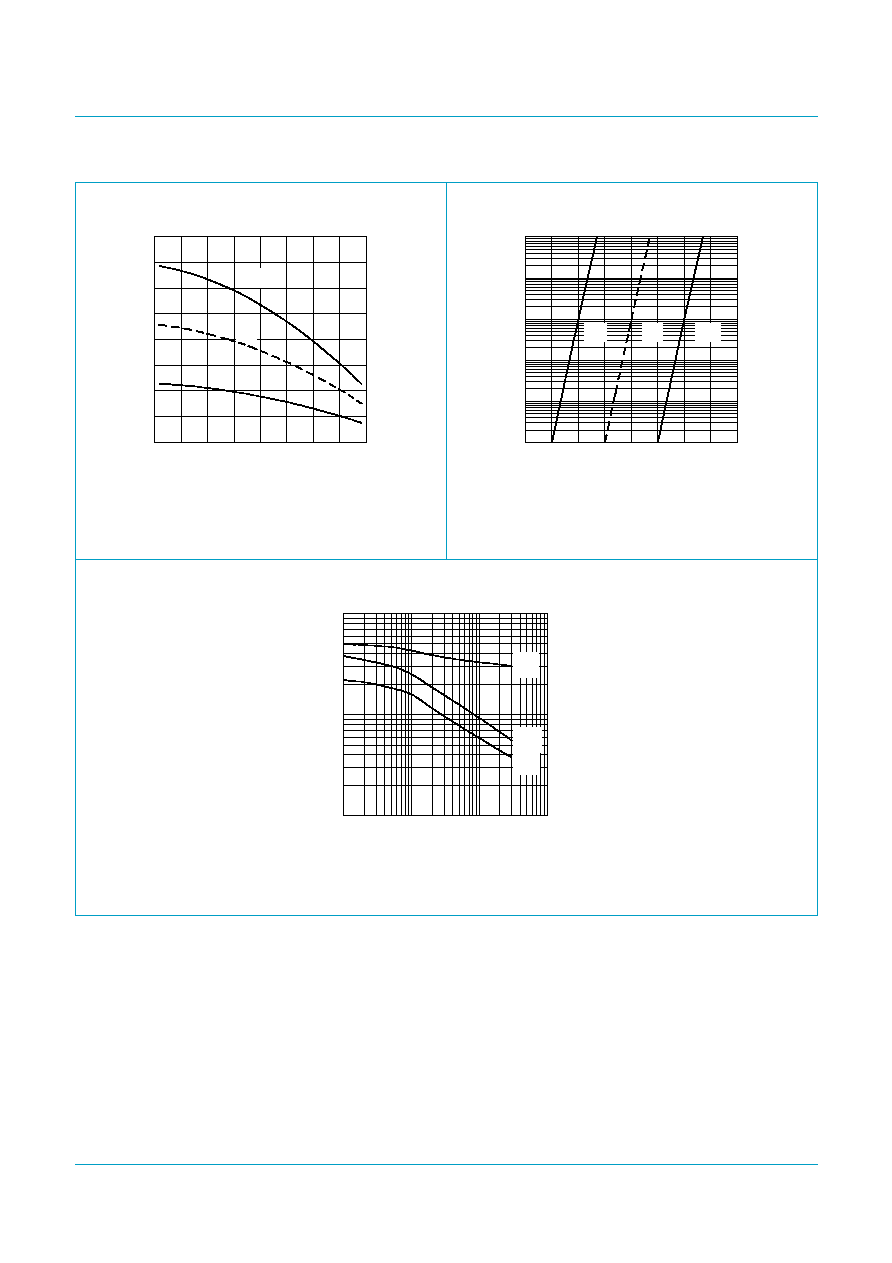

I

D

= 1 mA; V

DS

= V

GS

T

j

= 25

�

C; V

DS

= 5 V

Fig 9.

Gate-source threshold voltage as a function of

junction temperature.

Fig 10. Sub-threshold drain current as a function of

gate-source voltage.

V

GS

= 0 V; f = 1 MHz

Fig 11. Input, output and reverse transfer capacitances as a function of drain-source voltage; typical values.

03af65

0

1

2

3

4

-60

0

60

120

180

min

max

typ

03af66

10-6

10-5

10-4

10-3

10-2

10-1

0

1

2

3

4

min

typ

max

03ah10

102

103

104

10-1

1

10

102

V

DS

(V)

C

(pF)

C

iss

C

oss

C

rss

Philips Semiconductors

PSMN005-30K

TrenchMOSTM logic level FET

Product data

Rev. 01 -- 6 March 2002

8 of 12

9397 750 09334

� Koninklijke Philips Electronics N.V. 2002. All rights reserved.

T

j

= 25

�

C and 175

�

C; V

GS

= 0 V

I

D

= 20 A; V

DD

= 15 V

Fig 12. Source (diode forward) current as a function of

source-drain (diode forward) voltage; typical

values.

Fig 13. Gate-source voltage as a function of gate

charge; typical values.

03ah09

0

20

40

60

0

0.4

0.8

1.2

VSD (V)

IS

(A)

Tj = 25 �C

150 �C

VGS = 0 V

03ah11

0

2

4

6

8

10

0

20

40

60

80

QG (nC)

VGS

(V)

ID = 20 A

Tj = 25 �C

VDD = 15 V

Philips Semiconductors

PSMN005-30K

TrenchMOSTM logic level FET

Product data

Rev. 01 -- 6 March 2002

9 of 12

9397 750 09334

� Koninklijke Philips Electronics N.V. 2002. All rights reserved.

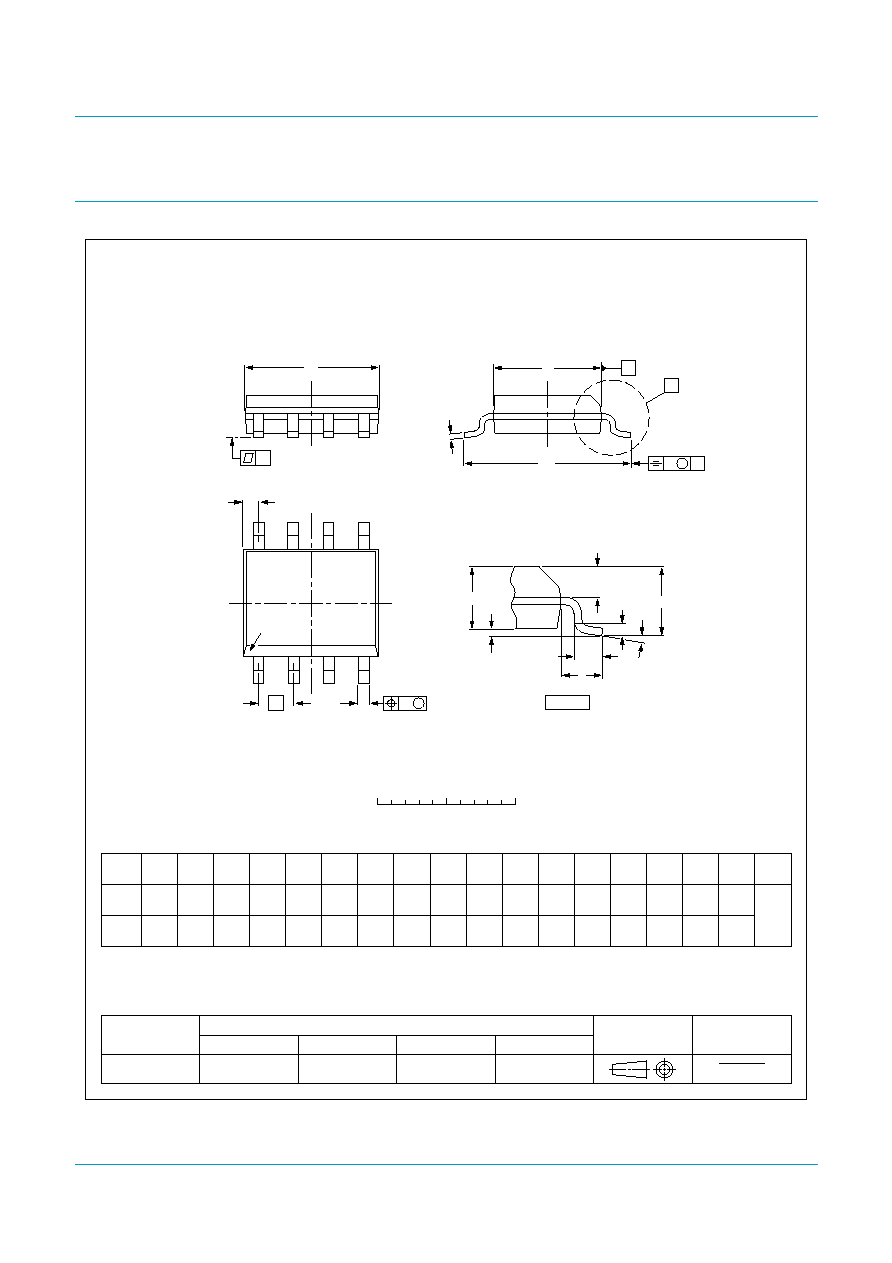

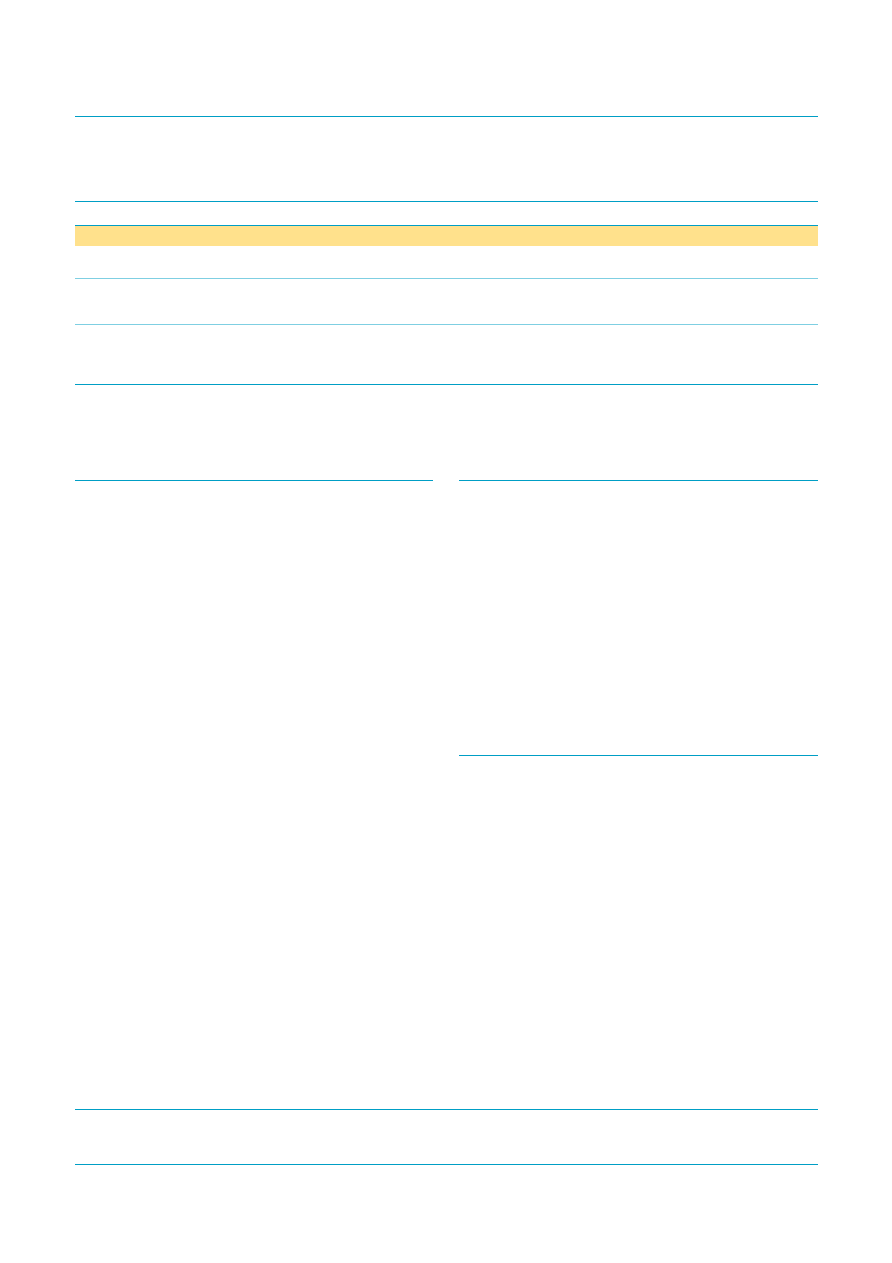

9.

Package outline

Fig 14. SOT96-1 (SO8).

UNIT

A

max.

A

1

A

2

A

3

b

p

c

D

(1)

E

(2)

(1)

e

H

E

L

L

p

Q

Z

y

w

v

REFERENCES

OUTLINE

VERSION

EUROPEAN

PROJECTION

ISSUE DATE

IEC

JEDEC

EIAJ

mm

inches

1.75

0.25

0.10

1.45

1.25

0.25

0.49

0.36

0.25

0.19

5.0

4.8

4.0

3.8

1.27

6.2

5.8

1.05

0.7

0.6

0.7

0.3

8

0

o

o

0.25

0.1

0.25

DIMENSIONS (inch dimensions are derived from the original mm dimensions)

Notes

1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

2. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

1.0

0.4

SOT96-1

X

w

M

A

A

1

A

2

b

p

D

H

E

L

p

Q

detail X

E

Z

e

c

L

v

M

A

(A )

3

A

4

5

pin 1 index

1

8

y

076E03

MS-012

0.069

0.010

0.004

0.057

0.049

0.01

0.019

0.014

0.0100

0.0075

0.20

0.19

0.16

0.15

0.050

0.244

0.228

0.028

0.024

0.028

0.012

0.01

0.01

0.041

0.004

0.039

0.016

0

2.5

5 mm

scale

SO8: plastic small outline package; 8 leads; body width 3.9 mm

SOT96-1

97-05-22

99-12-27

Philips Semiconductors

PSMN005-30K

TrenchMOSTM logic level FET

Product data

Rev. 01 -- 6 March 2002

10 of 12

9397 750 09334

� Koninklijke Philips Electronics N.V. 2002. All rights reserved.

10. Revision history

Table 6:

Revision history

Rev Date

CPCN

Description

01

20020306

-

Product Data; initial version

9397 750 09334

Philips Semiconductors

PSMN005-30K

TrenchMOSTM logic level FET

� Koninklijke Philips Electronics N.V. 2002. All rights reserved.

Product data

Rev. 01 -- 6 March 2002

11 of 12

9397 750 09334

Philips Semiconductors

PSMN005-30K

TrenchMOSTM logic level FET

� Koninklijke Philips Electronics N.V. 2002. All rights reserved.

Product data

Rev. 01 -- 6 March 2002

11 of 12

Contact information

For additional information, please visit http://www.semiconductors.philips.com.

For sales office addresses, send e-mail to: sales.addresses@www.semiconductors.philips.com.

Fax: +31 40 27 24825

11. Data sheet status

[1]

Please consult the most recently issued data sheet before initiating or completing a design.

[2]

The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at

URL http://www.semiconductors.philips.com.

12. Definitions

Short-form specification -- The data in a short-form specification is

extracted from a full data sheet with the same type number and title. For

detailed information see the relevant data sheet or data handbook.

Limiting values definition -- Limiting values given are in accordance with

the Absolute Maximum Rating System (IEC 60134). Stress above one or

more of the limiting values may cause permanent damage to the device.

These are stress ratings only and operation of the device at these or at any

other conditions above those given in the Characteristics sections of the

specification is not implied. Exposure to limiting values for extended periods

may affect device reliability.

Application information -- Applications that are described herein for any

of these products are for illustrative purposes only. Philips Semiconductors

make no representation or warranty that such applications will be suitable for

the specified use without further testing or modification.

13. Disclaimers

Life support -- These products are not designed for use in life support

appliances, devices, or systems where malfunction of these products can

reasonably be expected to result in personal injury. Philips Semiconductors

customers using or selling these products for use in such applications do so

at their own risk and agree to fully indemnify Philips Semiconductors for any

damages resulting from such application.

Right to make changes -- Philips Semiconductors reserves the right to

make changes, without notice, in the products, including circuits, standard

cells, and/or software, described or contained herein in order to improve

design and/or performance. Philips Semiconductors assumes no

responsibility or liability for the use of any of these products, conveys no

licence or title under any patent, copyright, or mask work right to these

products, and makes no representations or warranties that these products are

free from patent, copyright, or mask work right infringement, unless otherwise

specified.

14. Trademarks

SiliconMAX -- is a trademark of Koninklijke Philips Electronics N.V.

TrenchMOS -- is a trademark of Koninklijke Philips Electronics N.V.

Data sheet status

[1]

Product status

[2]

Definition

Objective data

Development

This data sheet contains data from the objective specification for product development. Philips Semiconductors

reserves the right to change the specification in any manner without notice.

Preliminary data

Qualification

This data sheet contains data from the preliminary specification. Supplementary data will be published at a

later date. Philips Semiconductors reserves the right to change the specification without notice, in order to

improve the design and supply the best possible product.

Product data

Production

This data sheet contains data from the product specification. Philips Semiconductors reserves the right to

make changes at any time in order to improve the design, manufacturing and supply. Changes will be

communicated according to the Customer Product/Process Change Notification (CPCN) procedure

SNW-SQ-650A.

� Koninklijke Philips Electronics N.V. 2002.

Printed in The Netherlands

All rights are reserved. Reproduction in whole or in part is prohibited without the prior

written consent of the copyright owner.

The information presented in this document does not form part of any quotation or

contract, is believed to be accurate and reliable and may be changed without notice. No

liability will be accepted by the publisher for any consequence of its use. Publication

thereof does not convey nor imply any license under patent- or other industrial or

intellectual property rights.

Date of release: 6 March 2002

Document order number: 9397 750 09334

Contents

Philips Semiconductors

PSMN005-30K

TrenchMOSTM logic level FET

1

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

3

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

4

Pinning information . . . . . . . . . . . . . . . . . . . . . . 1

5

Quick reference data . . . . . . . . . . . . . . . . . . . . . 2

6

Limiting values. . . . . . . . . . . . . . . . . . . . . . . . . . 2

7

Thermal characteristics. . . . . . . . . . . . . . . . . . . 4

7.1

Transient thermal impedance . . . . . . . . . . . . . . 4

8

Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . 5

9

Package outline . . . . . . . . . . . . . . . . . . . . . . . . . 9

10

Revision history . . . . . . . . . . . . . . . . . . . . . . . . 10

11

Data sheet status . . . . . . . . . . . . . . . . . . . . . . . 11

12

Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

13

Disclaimers . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

14

Trademarks. . . . . . . . . . . . . . . . . . . . . . . . . . . . 11