| –≠–Ľ–Ķ–ļ—ā—Ä–ĺ–Ĺ–Ĺ—č–Ļ –ļ–ĺ–ľ–Ņ–ĺ–Ĺ–Ķ–Ĺ—ā: CXD2720Q | –°–ļ–į—á–į—ā—Ć:  PDF PDF  ZIP ZIP |

≠ 1 ≠

CXD2720Q

E96426-ST

Single-Chip Digital Signal Processor for Karaoke

Description

The CXD2720Q is a digital signal processor LSI for

Karaoke, suitable for use in LD/CD/CD-G/video CD

and the like.

A large capacity DRAM and AD/DA converters are

built in, and Karaoke functions such as key control,

microphone echo and voice canceling are contained

on a single chip.

Features

∑ 3-channel 1-bit AD converter and decimation filter

S/N ratio: 88 dB

THD + N: 0.016%

Filter pass band ripple:

less than Ī0.5dB

Filter stop band attenuation: less than ≠41dB

(all characteristics are typical values)

∑ 2-channel 1-bit DA converter and oversampling

filter

S/N ratio: 98dB

THD + N: 0.006%

Filter pass band ripple:

less than Ī0.2dB

Filter stop band attenuation: less than ≠41dB

(all characteristics are typical values)

∑ In addition to analog input/output, 2-channel input/

2-channel output of digital input/output are provided.

The interface also supports a variety of formats.

∑ 128K-bit DRAM for key control and microphone

echo processing

Functions

∑ Key controller pitch setting can be varied to a

maximum of Ī1 octave with a precision of 14 bits

∑ Microphone echo delay time can be varied to a

maximum of 185ms (when Fs = 44.1kHz)

∑ Voice canceller supports settings other than center

by the panpot volume

∑ Voice parametric equalizer

∑ Voice pitch shifter

∑ Mixing function to support sound multiplexing

software

∑ Digital de-emphasis function

Structure

Silicon gate CMOS

Applications

Equipment having Karaoke function, such as

LD/CD, compact music center, video games, etc.

Absolute Maximum Ratings

(Ta = 25įC, V

SS

= 0V)

∑ Supply voltage

V

DD

V

SS

≠ 0.5 to +7.0

V

∑ Input voltage

V

I

V

SS

≠ 0.5 to V

DD

+ 0.5 V

∑ Output voltage

V

O

V

SS

≠ 0.5 to V

DD

+ 0.5 V

∑ Operating temperature

Topr

≠20 to +75

įC

∑ Storage temperature Tstg

≠55 to +150

įC

Recommended Operating Conditions

∑ Supply voltage

V

DD

4.5 to 5.5 (5.0 typ.)

V

∑ Operating temperature

Ta

≠20 to +75

įC

Input/Output Capacitance

∑ Input capacitance

C

IN

9 (max.)

pF

∑ Output capacitance

C

OUT

11 (max.)

pF

∑ Input/output capacitance C

I/O

11(max.)

pF

Measurement conditions: V

DD

= V

I

= 0V, F = 1MHz

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

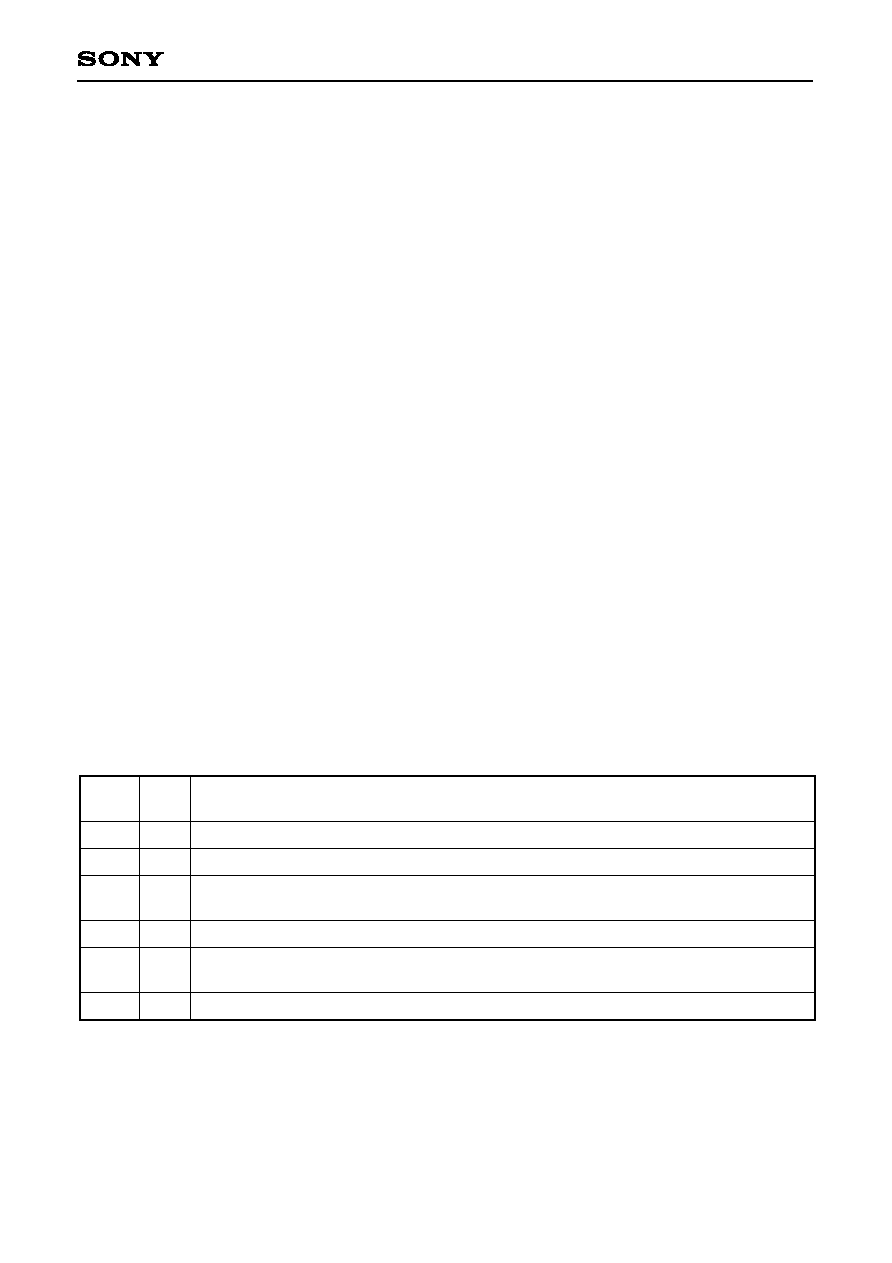

100 pin QFP (Plastic)

≠ 2 ≠

CXD2720Q

3

4

5

6

7

25

26

40

39

32

33

82

128K bit DELAY RAM

DSP

CLOCK GENERATOR

/TIMING CIRCUIT

DAC1

DAC2

ADC1

ADC2

ADC3

29

22

36

MICRO

COMPUTER

I/F

SERIAL

DATA

I/F

8

12

88

87

86

AIN1

RVDT

SCK

XLAT

REDY

TRDT

LRCK

BCK

SI

SO

XWO

XTLI XTLO BFOT

AO1P

AO1N

AO2N

AO2P

AIN2

AIN3

Block Diagram

40

39

38

37

36

35

34

31

32

33

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

70 69 68 67

63

64

65

66

61

62

71

72

73

74

75

76

77

78

79

80

81

82

83

84

88

87

86

85

89

90

100

99

98

97

96

95

94

91

92

93

2

3

4

5

6

7

8

9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30

1

AV

S

0

V

SS

0

RVDT

SCK

XLAT

REDY

TRDT

XWO

XRST

V

SS

1

V

DD

0

SO

XS24

TST0

TST1

TST2

TST3

TST4

TST5

V

SS

2

AV

S

3

AIN3

AV

D

3

AV

D

4

AO1P

AO1N

AV

S

4

AV

S

1

AIN1

AV

D

1

V

SS

6

NC

NC

NC

NC

NC

NC

NC

NC

NC

V

DD

2

V

SS

5

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

V

SS

4

NC

NC

NC

NC

NC

NC

NC

NC

NC

V

DD

1

V

SS

3

AV

S

5

AO2P

AO2N

AV

D

5

AV

D

2

AIN2

AV

S

2

XV

SS

XTLI

XTLO

XV

DD

LRCK

X768

BFOT

INVI

NC

NC

SI

BCK

XMST

V

SS

7

NC

NC

NC

NC

NC

NC

NC

NC

V

DD

3

AV

D

0

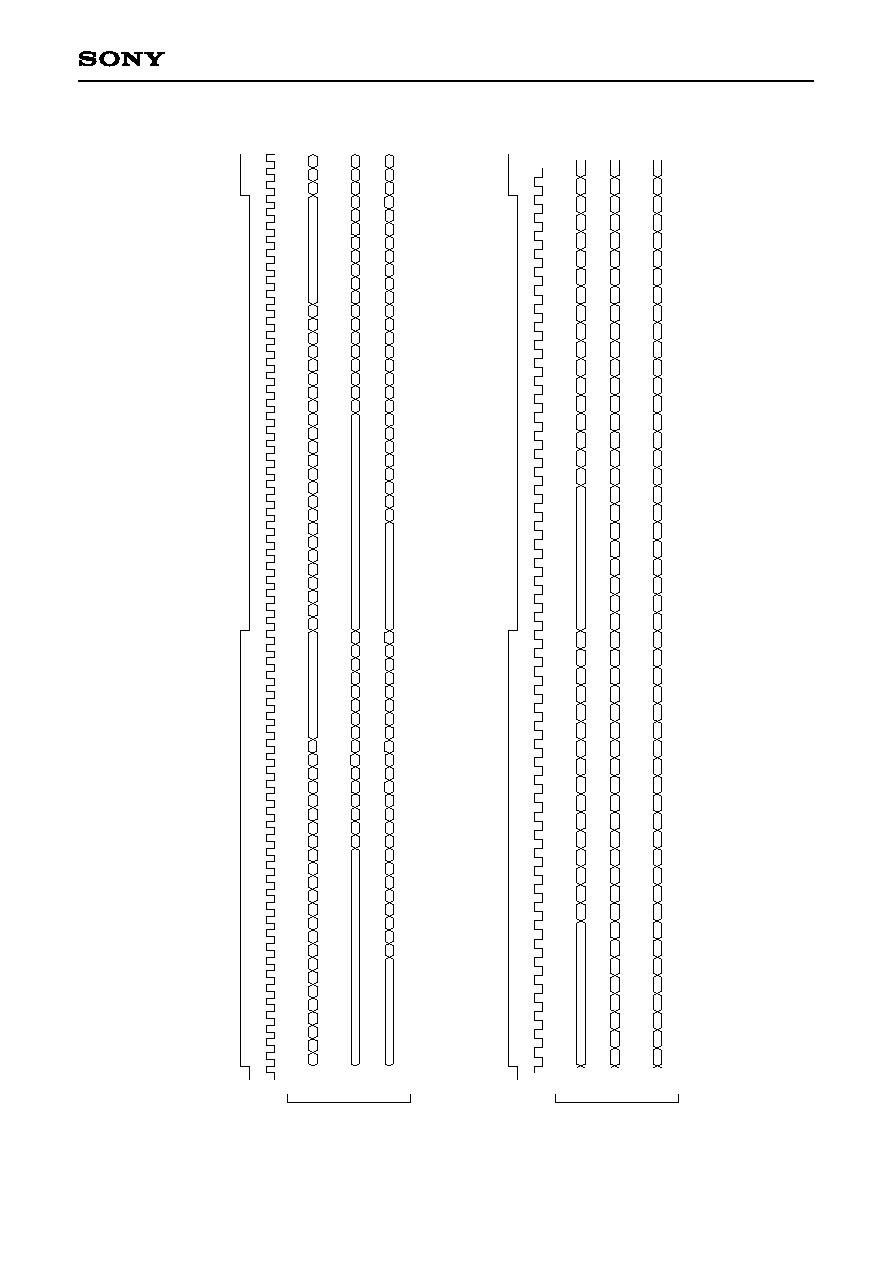

Pin Configuration

≠ 3 ≠

CXD2720Q

Pin Description

Pin

No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

AV

S

0

V

SS

0

RVDT

SCK

XLAT

REDY

TRDT

XWO

XRST

V

SS

1

V

DD

0

SO

XS24

TST0

TST1

TST2

TST3

TST4

TST5

V

SS

2

AV

S

3

AIN3

AV

D

3

AV

D

4

AO1P

AO1N

AV

S

4

AV

S

1

AIN1

AV

D

1

XV

DD

XTLO

XTLI

XV

SS

AV

S

2

--

--

I

I

I

O

O

I

I

--

--

O

I

I

I

I

I

I

I

--

--

I

--

--

O

O

--

--

I

--

--

O

I

--

--

DRAM digital GND.

Digital GND.

Data input for microcomputer interface.

Shift clock input for microcomputer interface.

Latch input for microcomputer interface.

Transmission enabling signal output for microcomputer interface. Transmission

prohibited when Low.

Serial data output for microcomputer interface.

Window open input for synchronization. Normally High.

System reset input. Resets when Low.

Digital GND.

Digital power supply.

1-sampling 2-channel serial data output.

Serial data 24-/32-bit slot selection. 24-bit slot when Low. (valid for slave mode)

Test pin. Normally set Low.

Test pin. Normally set Low.

Test pin. Normally set Low.

Test pin. Normally set Low.

Test pin. Normally set Low.

Test pin. Normally set Low.

Digital GND.

CH3 AD converter GND.

CH3 AD converter analog input (for microphone input).

CH3 AD converter power supply.

CH1 DA converter power supply.

CH1 DA converter analog positive phase output.

CH1 DA converter analog reversed phase output.

CH1 DA converter GND.

CH1 AD converter GND.

CH1 AD converter analog input.

CH1 AD converter power supply.

Digital power supply for master clock.

Crystal oscillator circuit output.

Crystal oscillator circuit input.

Digital GND for master clock.

CH2 AD converter GND.

Symbol

I/O

Description

≠ 4 ≠

CXD2720Q

Pin

No.

36

37

38

39

40

41

42

43

44 to 52

53

54 to 68

69

70

71 to 79

80

81

82

83

84

85

86

87

88

89

90

91 to 98

99

100

AIN2

AV

D

2

AV

D

5

AO2N

AO2P

AV

S

5

V

SS

3

V

DD

1

NC

V

SS

4

NC

V

SS

5

V

DD

2

NC

V

SS

6

X768

BFOT

INVI

NC

NC

SI

BCK

LRCK

XMST

V

SS

7

NC

V

DD

3

AV

D

0

I

--

--

O

O

--

--

--

--

--

--

--

I

O

I

I

I/O

I/O

I

--

--

--

CH2 AD converter analog input.

CH2 AD converter power supply.

CH2 DA converter power supply.

CH2 DA converter analog reversed phase output.

CH2 DA converter analog positive phase output.

CH2 DA converter GND.

Digital GND.

Digital power supply.

Normally open.

Digital GND.

Normally open.

Digital GND.

Digital power supply.

Normally open.

Digital GND.

Test input pin. Normally set Low.

Clock, frequency-divider output (384fs).

Test pin. Normally set Low.

Normally open.

Normally open.

1-sampling 2-channel serial data input.

Serial bit transmission clock for serial input/output data SI and SO.

Sampling frequency clock for serial input/output data SI and SO.

BCK, LRCK master/slave mode switching input. Master mode when Low.

Digital GND.

Normally open.

Digital power supply.

Digital power supply for DRAM.

Symbol

I/O

Description

≠ 5 ≠

CXD2720Q

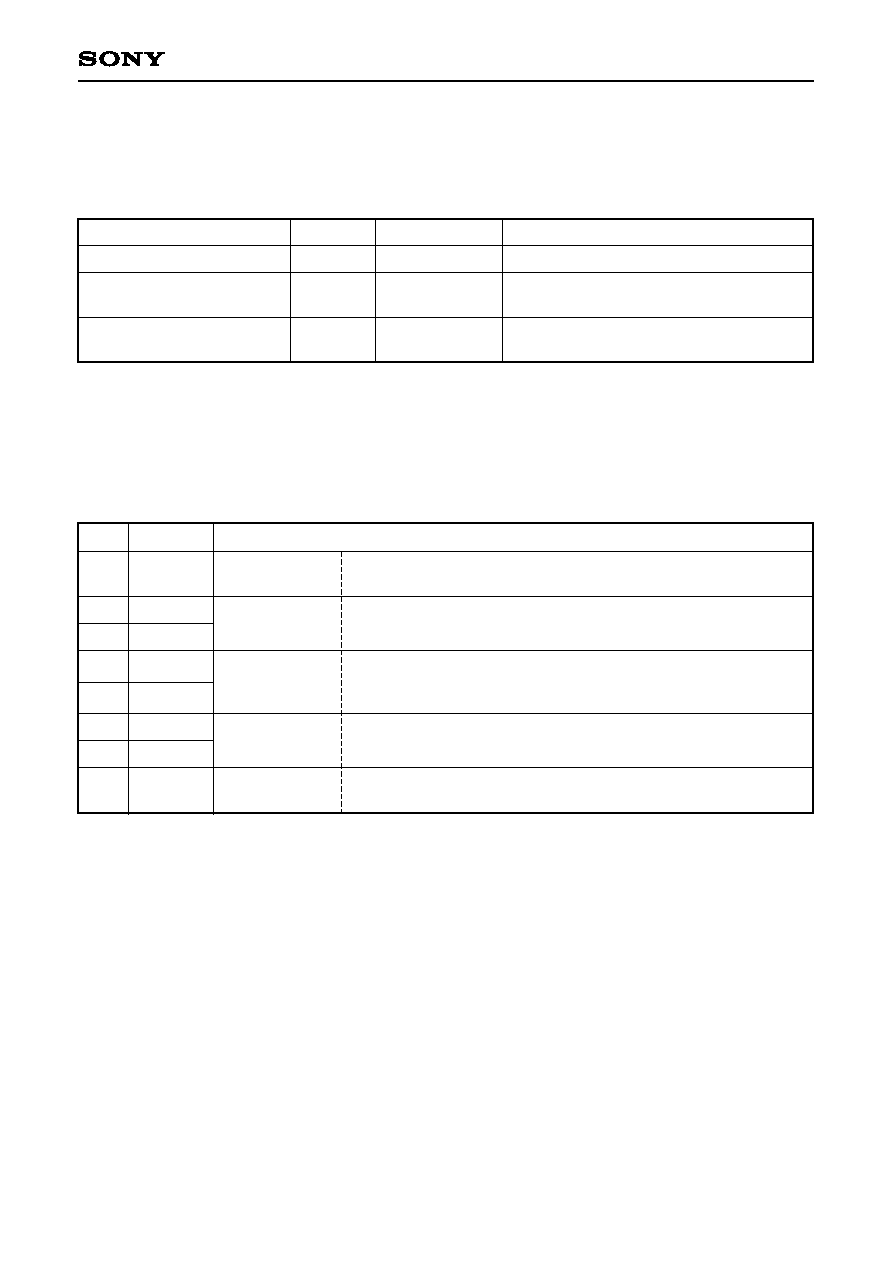

DC Characteristics

(AV

D

0 to 5 = XV

DD

= V

DD

0 to 3 = 5V Ī 10%, AV

S

0 to 5 = XV

SS

= V

SS

0 to 7 = 0V, Ta = ≠20 to +75įC)

Item

Symbol

Conditions

Min.

Typ.

Max.

Unit Applicable pins

High level

Low level

High level

Low level

High level

Low level

High level

Low level

High level

Low level

V

IH

V

IL

V

IH

V

IL

V

IN

V

OH

V

OL

V

OH

V

OL

V

OH

V

OL

I

I

I

I

I

OZ

R

FB

I

DD

Analog input

I

OH

= ≠2.0mA

I

OL

= 4.0mA

I

OH

= ≠6.0mA

I

OL

= 4.0mA

I

OH

= ≠12.0mA

I

OL

= 12.0mA

V

IH

= V

DD

, V

SS

V

IH

= V

DD

, V

SS

V

IH

= V

DD

, V

SS

fs = 44.1kHz

0.7V

DD

0.8V

DD

V

SS

V

DD

≠ 0.8

V

DD

≠ 0.8

V

DD

/2

≠10

≠40

≠40

250k

1M

79

0.3V

DD

0.2V

DD

V

DD

0.4

0.4

V

DD

/2

10

40

40

2.5M

90

V

V

V

V

V

V

V

V

V

V

V

ĶA

ĶA

ĶA

mA

1,

4,

5

1,

4,

5

3

3

2

6,

7,

8

6,

7,

8,

9

10

10

11

11

1,

3,

5

4

8,

9

Resistance

between

5

and

11

.

Input voltage (1)

Input voltage (2)

Output voltage

(1)

Output voltage

(2)

Output voltage

(3)

Input leak current (1)

Input leak current (2)

Output leak current

Feedback resistance

Current consumption

Input voltage (3)

1

RVDT, SCK, XLAT, XWO, XRST, XS24, TST0 to TST5, X768, SI, XMST

2

AIN1, AIN2, AIN3

3

INVI

4

During input to bidirectional pins BCK, LRCK

5

XTLI

6

During output from bidirectional pins BCK, LRCK

7

SO, BFOT

8

TRDT

9

REDY

10

AO1P, AO1N, AO2N, AO2P

11

XTLO

≠ 6 ≠

CXD2720Q

AC Characteristics

(AV

D

0 to 5 = XV

DD

= V

DD

0 to 3 = 5VĪ10%, AV

S

0 to 5 = XV

SS

= V

SS

0 to 7 = 0V, Ta = ≠20 to +75įC)

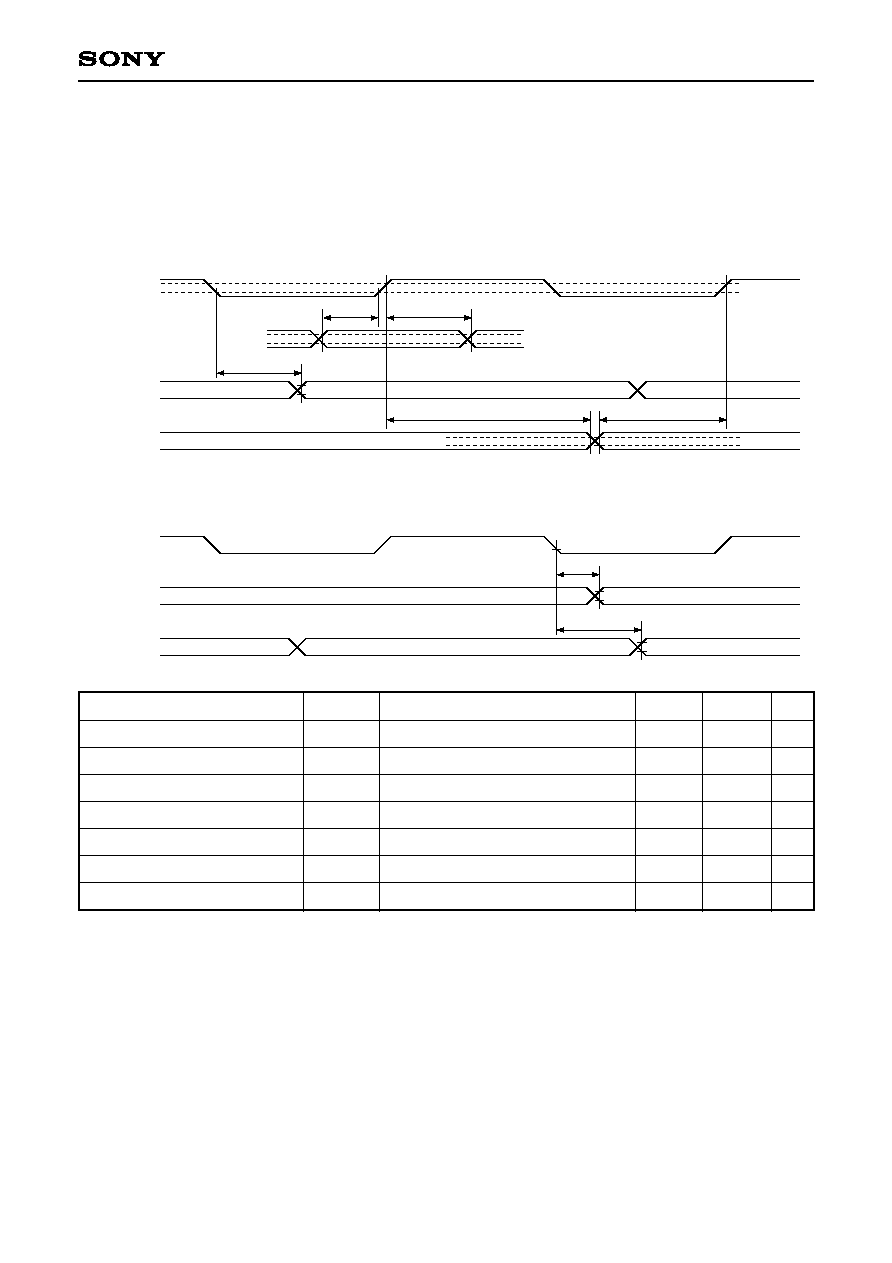

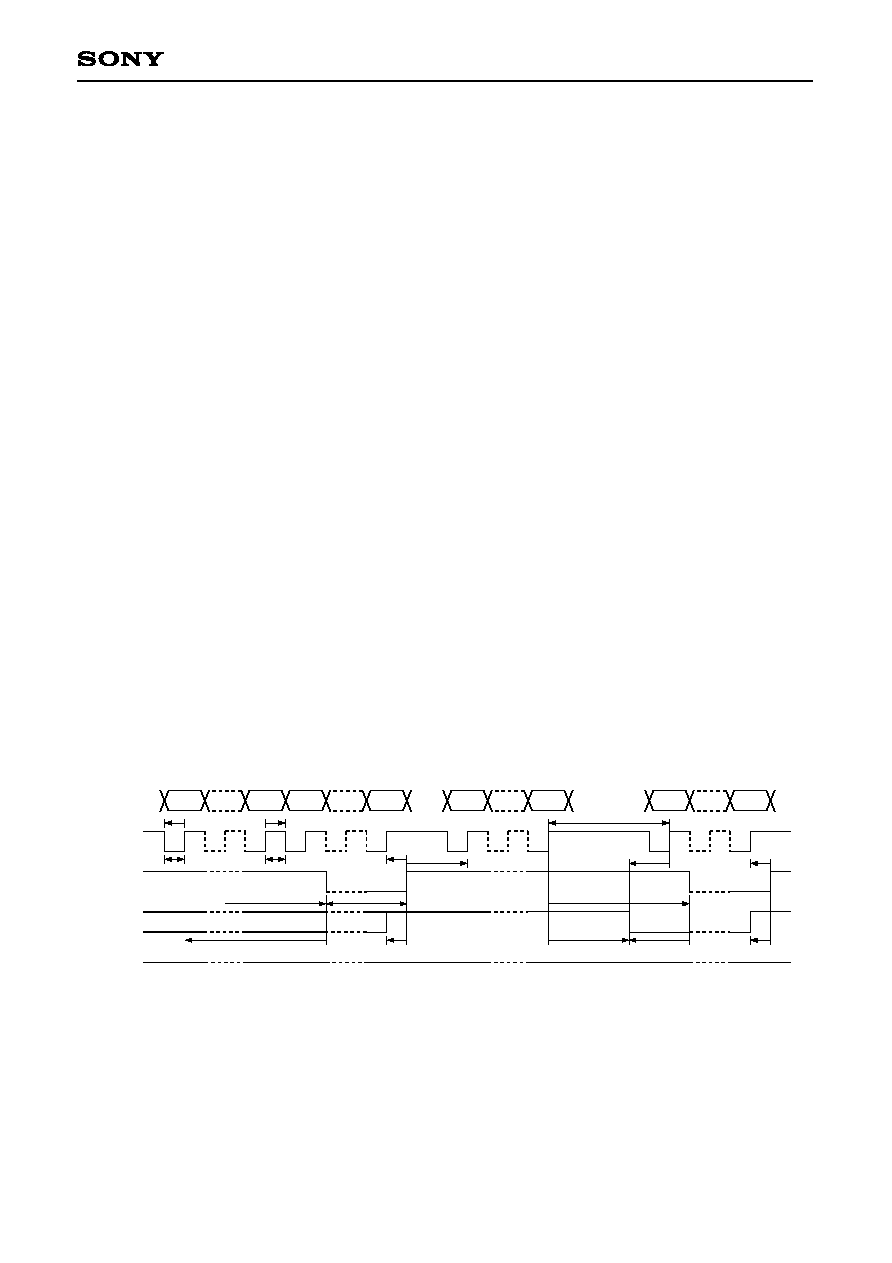

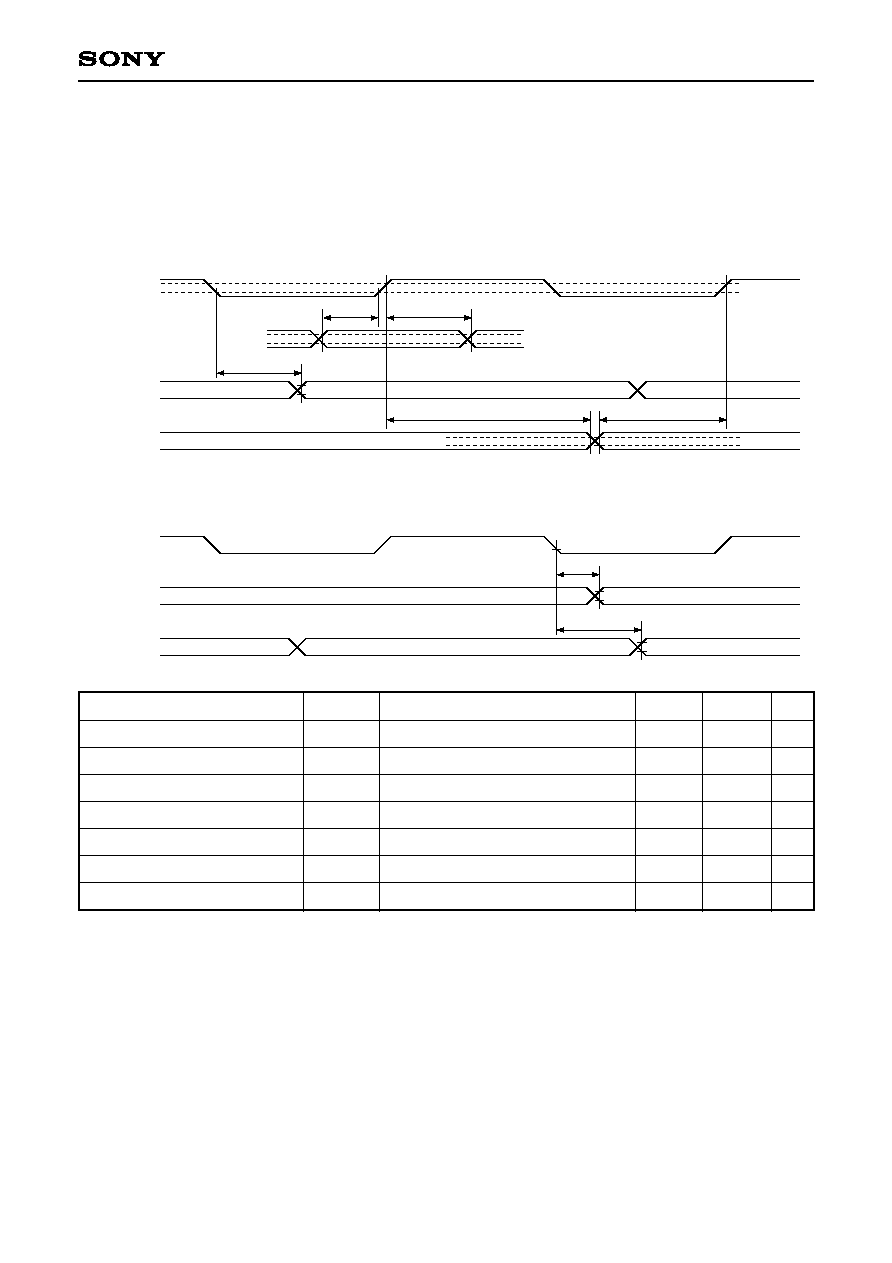

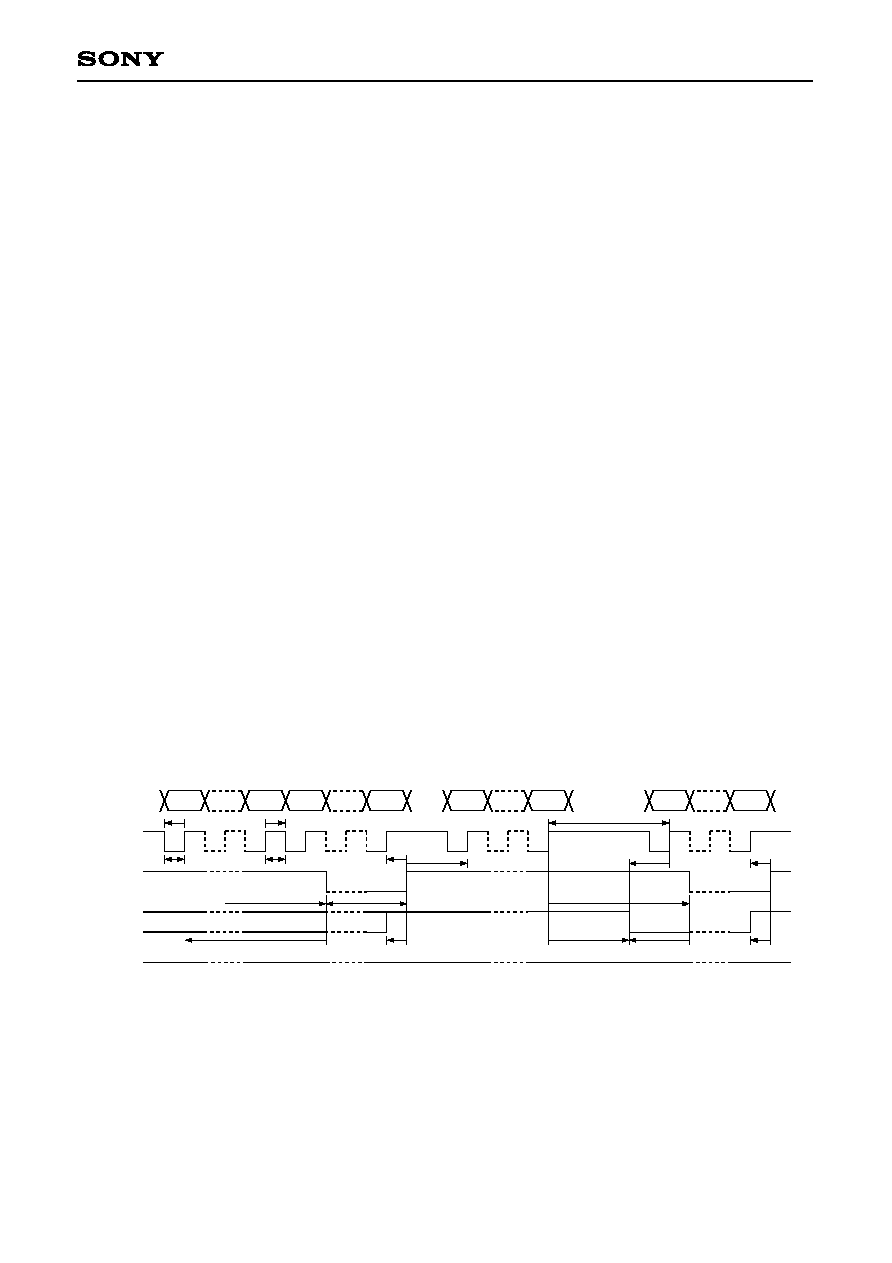

Serial Audio Interface Timing

[Slave mode]

0.7V

DD

t

SLR

0.3V

DD

t

HLR

0.7V

DD

0.3V

DD

0.7V

DD

0.3V

DD

t

HSI

t

SSI

t

DSSO

BCK

SI

SO

LRCK

BCK

SO

LRCK

t

DLR

t

DMSO

[Master mode]

Item

SI setup time

SI hold time

SO delay time

LRCK setup time

LRCK hold time

LRCK delay time

SO delay time

Slave mode

Slave mode

Slave mode, CL = 60pF

Slave mode

Slave mode

Master mode, CL = 120pF

Master mode, CL = 60pF

20

40

20

40

50

50

100

ns

ns

ns

ns

ns

ns

ns

t

SSI

t

HSI

t

DSSO

t

SLR

t

HLR

t

DLR

t

DMSO

Symbol

Conditions

Min.

Max.

Unit

≠ 7 ≠

CXD2720Q

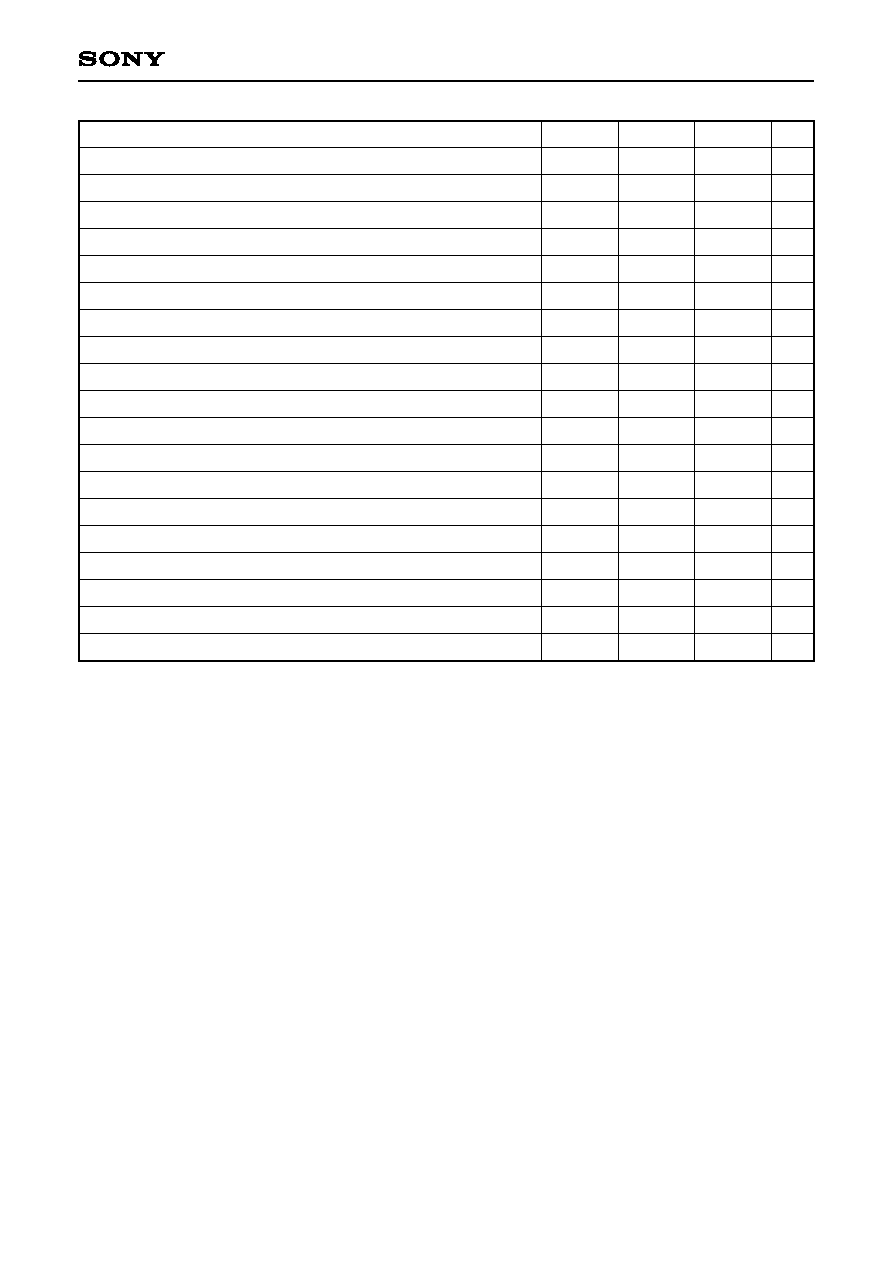

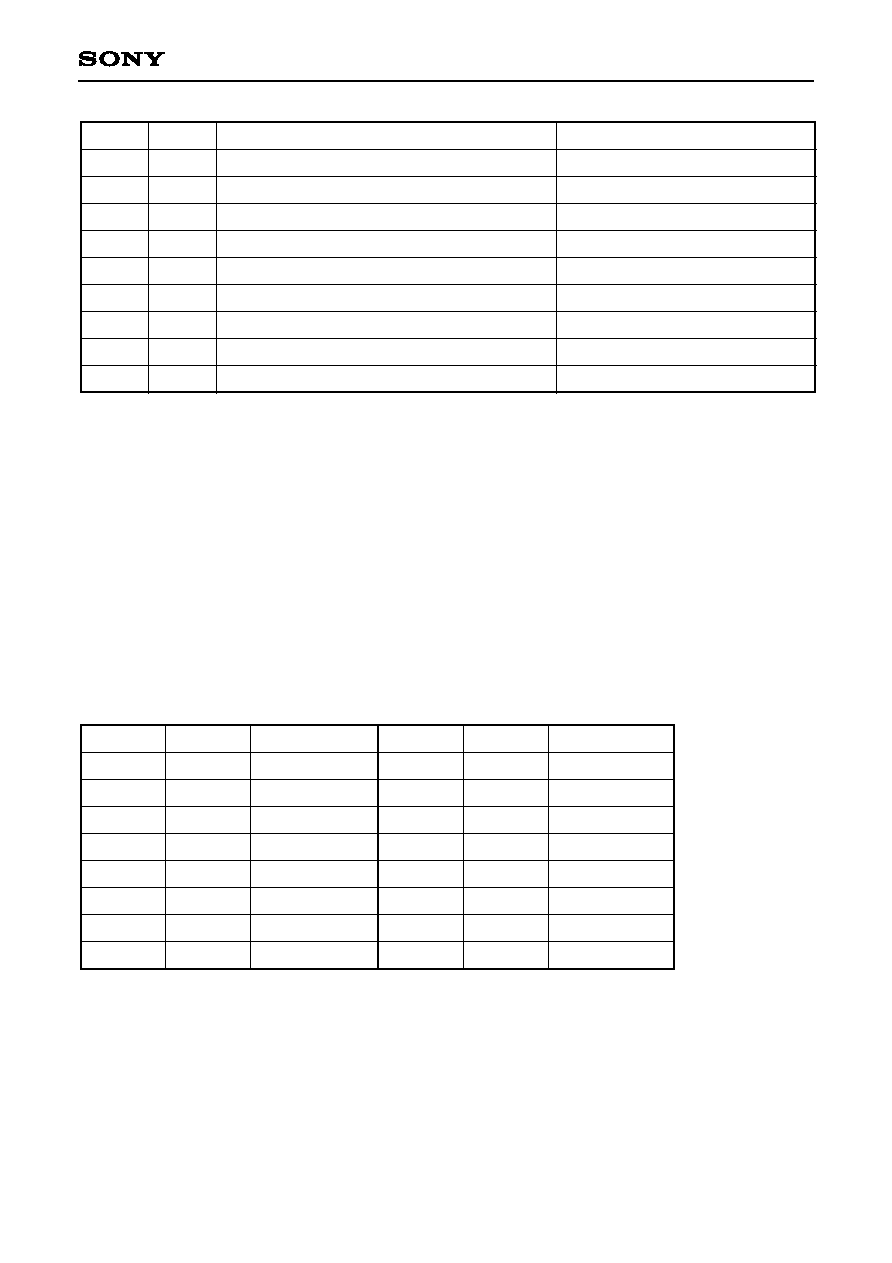

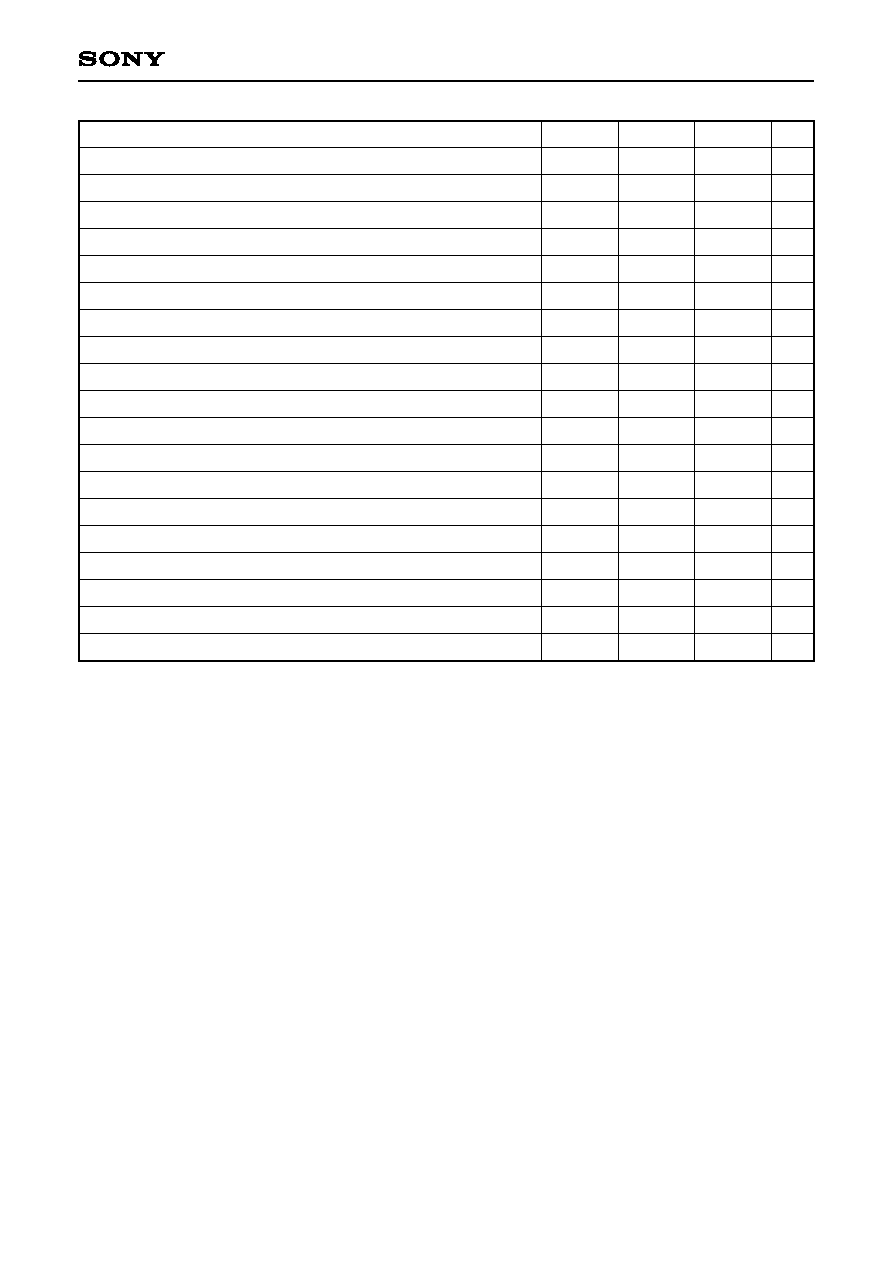

Microcomputer Interface Timing

[Write]

∑ Transmission timing for address section, transmission mode section, data section LSB

t

SWL

RVDT

SCK

XLAT

REDY

t

SWH

t

DS

t

DH

t

LSD

t

SLP

0.7V

DD

0.3V

DD

t

LWL

Mode MSB

0.7V

DD

0.3V

DD

0.7V

DD

0.3V

DD

Address LSB

Data LSB

Data MSB

t

LWH

[Read]

∑ Transmission timing for address section and transmission mode section is the same as for write.

Mode MSB

RVDT

SCK

XLAT

REDY

Address LSB

0.7V

DD

0.3V

DD

0.7V

DD

0.3V

DD

0.7V

DD

0.3V

DD

TRDT

t

SS

t

SLP

t

LWL

t

LBD

t

LDN

t

SDD

t

RSDP

Data MSB

Data LSB

∑ Transmission timing from data section MSB to address section and transmission mode section

0.7V

DD

0.3V

DD

Data MSB

Address LSB

Mode MSB

0.7V

DD

0.3V

DD

0.7V

DD

0.3V

DD

RVDT

SCK

XLAT

REDY

t

SS

t

SLD

t

SBD

t

LDR

t

BSP

t

RLP

≠ 8 ≠

CXD2720Q

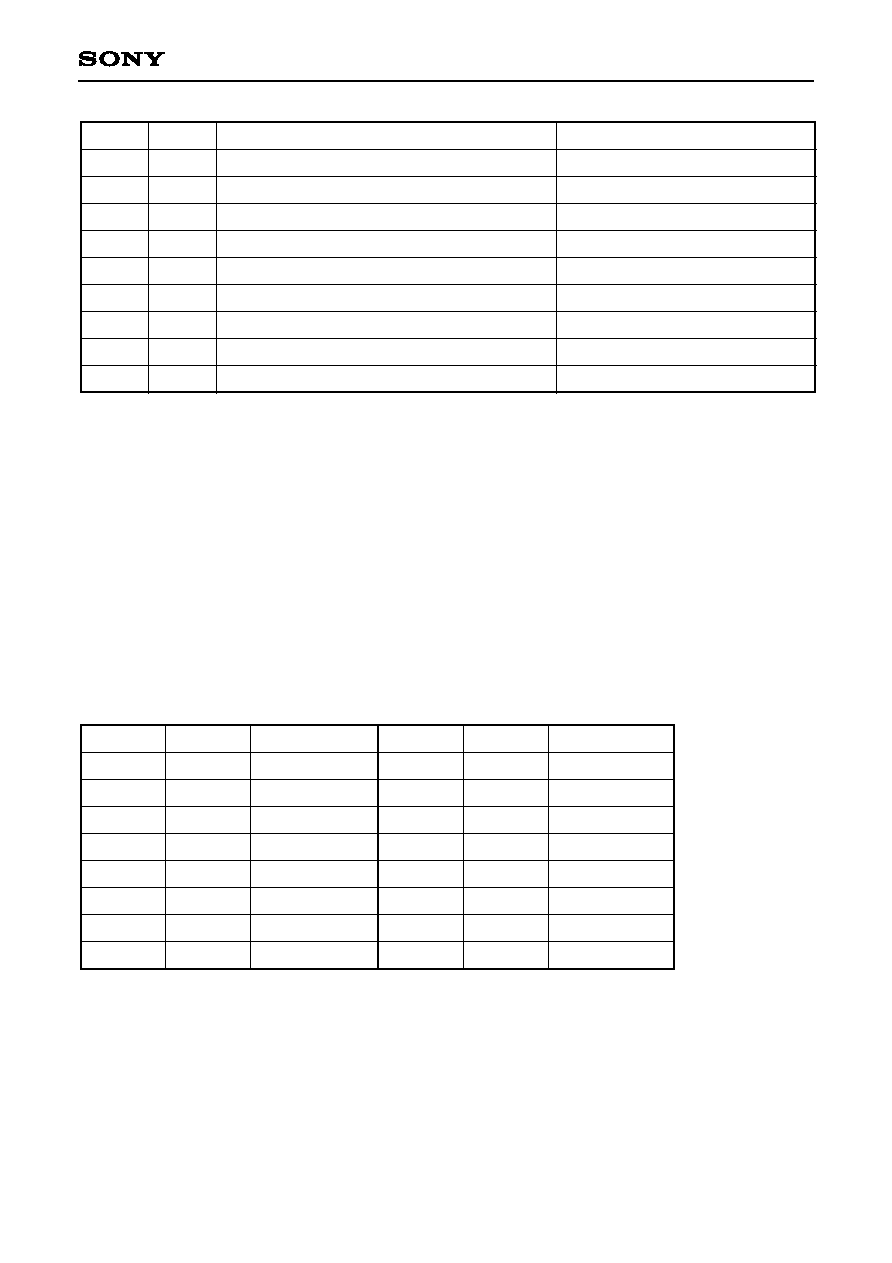

Item

RVDT setup time relative to SCK rise

RVDT data hold time from SCK rise

SCK Low level width

SCK High level width

XLAT Low level width

XLAT High level width

SCK rise preceding time relative to XLAT rise

SCK rise wait time relative to XLAT rise

Delay time to REDY fall relative to XLAT rise.

Delay time to REDY fall relative to SCK rise

REDY fall preceding time relative to SCK rise

REDY rise preceding time relative to XLAT rise

REDY rise preceding time relative to SCK fall

XLAT fall wait time relative to SCK rise

XLAT fall delay time relative to REDY fall

Delay time from XLAT rise until TRDT data becomes active

Delay time from SCK rise until TRDT data becomes high-impedance

Delay time from SCK fall until TRDT data is verified

CK rise wait time for next transmission

20

1

t

+ 20

1

t

+ 20

1

t

+ 20

1

t

+ 20

1

t

+ 20

20

3

t

+ 20

20

20

20

3

t

+ 20

20

2

t

+ 40

3

t

+ 50

4

t

+ 50

3

t

+ 80

3

t

+ 80

2

t

+ 70

t

DS

t

DH

t

SWL

t

SWH

t

LWL

t

LWH

t

SLP

t

LSD

t

LBD

t

SBD

t

BSP

t

RLP

t

RSDP

t

SLD

t

LDR

t

LDN

t

SDF

t

SDD

t

SS

Symbol

Min.

Max.

Note 1)

t

is the cycle of 1/2 the clock frequency applied to the XTLI pin. (384fs)

Note 2) REDY and TRDT pins are the values for CL = 60pF.

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

≠ 9 ≠

CXD2720Q

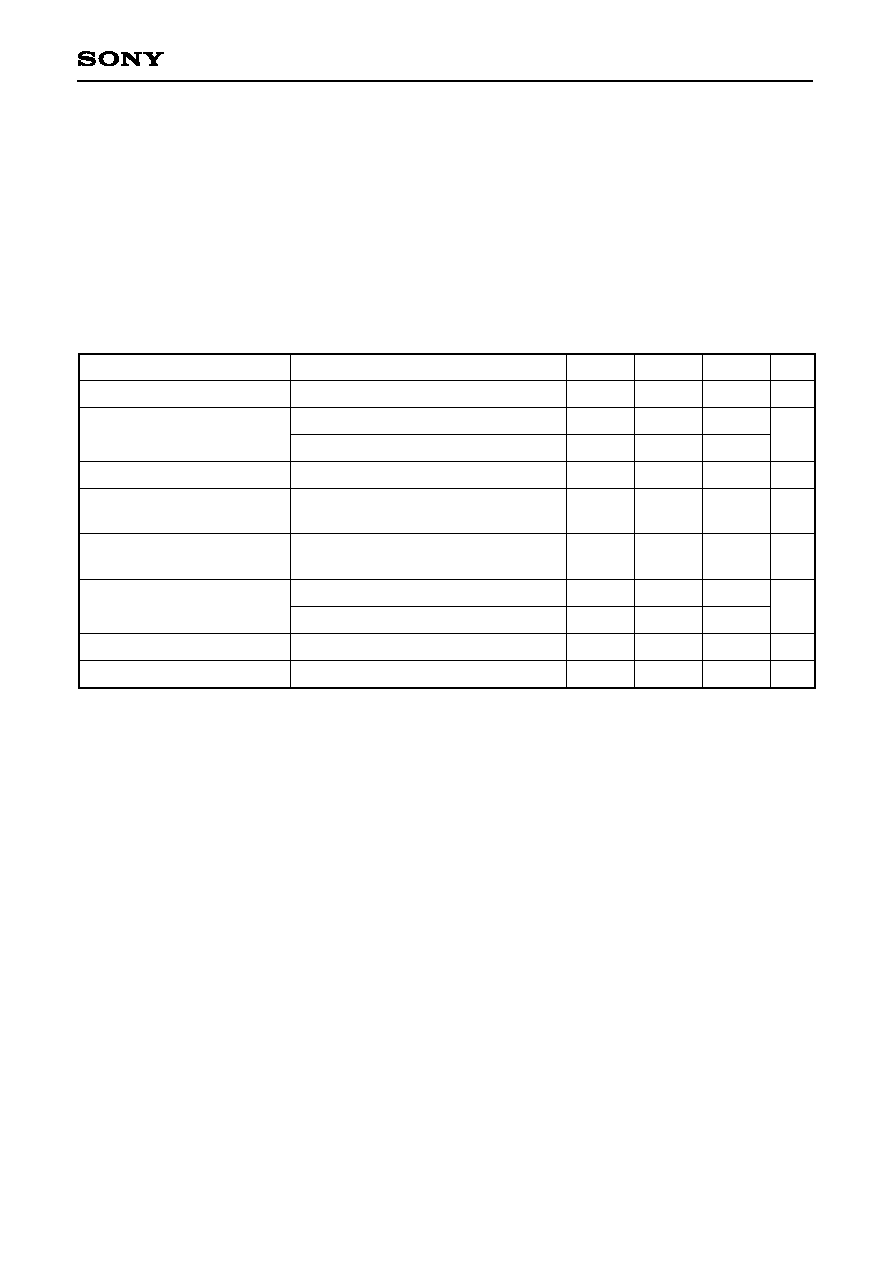

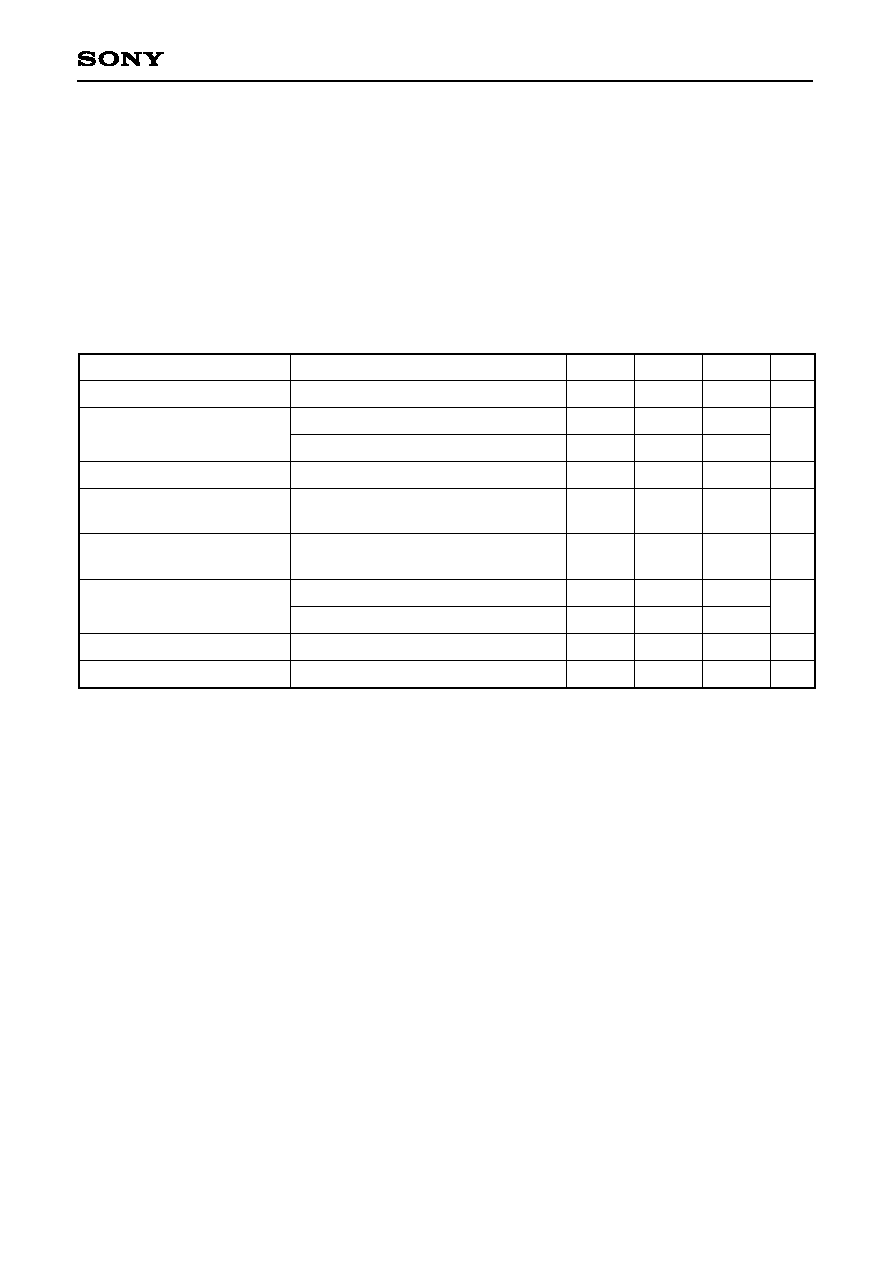

Analog Characteristics (AV

D

0 to 5 = V

DD

0 to 3 = XV

DD

= 5.0V, AV

S

0 to 5 = V

SS

0 to 7 = XV

SS

= 0.0V, Ta = 25įC,

DSP: each function = OFF, gain = 1)

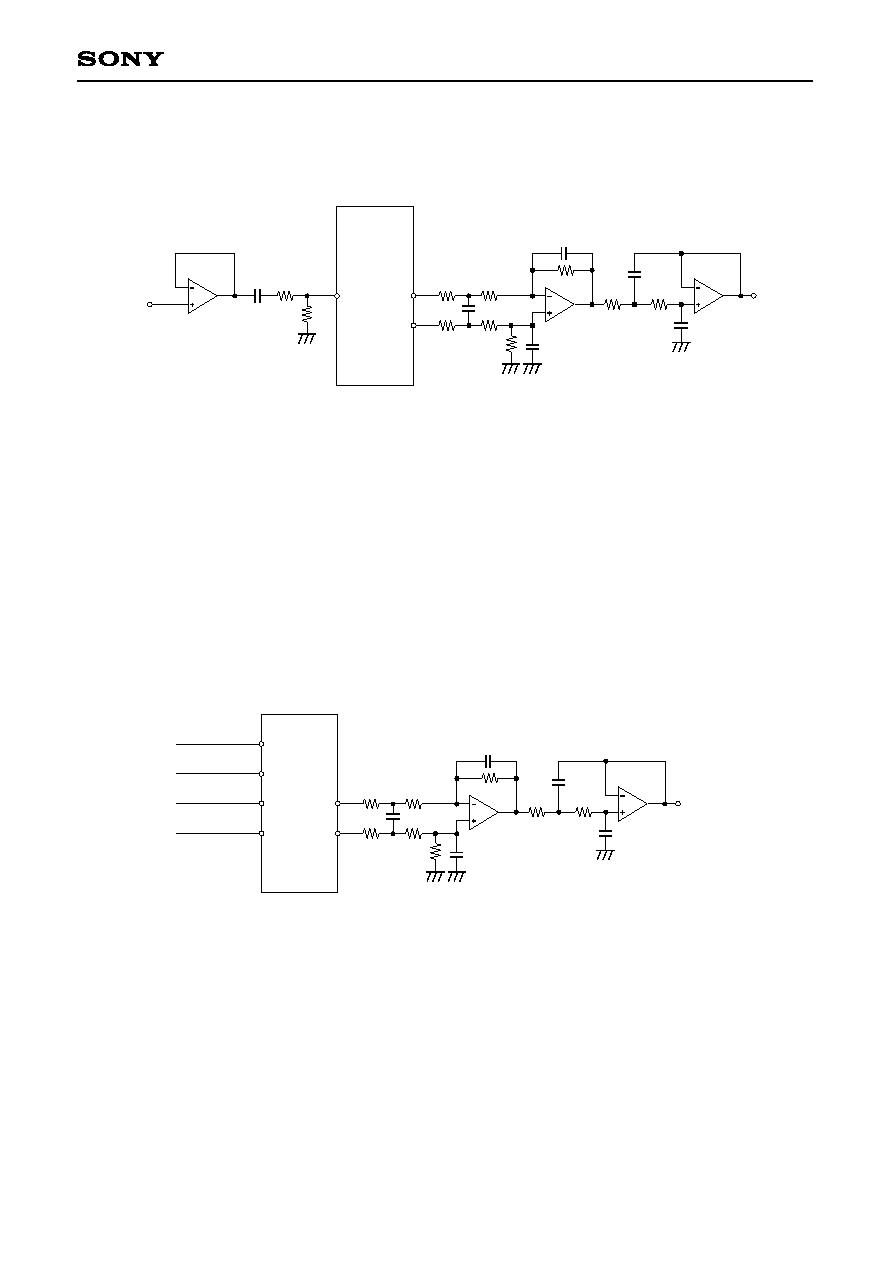

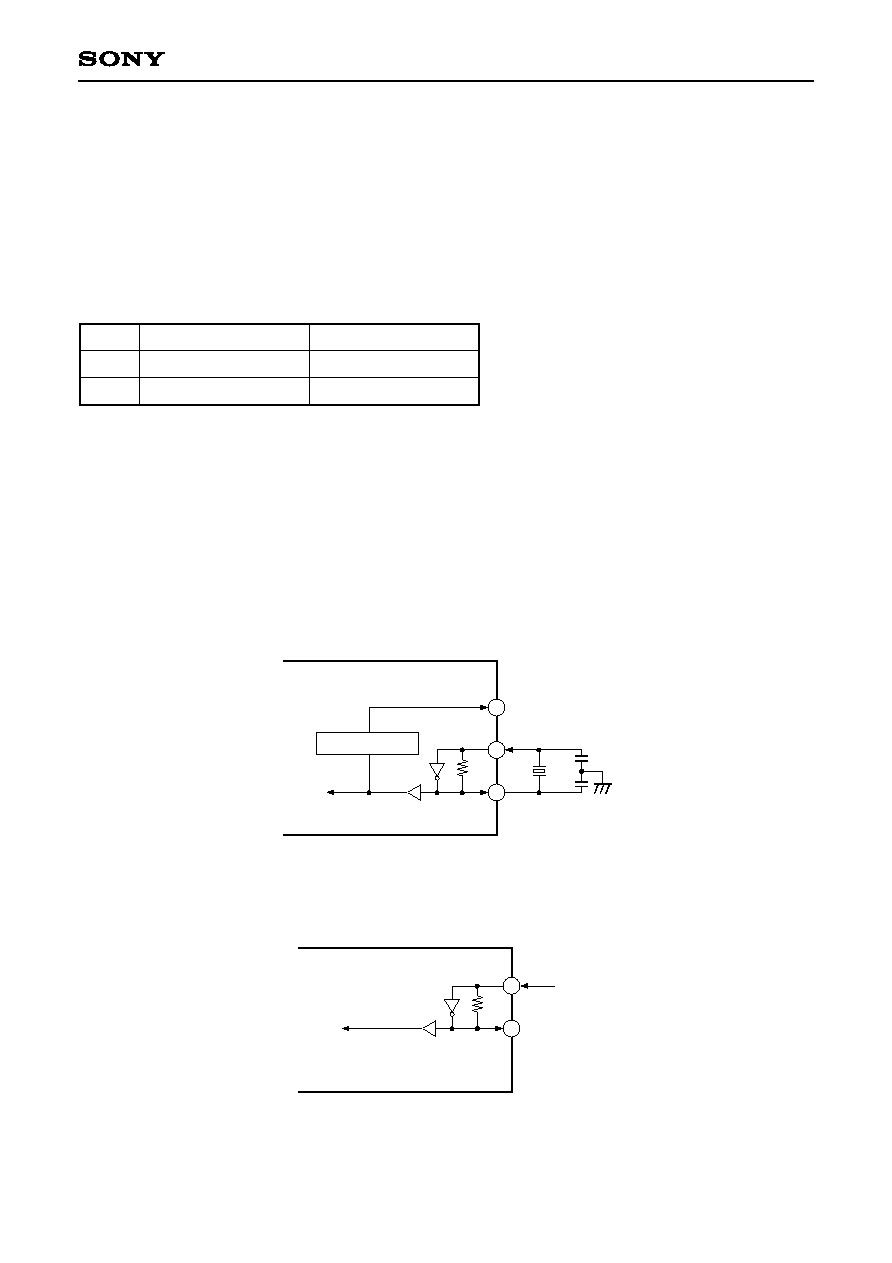

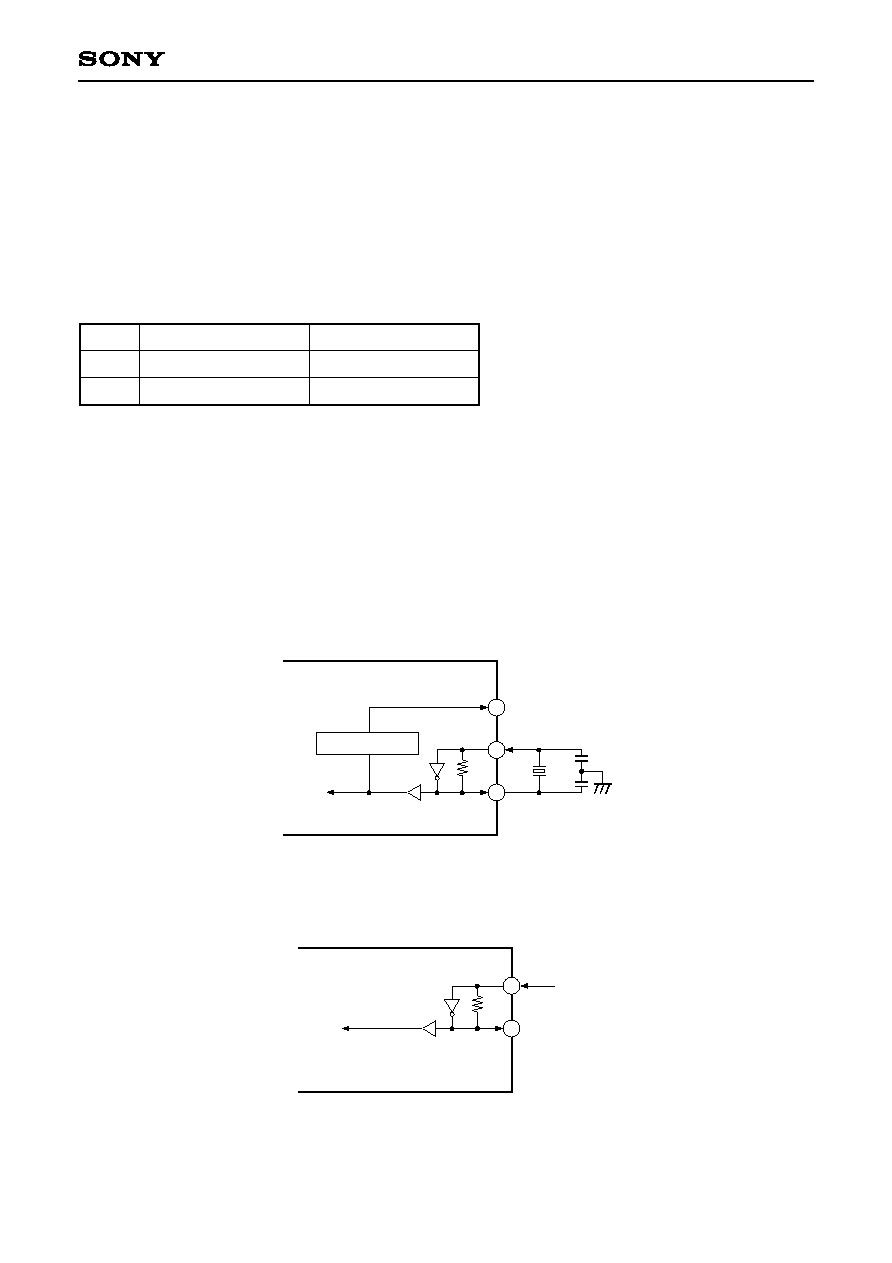

[1] ADC + DAC connection total characteristics

The measurement circuit in Figure 1-1 is used. Unless otherwise indicated, the measurement conditions are as

given below.

∑ Input signal ...1.0Vrms, 1kHz

∑ fs....................44.1kHz

∑ Rin .................0

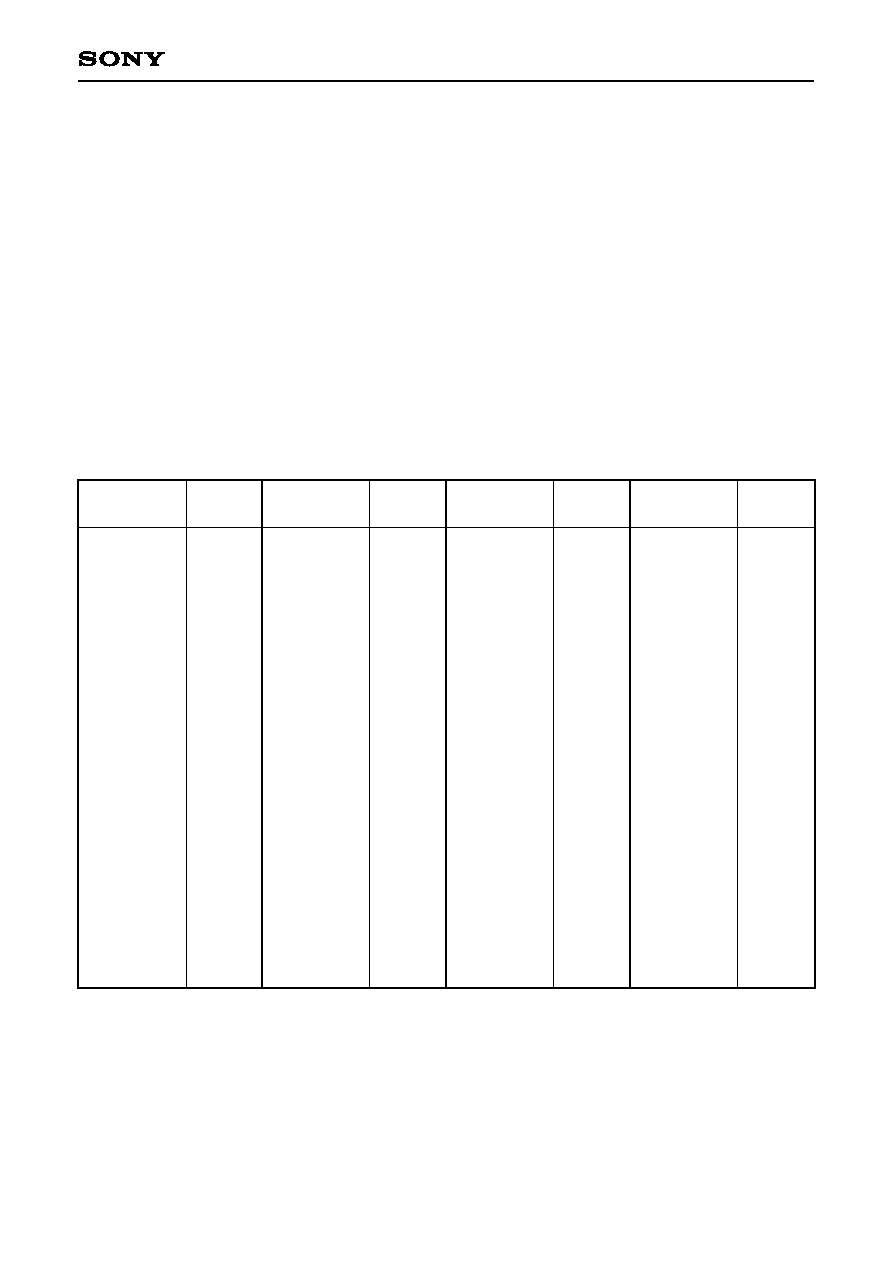

Item

S/N ratio

THD + N

Dynamic range

Channel separation

Level difference between

channels

Analog full-scale input level

ADC input impedance

Analog current consumption

1.0Vrms, EIAJ (with "A" weighting filter)

1.0Vrms, EIAJ

0.5Vrms, EIAJ

EIAJ

Only ADC characteristics using DAC1,

EIAJ

Only ADC characteristics using DAC1

Rin = 0

Rin = 22k

80

88

0.016

0.012

92

108

0.05

1.26

2.06

34.6

21

0.03

Measurement conditions

Min.

Typ.

Max.

1

Analog input level which outputs digital full scale.

An optional analog input signal level Vin (Vrms) of 1.26Vrms or more can be set in digital full scale by the

measurement circuit external resistor Rin.

The calculation formula for external resistor Rin is:

Rin = 27.5

◊

Vin ≠ 34.6 [k

] ......(1)

However, THD + N characteristics deteriorate for full-scale output as shown in Graph 1, so use of up to 80%

(when Rin = 0

, 0.8

◊

1.26 (Vrms) = 1.0 (Vrms)

"analog full scale") of the analog signal level is recommended

for digital full-scale output.

In this case, the Rin calculation formula is the same as formula (1), except that Vin becomes 1.25

◊

Vin.

Note that this change causes the output level after ADC + DAC to change.

Most of the above specifications are measurement values for analog full scale.

Unit

dB

%

dB

dB

dB

Vrms

k

mA

≠ 10 ≠

CXD2720Q

[2] DAC unit characteristics

Use the measurement circuit in Figure 1-2. Unless otherwise specified, the measurement conditions are as

follows.

∑ Input signal ....0dB, 1kHz, 16 bit

∑ fs....................44.1kHz

Item

S/N ratio

THD + N

Dynamic range

Channel separation

Level difference between

channels

Output level

EIAJ (with "A" weighting filter)

EIAJ (0dB)

EIAJ (≠1dB)

EIAJ (≠60dB)

EIAJ

EIAJ

EIAJ (Measure at OUT in Figure 1-2.)

98

0.006

0.004

98

120

0.05

2.0

dB

%

dB

dB

dB

Vrms

Measurement conditions

Min.

Typ.

Max.

Unit

Analog input level [dBV]

≠60

≠50

≠40

≠30

≠20

≠10

0

10

(1Vrms)

0.01

0.10

1.00

THD + N [%]

Digital full scale

Analog full scale

(Rin = 0

)

Graph 1.

≠ 11 ≠

CXD2720Q

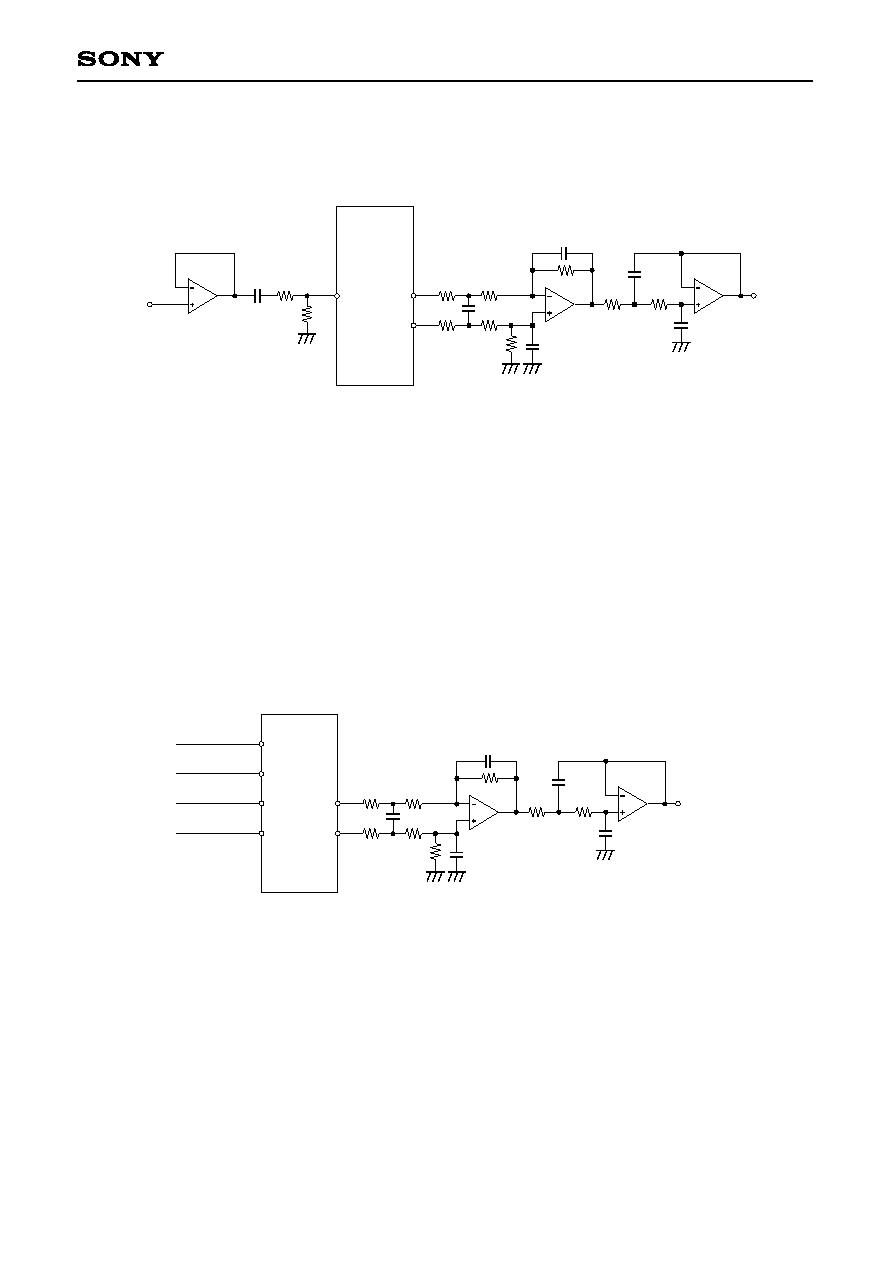

OUT

8200p

2.2k

2.2k

820p

39k

150p

22k

12k

22k

12k

330p

150p

39k

1M

Rin

10Ķ

Vin

AINx AOxN

AOxP

CXD2720Q

(Master mode)

Figure 1-1. ADC + DAC Measurement Circuit Diagram

OUT

8200p

2.2k

2.2k

820p

39k

150p

22k

12k

22k

12k

330p

150p

39k

LRCK AOxN

AOxP

CXD2720Q

(Slave mode)

SI

XTLI

BCK

768fs

48fs

fs

DATA

(fs = 44.1kHz)

Figure 1-2. DAC Measurement Circuit Diagram

≠ 12 ≠

CXD2720Q

Description of Functions

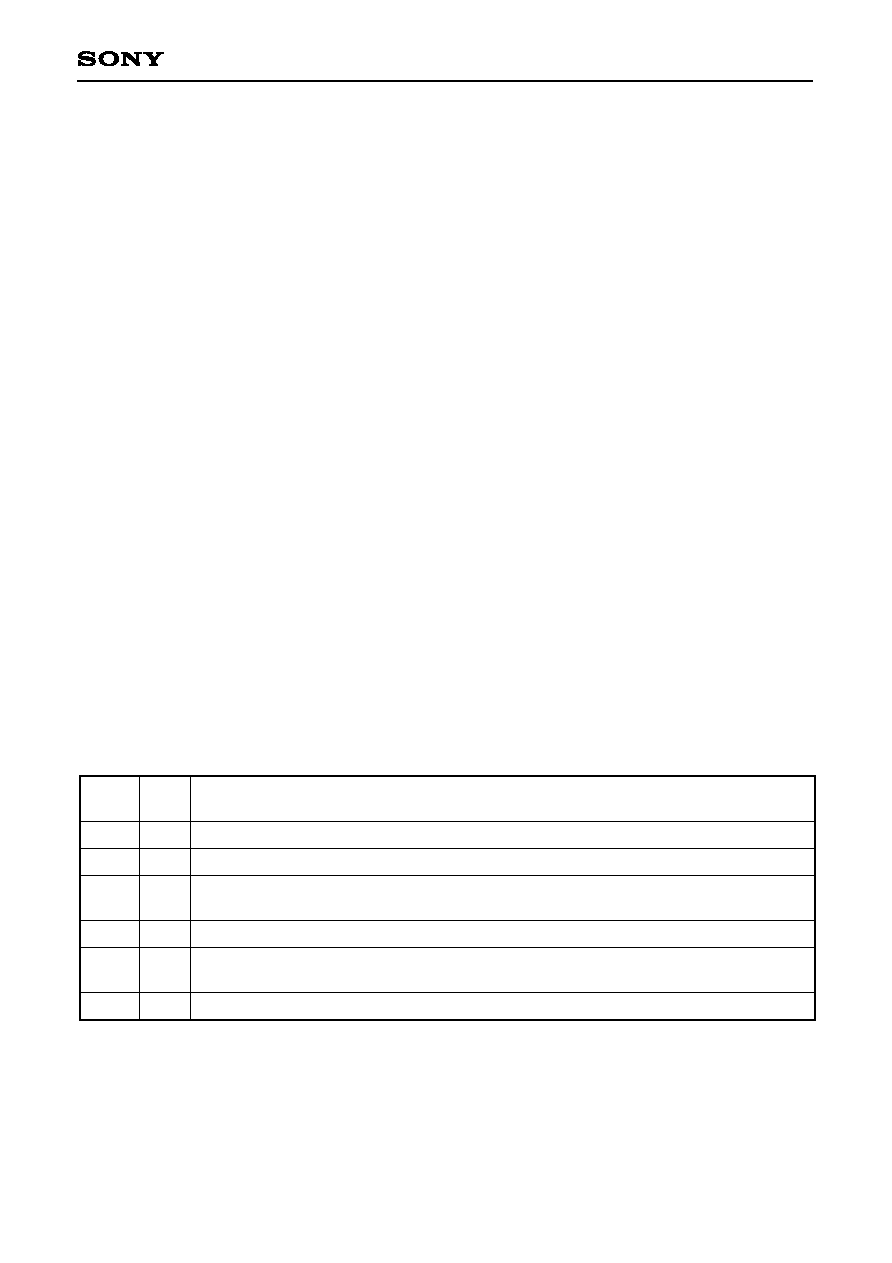

1. Master/Slave Modes

[Relevant pins] XMST, LRCK, BCK

When connecting multiple CXD2720Qs, or when using as a pair with a D/A converter such as the CXD2558M,

one of the CXD2720Q should be in master mode to supply LRCK and BCK.

The clock applied to LRCK and BCK in slave mode must be synchronized to either the crystal oscillator clock

of the XTLI and XTLO pins or the external clock input from the XTLI pin

XMST

H

L

Slave mode

Master mode

Input

Output

Mode

LRCK, BCK I/O

2. Master Clock System

[Relevant pins] XTLI, XTLO, BFOT

768fs (fs = 44.1kHz) is assumed for the master clock system, and the connection is as shown below. (Please

inquire with regard to use at other than fs = 44.1kHz.)

(1) Master

Table 1-1. LRCK, BCK Mode Setting

768fs

XTLO

Frequency divider

XTLI

BFOT

768fs

384fs

O

I

O

768fs

XTLO

XTLI

O

I

768fs

OPEN

(2) Slave

≠ 13 ≠

CXD2720Q

3. Input/Output Synchronization Circuit

[Relevant pins] LRCK, XWO

During normal operation, synchronization is performed automatically to input LRCK (in slave mode), and phase

is matched with serial input data, but if there is a lot of jitter on LRCK, or during power input, synchronization

may be impossible. In this case, forced synchronization can be done by making the XWO pin Low for 2/Fs or

more. Forced synchronization operation is done by the timing of the second LRCK rising edge after the XWO

pin is made Low. When synchronization is completed, return the XWO pin to High.

4. Reset Circuit

[Relevant pins] XRST, XTLI, XTLO

This LSI must be reset after power is turned ON.

Reset is done by making the XRST pin Low for 1/Fs or more after supply voltage satisfies the recommended

operating condition, and the crystal oscillator clock of the XTLI, XTLO pins or the external clock input from the

XTLI pin is correctly applied.

5. Serial Audio Interface (SIF)

[Relevant pins] SI, SO, BCK, LRCK, XS24, XMST

Serial data is used for the external communication of the digital audio data.

The CXD2720Q has one system each for input and output, and each one inputs/outputs 2 channels of data at

1 sampling cycles. Either the 32-bit clock mode or 24-bit clock mode can be selected. In master mode, the 32

bit clock mode is fixed.

(1) Pin Configuration

The pins shown in the table below are assigned to SIF.

Pin

name

SI

SO

BCK

LRCK

XS24

XMST

I

O

I/O

I/O

I

I

Serial input; taken synchronized to BCK.

Serial output; output synchronized to BCK.

BCK input/output; either 32-bit clock mode (64fs) or 24-bit clock mode (48fs). BCK output

supports 32-bit clock mode only.

LRCK input/output (1fs).

SI0 slot number (24/32) selection input. Low: 24-bit slot; High: 32-bit slot. Valid only in slave

mode. Set High in master mode.

BCK, LRCK master mode/slave mode switching input. Low: master mode; High: slave mode.

I/O

Function

Table 5-1. Pin Configuration

≠ 14 ≠

CXD2720Q

(2) Operation Modes

The LRCK/BCK mode and SI/SO system settings can be selected by the setup register settings as follows.

LRCK/BCK Mode Setting

Setup register

SQ11

SQ10

SQ09

LRCK format

LRCK polarity selection

BCK polarity selection relative to LRCK edge

"0" : normal,

"1" : IIS

"0" : Lch "H",

"1" : Lch "L"

"0" : edge

,

"1" : edge

Function

Contents

Table 5-2. LRCK/BCK Mode Setting

SI/O System Register Setting

SI system

Setup register

SQ08

SQ07

SQ06

SQ05

SI data list

SI frontward/rearward truncation

SI data word length

SI data word length

"0" : MSB first,

"1" : LSB first

"0" : Forward truncation,

"1" : Rearward truncation

SQ06 SQ05

0

0

: 16 bit

1

1

: 24 bit

Function

Contents

Table 5-3. SI System Register Setting

SO system

Setup register

SQ04

SQ03

SQ02

SQ01

SO data list

SO forward/rearward truncation

SO data word length

"0" : MSB first,

"1" : LSB first

"0" : Forward truncation,

"1" : Rearward truncation

SQ02 SQ01

0

0

: 16 bit

0

1

: 18 bit

1

0

: 20 bit

1

1

: 24 bit

Function

Contents

Table 5-4. SO System Register Setting

≠ 15 ≠

CXD2720Q

(3) SIF Format

Serial I/F have one input/output system each, and except for slot number, the following formats can be set for

input and output, independently, by setting the setup register. It can also be made to support IIS format, to

enable connection to Philips and other devices. The timing charts for each data format are given on the

following pages.

32-bit slot (XS24 = High)

MSB first

24 bit

Forward truncation

MSB first

16 bit

Forward truncation

LSB first

24 bit

Rearward truncation

1

0

1

SQ05 SQ06 SQ07

1

0

1

0

1

1

SQ08

0

0

1

Supplement

Supports 20, 16 bits

Supports 20, 16 bits

SI format

Setup register

Table 5-5. 32-bit Slot Serial IN

MSB first

16 bit

Rearward truncation

MSB first

18 bit

Rearward truncation

MSB first

20 bit

Rearward truncation

MSB first

24 bit

Rearward truncation

MSB first

24 bit

Forward truncation

LSB first

24 bit

Rearward truncation

0

1

0

1

1

1

SQ01 SQ02 SQ03

0

0

1

1

1

1

1

1

1

1

0

1

SQ04

0

0

0

0

0

1

SI format

Setup register

Table 5-6. 32-bit Slot Serial OUT

24-bit slot (XS24 = Low)

MSB first

16 bit

Rearward truncation

MSB first

24 bit

LSB first

24 bit

0

1

1

SQ05 SQ06 SQ07

0

1

1

1

SQ08

0

0

1

Supplement

Supports 20, 16 bits for forward

truncation

Supports 20, 16 bits for rearward

truncation

SI format

Setup register

Table 5-7. 24-bit Slot Serial IN

MSB first

16 bit

Rearward truncation

MSB first

18 bit

Rearward truncation

MSB first

20 bit

Rearward truncation

MSB first

24 bit

LSB first

24 bit

0

1

0

1

1

SQ01 SQ02 SQ03

0

0

1

1

1

1

1

1

SQ04

0

0

0

0

1

SI format

Setup register

Table 5-8. 24-bit Slot Serial OUT

Note 1) When performing 20-bit and 16-bit data input in serial IN 24-bit data format, fill the lower 4 and 8 bits

with "0", respectively.

Note 2)

means "don't care".

≠ 16 ≠

CXD2720Q

Invalid

Invalid

23

22

21

20

19

18

17

16

15

14

13

12

11

10

09

08

07

06

05

04

03

02

01

00

LSB

MSB

23

22

21

20

19

18

17

16

15

14

13

12

11

10

09

08

07

06

05

04

03

02

01

00

LSB

MSB

15

14

13

12

11

10

09

08

07

06

05

04

03

02

01

00

LSB

MSB

15

14

13

12

11

10

09

08

07

06

05

04

03

02

01

00

LSB

MSB

Invalid

Invalid

00

01

02

03

04

05

06

07

08

09

10

11

12

13

14

15

16

17

18

19

20

21

22

23

MSB

LSB

Invalid

00

01

02

03

04

05

06

07

08

09

10

11

12

13

14

15

16

17

18

19

20

21

22

23

MSB

LSB

Invalid

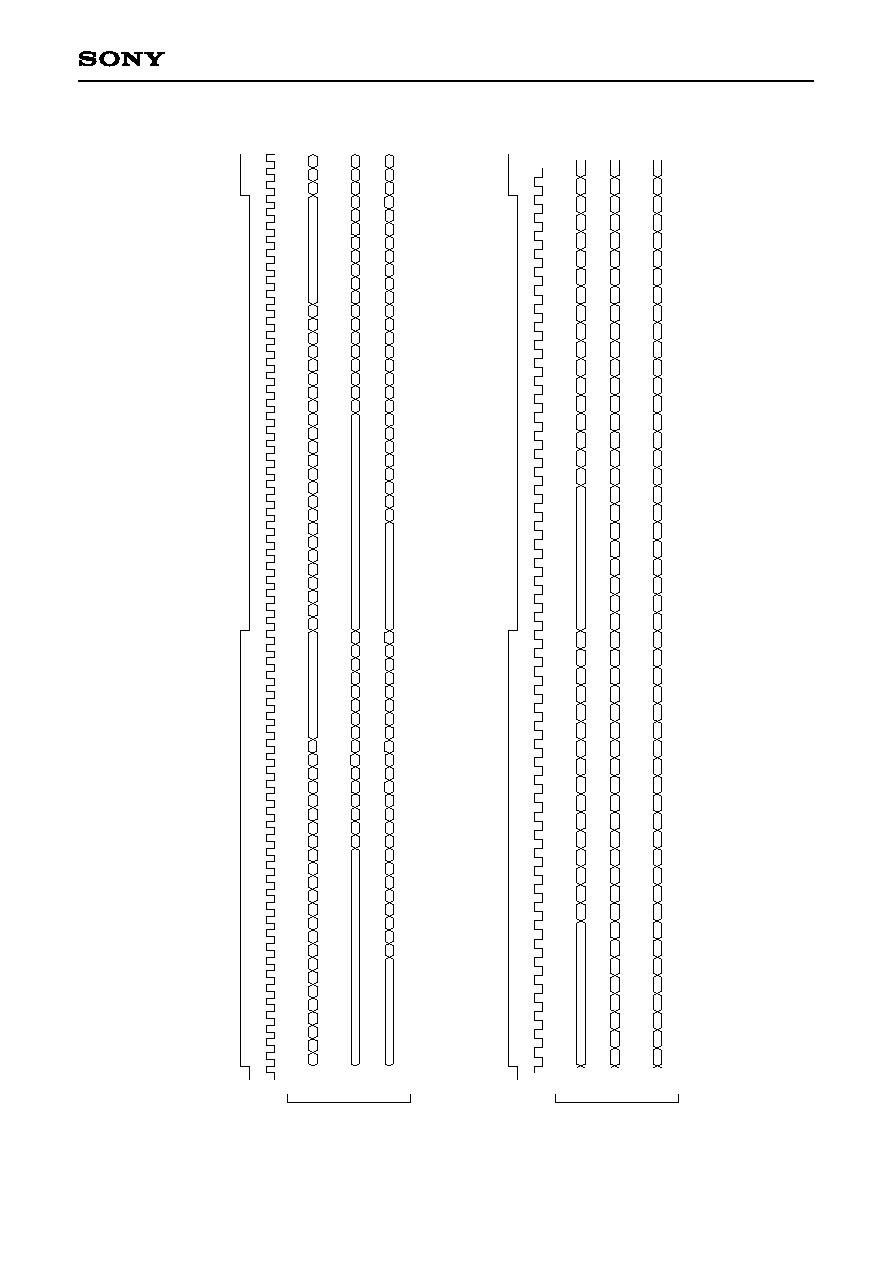

LRCK

BCK

32 bit slot

∑ MSB first 24 bits forward truncation

∑ MSB first 16 bits rearward truncation

∑ LSB first 24 bits rearward truncation

SI

Lch

Rch

Invalid

00

LRCK

BCK

24 bit slot

∑ MSB first 16 bits rearward truncation

∑ MSB first 24 bits

∑ LSB first 24 bits

SI

Lch

Rch

01

02

03

04

05

06

07

08

09

10

11

12

13

14

15

16

17

18

19

20

21

22

23

00

01

02

03

04

05

06

07

08

09

10

11

12

13

14

15

16

17

18

19

20

21

22

23

LSB

MSB

LSB

MSB

23

22

21

20

19

18

17

16

15

14

13

12

11

10

09

08

07

06

05

04

03

02

01

00

23

22

21

20

19

18

17

16

15

14

13

12

11

10

09

08

07

06

05

04

03

02

01

00

MSB

LSB

MSB

LSB

15

14

13

12

11

10

09

08

07

06

05

04

03

02

01

00

15

14

13

12

11

10

09

08

07

06

05

04

03

02

01

00

LSB

LSB

Invalid

MSB

MSB

Digital Audio Data Input Timing (with polarities: SQ11 = 0, SQ10 = 0, SQ09 = 0)

Figure 5-1.

≠ 17 ≠

CXD2720Q

LSB

MSB

23

22

21

20

19

18

17

16

15

14

13

12

11

10

09

08

07

06

05

04

03

02

01

00

23

22

21

20

19

18

17

16

15

14

13

12

11

10

09

08

07

06

05

04

03

02

01

00

LSB

MSB

LRCK

BCK

32 bit slot

∑ MSB first 24 bits forward truncation

15

14

13

12

11

10

09

08

07

06

05

04

03

02

01

00

LSB

MSB

15

06

14

13

12

11

10

09

08

07

05

04

03

02

01

00

LSB

MSB

∑ MSB first 16 bits rearward truncation

SO

Lch

Rch

LRCK

BCK

24 bit slot

∑ MSB first 16 bits rearward truncation

∑ MSB first 24 bits

∑ LSB first 24 bits

SO

Lch

Rch

00

01

02

03

04

05

06

07

08

09

10

11

12

13

14

15

16

17

18

19

20

21

22

23

00

01

02

03

04

05

06

07

08

09

10

11

12

13

14

15

16

17

18

19

20

21

22

23

LSB

MSB

LSB

MSB

23

22

21

20

19

18

17

16

15

14

13

12

11

10

09

08

07

06

05

04

03

02

01

00

23

22

21

20

19

18

17

16

15

14

13

12

11

10

09

08

07

06

05

04

03

02

01

00

MSB

LSB

MSB

LSB

15

14

13

12

11

10

09

08

07

06

05

04

03

02

01

00

15

14

13

12

11

10

09

08

07

06

05

04

03

02

01

00

LSB

LSB

MSB

MSB

∑ MSB first 20 bits rearward truncation

19

18

17

16

15

14

13

12

11

10

09

08

07

06

05

04

03

02

01

00

19

18

17

16

15

14

13

12

11

10

09

08

07

06

05

04

03

02

01

00

MSB

LSB

MSB

LSB

∑ MSB first 18 bits rearward truncation

17

16

15

14

13

12

11

10

09

08

07

06

05

04

03

02

01

00

17

16

15

14

13

12

11

10

09

08

07

06

05

04

03

02

01

00

MSB

LSB

MSB

LSB

00

01

02

03

04

05

06

07

08

09

10

11

12

13

14

15

16

17

18

19

20

21

22

23

MSB

LSB

00

01

02

03

04

05

06

07

08

09

10

11

12

13

14

15

16

17

18

19

20

21

22

23

MSB

LSB

∑ LSB first 24 bits rearward truncation

" 0 " truncation

" 0 " truncation

" 0 " truncation

LSB

MSB

LSB

MSB

23

22

21

20

19

18

17

16

15

14

13

12

11

10

09

08

07

06

05

04

03

02

01

00

23

22

21

20

19

18

17

16

15

14

13

12

11

10

09

08

07

06

05

04

03

02

01

00

∑ MSB first 24 bits rearward truncation

LSB

MSB

LSB

MSB

19

18

17

16

15

14

13

12

11

10

09

08

07

06

05

04

03

02

01

00

19

06

18

17

16

15

14

13

12

11

10

09

08

07

05

04

03

02

01

00

∑ MSB first 20 bits rearward truncation

LSB

MSB

LSB

MSB

17

16

15

14

13

12

11

10

09

08

07

06

05

04

03

02

01

00

17

16

15

14

13

12

11

10

09

08

07

06

05

04

03

02

01

00

∑ MSB first 18 bits rearward truncation

" 0 " truncation

Digital Audio Data Output Timing (with polarities: SQ11 = 0, SQ10 = 0, SQ09 = 0)

Figure 5-2.

≠ 18 ≠

CXD2720Q

6. Microcomputer Interface

[Relevant pins] RVDT, TRDT, SCK, XLAT, REDY

The CXD2720Q performs serial audio interface format setting, volume, coefficient settings of microphone echo

delay amount and others by serial data from the microcomputer.

Further, bidirectional communication such as internal data read from the CXD2720Q to the microcomputer can

be done at the rate of once in 1 LRCK.

(1) Pin Structure

The five external pins indicated in the table below are allocated for microcomputer interface.

Microcomputer interface begins operation when XLAT is received, so RVDT, TRDT, SCK and REDY are

connected in common, and by controlling (wiring) only XLAT separately, multiple CXD2720Qs can be used.

Pin

name

RVDT

TRDT

SCK

XLAT

REDY

I

O

I

I

O

Serial data input from microcomputer.

Serial data output to microcomputer. High impedance state unless this pin is set to internal

data read state by the microcomputer. Therefore, it is preferable to perform pull-up or pull-

down so that potential is not unstable when this pin is not active.

Shift clock for serial data. Input data from RVDT is taken according to SCK rise, and output

data from TRDT is sent out according to SCK fall.

Interprets the 8 bits of RVDT before this signal rises as transmission mode data, and the

bits before that as address data.

Transmission prohibited while at Low level. Transmission enabled at High. This pin is an

open drain, and must be pulled up externally.

I/O

Function

Table 6-1. Microcomputer Interface External Pins

≠ 19 ≠

CXD2720Q

(2) Description of Communication Formats

The data transmission timing between the microcomputer interface and coefficient RAM and setup register is

called the SV cycle, and is generated once in 1LRCK.

The SV cycle is generated immediately preceding the signal processing program, so it has absolutely no effect

on signal processing, and there is no risk of the sound being cut.

In read/write modes,

Address section + Mode section + Data section

act as one package of data to perform data transmission between the microcomputer and the CXD2720Q.

[Write] ∑ For coefficient RAM

Address section (8 bits)

Mode section (8 bits)

Data section (16 bits)

A0

A7

M0

M7

D0

D15

RVDT

SCK

XLAT

REDY

TRDT

[Read] ∑ For coefficient RAM

Address section (8 bits) Mode section (8 bits)

Data section (16 bits)

A0

A7

M0

M7

D0

D15

RVDT

SCK

XLAT

REDY

TRDT

Note) For both read and write, the data section is 24 bits for the setup register.

Figure 6-1. Examples of Communication

≠ 20 ≠

CXD2720Q

(3) Data Structure

Data structure is classified in three types, as shown in the table below. All data communication is done with

LSB first.

Name

A0 to A7

M0 to M7

D0 to D15/SQ00 to SQ23

8

8

16/24

Address section

Transmission

mode section

Data section

Coefficient RAM is 16 bits; setup register is

24 bits

Bit length

Contents

Remarks

(3)-1. Transmission Mode Section

The transmission mode section is 8 bits and has the following functions.

Bit

M7

M6

M5

M4

M3

M2

M1

M0

0: ON (No sound)

1: OFF

VS1

VS0

0

0

Setup register

1

0

Coefficient RAM (K-RAM)

0: Receive

1: Send

XVMT

VS1

VS0

VRD

SO Mute

Reserve

Data type

Reserve

Send/Receive

Name

Function

(3)-2. Address Section

The coefficient RAM has a 192-word structure, so the address section is 8 bits. The setup register has a 1-

word structure, so the address section data may be optional.

(3)-3. Data Section

Sixteen SCK are required, as the coefficient RAM has a 16-bit structure (D0 to D15). The setup register has a

24-bit structure (SQ00 to SQ23), so twenty-four SCK are required.

Table 6-2. Data Structure

Table 6-3. Transmission Mode Section

Note) Polarity as seen from the CXD2720Q

≠ 21 ≠

CXD2720Q

(4) Details of Communication Methods

The definitions of signal timing required for control from the microcomputer are given below.

(4)-1. Write

First, address section data and mode section data are sent from the microcomputer, synchronized to SCK, to

the RVDT pin.

The address section data is 8 bits both for the coefficient RAM and setup register, and the setup register

transmits optional data for 1 word length. Address section data is sent with LSB first.

Mode section data is fixed at 8 bits regardless of content.

The phase relationship between SCK and RV data (data applied to the RVDT pin) has the following restrictions:

∑ RV data must be verified before SCK rise (

t

DS

20ns).

∑ RV data must be held for 1

t

+ 20ns or more after SCK rise (

t

DH

).

SCK itself has the following restrictions:

∑ SCK Low level must be 1

t

+ 20ns or more (

t

SWL

).

∑ SCK High level must also be 1

t

+ 20ns or more (

t

SWH

).

After raising SCK which corresponds to mode section final data, XLAT is raised (

t

SLP

20ns). XLAT Low level

width must be maintained at 1

t

+ 20ns or more (

t

LWL

). Further, fall timing restrictions are:

∑ for the preceding transmission, if REDY falls due to SCK, as for write, 3

t

+ 20ns or more is required. (

t

SLD

)

∑ for the preceding transmission, if REDY falls due to XLAT, as for read, 20ns or more is required. (

t

LDR

)

Further, if preceding transmissions have been performed and REDY = Low, it is necessary to wait for REDY =

High to raise XLAT.

The procedure until this point is the same for write and read.

A0

RVDT

A7

M0

M7

SQ00

SQ23

A0

M7

SCK

XLAT

REDY

TRDT

t

DS

t

DH

t

SWL

t

SWH

t

LSD

t

SLP

t

SS

t

BSP

t

SLP

t

SLD

t

SBD

t

LDR

t

RLP

t

RLP

t

LWL

t

LDR

t

SLD

or t

LWH

High-Z

D0/SQ00

D15/SQ23

Figure 6-2. Write Timing

≠ 22 ≠

CXD2720Q

Data section write begins after XLAT rise, and here also transmission must be with LSB first, with

t

DS

and

t

DH

restrictions. In addition, after raising XLAT at the starting point for sending to the data section, wait for 3

t

+

20ns or more for the first SCK rise. (

t

LSD

)

When 16 bits (coefficient RAM) or 24 bits (setup register) of this write is repeated, REDY = Low within 4

t

+ 50ns,

and the microcomputer is informed of waiting status for the SV cycle, which is the dedicated data rewrite cycle

by microcomputer interface. (

t

SBD

)

When REDY goes High again, the corresponding data is written.

The next communication restarts by using the REDY signal as follows.

∑ When REDY = Low, the SCK for the next transmission can rise (

t

BSP

20ns ).

∑ In the same way, when REDY = Low, the XLAT for the next transmission can fall (

t

LDR

20ns).

REDY will fall due to this transmission, but it is prohibited for XLAT to rise for the next transmission before the

REDY rises. Be sure to raise the next XLAT after REDY falls (

t

RLP

20ns ).

In order to restart the next transmission without using the REDY signal, the following conditions must be observed:

∑ There should be 2

t

+ 40ns or more left between the SCK rise for the final data section and the SCK rise for

the next transmission (

t

SS

).

∑ In the same way, the XLAT for the next transmission can fall after waiting 3

t

+ 20ns or more after the final

data section SCK rise (

t

SLD

).

The

t

ss and

t

SLD

here are shorter times than

t

SBD

4

t

+ 50ns, so the restriction conditions are not much strict.

However, even in this case the rise of XLAT for the next transmission must come after REDY rise (

t

RLP

20ns).

Further, the restriction for XLAT fall at the starting point of this write from

t

SLD

can be:

∑

t

SLD

3

t

+ 20ns if the preceding transmission was "write".

≠ 23 ≠

CXD2720Q

(4)-2. Read

First, address section and mode section data are transmitted synchronized to SCK, and XLAT is raised

matched with this; the procedure until this point is the same as for write, so the description is omitted here.

Read differs from write in that after XLAT rise, REDY falls within 3

t

+ 50ns (

t

LBD

), and the microcomputer is

informed of SV cycle waiting.

At this time, the TRDT pin changes from high-impedance state to active state (

t

LDN

3

t

+ 80ns) simultaneously

with REDY fall. When the read data is ready, the REDY pin changes from Low to High. When the data read out

from the TRDT pin is made TR, and SCK falls (

t

RSDP

20ns) when the REDY pin goes High, the first TR data

is defined within 2

t

+ 70ns (

t

SDD

). The microcomputer reads this data at SCK rise. The TR data is read in order

from the LSB with 16 bits for the coefficient RAM and 24 bits for the setup register by adding SCK, the

corresponding data is all read, and then read is completed.

Next, the method for restarting transmission after read is completed is described.

As in Case 1, there is a method for sending address section and mode section data consecutively after reading

all of the 16- or 24-bit data. There should be 2

t

+ 40ns or more left between the SCK rise for the final data read

and the next SCK rise (

t

ss), and this is established by the conditions

t

SWL

1

t

+ 20ns and

t

SWH

1

t

+ 20ns.

Further, at this read REDY changes from High to Low, but it is prohibited for the XLAT for the next

transmission to fall before this. If REDY = Low has been verified, XLAT can fall (

t

LDR

20 ns).

Also, while 16- or 24-bit data is being read from the TRDT pin, address and mode section data writing to the

RVDT pin for the next transmission can be started.

In Case 3, the final section of read data and the final data in the mode section overlap, and this allows shifting

to the next transmission processing in the shortest possible time after data read.

It is also possible to have data read and address and mode section write overlap partially, as shown by Case 2.

≠ 24 ≠

CXD2720Q

A0

t

DS

t

DH

t

SLD

or t

LWH

RVDT

SCK

A7

M0

M7

A1

M7

A0

SQ00

SQ23

SQ22

XLAT

REDY

TRDT

t

SWL

t

SWH

t

SLP

t

RSDP

t

SS

t

SLP

t

LDR

t

LDR

t

RLP

t

SDD

t

SDD

t

SDD

t

SDF

D15/SQ23

D0/SQ00

D14/SQ22

t

LDN

t

LBD

t

LWL

case1

A0

t

DS

t

DH

t

SLD

or t

LWH

RVDT

SCK

A7

M0

M7

A6

M7

A5

SQ00

SQ23

SQ22

XLAT

REDY

TRDT

t

SWL

t

SWH

t

SLP

t

RSDP

t

SS

t

SLP

t

LDR

t

LDR

t

RLP

t

SDD

t

SDD

t

SDD

t

SDF

D15/SQ23

D0/SQ00

D14/SQ22

t

LDN

t

LBD

t

LWL

case2

A0

t

DS

t

DH

t

SLD

or t

LWH

RVDT

SCK

A7

M0

M7

M7

SQ00

SQ23

SQ22

XLAT

REDY

TRDT

t

SWL

t

SWH

t

SLP

t

RSDP

t

SLP

t

LDR

t

LDR

t

RLP

t

SDD

t

SDD

t

SDD

D15/SQ23

D0/SQ00

D14/SQ22

t

LDN

t

LBD

t

LWL

case3

Figure 6-3. Read Timing

≠ 25 ≠

CXD2720Q

7. Setup Register

When the setup register is selected for microcomputer interface transmission mode, the following settings are

possible for serial audio interface and DAC.

Data

section bit

Control

When system reset is Low

SQ23 to 12

SQ11

SQ10

SQ09

SQ08

SQ07

SQ06, 05

SQ04

SQ03

SQ02, 01

SQ00

Reserve bit

LRCK format

LRCK polarity selection

BCK polarity selection

relative to LRCK edge

SI data list

SI frontward/rearward

truncation

SI data word length

SO data list

SO frontward/rearward

truncation

SO data word length

DAC forced mute

Must be Low for setup register setting

change

0: normal

1: IIS

0: Lch High

1: Lch Low

0: Falling edge

1: Rising edge

0: MSB first

1: LSB first

(24-bit rearward truncation)

0: Frontward truncation

(valid only for MSB first/24 bits/32 slots)

1: Rearward truncation

SQ06

SQ05

0

0

: 16 bits

1

1

: 24 bits

0: MSB first

1: LSB first

0: Frontward truncation

1: Rearward truncation

SQ02

SQ01

0

0

: 16 bits

0

1

: 18 bits

1

0

: 20 bits

1

1

: 24 bits

0: ON

1: OFF

All Low

Normal

Lch High

Falling edge

MSB first

Frontward truncation

16 bits

LSB first

Frontward truncation

16 bits

ON

Table 7-1.

≠ 26 ≠

CXD2720Q

8. Coefficient RAM Setting

When the coefficient RAM is selected in microcomputer interface transmission mode, the coefficient parameters

such as each section's volumes and microphone echo delay amount can be set. Data settings other than those

given following in Tables 8-1 and 8-2 are "don't care".

(1) Fixed Values for System Initialization

When the system is initialized, the coefficient RAM must be set at the fixed values, shown below, due to

internal operation.

Address

01H

02H

03H

0DH

12H

13H

14H

15H

16H

17H

19H

1AH

1BH

1DH

20H

21H

23H

24H

25H

26H

27H

28H

2DH

30H

32H

41H

46H

50H

58H

68A9H

5121H

0000H

0000H

8B2AH

3BF7H

38DFH

4E77H

2E90H

0000H

0000H

2000H

4000H

4000H

0010H

4000H

4000H

1600H

2A00H

3FF0H

8000H

0000H

0008H

0000H

0000H

8000H

0000H

0008H

0008H

Fixed value

Table 8-1.

For Fs = 44.1kHz. Please inquire with regard to use at other than Fs = 44.1kHz, as the fixed values change.

≠ 27 ≠

CXD2720Q

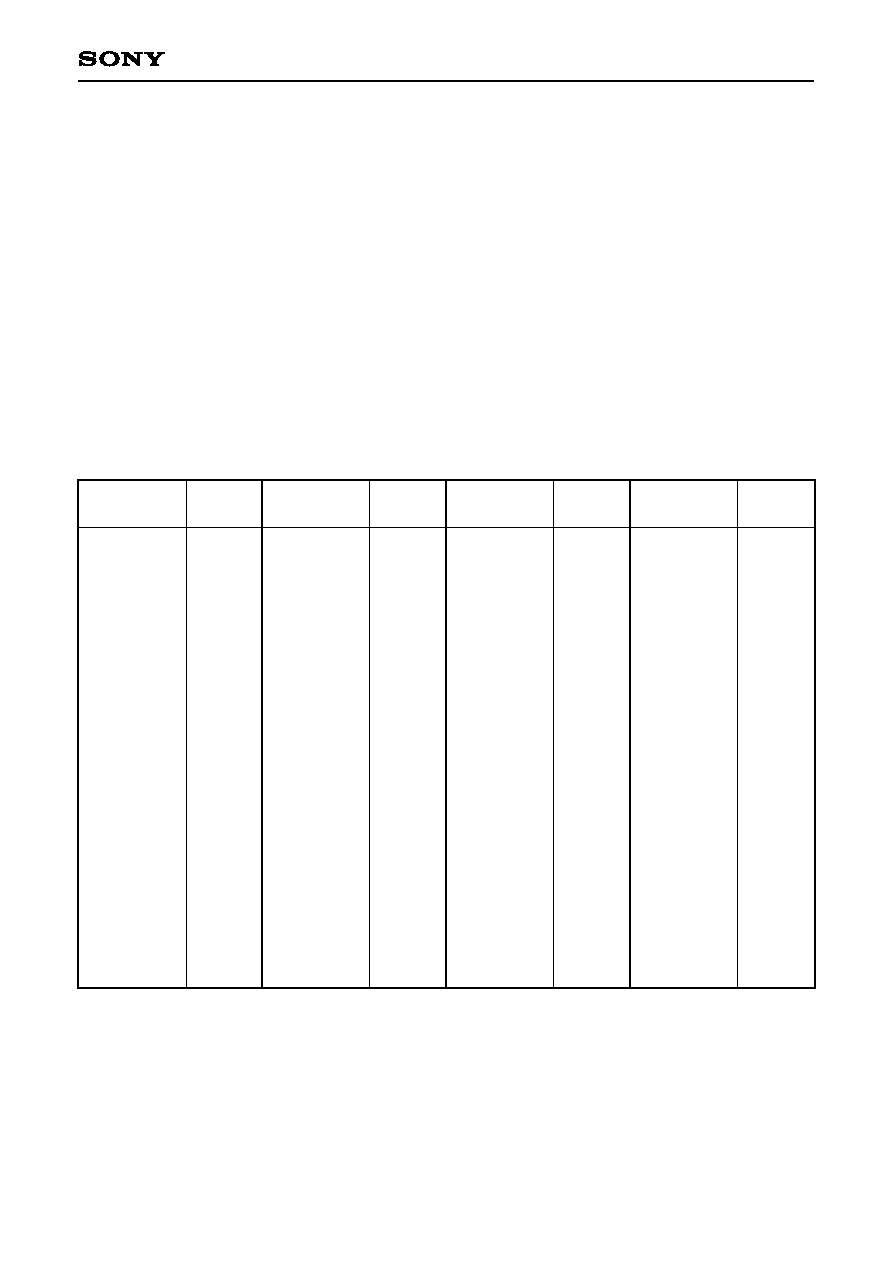

(2) Setting Data

The relationships between the coefficient RAM and each function during DSP operation are as follows.

Address

00H

04H

05H

06H

07H

08H

09H

0AH

0BH

0CH

0EH

0FH

10H

11H

18H

22H

2EH

31H

33H

34H

35H

36H

37H

38H

39H

3AH

3BH

3CH

3DH

3EH

3FH

40H

42H

44H

45H

Ki

Ke

KisLm

KisRc

KiaLm

KiaRc

KisRm

KisLc

KiaRm

KiaLc

DC1sw

DC1f0

PL

PR

Kvc

nRpR

Ks

Kimc

DC2f0

DC2sw

PEQa

PEQb1

PEQb2

PEQg

HC1a1

HC1a0

HC1b

Kdry

Keff

KLm

KRm

KLo

KRo

Tdo

Kre

SI data input level control

De-emphasis ON/OFF

SI CH1 data

Lch mix

SI CH2 data

Lch mix

ADC CH1 data

Lch mix

ADC CH2 data

Lch mix

SI CH2 data

Rch mix

SI CH1 data

Rch mix

ADC CH2 data

Rch mix

ADC CH1 data

Rch mix

DC cut1 ON/OFF for accompaniment

DC cut1 cut-off frequency for accompaniment

Panpot volume for voice cancellation

Panpot volume for voice cancellation

Voice cancelling ON/OFF

Pitch ratio for accompaniment

Key control ON/OFF for accompaniment

Microphone input level control

DC cut2 cut-off frequency for voice

DC cut2 ON/OFF for voice

PEQ coefficient for voice

PEQ coefficient for voice

PEQ coefficient for voice

PEQ coefficient for voice

High cut1 for voice

High cut1 for voice

High cut1 for voice

Microphone input direct sound mix

Microphone input echo mix

Key control output Lch mix for accompaniment

Key control output Rch mix for accompaniment

System volume Lch

System volume Rch

Microphone echo delay amount

Microphone echo read tap volume

Refer to Table 12-1 for setting value

ON/AC19H; OFF/0000H

Refer to Table 12-1 for setting value

Refer to Table 12-1 for setting value

Refer to Table 12-1 for setting value

Refer to Table 12-1 for setting value

Refer to Table 12-1 for setting value

Refer to Table 12-1 for setting value

Refer to Table 12-1 for setting value

Refer to Table 12-1 for setting value

ON/4000H; OFF/0000H

Refer to Table 14-1 for setting value

Refer to Table 9-1 for setting value

Refer to Table 9-1 for setting value

ON/8000H; OFF/0000H

Refer to Table 10-1 for setting value

ON/8000H; OFF/0000H

Refer to Table 12-1 for setting value

Refer to Table 14-1 for setting value

ON/4000H; OFF/0000H

Refer to Table 14-4 for setting value

Refer to Table 14-4 for setting value

Refer to Table 14-4 for setting value

Refer to Table 14-5 for setting value

Refer to Table 14-2 for setting value

Refer to Table 14-2 for setting value

Refer to Table 14-2 for setting value

Refer to Table 12-1 for setting value

Refer to Table 12-1 for setting value

Refer to Table 12-1 for setting value

Refer to Table 12-1 for setting value

Refer to Table 12-1 for setting value

Refer to Table 12-1 for setting value

Refer to Table 11-1 for setting value

Refer to Table 12-2 for setting value

Name

Function

Setting value

Table 8-2 (1). Coefficient RAM Setting Data (1/2)

≠ 28 ≠

CXD2720Q

Address

47H

49H

4AH

4BH

4CH

4DH

53H

5AH

5BH

Tre

Krd

Kfb

HC2a1

HC2a0

HC2b

VnRpR

Krmc

Krmp

Microphone echo read tap address

Microphone echo input sound mix

Microphone echo reverberation sound mix

Microphone echo high cut2

Microphone echo high cut2

Microphone echo high cut2

Voice pitch ratio

Microphone input mix

Voice pitch control output mix

Refer to Table 11-1 for setting value

Refer to Table 12-1 for setting value

Refer to Table 12-1 for setting value

Refer to Table 14-3 for setting value

Refer to Table 14-3 for setting value

Refer to Table 14-3 for setting value

Refer to Table 10-1 for setting value

Refer to Table 12-1 for setting value

Refer to Table 12-1 for setting value

Name Function

Setting

value

Table 8-2. Coefficient RAM Setting Data (2/2)

Refer to 13. DSP Signal Flow regarding the names.

9. Voice Canceller Settings

[Relevant pins] PL (address = 10H), PR (address = 11H), Kvc (address = 18H)

The vocal sound set at the center can be cancelled by setting Kvc = 8000H and PL, PR = 7000H.

Voice canceling at other than center setting can be done by the panpot volume.

Panpot volume value is PL for CH1, and PR for CH2, and at the center position they are both 0.857. When

voice cancellation is OFF, set Kvc = 0000H and PL, PR = 0000H.

PL and PR setting values are hexadecimal notation with D15 as MSB and D0 as LSB.

PL

7000H

7000H

7000H

7000H

7000H

7000H

7000H

7000H

7000H

6000H

5000H

4000H

3000H

2000H

1000H

0000H

center

CH2

7000H

6000H

5000H

4000H

3000H

2000H

1000H

0000H

7000H

7000H

7000H

7000H

7000H

7000H

7000H

7000H

center

CH1

PR

Setting position

PL

PR

Setting position

Table 9-1. Settings for Voice Canceller Panpot Volume

≠ 29 ≠

CXD2720Q

10. Key Controller Setting

[Relevant coefficients] nRpR (address = 22H), Ks (address = 2EH), VnRpR (address = 53H),

Krmp (address = 5BH)

(1) Key Controller Pitch Ratio

nRpR (D15,.....,D2) is a 2's complement format with a decimal point between D14 and D13, and sets the

desired pitch ratio directly. (VnRpR has the same type of setting as nRpR.)

15

nRpR =

Dn

◊

2

n≠14

n = 2

The expression range for the pitch ratio is: ≠2.0

nRpR

2.0 ≠ 2

≠12

but for practical use it is: ≠0.5

nRpR

1.0

or Ī1 octave.

Use within a range of Ī half an octave is recommended for quality of sound, although it depends on the aim

and the source.

Also, the algorithm is such that allophones will not be generated even when nRpR setting value is changed.

(2) Notes on Key Controller OFF

The pitch does not change when nRpR and VnRpR are set to 0000H (OFF) when the key controller is OFF,

but depending on the internal state during OFF, there is no guarantee that the input value will be output as is.

During OFF, after setting nRpR and VnRpR to 0000H (OFF), set the pitch control section to through state with

the following settings.

Accompaniment controller OFF: Ks = 0000H (OFF)

Voice key controller OFF: sKrmp = 0000H (OFF)

≠ 30 ≠

CXD2720Q

(3) Examples of Key Controller Setting

Examples of pitch ratio setting are illustrated below.

nRpR setting values are hexadecimal notation with D15 as MSB and D2 as LSB for a total of 14 bits.

(D1 and D0 can be optional data.)

CENT

0

+50

+100

+150

+200

+250

+300

+350

+400

+450

+500

+550

+600

+650

+700

+750

+800

+850

+900

+950

+1000

+1050

+1100

+1150

+1200

0000H

01E0H

03CEH

05CAH

07D6H

09F1H

0C1BH

0E56H

10A2H

12FFH

156EH

17EEH

1A82H

1D29H

1FE4H

22B3H

2597H

2892H

2BA2H

2EC9H

3208H

3560H

38D0H

3C5BH

4000H

0

≠50

≠100

≠150

≠200

≠250

≠300

≠350

≠400

≠450

≠500

≠550

≠600

≠650

≠700

≠750

≠800

≠850

≠900

≠950

≠1000

≠1050

≠1100

≠1150

≠1200

0000H

FE2EH

FC69H

FAB1H

F905H

F765H

F5D2H

F44AH

F2CCH

F15AH

EFF3H

EE95H

ED42H

EBF8H

EAB8H

E980H

E852H

E72CH

E60EH

E4F9H

E3ECH

E2E6H

E1E8H

E0F1H

E000H

nPpR

CENT

nPpR

Table 10-1. Pitch Ratio Setting Examples

The numeric representation format for pitch ratio here is:

15

nRpR =

Dn

◊

2

n≠14

n = 2

The numeric representation range is: ≠2.0

nRpR

2.0 ≠ 2

≠12

Also, the relationship formula with music word cent value C is:

nRpR = 2 ≠ 1, C = 1200 log

2

[nRpR + 1] [cent]

The semitone at average ratio is 100 [cent].

1200

C

≠ 31 ≠

CXD2720Q

11. Microphone Echo Delay Amount Setting

[Relevant coefficients] Tdo (address = 44H), Tre (address = 47H)

Microphone echo delay amount can be varied by setting coefficient Tdo (12 bits from D14 to D3) values. The

relationships between the coefficient and the delay amount are shown in Table 11-1.

Coefficient Tre (12 bits from D14 to D3) is microphone input echo initial delay time.

Set in the range of 0008H to Tdo.

Setting value Tdo

0008H

0010H

0018H

∑

∑

∑

∑

7ff0H

7ff8H

0000H

4096step

Delay (fs = 44.1kHz)

0.045 ms/step

setting possible

Table 11-1. Microphone Echo Delay Amount Setting

When Fs = 44.1kHz. Please inquire with regard to use at other than Fs = 44.1kHz, as the delay amount changes.

0.045ms

∑

∑

∑

∑

∑

∑

∑

∑

185.76ms

≠ 32 ≠

CXD2720Q

12. Input/Output Level Settings

[Relevant coefficients] Ki (address = 00H), KisLm (address = 05H), KisRc (address = 06H),

KiaLm (address = 07H), KiaRc (address = 08H), KisRm (address = 09H),

KisLc (address = 0AH), KiaRm (address = 0BH), KiaLc (address = 0CH),

Kimc (address = 31H), Kdry (address = 3CH), Keff (address = 3DH),

KLm (address = 3EH), KRm (address = 3FH), KLo (address = 40H),

KRo (address = 42H), Kre (address = 45H), Krd (address = 49H),

Kfb (address = 4AH), Krmc (address = 5AH), Krmp (address = 5BH)

The input/output levels and volumes are 2's complement format with a decimal point between D15 and D14,

and hexadecimal notation with D15 as MSB and D0 as LSB.

The coefficient and level relationships are as follows.

D15 to D0

8000H

FFFFH

0000H

0dB

≠90.31dB

≠

Level

D15 to D0

8000H

FFFFH

0000H

+12.04dB

≠78.27dB

≠

Level

Table 12-1. Input/Output Level Settings

(other than Kre)

Table 12-2. Input/Output Level Settings

(Kre)

The input/output levels for 8001H to FFFEH are determined by the following formulas.

14

(Coefficient value) = [ (≠1)

◊

D15 +

Dn

◊

2

n≠15

]

◊

(≠1) for other than Kre

n = 0

14

(Coefficient value) = [ (≠1)

◊

D15 +

Dn

◊

2

n≠15

]

◊

(≠4) for Kre

n = 0

Input/output level = 20 log [coefficient value] dB

D15 to D0 are negative values, but the calculation is (≠1)

◊

(D15 to D0).

≠ 33 ≠

CXD2720Q

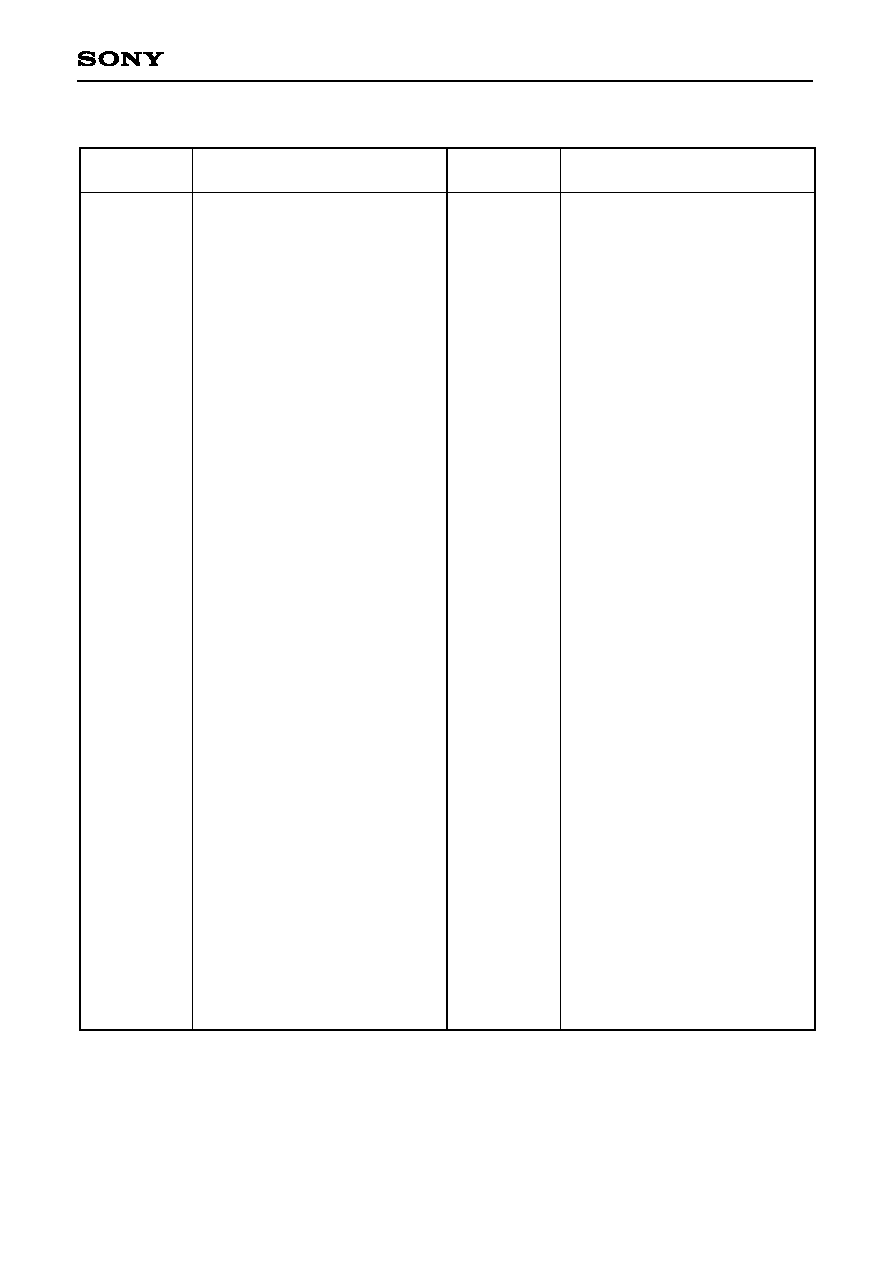

MIC

Pitch

Control

DC Cut2

≠Krmp

5BH

≠Krmc

5AH

≠Kimc

31H

34H

33H

Decimation

ADC

3BH

3AH

High Cut1

PEQ

38H

37H

39H

36H

35H

53H

Down

Sampling

≠Krd

49H

4CH

4BH

High Cut2

≠Kfb

Over

Sampling

≠Keff

3DH

4DH

4AH

Delay Line

Tdo

Tdi

Tre

44H

47H

45H

≠Kre

AD2

DC Cut1

0FH

0EH

Decimation

ADC

AD1

DC Cut1

Decimation

ADC

SI2

DeEmphasis

SI1

DeEmphasis

≠Ki

≠Ki

00H

04H

≠KisLm

05H

≠KisRc

06H

≠KiaLm

07H

≠KiaRc

08H

≠KisLc

0AH

≠KisRm

09H

≠KiaLc

0CH

≠KiaRm

0BH

Voice

Cancel

18H

11H

10H

DA2

Over

Sampling

≠KRm

3FH

Pitch

Control

≠KRo

42H

DAC

SO2

DA1

Over

Sampling

≠KLm

3EH

Pitch

Control

≠KLo

40H

DAC

SO1

2EH

22H

≠Kdry

3CH

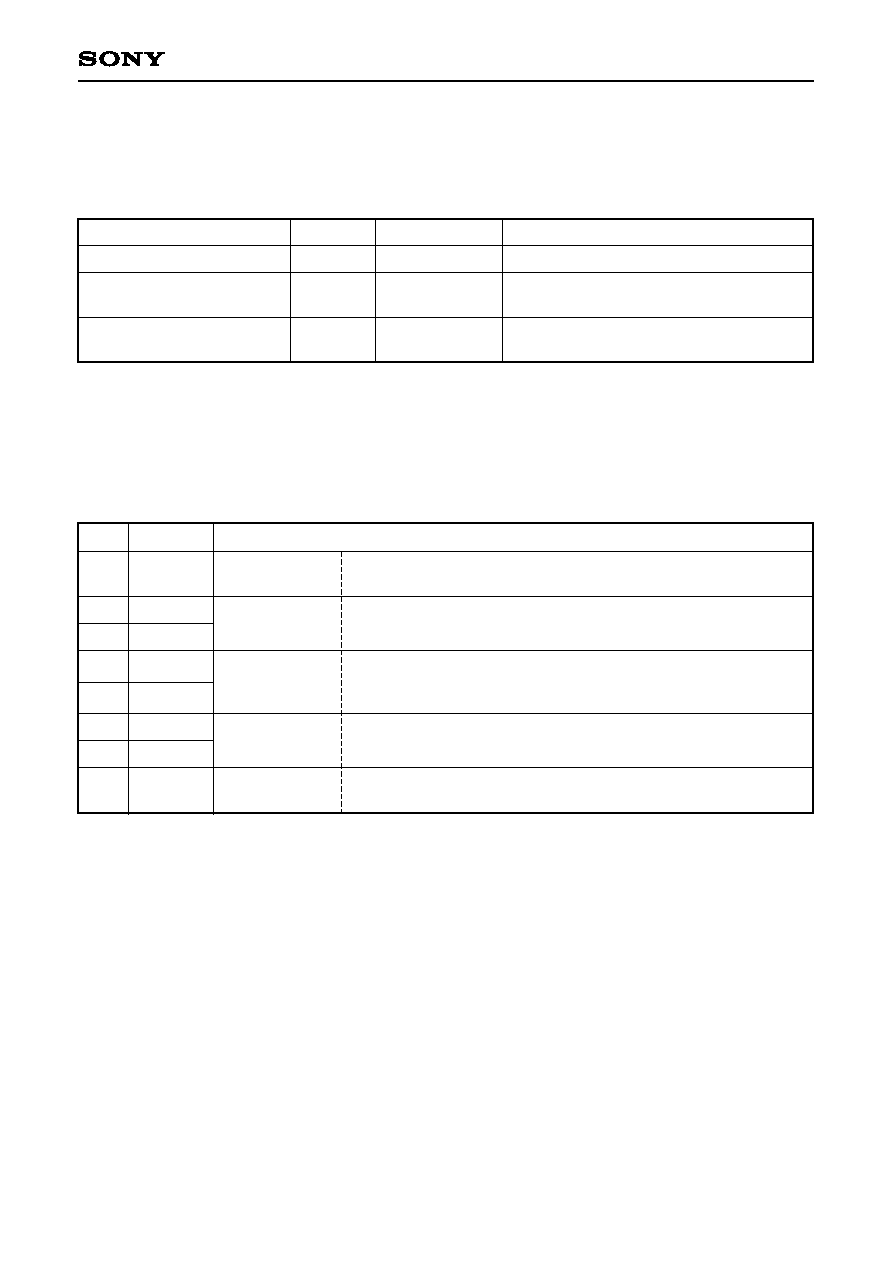

13. DSP Signal Flow

Refer to the coefficient RAM setting for information on each coefficient.

≠ 34 ≠

CXD2720Q

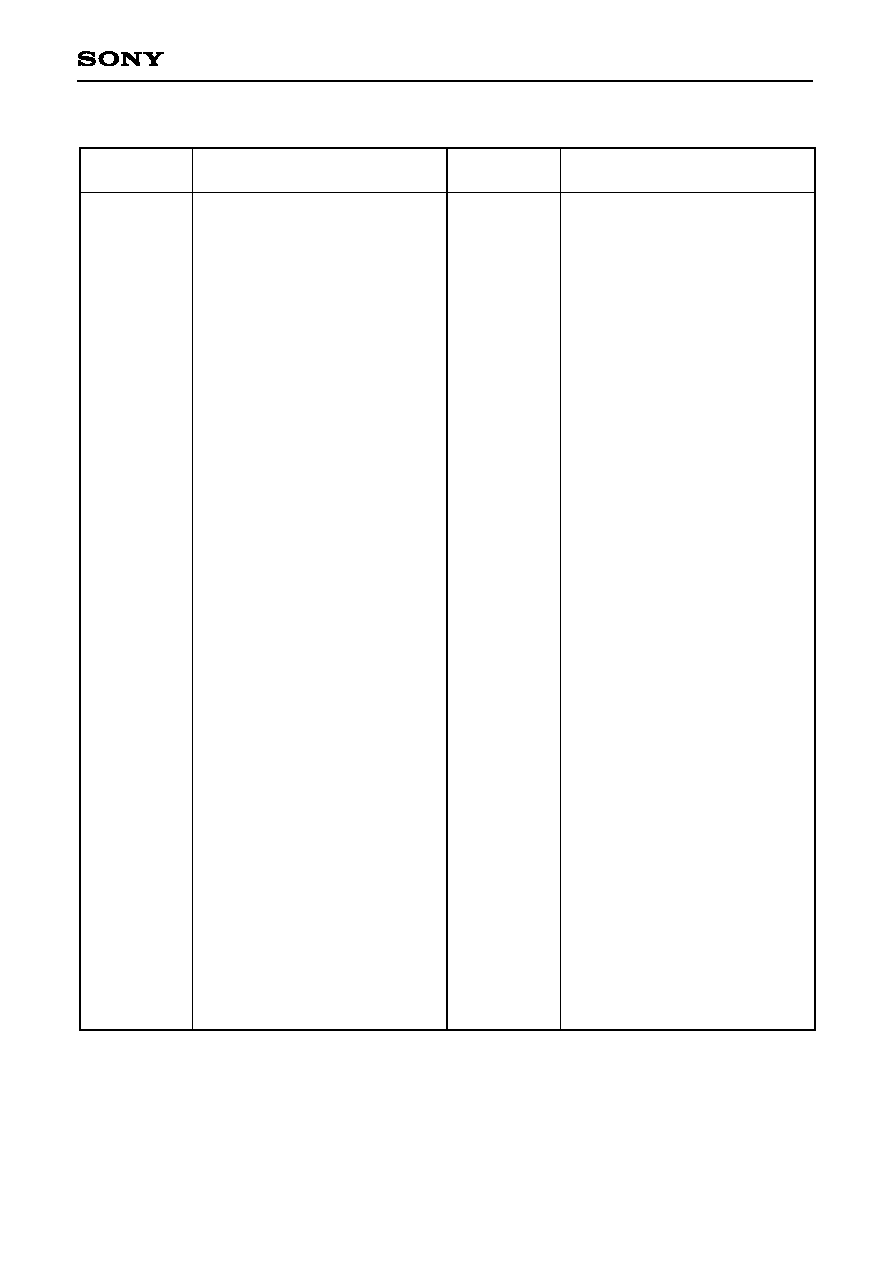

14. Filter Coefficient Table

[Relevant coefficient] DC1f0 (address = 0FH), DC2f0 (address = 33H), HC1b (address = 3BH),

HC1a1 (address = 39H), HC1a0 (address = 3AH), HC2b (address = 4DH),

HC2a1 (address = 4BH), HC2a0 (address = 4CH), PEQa (address = 35H),

PEQb1 (address = 36H), PEQb2 (address = 37H), PEQg (address = 38H)

The cut-off frequencies and PEQ gain, Q, and center frequency settings for each signal flow filter are shown in

Tables 13-1 to 13-5.

Note that if the above setting values are changed during DSP operation, the output level becomes unstable for

several 1/fs.

Tables 14-1 to 14-5 and digital de-emphasis are given for fs = 44.1kHz. Please inquire with regard to using an

fs other than this value.

(1) DC Cut1 for Accompaniment/ DC Cut2 for Voice

Cut-off

frequency (Hz)

20

30

40

50

60

70

80

90

100

110

120

130

140

150

160

170

180

190

200

210

220

230

240

250

260

7FA2

7F74

7F45

7F17

7EE9

7EBA

7E8C

7E5E

7E30

7E02

7DD4

7DA6

7D78

7D4B

7D1D

7CEF

7CC2

7C94

7C67

7C39

7C0C

7BDF

7BB2

7B85

7B58

270

280

290

300

310

320

330

340

350

360

370

380

390

400

410

420

430

440

450

460

470

480

490

500

510

7B2B

7AFE

7AD1

7AA4

7A77

7A4B

7A1E

79F1

79C5

7998

796C

7940

7914

78E7

78BB

788F

7863

7837

780B

77DF

77B4

7788

775C

7731

7705

520

530

540

550

560

570

580

590

600

610

620

630

640

650

660

670

680

690

700

710

720

730

740

750

760

76D9

76AE

7683

7657

762C

7601

75D6

75AB

7580

7555

752A

74FF

74D4

74A9

747E

7454

7429

73FF

73D4

73AA

737F

7355

732B

7301

72D6

770

780

790

800

810

820

830

840

850

860

870

880

890

900

910

920

930

940

950

960

970

980

990

1000

72AC

7282

7258

722E

7204

71DB

71B1

7187

715D

7134

710A

70E1

70B7

708E

7064

703B

7012

6FE9

6FBF

6F96

6F6D

6F44

6F1B

6EF2

DC1f0

DC2f0

Cut-off

frequency (Hz)

DC1f0

DC2f0

Cut-off

frequency (Hz)

DC1f0

DC2f0

Cut-off

frequency (Hz)

DC1f0

DC2f0

Table 14-1.

≠ 35 ≠

CXD2720Q

(2) High Cut1 for Voice

Cut-off

frequency (Hz)

1000

1100

1200

1300

1400

1500

1600

1700

1800

1900

2000

2100

2200

2300

2400

2500

2600

2700

2800

2900

3000

3100

3200

3300

3400

3500

3600

3700

3800

3900

4000

4100

4200

4300

4400

4500

4600

4700

4800

4900

5000

5100

5200

5300

5400

5500

6EF2

6D5C

6BCB

6A3E

68B6

6733

65B4

6439

62C3

6150

5FE2

5E77

5D11

5BAE

5A4E

58F2

579A

5645

54F3

53A4

5259

5110

4FCB

4E88

4D48

4C0B

4AD0

4998

4863

4730

4600

44D2

43A6

427C

4155

4030

3F0D

3DEC

3CCD

3BAF

3A94

397B

3863

374D

3639

3527

0886

0951

0A1A

0AE0

0BA4

0C66

0D25

0DE3

0E9E

0F57

100E

10C4

1177

1228

12D8

1386

1432

14DD

1586

162D

16D3

1777

181A

18BB

195B

19FA

1A97

1B33

IBCE

1C67

1CFF

1D96

1E2C

1EC1

1F55

1FE7

2079

2109

2199

2228

22B5

2342

23CE

2459

24E3

256C

F77A

F6AF

F5E6

F520

F45C

F39A

F2DB

F21D

F162

F0A9

EFF2

EF3C

EE89

EDD8

ED28

EC7A

EBCE

EB23

EA7A

E9D3

E92D

E889

E7E6

E745

E6A5

E606

E569

E4CD

E432

E399

E301

E26A

E1D4

E13F

E0AB

E019

DF87

DEF7

DE67

DDD8

DD4B

DCBE

DC32

DBA7

DB1D

DA94

5600

5700

5800

5900

6000

6100

6200

6300

6400

6500

6600

6700

6800

6900

7000

7100

7200

7300

7400

7500

7600

7700

7800

7900

8000

8100

8200

8300

8400

8500

8600

8700

8800

8900

9000

9100

9200

9300

9400

9500

9600

9700

9800

9900

10000

OFF

3416

3306

31F9

30EC

2FE2

2ED8

2DD0

2CCA

2BC4

2AC0

29BD

28BC

27BB

26BC

25BD

24C0

23C4

22C9

21CF

20D5

1FDD

1EE6

1DEF

1CF9

1C04

1B10

1A1C

192A

1838

1746

1655

1565

1475

1386

1298

11A9

10BC

0FCF

0EE2

0DF5

0D09

0C1E

0B32

0A47

095C

0000

25F4

267C

2703

2789

280E

2893

2917

299A

2A1D

2A9F

2B21

2BA1

2C22

2CA1

2D21

2D9F

2E1D

2E9B

2F18

2F95

3011

308C

3108

3183

31FD

3277

32F1

336A

33E3

345C

34D5

354D

35C5

363C

36B3

372B

37A1

3818

388E

3905

397B

39F0

3A66

3ADC

3B51

0000

DA0C

D984

D8FD

D877

D7F2

D76D

D6E9

D666

D5E3

D561

D4DF

D45F

D3DE

D35F

D2DF

D261

D1E3

D165

D0E8

D06B

CFEF

CF74

CEF8

CE7D

CE03

CD89

CD0F

CC96

CC1D

CBA4

CB2B

CAB3

CA3B

C9C4

C94D

C8D5

C85F

C7E8

C772

C6FB

C685

C610

C59A

C524

C4AF

8000

HC1b

HC1a1

HC1a0

Cut-off

frequency (Hz)

HC1b

HC1a1

HC1a0

Table 14-2.

≠ 36 ≠

CXD2720Q

(3) High Cut2 for Microphone Echo

Cut-off

frequency (Hz)

1000

1100

1200

1300

1400

1500

1600

1700

1800

1900

2000

2100

2200

2300

2400

2500

2600

2700

2800

2900

3000

3100

3200

3300

3400

3500

3600

3700

3800

3900

4000

4100

4200

4300

4400

4500

4600

4700

4800

4900

5000

5100

5200

5300

5400

5500

5FE2

5D11

5A4E

579A

54F3

5259

4FCB

4D48

4AD0

4863

4600

43A6

4155

3F0D

3CCD

3A94

3863

3639

3416

31F9

2FE2

2DD0

2BC4

29BD

27BB

25BD

23C4

21CF

1FDD

1DEF

1C04

1A1C

1838

1655

1475

1298

10BC

0EE2

0D09

0B32

095C

0788

05B3

03E0

020D