June 2003

1/132

Rev. 2.2

ST7262

LOW SPEED USB 8-BIT MCU WITH 3 ENDPOINTS, FLASH OR

ROM MEMORY, LVD, WDG, 10-BIT ADC, 2 TIMERS, SCI, SPI

s

Memories

� 8K or 16K Program memory

(ROM, FASTROM or Dual voltage FLASH)

with read-write protection

� In-Application and In-Circuit Programming for

FLASH versions

� 384 to 768 bytes RAM (128-byte stack)

s

Clock, Reset and Supply Management

� Enhanced Reset System (Power On Reset)

� Low Voltage Detector (LVD)

� Clock-out capability

� 6 or 12 MHz Oscillator (8, 4, 2, 1 MHz internal

frequencies)

� 3 Power saving modes

s

USB (Universal Serial Bus) Interface

� DMA for low speed applications compliant

with USB 1.5 Mbs specification (v 1.1) and

USB HID specification (v 1.0):

� Integrated 3.3V voltage regulator and trans-

ceivers

� Suspend and Resume operations

� 3 Endpoints

s

Up to 31 I/O Ports

� Up to 31 multifunctional bidirectional I/O lines

� Up to 12 External interrupts (3 vectors)

� 13 alternate function lines

� 8 high sink outputs

(8 mA@0.4 V/20 mA@1.3 V)

� 2 true open drain pins (N buffer 8 mA@0.4 V)

s

3 Timers

� Configurable watchdog timer (8 to 500 ms

timeout)

� 8-bit Auto Reload Timer (ART) with 2 Input

Captures, 2 PWM outputs and External Clock

� 8-bit Time Base Unit (TBU) for generating pe-

riodic interrupts cascadable with ART

s

Analog Peripheral

� 10-bit A/D Converter with up to 8 input pins.

s

2 Communications Interfaces

� Asynchronous Serial Communication inter-

face

� Synchronous Serial Peripheral Interface

s

Instruction Set

� 8-bit data manipulation

� 63 basic instructions

� 17 main addressing modes

� 8 x 8 unsigned multiply instruction

� True bit manipulation

s

Nested interrupts

s

Development Tools

� Full hardware/software development package

Device Summary

PDIP32 shrink

SO34 shrink

TQFP44

PDIP42 shrink

SO20

PDIP20

Features

ST72623F2

ST72622K2

ST72621K4

ST72622L2

ST72621L4

ST72621J2

ST72621J4

Program memory - bytes

8K

8K

16K

8K

16K

8K

16K

RAM (stack) - bytes

384 (128)

384 (128)

768 (128)

384 (128)

768 (128)

384 (128)

768 (128)

Peripherals

USB, Watchdog, Low Voltage Detector, 8-bit Auto-Reload timer, Timebase unit, A/D Converter

Serial I/O

-

SPI

SPI + SCI

SPI

SPI + SCI

I/Os

11

21

23

31

Operating Supply

4.0V to 5.5V (Low voltage 3.0V to 5.5V ROM versions available)

Operating Temperature

0�C to +70�C

Packages

PDIP20/SO20

PDIP32

SO34

PDIP42/TQFP44

1

Table of Contents

132

2/132

1

1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2 PIN DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2.1 PCB LAYOUT RECOMMENDATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

3 REGISTER & MEMORY MAP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 1

4 FLASH PROGRAM MEMORY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

4.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

4.2 MAIN FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

4.3 STRUCTURE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

4.4 ICC INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

4.5 ICP (IN-CIRCUIT PROGRAMMING) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

4.6 IAP (IN-APPLICATION PROGRAMMING) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

4.7 RELATED DOCUMENTATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

4.8 REGISTER DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

5 CENTRAL PROCESSING UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

5.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

5.2 MAIN FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

5.3 CPU REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

6 CLOCKS AND RESET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

6.1 CLOCK SYSTEM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

6.2 RESET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

7 INTERRUPTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

7.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

7.2 MASKING AND PROCESSING FLOW . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

7.3 INTERRUPTS AND LOW POWER MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

7.4 CONCURRENT & NESTED MANAGEMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

7.5 INTERRUPT REGISTER DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

7.6 INTERRUPT REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

8 POWER SAVING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

8.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

8.2 WAIT MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

8.3 HALT MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

9 I/O PORTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

9.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

9.2 FUNCTIONAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

9.3 MISCELLANEOUS REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

10 ON-CHIP PERIPHERALS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

10.1 WATCHDOG TIMER (WDG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

10.2 PWM AUTO-RELOAD TIMER (ART) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

10.3 TIMEBASE UNIT (TBU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 2

10.4 SERIAL PERIPHERAL INTERFACE (SPI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

10.5 SERIAL COMMUNICATIONS INTERFACE (SCI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Table of Contents

132

3/132

10.6 USB INTERFACE (USB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

10.7 10-BIT A/D CONVERTER (ADC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

11 INSTRUCTION SET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

11.1 CPU ADDRESSING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

11.2 INSTRUCTION GROUPS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

12 ELECTRICAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

12.1 PARAMETER CONDITIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

12.2 ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

12.3 OPERATING CONDITIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

12.4 SUPPLY CURRENT CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

12.5 CLOCK AND TIMING CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

12.6 MEMORY CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

12.7 EMC CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

12.8 I/O PORT PIN CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

12.9 CONTROL PIN CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

12.10TIMER PERIPHERAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

12.11COMMUNICATION INTERFACE CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . 117

12.1210-BIT ADC CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

13 PACKAGE CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

13.1 PACKAGE MECHANICAL DATA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

14 DEVICE CONFIGURATION AND ORDERING INFORMATION . . . . . . . . . . . . . . . . . . . . . . . 126

14.1 OPTION BYTE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

14.2 DEVICE ORDERING INFORMATION AND TRANSFER OF CUSTOMER CODE . . . . . 126

14.3 DEVELOPMENT TOOLS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

15 IMPORTANT NOTES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

15.1 UNEXPECTED RESET FETCH . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

15.2 HALT MODE POWER CONSUMPTION WITH ADC ON . . . . . . . . . . . . . . . . . . . . . . . . . 130

16 SUMMARY OF CHANGES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

To obtain the most recent version of this datasheet,

please check at www.st.com>products>technical literature>datasheet

Please pay special attention to the Section "IMPORTANT NOTES" on page 130.

ST7262

4/132

1 INTRODUCTION

The ST7262, ST72P62 and ST72F62 devices are

members of the ST7 microcontroller family de-

signed for USB applications.

All devices are based on a common industry-

standard 8-bit core, featuring an enhanced instruc-

tion set.

The ST7262 devices are ROM versions.

The ST72P62 devices are Factory Advanced

Service Technique ROM (FASTROM) versions:

they are factory-programmed and are not repro-

grammable.

The ST72F62 versions feature dual-voltage

FLASH memory with FLASH Programming capa-

bility.

Under software control, all devices can be placed

in WAIT, SLOW, or HALT mode, reducing power

consumption when the application is in idle or

standby state.

The enhanced instruction set and addressing

modes of the ST7 offer both power and flexibility to

software developers, enabling the design of highly

efficient and compact application code. In addition

to standard 8-bit data management, all ST7 micro-

controllers feature true bit manipulation, 8x8 un-

signed multiplication and indirect addressing

modes.

Figure 1. General Block Diagram

8-BIT CORE

ALU

A

DDRE

S

S

A

ND DA

T

A

B

U

S

OSCIN

OSCOUT

RESET

PORT B

USB SIE

PORT A

SCI

PORT C

SPI

PB7:0

(8 bits)

PC7:0

(8 bits)

OSCILLATOR

Internal

CLOCK

CONTROL

RAM

(384,

PA7:0

(8 bits)

V

SS

V

DD

POWER

SUPPLY

PROGRAM

(8 or 16K Bytes)

LVD

10-BIT ADC

MEMORY

WATCHDOG

USBDP

USBDM

USBVCC

PWM ART

USB DMA

V

SSA

V

DDA

PORT D

PD6:0

(7 bits)

TIME BASE UNIT

V

PP

or 768 Bytes)

1

ST7262

5/132

2 PIN DESCRIPTION

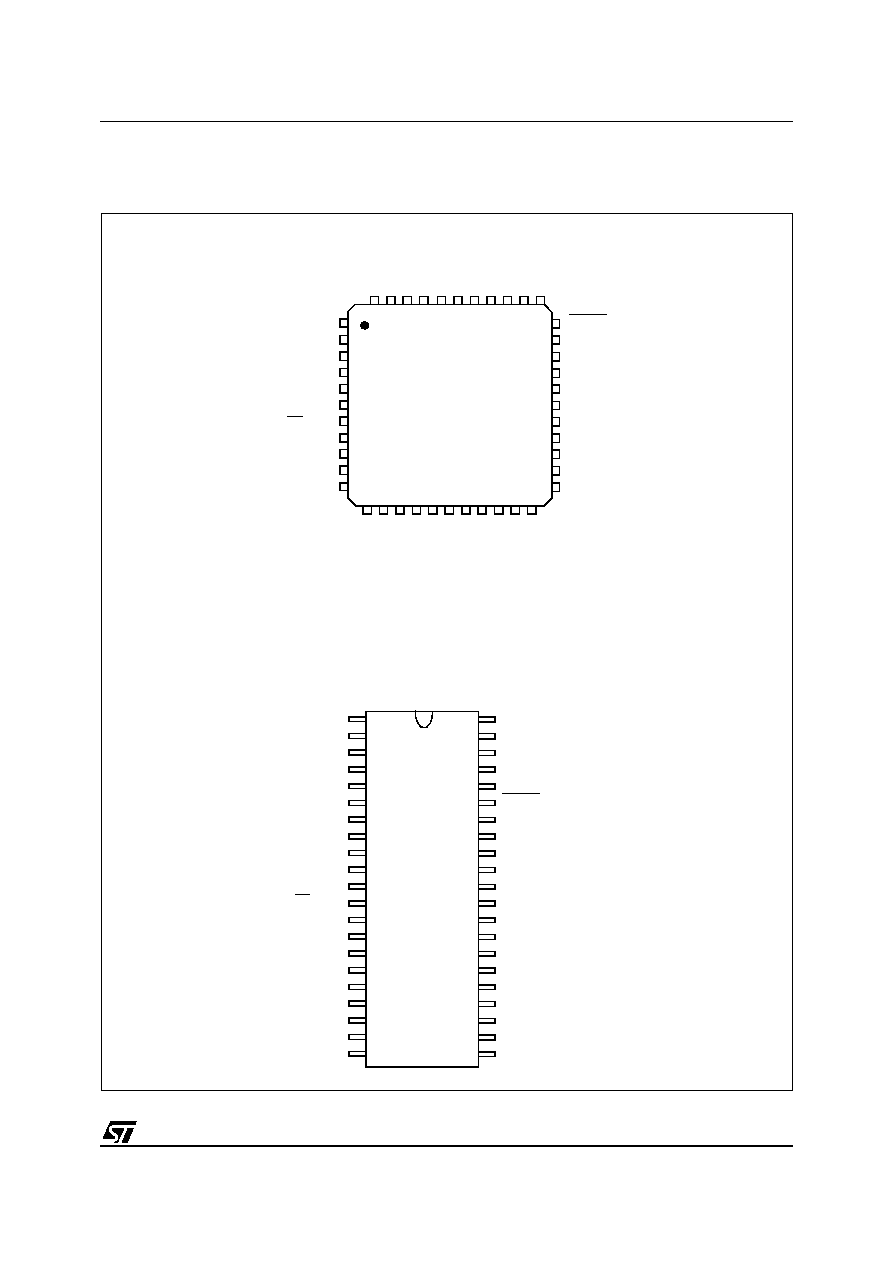

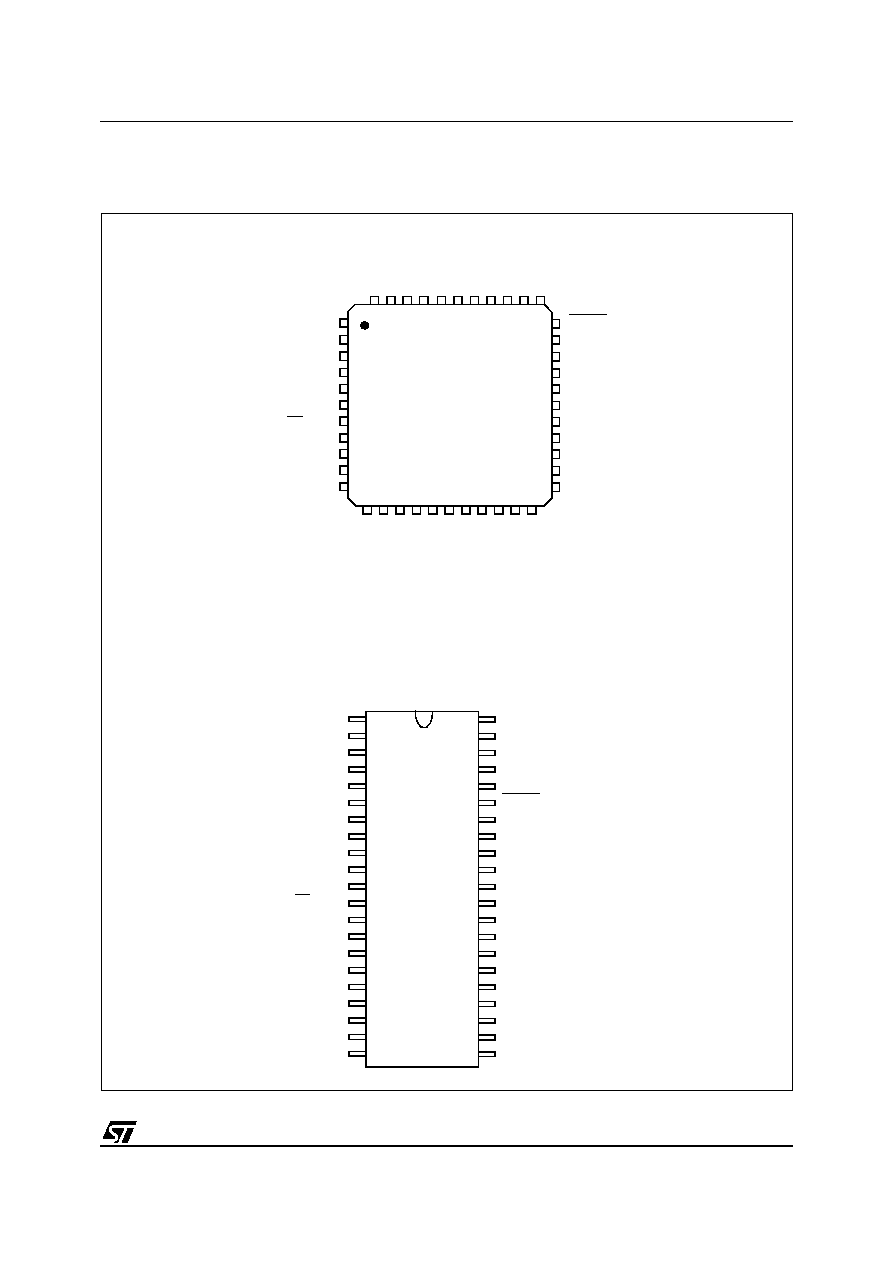

Figure 2. 44-pin TQFP and 42-Pin SDIP Package Pinouts

44 43 42 41 40 39 38 37 36 35 34

33

32

31

30

29

28

27

26

25

24

23

12 13 14 15 16 17 18 19 20 21 22

1

2

3

4

5

6

7

8

9

10

11

38

37

36

35

34

33

32

31

30

29

28

27

16

15

1

2

3

4

5

6

7

8

9

10

11

12

13

14

39

40

41

42

PD6

PD5

OSCOUT

OSCIN

IT9 / PC2

IT10 / SCK / PC3

IT11 / SS / PC4

IT12 / MISO / PC5

MOSI / PC6

PD1

V

PP

PD2

PD3

PD4

PC7

PD0

V

DDA

USBVCC

PB1 (HS) / RDI

PB0 (HS) / MCO

PA7 / AIN7

PA6 / AIN6

PA5 / AIN5

PA4 / AIN4

PA3 / AIN3 / IT4

PA0 / AIN0 / IT1 / USBOE

RESET

V

SSA

USBDM

USBDP

PA1 / AIN1 / IT2

PA2 / AIN2 / IT3

21

20

17

18

19

IT8 / PWM1 / PB7 (HS)

PC0

PC1

V

DD

V

SS

26

25

24

23

22

PB6 (HS) / PWM0 / IT7 / ICCDATA

PB5 (HS) / ARTIC2 / IT6 / ICCCLK

PB4 (HS) / ARTIC1 / IT5

PB3 (HS) / ARTCLK

PB2 (HS) / TDO

OSCOUT

OSCIN

IT9 / PC2

IT10 / SCK / PC3

IT11 / SS / PC4

IT12 / MISO / PC5

MOSI / PC6

PD1

V

PP

PC7

PD0

IT

8

/

PW

M

1

/

PB7

PC

0

PC

1

V

DD

V

SS

AR

T

C

L

K

/

PB3

(

H

S)

IT

5

/

AR

T

I

C

1

/

PB4

(

H

S)

IC

C

C

L

K

/

IT

6

/

AR

T

I

C

2

/

PB5

(

H

S)

IC

C

D

AT

A /

I

T

7

/ P

W

M

0

/

PB6

(

H

S)

N.

C

.

T

D

O

/

PB2

(

H

S)

PB1 (HS) / RDI

PB0 (HS) / MCO

PA7 / AIN7

PA6 / AIN6

PA5 / AIN5

PA4 / AIN4

PA3 / AIN3 / IT4

PA0 / AIN0 / IT1 / USBOE

RESET

PA1 / AIN1 / IT2

PA2 / AIN2 / IT3

V

DDA

U

SBVC

C

V

SS

A

U

SBD

M

U

SBD

P

PD

3

PD

4

Re

s

e

rv

ed*

PD

6

PD

5

PD

2

* Pin 39 of the TQFP44 package

must be left unconnected.