July 2000

This is preliminary information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

(1)

in order to enable SRS WOW algorithm a mandatory configuration file is required.

ORDERING NUMBERS: STA014 (SO28)

STA014T (TQFP44)

STA014B (LFBGA 64)

SINGLE CHIP MPEG2 LAYER 3 DECODER

SUPPORTING:

- All features specified for Layer III in ISO/IEC

11172-3 (MPEG 1 Audio)

- All features specified for Layer III in ISO/IEC

13818-3.2 (MPEG 2 Audio)

- Lower sampling frequencies syntax extension,

(not specified by ISO) called MPEG 2.5

DECODES LAYER III STEREO CHANNELS,

DUAL CHANNEL, SINGLE CHANNEL

(MONO)

SUPPORTING ALL THE MPEG 1 & 2 SAM-

PLING FREQUENCIES AND THE EXTEN-

SION TO MPEG 2.5:

48, 44.1, 32, 24, 22.05, 16, 12, 11. 025, 8 KHz

ACCEPTS MPEG 2.5 LAYER III ELEMEN-

TARY COMPRESSED BITSTREAM WITH

DATA RATE FROM 8 Kbit/s UP TO 320 Kbit/s

ADPCM CODEC CAPABILITIES:

- sample frequency from 8 kHz to 32 kHz

- sample size from 8 bits to 32 bits

- encoding algorithm: DVI,

ITU-G726 pack (G723-24, G721,G723-40)

- Tone control and fast-forward capability

SRS WOW

(1)

TECHNOLOGY CAN BE USED

AS POSTPROCESSING. SUPPORT FOR

DIFFERENT SPEAKERS TYPES:

- headphone

- medium

- large

WOW

(1)

TRUEBASS AND FOCUS CAN BE

INDIPENDENTLY ADJUSTED

EASY PROGRAMMABLE GPSO INTERFACE

FOR ENCODED DATA UP TO 5Mbit/s

(TQFP44 & LFBGA 64)

DIGITAL VOLUME

BASS & TREBLE CONTROL

SERIAL BITSTREAM INPUT INTERFACE

EASY PROGRAMMABLE ADC INPUT INTERFACE

ANCILLARY DATA EXTRACTION VIA I2C IN-

TERFACE.

SERIAL PCM OUTPUT INTERFACE (I

2

S

AND OTHER FORMATS)

PLL FOR INTERNAL CLOCK AND FOR OUT-

PUT PCM CLOCK GENERATION

CRC CHECK AND SYNCHRONISATION ER-

ROR DETECTION WITH SOFTWARE INDI-

CATORS

I

2

C CONTROL BUS

LOW POWER 2.4V CMOS TECHNOLOGY

WIDE RANGE OF EXTERNAL CRYSTALS

FREQUENCIES SUPPORTED

APPLICATIONS

PC SOUND CARDS

MULTIMEDIA PLAYERS

VOICE RECORDERS

DESCRIPTION

The STA014 is a fully integrated high flexibility

MPEG Layer III Audio Decoder, capable of de-

coding Layer III compressed elementary streams,

as specified in MPEG 1 and MPEG 2 ISO stand-

ards. The device decodes also elementary streams

compressed by using low sampling rates, as speci-

fied by MPEG 2.5. STA014 receives the input data

through a Serial Input Interface. The decoded sig-

nal is a stereo, mono, or dual channel digital output

that can be sent directly to a D/A converter, by the

PCM Output Interface. This interface is software

programmable to adapt the STA014 digital output

to the most common DACs architectures used on

the market. The functional STA014 chip partitioning

is described in Fig.1a and Fig.1b.

STA014 STA014B STA014T

MPEG 2.5 LAYER III AUDIO DECODER WITH ADPCM AND

SRS WOW

�

POSTPROCESSING CAPABILITY

PRODUCT PREVIEW

�

The Device incorporates the SRS

WOW

�

Technology under li-

cence from SRS Labs, Inc.

1/45

A

A1 = SDI

B2 = SCKR

D4 = BIT_EN

D1 = SRC_INT

E2 = SDO

F2 = SCKT

H1 = LRCKT

H3 = OCLK

F3 = VSS_2

E4 = VDD_2

G4 = VSS_3

G5 = VDD_3

F5 = PVDD

G6 = PVSS

1

2

3

4

5

6

7

8

B

C

D

E

F

G

H

D00AU1149

C2 = GPIO_STROBE

C3 = IODATA [4]

E3 = IODATA [5]

D2 = IODATA [6]

F1 = IODATA [7]

G3 = GPSO_REQ

F8 = IODATA [3]

F6 = IODATA [2]

E6 = IODATA [1]

C7 = IODATA [0]

C6 = GPSO_SCKR

A2 = GPSO_DATA

G7 = FILT

G8 = XTO

F7 = XTI

E7 = VSS_4

C8 = VDD_4

D7 = TESTEN

A7 = SDI_ADC

B6 = RESET

A5 = LRCK_ADC

C5 = OUT_CLK/DATA_REQ

B5 = VDD_1

B4 = VSS_1

A4 = SDA

B3 = SCL

VDD_1

VSS_1

RESET

SDA

SCL

SCKR

SDI

BIT_EN

SDO

VDD_4

VSS_4

XTI

FILT

XTO

PVSS

PVDD

VDD_3

VSS_3

1

3

2

4

5

6

7

8

9

26

25

24

23

22

20

21

19

27

10

28

VDD_2

TESTEN

D99AU1061

VSS_2

SCKT

LRCKT

LRCK_ADC

SRC_INT/SCK_ADC

SDI_ADC

11

12

13

18

16

17

15

14

OCLK

OUT_CLK/DATA_REQ

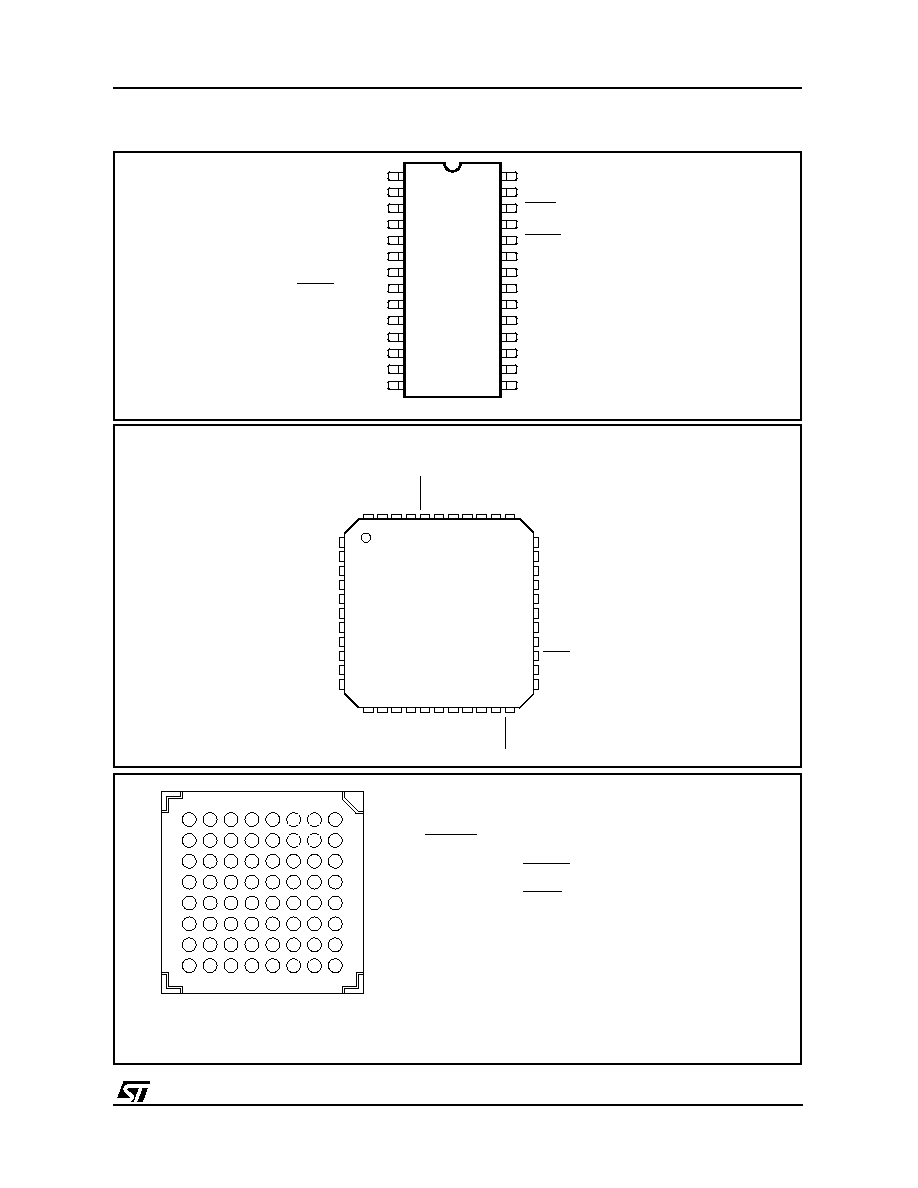

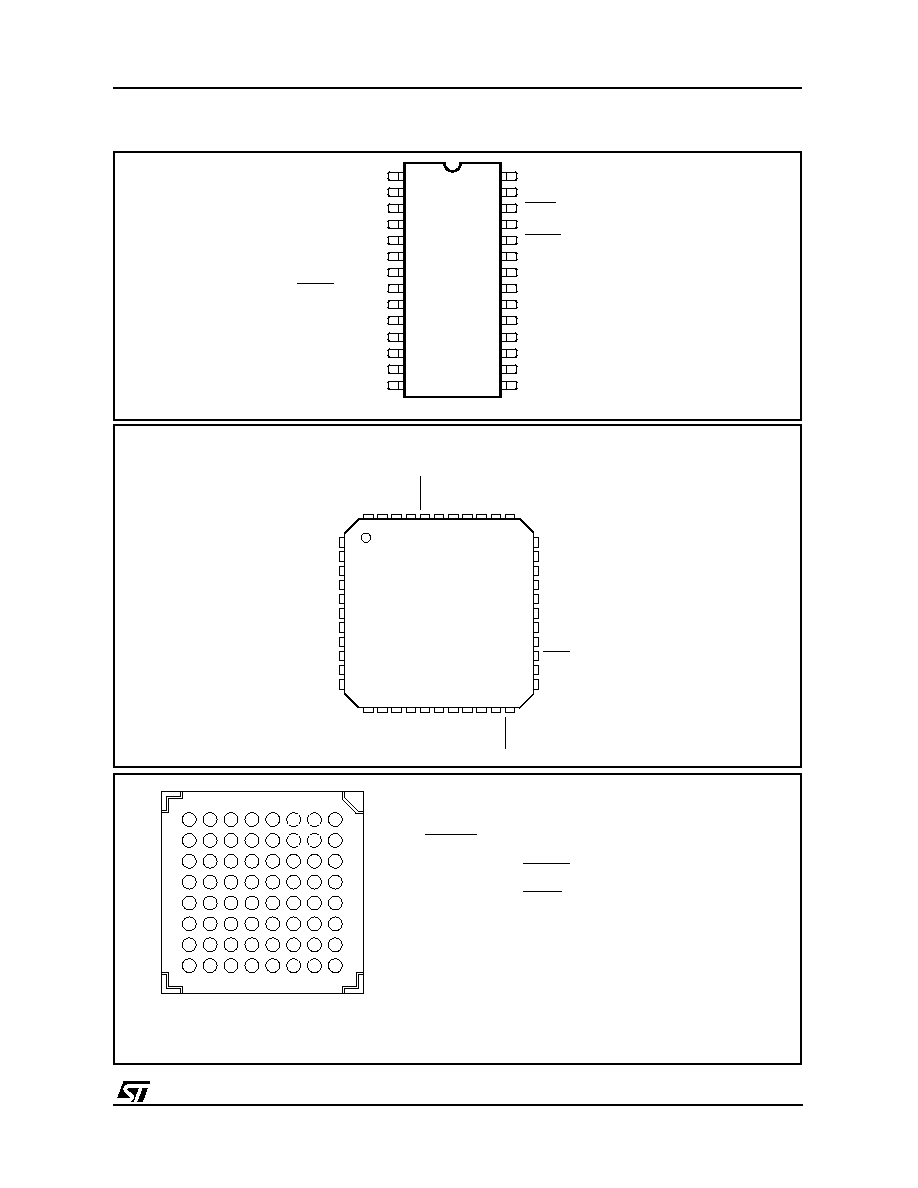

Figure 2. PIN CONNECTIONS

1

2

3

5

6

4

7

8

9

10

17

11

18

19

20

21

22

44

43

42

41

39

40

38

37

36

35

34

28

27

26

24

23

25

33

32

31

29

30

N.C.

LRCKT

OCLK

GPSO_REQ

VSS_2

VDD_2

VSS_3

VDD_3

N.C.

PVDD

PVSS

FILT

XTO

IODATA[3]

XTI

IODATA[2]

N.C.

IODATA[1]

VSS_4

IODATA[0]

VDD_4

TESTEN

SDI

GPIO/STROBE

SCKR

IODATA[4]

BIT_EN

IODATA[5]

SRC_INT/SCK_ADC

IODATA[6]

SDO

IODATA[7]

SCKT

N.C.

SDI_ADC

RESET

LRCK_ADC

OUT_CLK/DATA_REC

GPSO_SCKR

VDD_1

VSS_1

SDA

SCL

GPSO_DATA

D99AU1062

12

13

14

15

16

LFBGA64

TQFP44

SO28

STA014-STA014B-STA014T

3/45

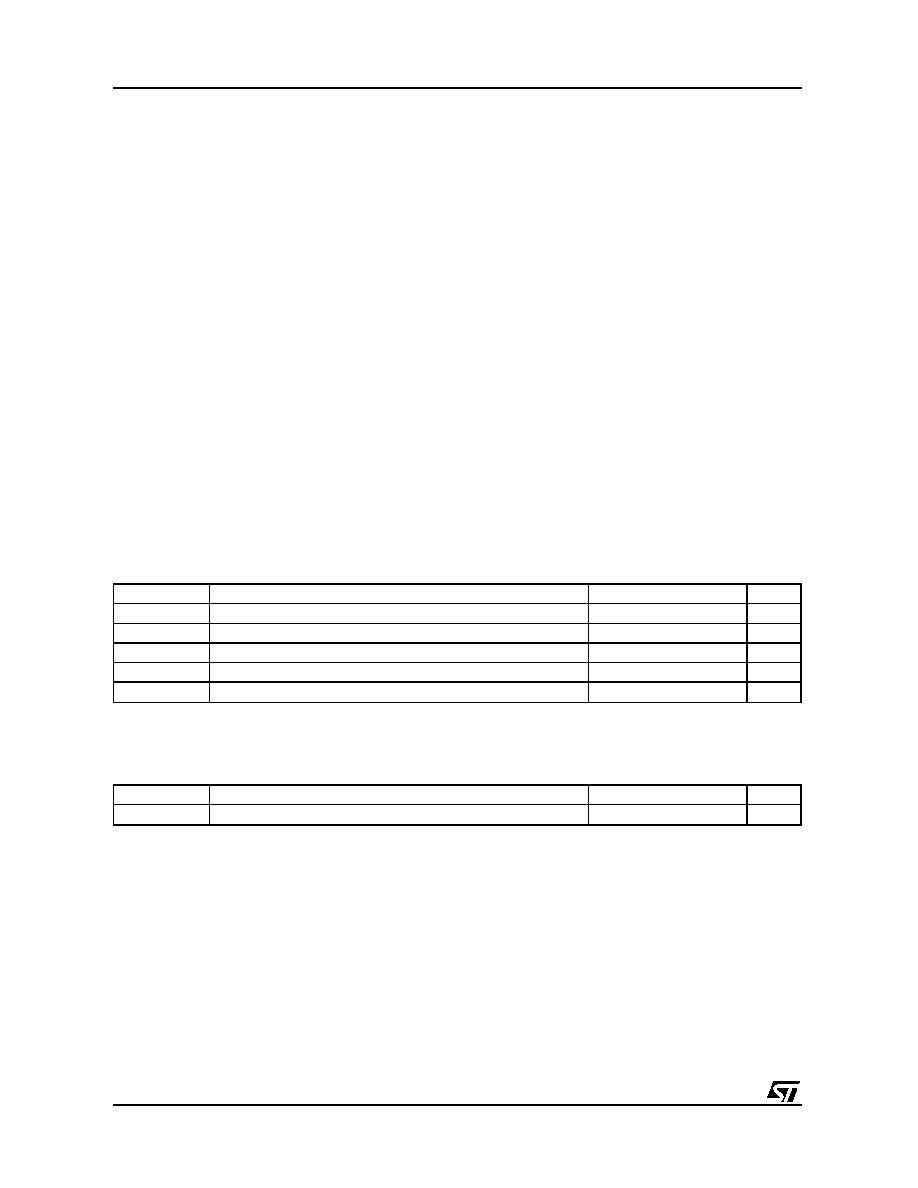

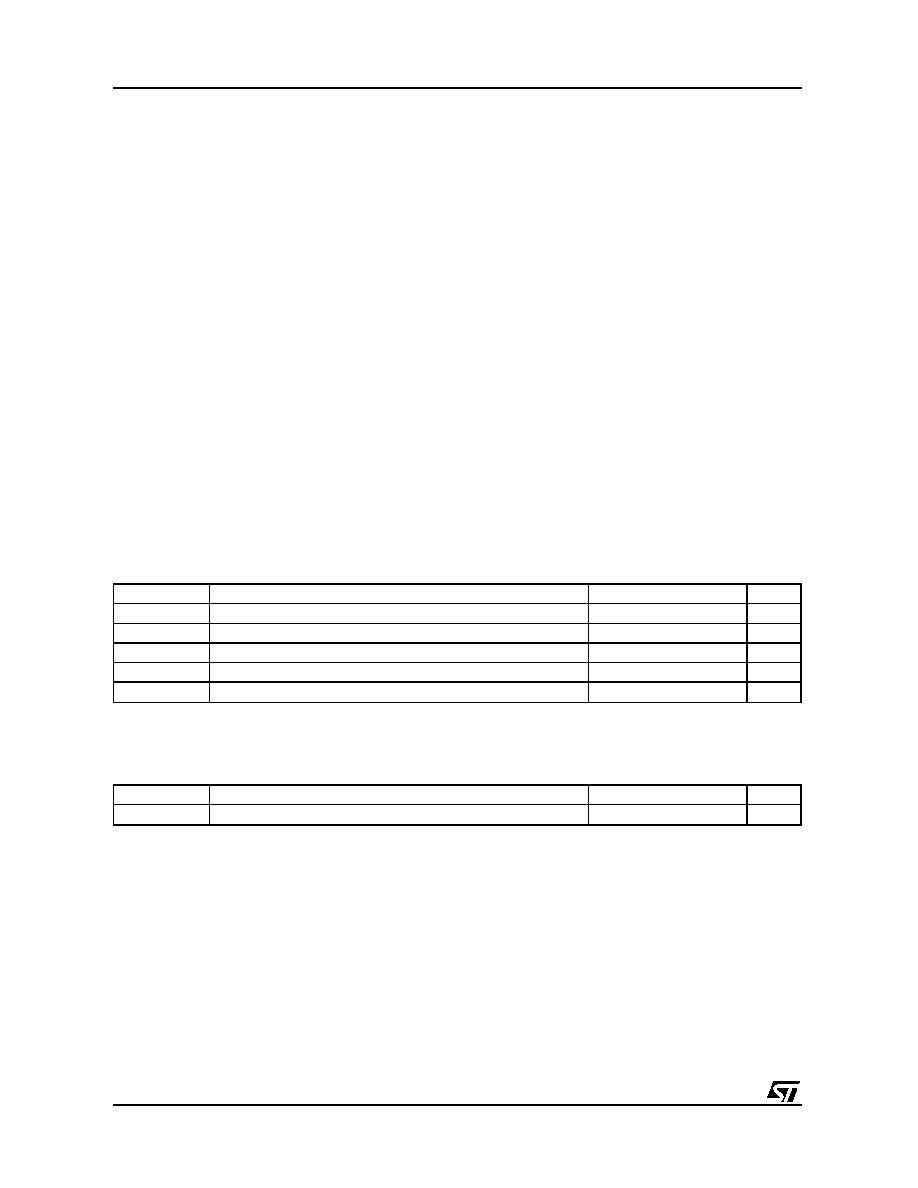

THERMAL DATA

Symbol

Parameter

Value

Unit

R

th j-amb

Thermal resistance Junction to Ambient

85

�C/W

1. OVERVIEW

1.1 - MP3 decoder engine

The MP3 decoder engine is able to decode any

Layer III compliant bitstream: MPEG1, MPEG2

and MPEG2.5 streams are supported. Besides

audio data decoding the MP3 engine also per-

forms ANCILLARY data extraction: these data

can be retrieved via I2C bus by the application

microcontroller in order to implement specific

functions.

Decoded audio data goes through a software vol-

ume control and a two-band equalizer blocks be-

fore feeding the output I2S interface. This results

in no need for an external audio processor.

MP3 bitstream is sent to the decoder using a sim-

ple serial input interface (see pins SDI, SCKR,

BIT_EN and DATA_REQ), supporting input rate

up to 20 Mbit/s. Received data are stored in a

256 bytes long input buffer which provides a

feedback line (see DATA_REQ pin) to the bit-

stream source (tipically an MCU).

1.2 - ADPCM encoder/decoder engine

This device also embeds a multistandard ADPCM

encoder/decoder supporting different sample

rates (from 8 KHz up to 32 KHz) and different

sample sizes (from 8 bit to 32 bits). During en-

coding process two different interfaces can be

used to feed data: the serial input interface (same

interface used also to feed MP3 bitstream) or the

ADC input interface, which provides a seamless

connection with an external A/D converter. The

currently used interface is selected via I2C bus.

Also to retrieve encoded data two different inter-

faces are available: the I2C bus or the faster

GPSO output interface. GPSO interface is able to

output data with a bitrate up to 5 Mbit/s and its

control pins (GPSO_SCKR, GPSO_DATA and

GPSO_REQ) can be configured in order to easily

fit the target application.

ABSOLUTE MAXIMUM RATINGS

Symbol

Parameter

Value

Unit

V

DD

Power Supply

-0.3 to 4

V

V

i

Voltage on Input pins

-0.3 to V

DD

+0.3

V

V

O

Voltage on output pins

-0.3 to V

DD

+0.3

V

T

stg

Storage Temperature

-40 to +150

�C

T

oper

Operative ambient temp

-20 to +85

�C

STA014-STA014B-STA014T

4/45

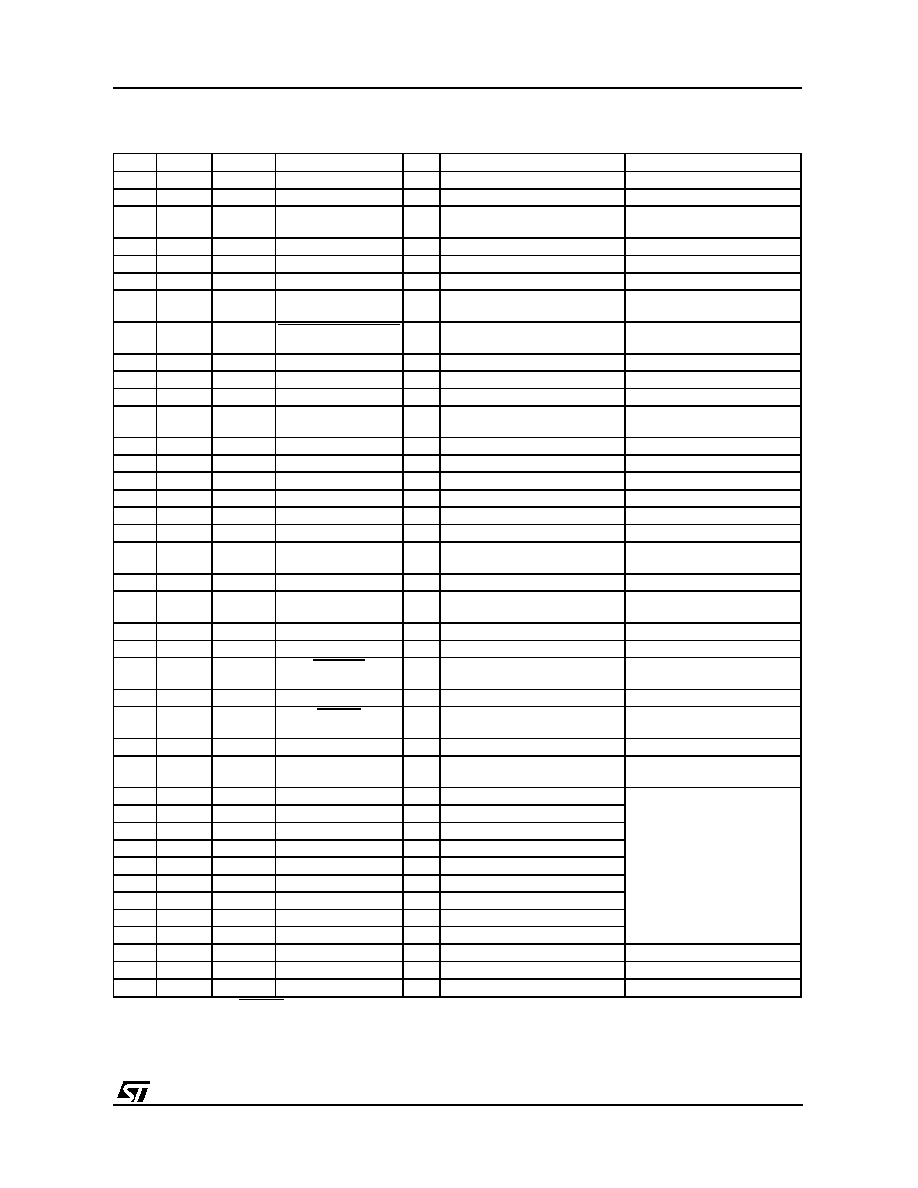

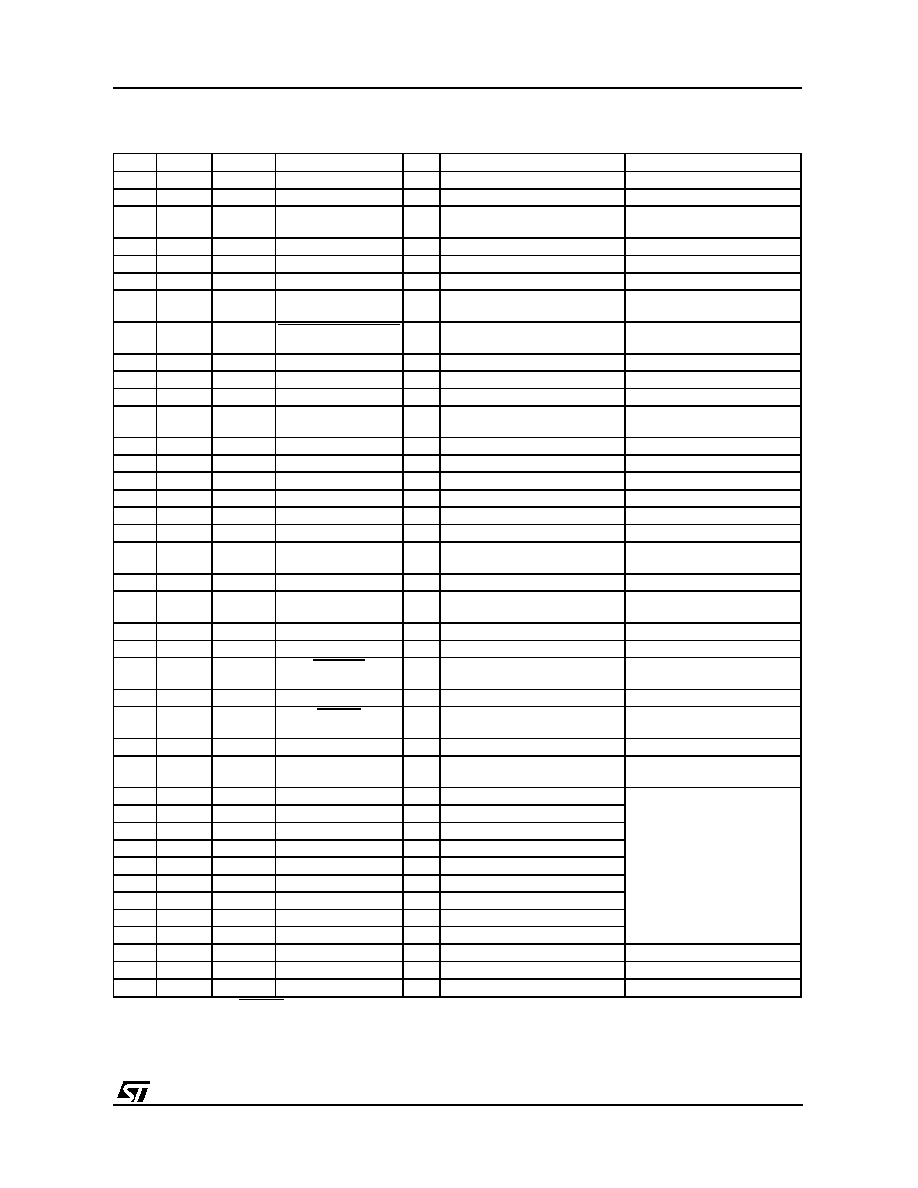

PIN DESCRIPTION

SO28 TQFP44 LFBGA64

Pin Name

Type

Function

PAD Description

1

29

B5

VDD_1

Supply Voltage

2

30

B4

VSS_1

Ground

3

31

A4

SDA

I/O

i

2

C Serial Data +

Acknowledge

CMOS Input Pad Buffer

CMOS 4mA Output Drive

4

32

B3

SCL

I

I

2

C Serial Clock

CMOS Input Pad Buffer

5

34

A1

SDI

I

Receiver Serial Data

CMOS Input Pad Buffer

6

36

B2

SCKR

I

Receiver Serial Clock

CMOS Input Pad Buffer

7

38

D4

BIT_EN

I

Bit Enable

CMOS Input Pad Buffer with

pull up

8

40

D1

SRC_INT/SCK_ADC

I

Interrupt Line/ADC Serial

Clock

CMOS Input Pad Buffer

9

42

E2

SDO

O

Transmitter Serial Data (PCM Data) CMOS 4mA Output Drive

10

44

F2

SCKT

O

Transmitter Serial Clock

CMOS 4mA Output Drive

11

2

H1

LRCLKT

O

Transmitter Left/Right Clock

CMOS 4mA Output Drive

12

3

H3

OCLK

I/O

Oversampling Clock for DAC

CMOS Input Pad Buffer

CMOS 4mA Output Drive

13

5

F3

VSS_2

Ground

14

6

E4

VDD_2

Supply Voltage

15

7

G4

VSS_3

Ground

16

8

G5

VDD_3

Supply Voltage

17

10

F5

PVDD

PLL Power

18

11

G6

PVSS

PLL Ground

19

12

G7

FILT

O

PLL Filter Ext. Capacitor

Conn.

20

13

G8

XTO

O

Crystal Output

CMOS 4mA Output Drive

21

15

F7

XTI

I

Crystal Input (Clock Input)

Specific Level Input Pad

(see paragraph 2.1)

22

19

E7

VSS_4

Ground

23

21

C8

VDD_4

Supply Voltage

24

22

D7

TESTEN

I

Test Enable

CMOS Input Pad Buffer with

pull up

25

24

A7

SDI_ADC

I

ADC Data Input

CMOS Input Pad Buffer

26

25

B6

RESET

I

System Reset

CMOS Input Pad Buffer with

pull up

27

26

A5

LRCK_ADC

I

ADC Left/Right Clock

CMOS Output Pad Buffer

28

27

C5

OUT_CLK/

DATA_REQ

O

Buffered Output Clock/

Data Request Signal

CMOS 4mA Output Drive

20

C7

IODATA[0]

I/O

GPIO Data Line

CMOS 4mA Schmitt Trigger

Bidir Pad Buffer

18

E6

IODATA[1]

I/O

GPIO Data Line

16

F6

IODATA[2]

I/O

GPIO Data Line

14

F8

IODATA[3]

I/O

GPIO Data Line

37

C3

IODATA[4]

I/O

GPIO Data Line

39

E3

IODATA[5]

I/O

GPIO Data Line

41

D2

IODATA[6]

I/O

GPIO Data Line

43

F1

IODATA[7]

I/O

GPIO Data Line

35

C2

GPIO_STROBE

I/O

GPIO Strobe Signal

4

G3

GPSO_REQ

O

GPSO Request Signal

CMOS Output Pad Buffer

28

C6

GPSO_SCKR

I

GPSO Serial Clock

CMOS Input Pad Buffer

33

A2

GPSO_DATA

O

GPSO Serial Data

CMOS Output Pad Buffer

Note: In functional mode TESTEN must be connected to VDD.

STA014-STA014B-STA014T

5/45