STB24NF10

N - CHANNEL 100V - 0.07

- 24A TO-263

LOW GATE CHARGE STripFET

TM

POWER MOSFET

PRELIMINARY DATA

s

TYPICAL R

DS(on)

= 0.07

s

EXCEPTIONAL dv/dt CAPABILITY

s

100% AVALANCHE TESTED

s

SURFACE-MOUNTING D

2

PAK (TO-263)

POWER PACKAGE IN TAPE & REEL

(SUFFIX "T4")

DESCRIPTION

This

MOSFET

series

realized

with

STMicroelectronics unique STripFET process has

specifically been designed to minimize input

capacitance and gate charge. It is therefore

suitable

as

primary

switch

in

advanced

high-efficiency, high-frequency isolated DC-DC

converters

for

Telecom

and

Computer

applications.

It

is

also

intended

for

any

applications with low gate drive requirements.

APPLICATIONS

s

HIGH-EFFICIENCY DC-DC CONVERTERS

s

UPS AND MOTOR CONTROL

�

INTERNAL SCHEMATIC DIAGRAM

April 2000

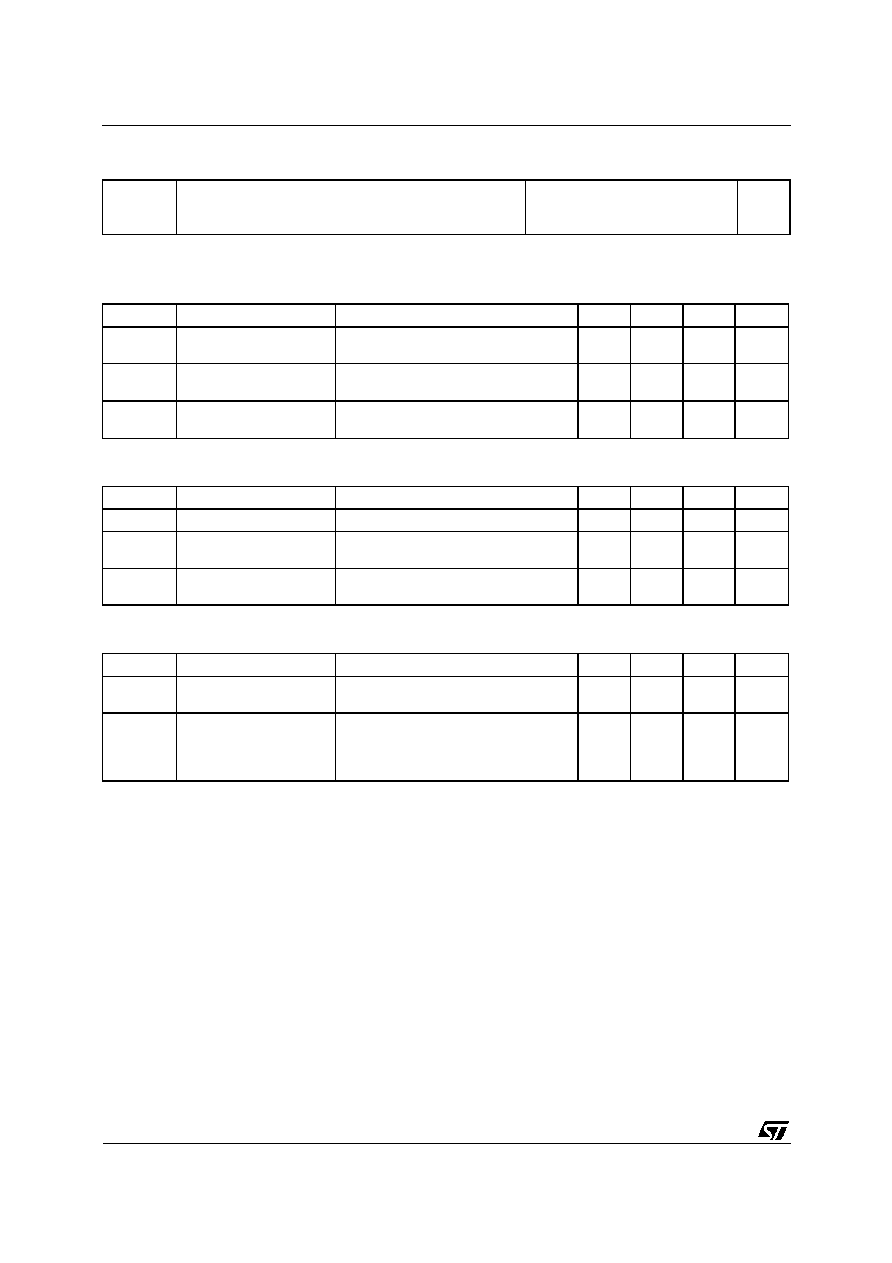

ABSOLUTE MAXIMUM RATINGS

Symb ol

Parameter

Value

Unit

V

DS

Drain-source Voltage (V

GS

= 0)

100

V

V

DGR

Drain- gate Voltage (R

GS

= 20 k

)

100

V

V

G S

G ate-source Volt age

�

20

V

I

D

Drain Current (continuous) at T

c

= 25

o

C

24

A

I

D

Drain Current (continuous) at T

c

= 100

o

C

15

A

I

DM

(

�

)

Drain Current (pulsed)

96

A

P

tot

T otal Dissipation at T

c

= 25

o

C

80

W

Derating Factor

0.53

W /

o

C

dv/ dt(

1

)

Peak Diode Recovery voltage slope

9

V/ns

E

AS

(

2

)

Single Pulse Avalanche Energy

75

mJ

T

st g

Storage Temperature

-65 to 175

o

C

T

j

Max. Operating Junction Temperature

175

o

C

(

�

) Pulse width limited by safe operating area

( 2) starting T

j

= 25

o

C, I

D

=24A , V

DD

= 50V

(1) I

SD

24 A, di/dt

300A/

�

s, V

DD

V

(BR)DSS

, T

j

T

JMA

TYPE

V

DSS

R

DS( on )

I

D

STB24NF10

100 V

< 0.077

24 A

1

3

D

2

PAK

TO-263

(Suffix "T4")

1/6

THERMAL DATA

R

thj -case

R

thj -amb

T

l

Thermal Resistance Junction-case

Max

Thermal Resistance Junction-ambient

Max

Maximum Lead Temperature F or Soldering Purpose

1.87

62.5

300

o

C/W

o

C/W

o

C

ELECTRICAL CHARACTERISTICS (T

case

= 25

o

C unless otherwise specified)

OFF

Symbo l

Parameter

Test Con ditions

Min.

Typ.

Max.

Unit

V

(BR)DSS

Drain-source

Breakdown Voltage

I

D

= 250

�

A

V

GS

= 0

100

V

I

DSS

Zero Gat e Voltage

Drain Current (V

GS

= 0)

V

DS

= Max Rat ing

V

DS

= Max Rat ing

T

c

=125

o

C

1

10

�

A

�

A

I

G SS

Gat e-body Leakage

Current (V

DS

= 0)

V

GS

=

�

20 V

�

100

nA

ON (

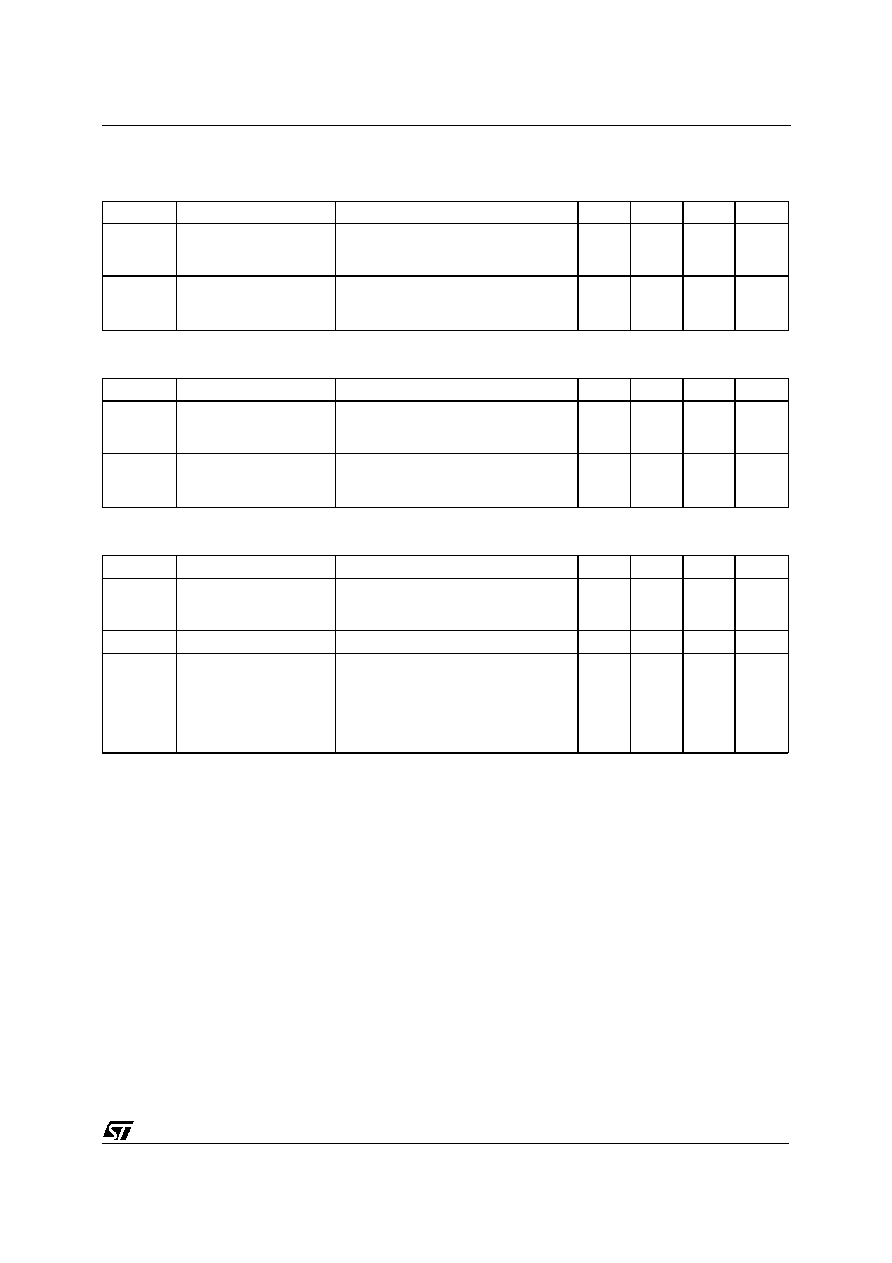

)

Symbo l

Parameter

Test Con ditions

Min.

Typ.

Max.

Unit

V

G S(th)

Gat e Threshold Voltage V

DS

= V

GS

I

D

= 250

�

A

2

3

4

V

R

DS(on)

Static Drain-source On

Resistance

V

GS

= 10 V

I

D

= 12 A

0.07

0.077

I

D(o n)

On State Drain Current

V

DS

> I

D(o n)

x R

DS(on )ma x

V

GS

= 10 V

24

A

DYNAMIC

Symbo l

Parameter

Test Con ditions

Min.

Typ.

Max.

Unit

g

f s

(

)

Forward

Transconductance

V

DS

> I

D(o n)

x R

DS(on )ma x

I

D

=12 A

20

S

C

iss

C

os s

C

rss

Input Capacitance

Out put Capacitance

Reverse Transfer

Capacitance

V

DS

= 25 V

f = 1 MHz

V

GS

= 0

870

125

52

pF

pF

pF

STB24NF10

2/6

ELECTRICAL CHARACTERISTICS (continued)

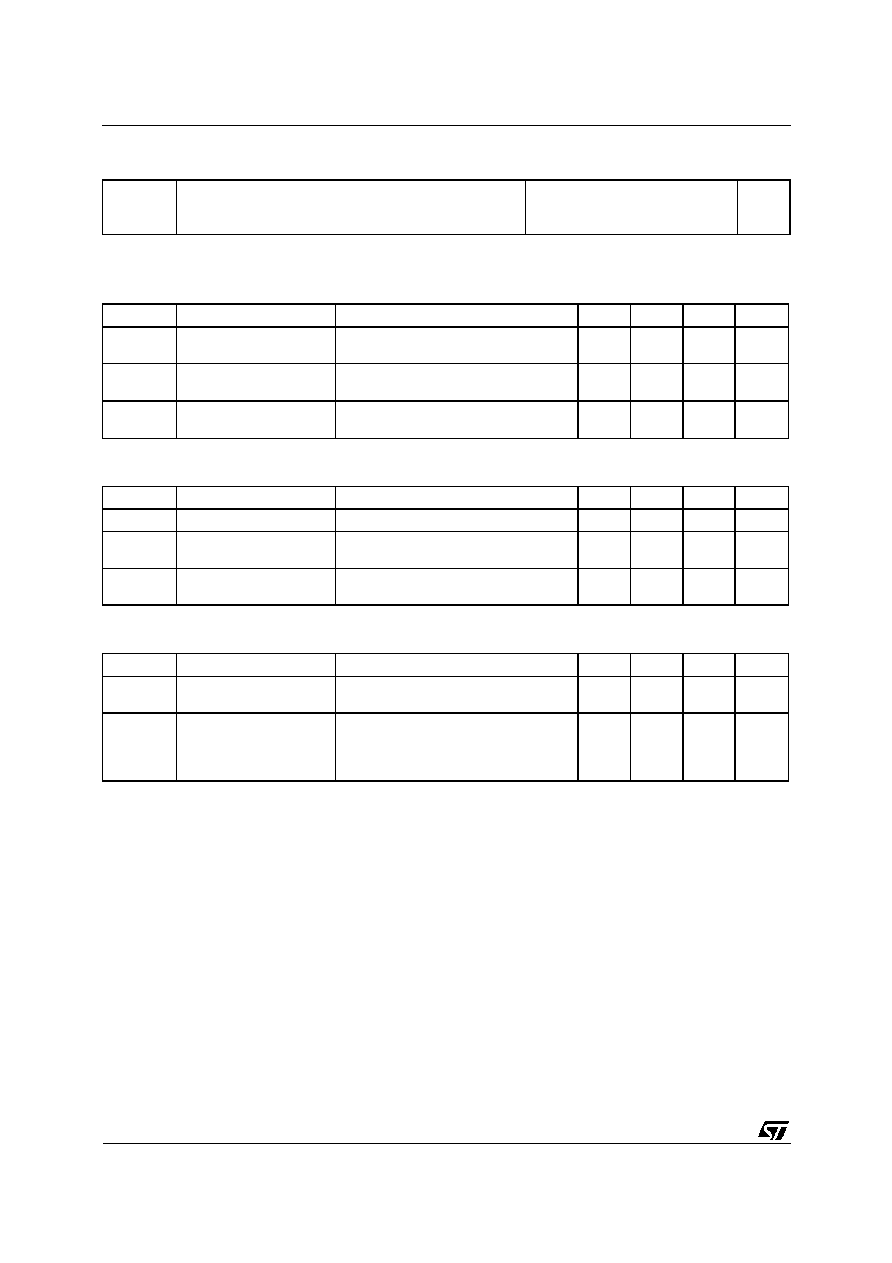

SWITCHING ON

Symbo l

Parameter

Test Con ditions

Min.

Typ.

Max.

Unit

t

d(on)

t

r

Turn-on Delay T ime

Rise Time

V

DD

= 50 V

I

D

= 12 A

R

G

= 4.7

V

G S

= 10 V

(Resistive Load, see fig. 3)

58

45

ns

ns

Q

g

Q

gs

Q

gd

Tot al G ate Charge

Gat e-Source Charge

Gat e-Drain Charge

V

DD

= 80 V I

D

= 24 A V

GS

= 10 V

30

6

10

nC

nC

nC

SWITCHING OFF

Symbo l

Parameter

Test Con ditions

Min.

Typ.

Max.

Unit

t

d(of f)

t

f

Turn-off Delay T ime

Fall T ime

V

DD

= 27 V

I

D

= 12 A

R

G

= 4.7

V

G S

= 10 V

(Resistive Load, see fig. 3)

49

17

ns

ns

t

d(of f)

t

f

t

c

Off -volt age Rise T ime

Fall T ime

Cross-over Time

Vclamp = 80 V

I

D

= 24 A

R

G

= 4.7

V

G S

= 10 V

(Induct ive Load, see fig. 5)

43

36

39

ns

ns

ns

SOURCE DRAIN DIODE

Symbo l

Parameter

Test Con ditions

Min.

Typ.

Max.

Unit

I

SD

I

SDM

(

�

)

Source-drain Current

Source-drain Current

(pulsed)

24

96

A

A

V

SD

(

)

Forward On Voltage

I

SD

= 24 A

V

GS

= 0

1. 5

V

t

rr

Q

rr

I

RRM

Reverse Recovery

Time

Reverse Recovery

Charge

Reverse Recovery

Current

I

SD

= 24 A

di/dt = 100 A/

�

s

V

DD

= 50 V

T

j

= 150

o

C

(see t est circuit, f ig. 5)

100

375

7.5

ns

nC

A

(

) Pulsed: Pulse duration = 300

�

s, duty cycle 1.5 %

(

�

) Pulse width limited by safe operatingarea

STB24NF10

3/6

Fig. 1: Unclamped Inductive Load Test Circuit

Fig. 3: Switching Times Test Circuits For

Resistive Load

Fig. 2: Unclamped Inductive Waveform

Fig. 4: Gate Charge test Circuit

Fig. 5: Test Circuit For Inductive Load Switching

And Diode Recovery Times

STB24NF10

4/6

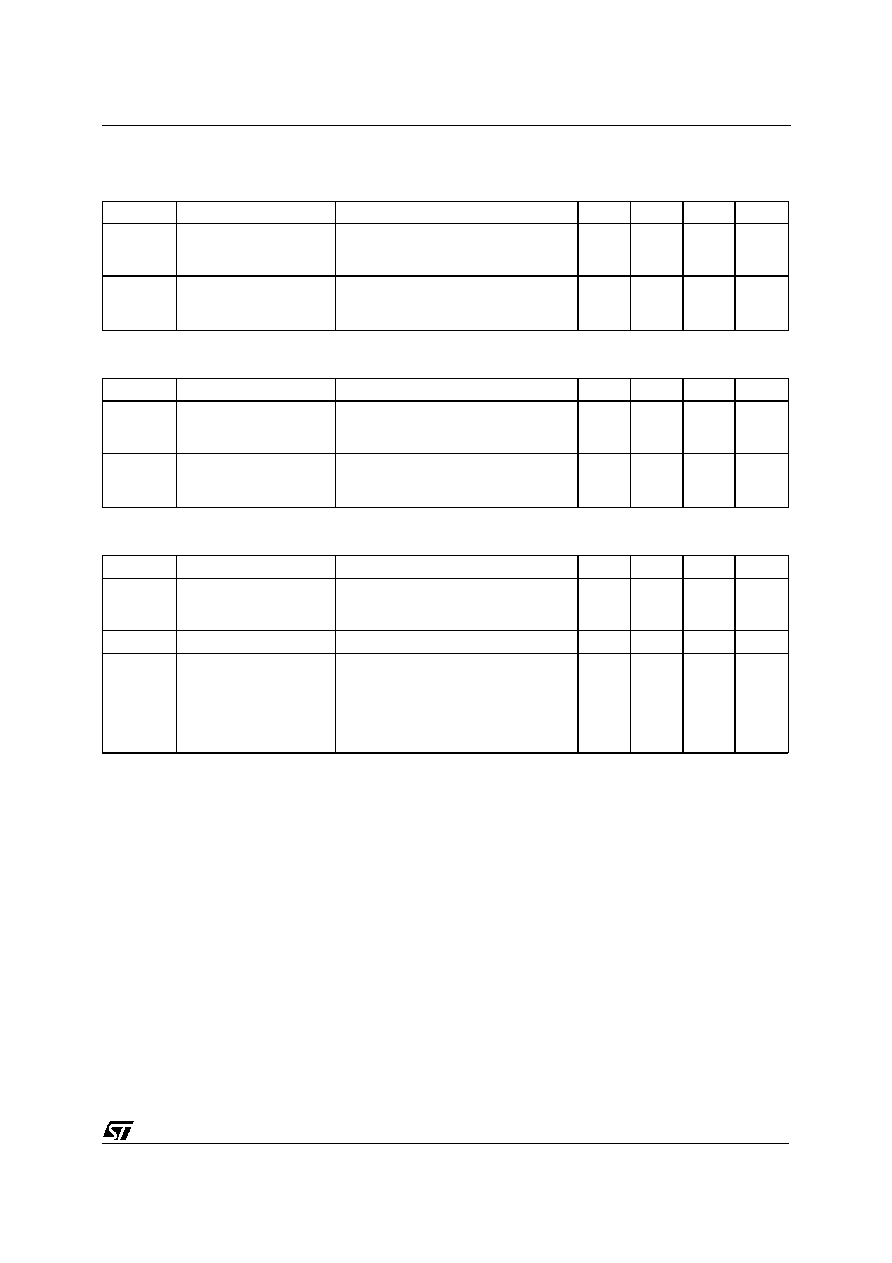

DIM.

mm

inch

MIN.

TYP.

MAX.

MIN.

TYP.

MAX.

A

4.4

4.6

0.173

0.181

A1

2.49

2.69

0.098

0.106

B

0.7

0.93

0.027

0.036

B2

1.14

1.7

0.044

0.067

C

0.45

0.6

0.017

0.023

C2

1.21

1.36

0.047

0.053

D

8.95

9.35

0.352

0.368

E

10

10.4

0.393

0.409

G

4.88

5.28

0.192

0.208

L

15

15.85

0.590

0.624

L2

1.27

1.4

0.050

0.055

L3

1.4

1.75

0.055

0.068

L2

L3

L

B2

B

G

E

A

C2

D

C

A1

DETAIL "A"

DETAIL "A"

A2

P011P6/E

TO-263 (D

2

PAK) MECHANICAL DATA

STB24NF10

5/6