1/10

June 2005

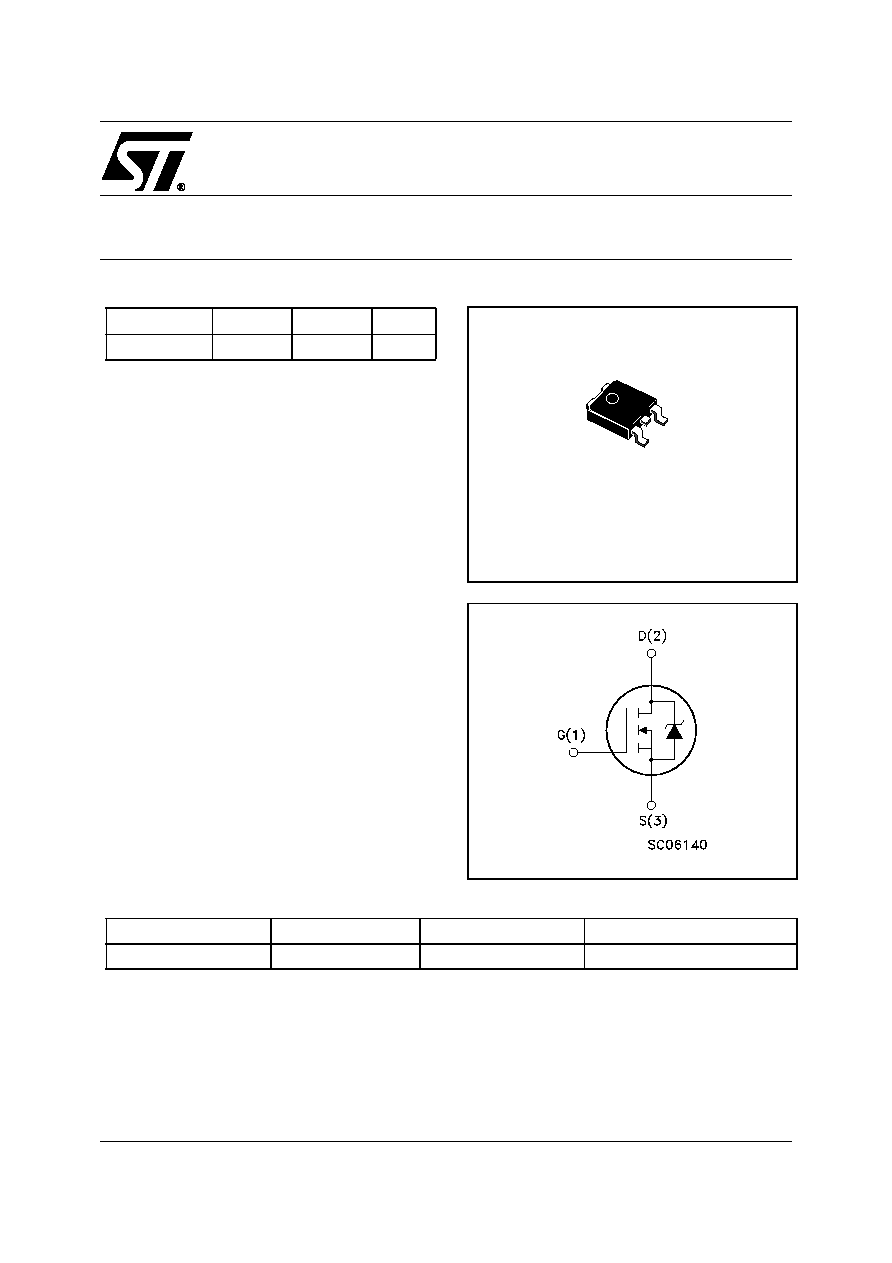

STD22NM20N

N-CHANNEL 200V - 0.088

- 22A DPAK

ULTRA LOW GATE CHARGE MDmeshTM II MOSFET

Table 1: General Features

s

WORLDWIDE LOWEST GATE CHARGE

s

TYPICAL R

DS

(on) = 0.088

s

HIGH dv/dt and AVALANCHE CAPABILITIES

s

LOW INPUT CAPACITANCE

s

LOW GATE RESISTANCE

DESCRIPTION

This 200V MOSFET with a new advanced layout

brings all unique advantages of MDmesh technol-

ogy to lower voltages. The device exhibits world-

wide lowest gate charge for any given on-

resistance. Its use is therefore ideal as primary

switch in isolated DC-DC converters for Telecom

and Computer applications. Used in combination

with secondary-side low-voltage STripFETTM

products, it contributes to reducting losses and

boosting effeciency.

APPLICATIONS

The MDmeshTM family is very suitable for increas-

ing power density allowing system miniaturization

and higher efficiencies

Table 2: Order Codes

Figure 1: Package

Figure 2: Internal Schematic Diagram

TYPE

V

DSS

R

DS(on)

I

D

STD22NM20N

200 V

< 0.105

22 A

1

3

DPAK

SALES TYPE

MARKING

PACKAGE

PACKAGING

STD22NM20NT4

D22NM20N

DPAK

TAPE & REEL

Rev. 4

STD22NM20N

2/10

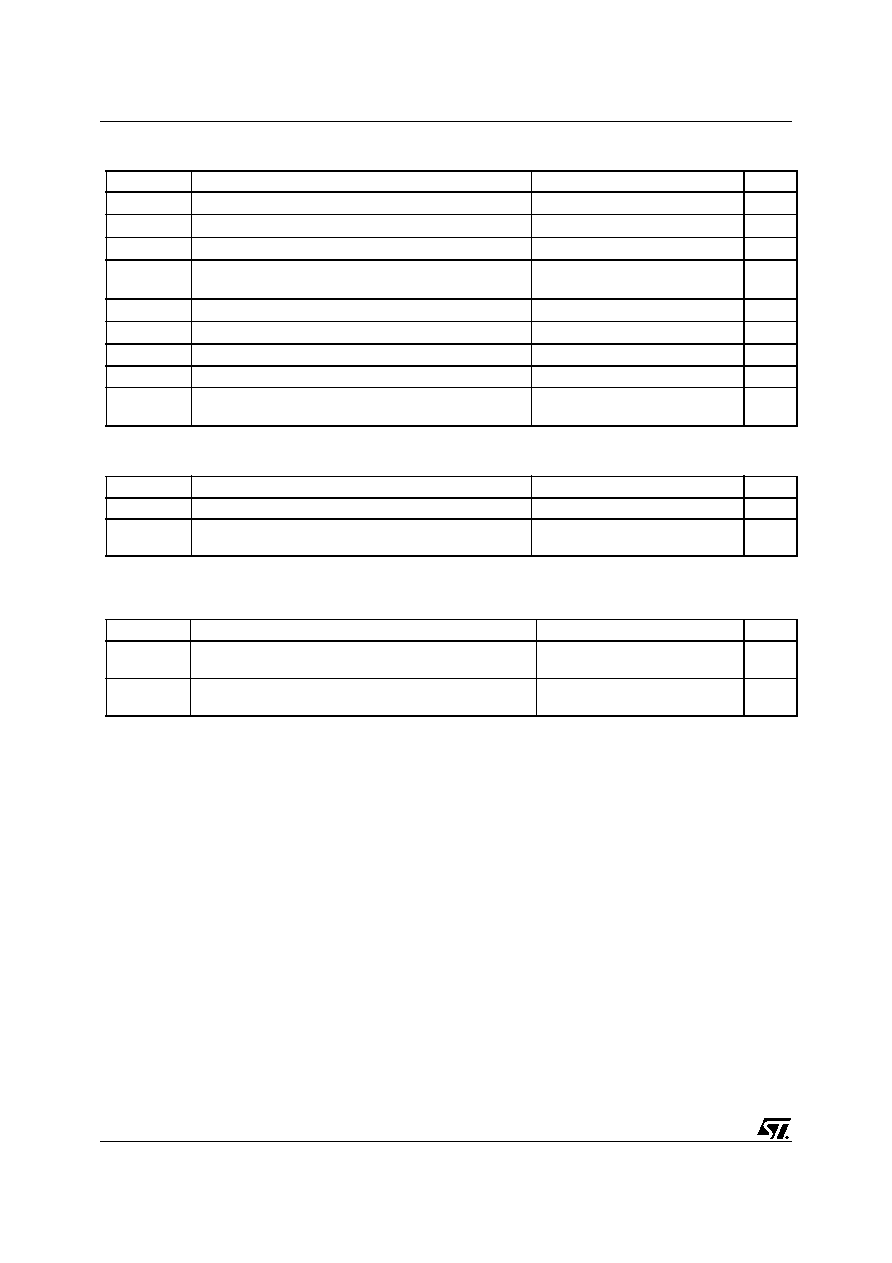

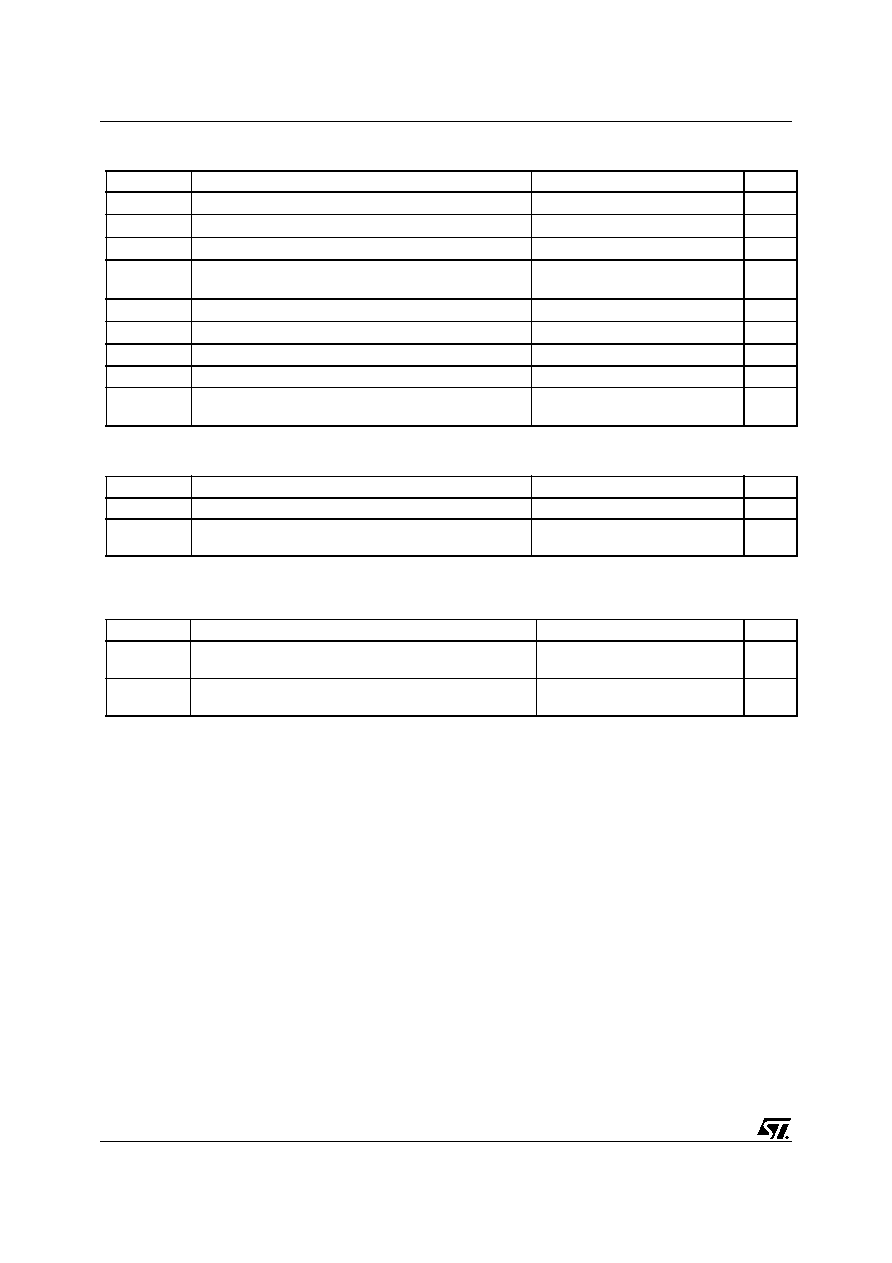

Table 3: Absolute Maximum ratings

(*) I

SD

22A, di/dt

400A/µs, V

DD

= 80%

V

(BR)DSS

Table 4: Thermal Data

(*) When mounted on 1 inch² FR-4 board, 2 oz Cu, t

10

sec

Table 5: Avalanche Characteristics

Symbol

Parameter

Value

Unit

V

DS

Drain-source Voltage (V

GS

= 0)

200

V

V

DGR

Drain-gate Voltage (R

GS

= 20 k

)

200

V

V

GS

Gate- source Voltage

± 20

V

I

D

Drain Current (continuous) at T

C

= 25°

Drain Current (continuous) at T

C =

100°

22

13.7

A

A

I

DM

(*)

Drain Current (pulsed)

88

A

P

TOT

Total Dissipation at T

C

= 25°C

100

W

Derating Factor

0.8

W/°C

dv/dt (2)

Peak Diode Recovery voltage slope

14

V/ns

T

j

T

stg

Storage Temperature

Max Operating Junction Temperature

150

-65 to 150

°C

°C

Rthj-case

Thermal Resistance Junction-case Max

1.25

°C/W

Rthj-amb

Thermal Resistance Junction-ambient Max

100

°C/W

Rthj-ambT

l

Thermal Resistance Junction-pcb (*)

Maximum Lead Temperature For Soldering Purpose

43

275

°C/W

°C

Symbol

Parameter

Max Value

Unit

I

AS

Avalanche Current, Repetitive or Not-Repetitive

(pulse width limited by T

j

max)

22

A

E

AS

Single Pulse Avalanche Energy

(starting T

j

= 25 °C, I

D

= 22 A, V

DD

= 50 V)

380

mJ

3/10

STD22NM20N

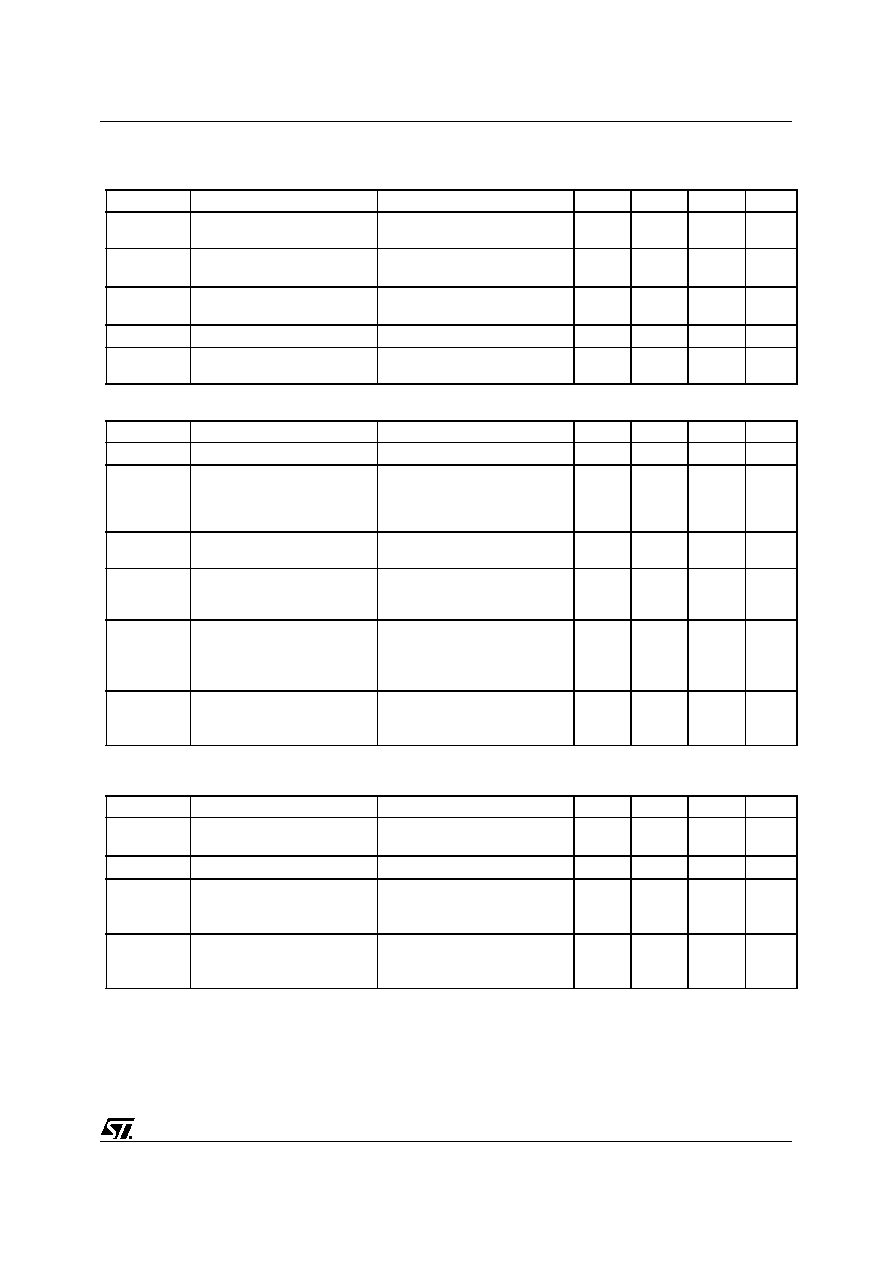

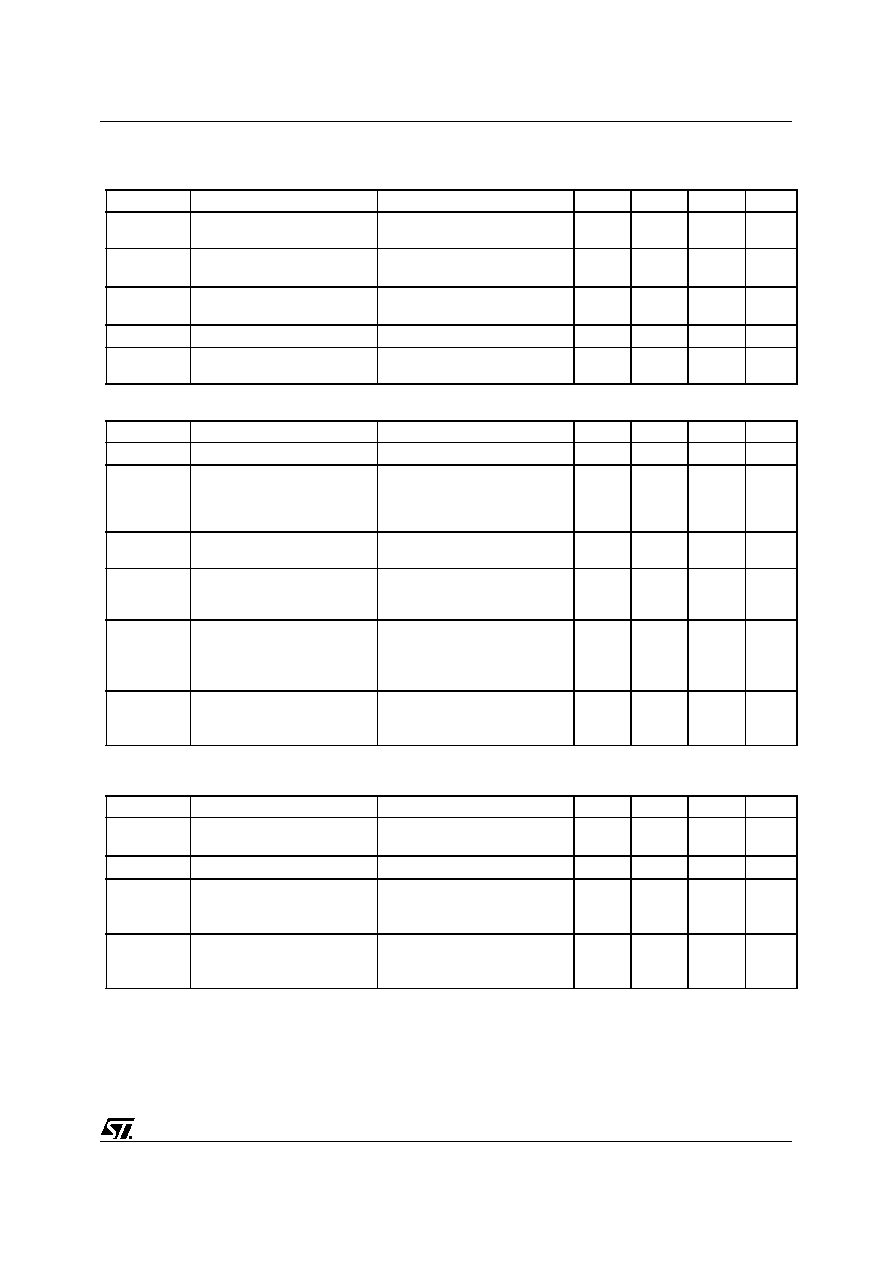

ELECTRICAL CHARACTERISTICS (T

CASE

=25°C UNLESS OTHERWISE SPECIFIED)

Table 6: On/Off

Table 7: Dynamic

(**) C

oss eq.

is defined as a constant equivalent capacitance giving the same charging time as C

oss

when V

DS

increases from 0 to 80% V

DSS

Table 8: Source Drain Diode

(1) Pulse width limited by safe operating area.

(2) Pulsed: Pulse duration = 300 µs, duty cycle 1.5 %

Symbol

Parameter

Test Conditions

Min.

Typ.

Max.

Unit

V

(BR)DSS

Drain-source

Breakdown Voltage

I

D

= 1mA, V

GS

= 0

200

V

I

DSS

Zero Gate Voltage

Drain Current (V

GS

= 0)

V

DS

= Max Rating

V

DS

= Max Rating, T

C

= 125 °C

1

10

µA

µA

I

GSS

Gate-body Leakage

Current (V

DS

= 0)

V

GS

= ± 20V

100

nA

V

GS(th)

Gate Threshold Voltage

V

DS

= V

GS

, I

D

= 250 µA

3.5

4.2

5

V

R

DS(on)

Static Drain-source On

Resistance

V

GS

= 10V, I

D

= 11 A

0.088

0.105

Symbol

Parameter

Test Conditions

Min.

Typ.

Max.

Unit

g

fs

(2)

Forward Transconductance

V

DS

= 15 V

,

I

D

=11 A

8

S

C

iss

C

oss

C

rss

Input Capacitance

Output Capacitance

Reverse Transfer

Capacitance

V

DS

= 25V, f = 1 MHz, V

GS

= 0

800

330

130

pF

pF

pF

C

oss eq. (**)

Equivalent Output

Capacitiance

V

GS

= 0 V, V

DS

= 0 V to 400 V

225

pF

R

G

Gate Input Resistance

f= 1MHz Gate DC Bias = 0

Test Sgnal Level = 20 mV

Open Drain

5

t

d(on)

t

r

t

r(Voff)

t

f

Turn-on Delay Time

Rise Time

Turn-off Delay Time

Fall Time

V

DD

= 100 V, I

D

= 11 A

R

G

= 4.7

V

GS

= 10 V

(see Figure 15)

40

15

40

11

ns

ns

ns

ns

Q

g

Q

gs

Q

gd

Total Gate Charge

Gate-Source Charge

Gate-Drain Charge

V

DD

= 100 V, I

D

= 20 A,

V

GS

= 10 V

(see Figure 19)

32

6

25

50

nC

nC

nC

Symbol

Parameter

Test Conditions

Min.

Typ.

Max.

Unit

I

SD

I

SDM

(1)

Source-drain Current

Source-drain Current (pulsed)

22

88

A

A

V

SD

(2)

Forward On Voltage

I

SD

= 20 A, V

GS

= 0

1.3

V

t

rr

Q

rr

I

RRM

Reverse Recovery Time

Reverse Recovery Charge

Reverse Recovery Current

I

SD

= 20 A, di/dt = 100 A/µs

V

DD

= 100V, T

j

= 25°C

(see test circuit, Figure 17)

160

960

128

ns

µC

A

t

rr

Q

rr

I

RRM

Reverse Recovery Time

Reverse Recovery Charge

Reverse Recovery Current

I

SD

= 20 A, di/dt = 100 A/µs

V

DD

= 100V, T

j

= 150°C

(see test circuit, Figure 17)

225

1642

15

ns

µC

A

STD22NM20N

4/10

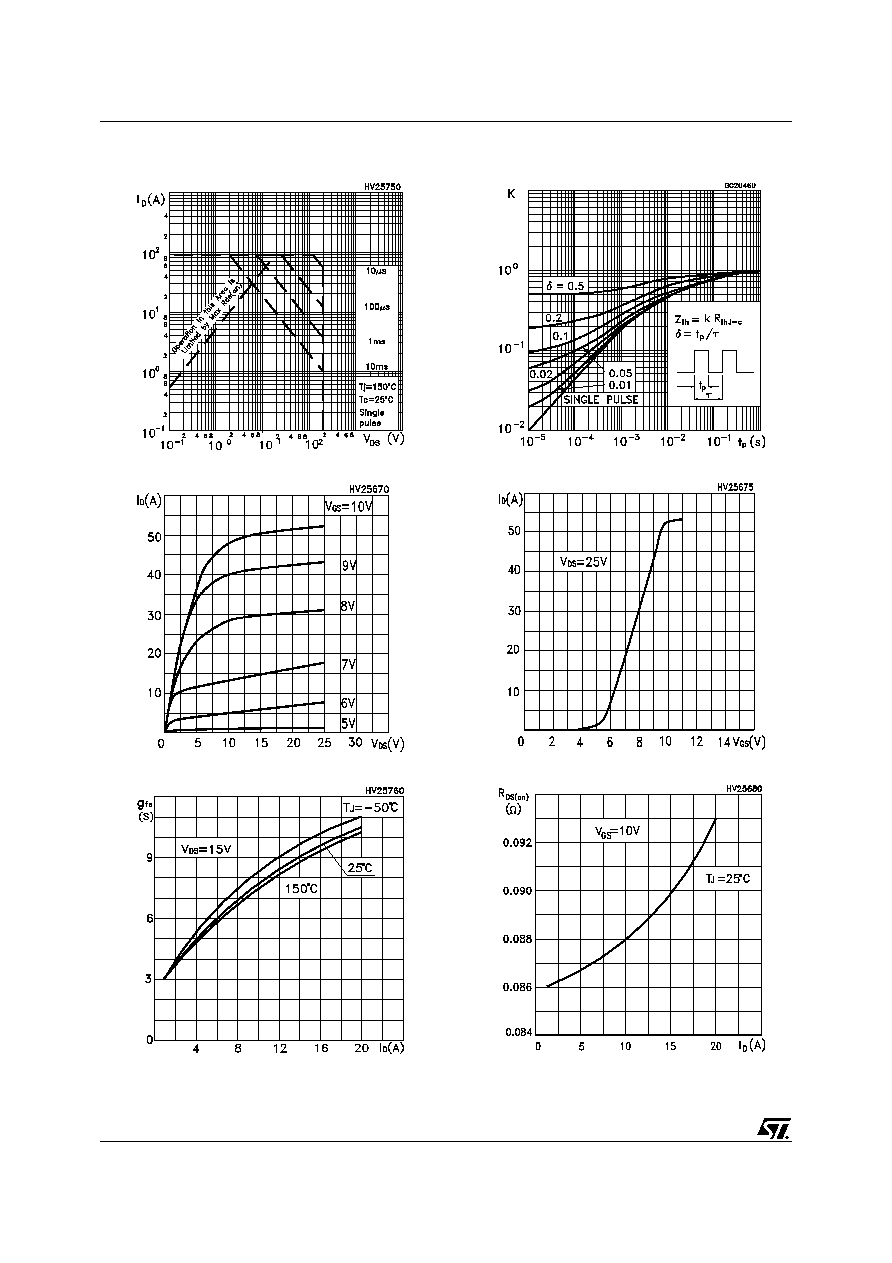

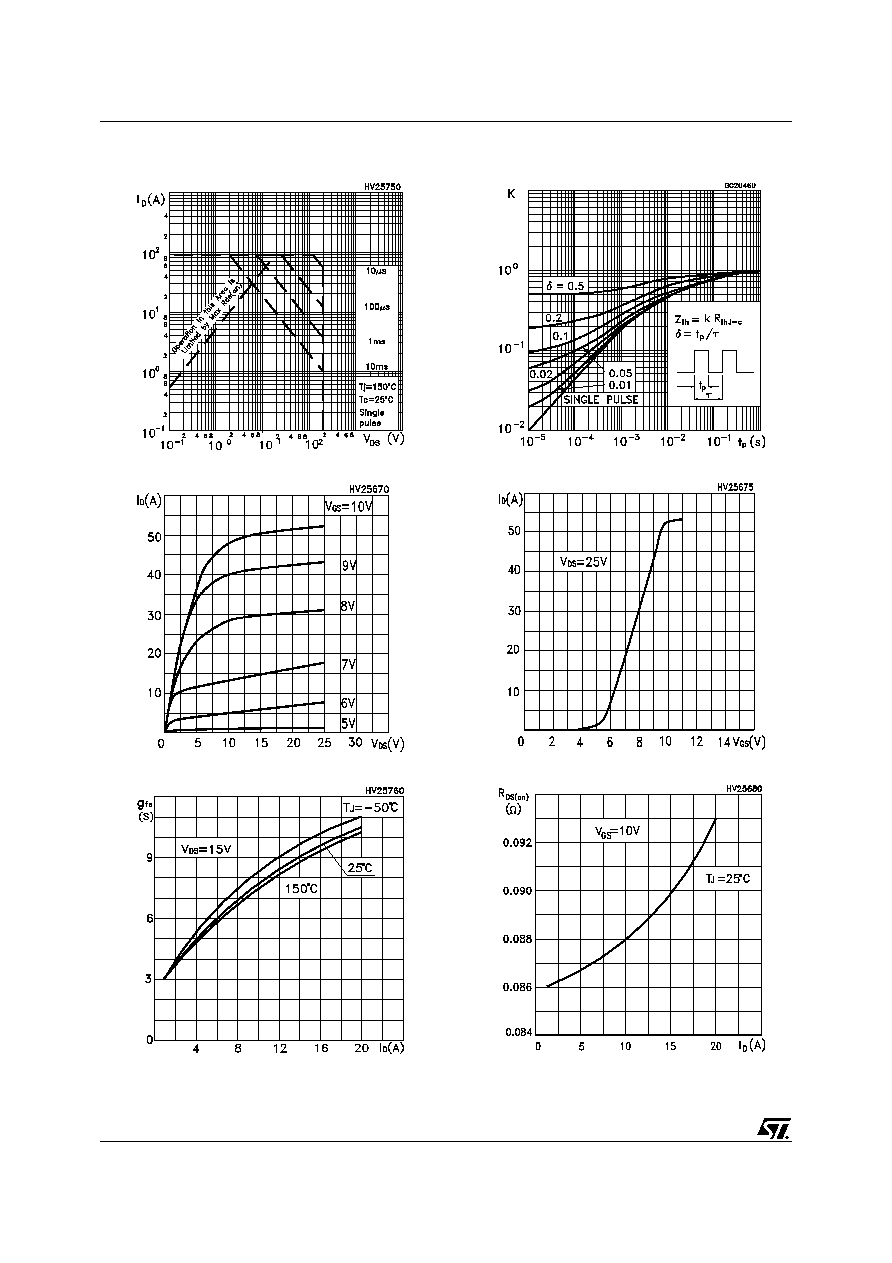

Figure 3: Safe Operating Area

Figure 4: Output Characteristics

Figure 5: Transconductance

Figure 6: Thermal Impedance

Figure 7: Transfer Characteristics

Figure 8: Static Drain-source On Resistance

5/10

STD22NM20N

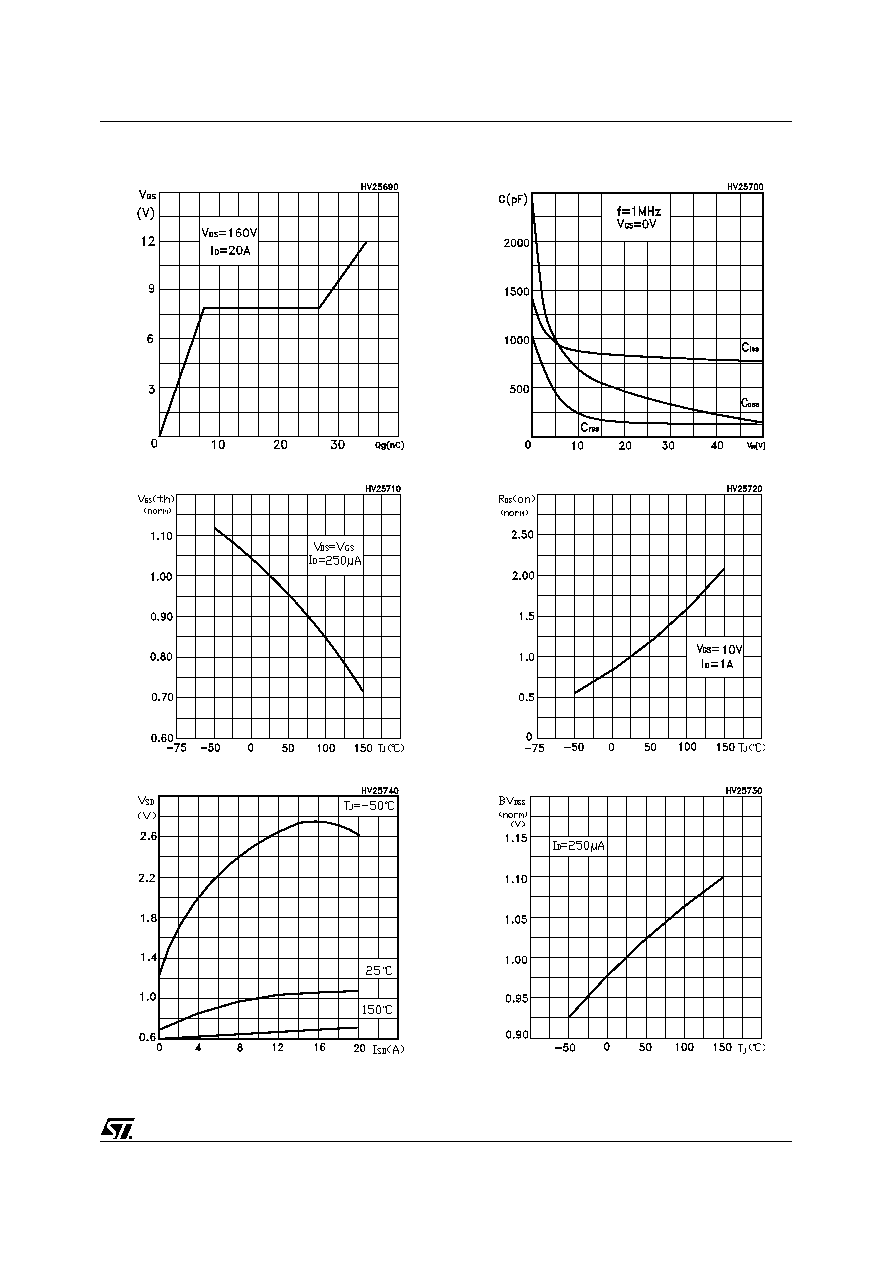

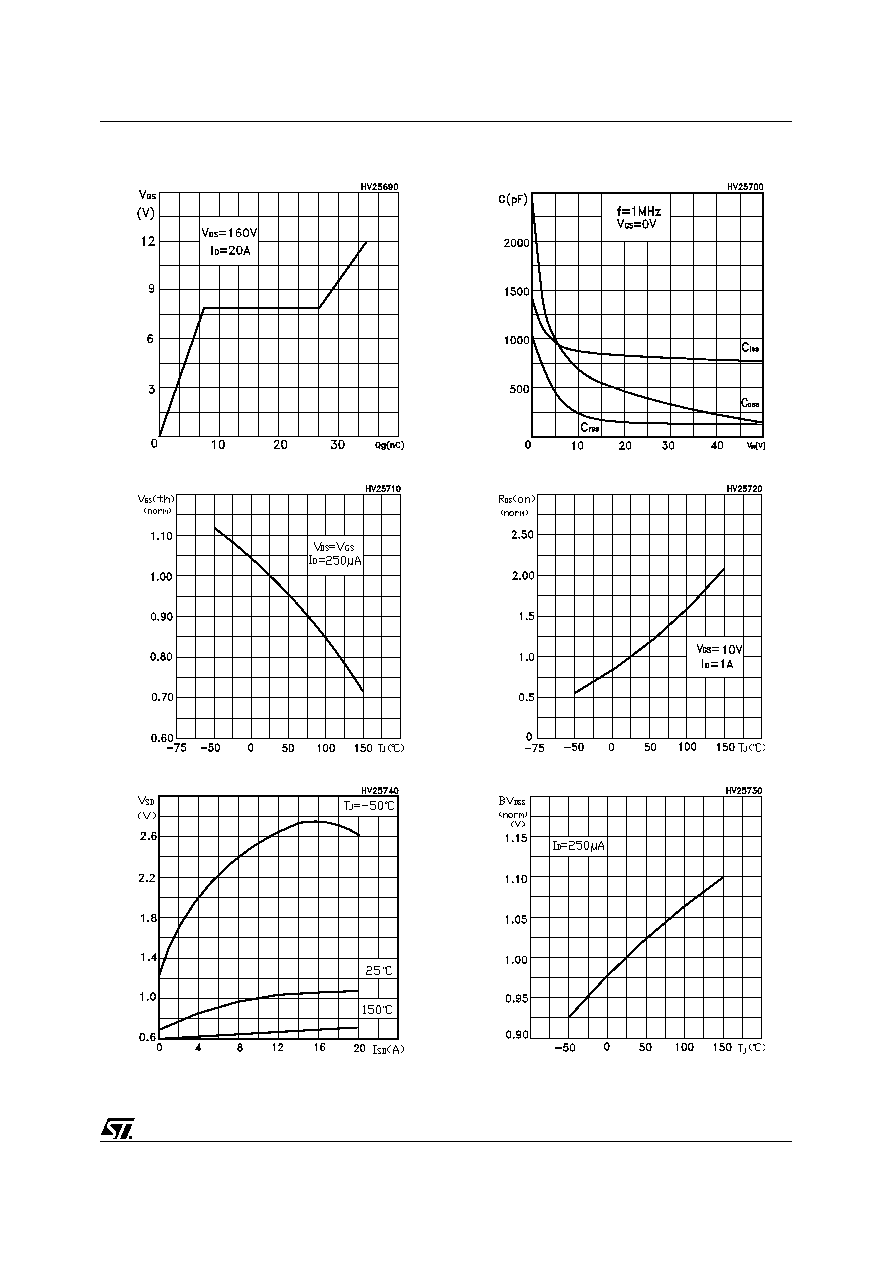

Figure 9: Gate Charge vs Gate-source Voltage

Figure 10: Normalized Gate Thereshold Volt-

age vs Temperature

Figure 11: Source-Drain Diode Forward Char-

acteristics

Figure 12: Capacitance Variations

Figure 13: Normalized On Resistance vs Tem-

perature

Figure 14: Normalized BVdss vs Temperature