1/66

STE2004

July 2004

1

FEATURES

102 x 65 bits Display Data RAM

Programmable MUX rate

Programmable Frame Rate

X,Y Programmable Carriage Return

Dual Partial Display Mode

Row by Row Scrolling

N-Line Inversion

Automatic data RAM Blanking procedure

Selectable Input Interface:

· I

2

C Bus Fast and Hs-mode (read and write)

· 68000 & 8080 Parallel Interfaces (read and write)

· 3-lines and 4-lines SPI Interface (read and write)

· 3-lines 9 bit Serial Interface (read and write)

Fully Integrated Oscillator requires no external

components

CMOS Compatible Inputs

Fully Integrated Configurable LCD bias voltage

generator with:

· Selectable multiplication factor (up to

5

X

)

· Effective sensing for High Precision Output

· Eight selectable temperature compensation

coefficients

Designed for chip-on-glass (COG) applications.

Low Power Consumption, suitable for battery

operated systems

Logic Supply Voltage range from 1.7 to 3.6V

High Voltage Generator Supply Voltage range

from 1.75 to 4.5V

Display Supply Voltage range from 4.5 to 14.5V

Backward Compatibility with STE2001/2

2

DESCRIPTION

The STE2004 is a low power CMOS LCD control-

ler driver. Designed to drive a 65 rows by 102 col-

umns graphic display, it provides all necessary

functions in a single chip, including on-chip LCD

supply and bias voltages generators, resulting in a

minimum of externals components and in a very

low power consumption.

STE2004 features six standard interfaces (3-lines

Serial, 3-lines SPI, 4-lines SPI, 68000 Parallel,

8080 parallel & I

2

C) for ease of interfacing with the

host micro-controller

Table 1. Order Codes

Part Numbers

Type

STE2004DIE1

Bumped Wafers

STE2004DIE2

Bumped Dice on Waffle Pack

102 X 65 SINGLE CHIP LCD CONTROLLER / DRIVER

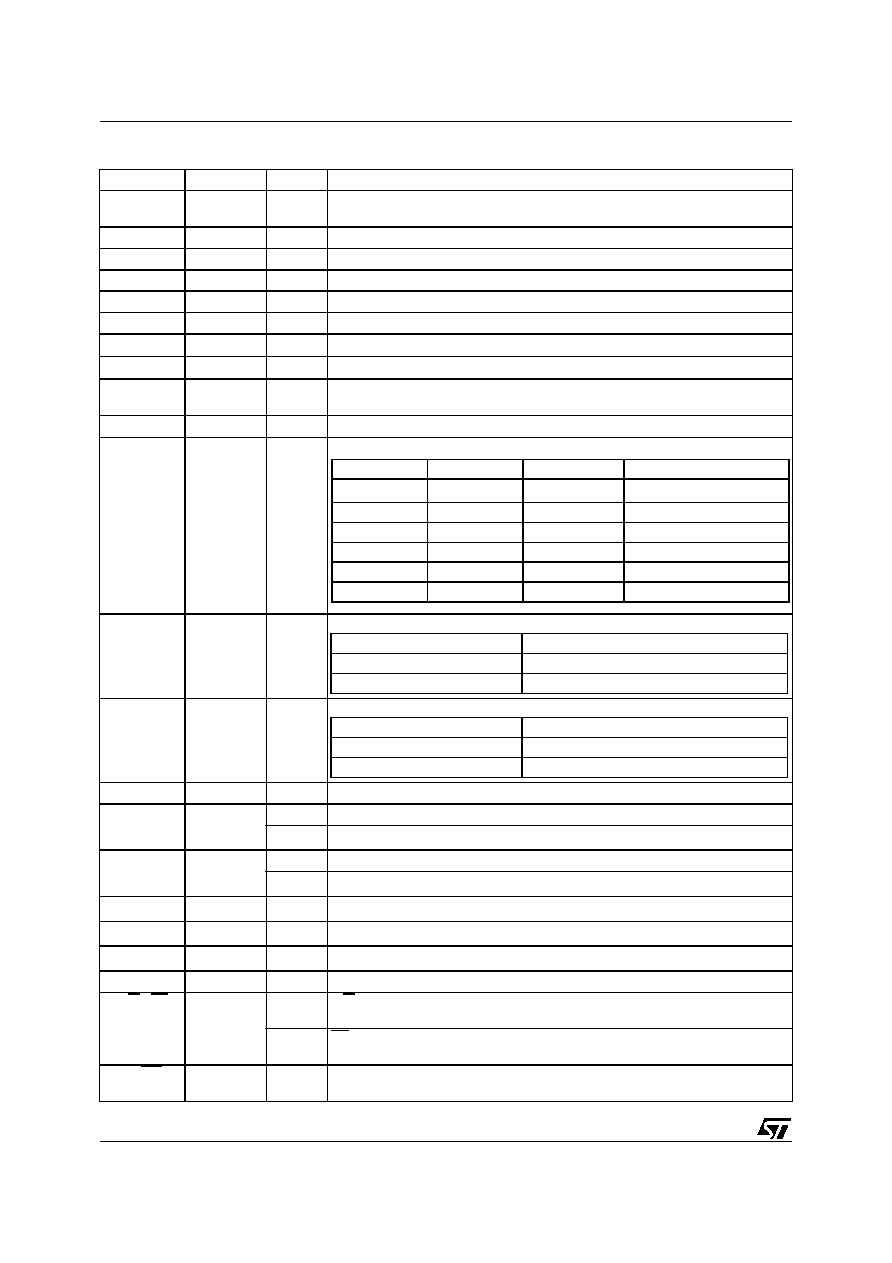

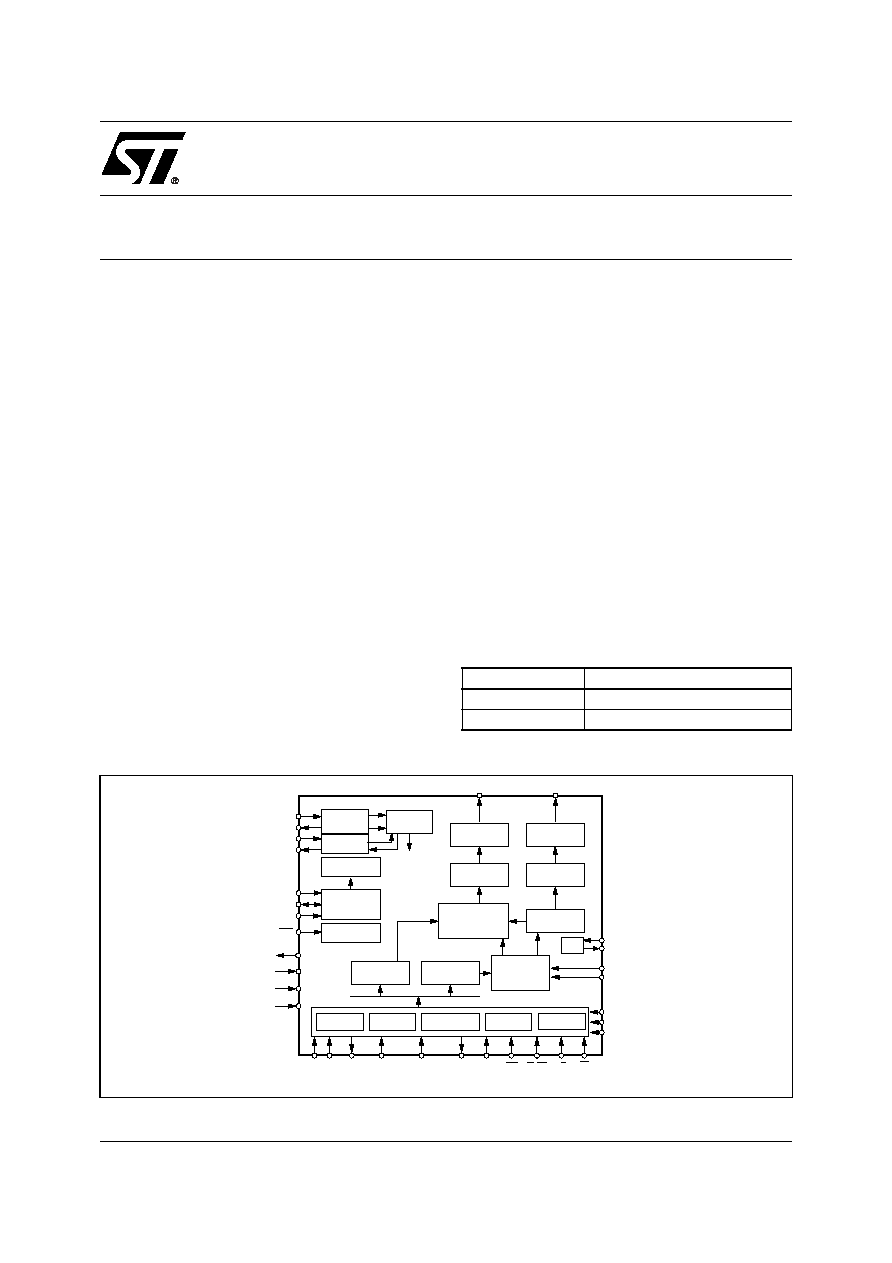

Figure 1. Block Diagram

COLUMN

DRIVERS

ROW

DRIVERS

DATA

LATCHES

65 x 102

RAM

DISPLAY

CONTROL

LOGIC

SCROLL

LOGIC

DATA

REGISTER

INSTRUCTION

REGISTER

CO to C101

R0 to R64

VSENSE SLAVE

RES

VDD1,2

CLOCK

TIMING

GENERATOR

BIAS VOLTAGE

GENERATOR

HIGH VOLTAGE

GENERATOR

RESET

TEST

SHIFT

REGISTER

VLCD

V

SS

SEL1,2

EXT

ICON_MODE

VSSAUX

SAO

SDIN/SDA_IN SDA_OUT

SCLK/SCL

DB0

to

DB7

9 Bit SERIAL

D/C

CS

SA1

SDOUT

E/WR R/W- RD

I2C BUS

3 & 4 Line SPI

Parallel 8080

Parallel 68K

SEL 0

SEL 1

SEL 2

TEST_VREF

TEST_MODE

LR0047

OSC

OSC_IN

OSC_OUT

FR_IN

FR_OUT

MASTER

SLAVE SYNC

VLCDSENSE

Rev. 4

STE2004

2/66

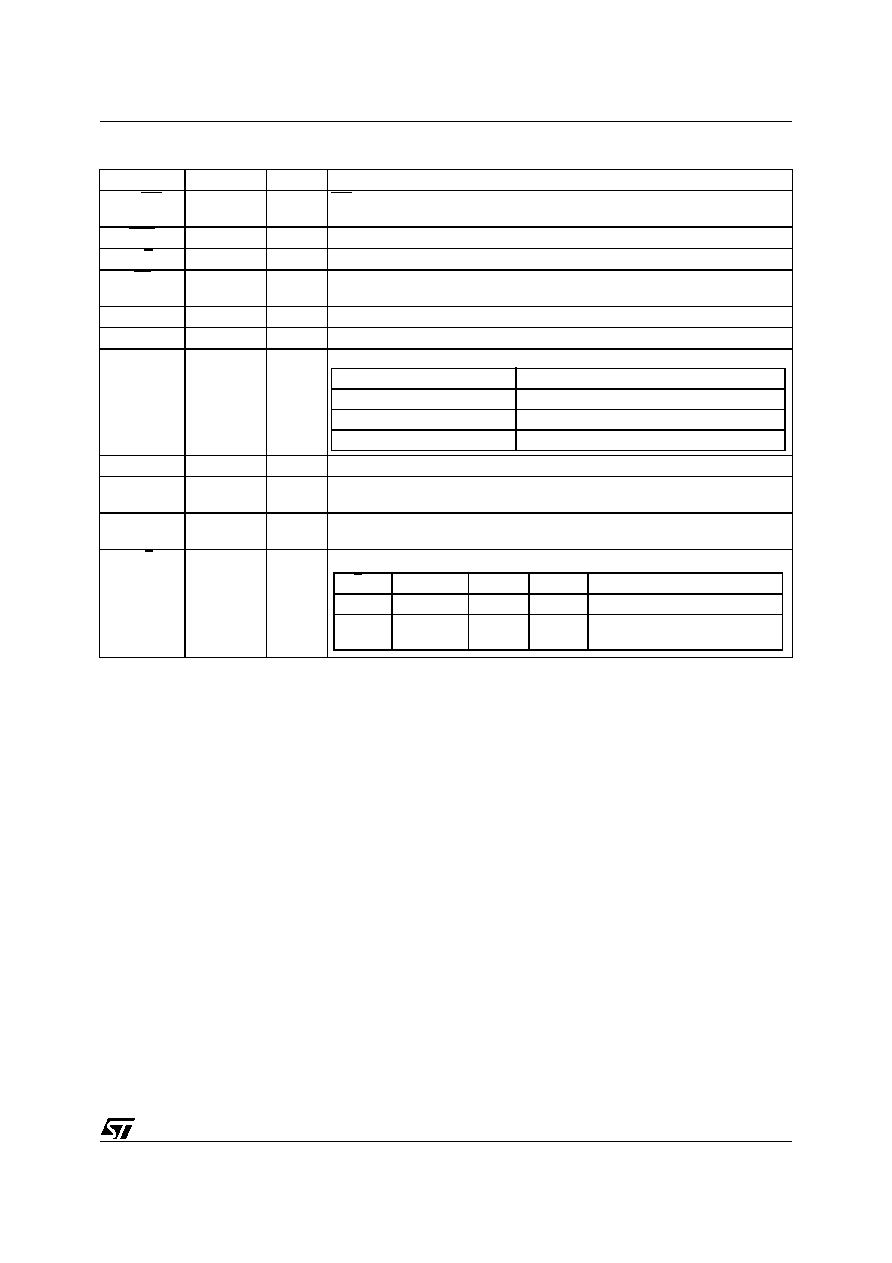

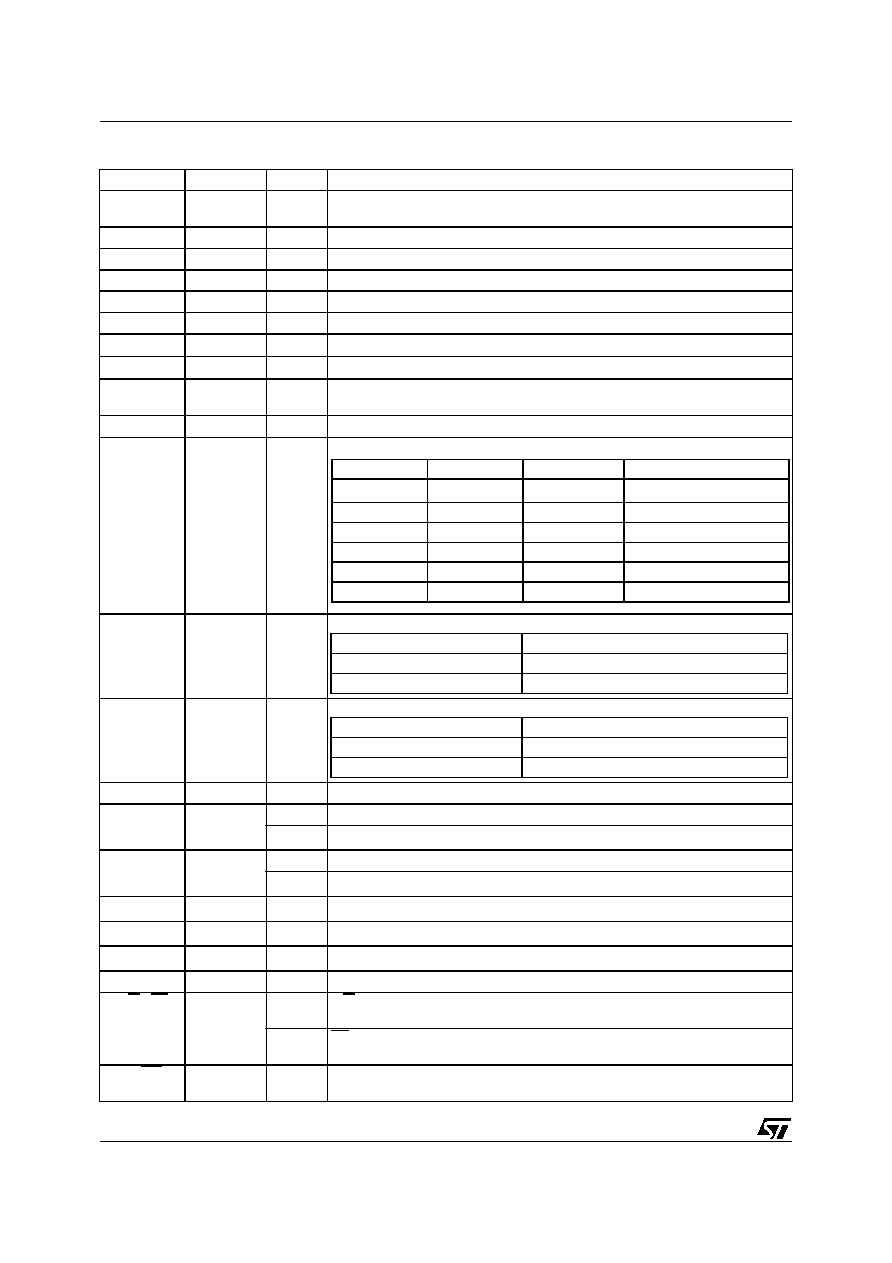

Table 2. Pin Description

N°

Pad

Type

Function

R0 to R64

1-6

109-141

O

LCD Row Driver Output

C0 to C101

6-107

O

LCD Column Driver Output

V

SS

192-203

GND

Ground pads.

V

DD1

156-163

Supply

IC Positive Power Supply

V

DD2

164-171

Supply

Internal Generator Supply Voltages.

V

LCD

205-209

Supply

Voltage Multiplier Output

V

LCDSENSE

204

Supply

Voltage Multiplier Regulation Input. V

LCDOUT

Sensing for Output Voltage Fine Tuning

V

SENSE_SLAVE

145

Supply

Voltage reference for SLAVE CHARGE PUMP

V

SSAUX

190-177-

147

O

Ground Reference for Pins Configuration

V

DD1AUX

142

O

VDD1 Reference for Pins Configuration

SEL1,2,3

152

153

154

I

Interface Mode Selection - CANNOT BE LEFT FLOATING

EXT_SET

151

I

Extended Instruction Set Selection - CANNOT BE LEFT FLOATING

ICON_MODE

155

I

Extended Instruction Set Selection - CANNOT BE LEFT FLOATING

SDOUT

180

O

Serial & SPI Data Output - IF UNUSED MUST BE LEFT FLOATING

SDIN - SDAIN

179

I

SDIN - Serial & SPI Interface Data Input - CANNOT BE LEFT FLOATING

I

SDAIN - I

2

C Bus Data In - CANNOT BE LEFT FLOATING

SCLK - SCL

181

I

SCLK - Serial & SPI Interface Clock - CANNOT BE LEFT FLOATING

I

SCL - I

2

C bus Clock - CANNOT BE LEFT FLOATING

SDA_OUT

178

O

I

2

C Bus Data Out IF UNUSED MUST BE LEFT FLOATING

SA0

149

I

I

2

C Slave Address BIT 0 - CANNOT BE LEFT FLOATING

SA1

148

I

I

2

C Slave Address BIT 1- CANNOT BE LEFT FLOATING

DB0 to DB7

182-189

I/O

Parallel Interface 8 Bit Data Bus - CANNOT BE LEFT FLOATING

R/W - RD

175

I

R/W - 68000 Series Parallel Interface Read & Write Control Input

- CANNOT BE LEFT FLOATING

I

RD - 8080 Series Parallel Interface Read enable Clock Input

- CANNOT BE LEFT FLOATING

E / WR

176

I

E - 68000 Series Parallel Interface Read & Write Clock Input

- CANNOT BE LEFT FLOATING

SEL3

SEL2

SEL1

Interface

GND / VSSAUX

GND / VSSAUX

GND / VSSAUX

I

2

C

GND / VSSAUX

GND / VSSAUX

VDD1

SPI 4-Lines 8 bit

GND / VSSAUX

VDD1

GND / VSSAUX

SPI 3-Lines 8 bit

GND / VSSAUX

VDD1

VDD1

Serial 3-Lines 9 bit

VDD1

GND / VSSAUX

GND / VSSAUX

Parallel 8080-series

VDD1

GND / VSSAUX

VDD1

Parallel 68000-series

EXT PAD CONFIG

INSTRUCTION SET SELECTED

GND or VSSAUX

BASIC

VDD1

EXTENDED

ICON MODE PAD CONFIG

ICON MODE STATUS

GND or VSSAUX

DISBLED

VDD1

ENABLED

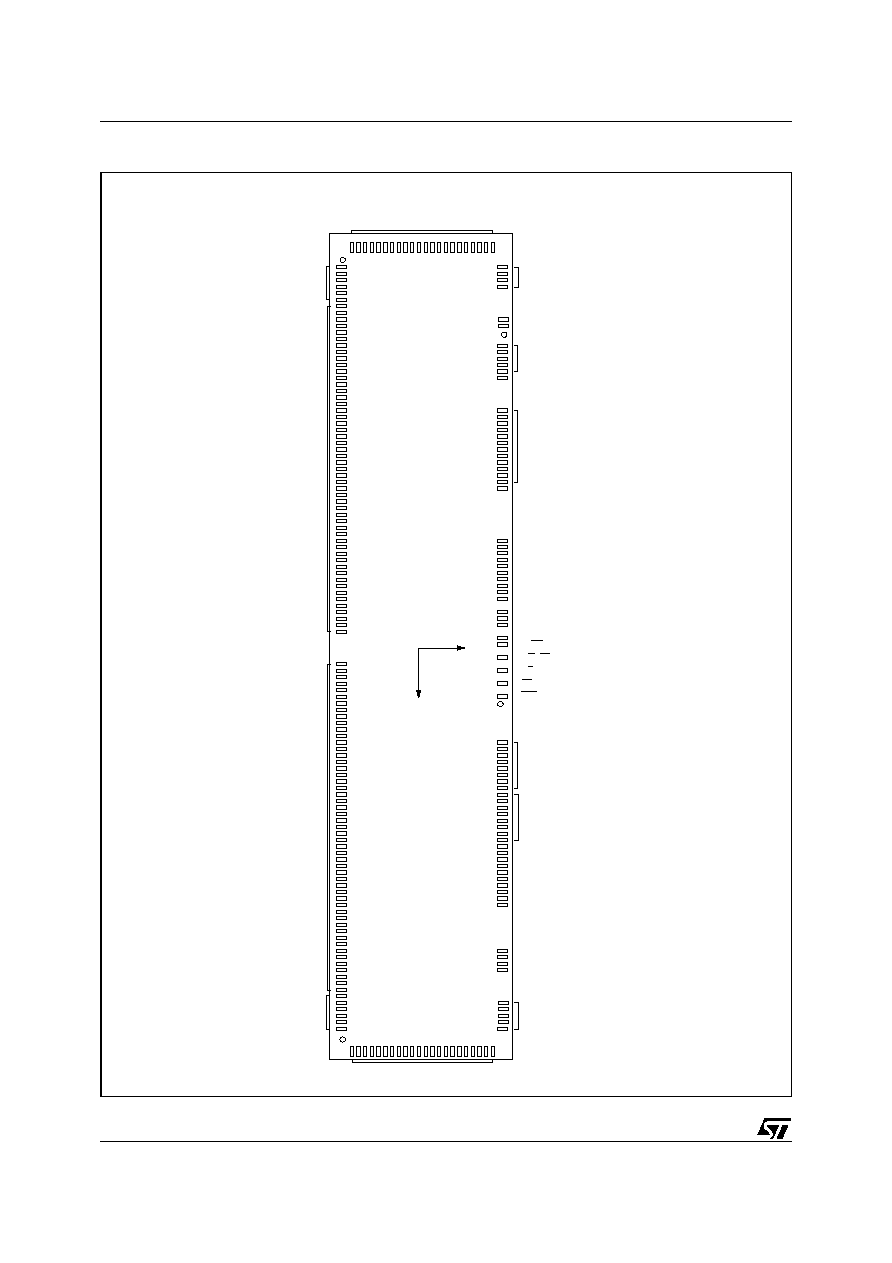

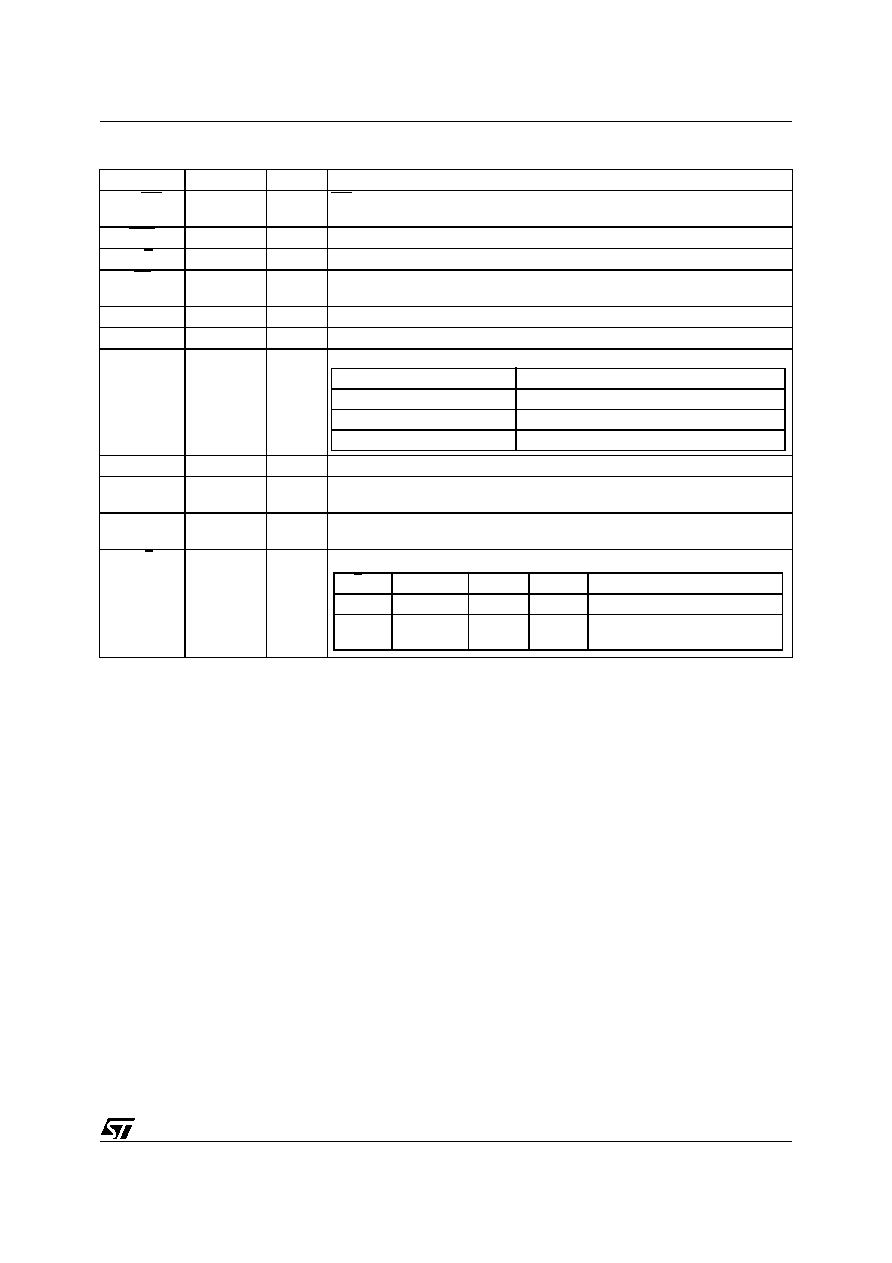

3/66

STE2004

E / WR

176

I

WR - 8080 Series Parallel Interface - Write enable clock input

- CANNOT BE LEFT FLOATING

RES

172

I

Reset Input. Active Low.

D/C

174

I

Interface Data/Command Selector- CANNOT BE LEFT FLOATING

CS

173

I

Serial & Parallel Interfaces ENABLE. When Low the Incoming Data are Clocked In.

CANNOT BE LEFT FLOATING

TEST_MODE

191

I

Test Pad - 50 kohm internal Pull-down MUST BE CONNECTED TO VSS/VSSAUX

TEST_VREF

146

O

Test Pad - MUST BE LEFT FLOATING

OSCIN

144

I

Oscillator Input:

OSCOUT

210

O

Internal/External Oscillator Out - IF UNUSED MUST BE LEFT FLOATING

FR_OUT

211

O

Master Slave Frame Inversion Synchronization.

IF UNUSED MUST BE LEFT FLOATING

FR_IN

143

I

Master Slave Frame Inversion Synchronization.

CANNOT BE LEFT FLOATING

M/S

100

I

Master/Slave Configuration Bit:- CANNOT BE LEFT FLOATING

Table 2. Pin Description (continued)

N°

Pad

Type

Function

OSC_IN

Configuration

High

Internal Oscillator Enabled

Low

Internal Oscillator Disabled

External Scillator

Internal Oscillator Disabled

M/S PIN

OSC_OUT

FR_OUT

FR_IN

Charge Pump

High

ENABLED

Enabled

Disabled

AuxVsense Disabled

Low

ENABLED

Enabled

Enabled

Charge Pump in Slave Mode or Ext

Power