1

Data sheet acquired from Harris Semiconductor

SCHS136C

Features

∑ Buffered Inputs and Outputs

∑ Typical Propagation Delay: 13ns (Data to Output at

V

CC

= 5V, C

L

= 15pF, T

A

= 25

o

C

∑ Serial or Parallel Expansion Without External Gating

∑ Fanout (Over Temperature Range)

- Standard Outputs . . . . . . . . . . . . . . . 10 LSTTL Loads

- Bus Driver Outputs . . . . . . . . . . . . . 15 LSTTL Loads

∑ Wide Operating Temperature Range . . . -55

o

C to 125

o

C

∑ Balanced Propagation Delay and Transition Times

∑ Significant Power Reduction Compared to LSTTL

Logic ICs

∑ HC Types

- 2V to 6V Operation

- High Noise Immunity: N

IL

= 30%, N

IH

= 30%of V

CC

at

V

CC

= 5V

∑ HCT Types

- 4.5V to 5.5V Operation

- Direct LSTTL Input Logic Compatibility,

V

IL

= 0.8V (Max), V

IH

= 2V (Min)

- CMOS Input Compatibility, I

l

1

µ

A at V

OL

, V

OH

Description

The 'HC85 and 'HCT85 are high speed magnitude

comparators that use silicon-gate CMOS technology to

achieve operating speeds similar to LSTTL with the low

power consumption of standard CMOS integrated circuits.

These 4-bit devices compare two binary, BCD, or other

monotonic codes and present the three possible magnitude

results at the outputs (A > B, A < B, and A = B). The 4-bit

input words are weighted (A0 to A3 and B0 to B3), where A3

and B

3

are the most significant bits.

The devices are expandable without external gating, in both

serial and parallel fashion. The upper part of the truth table

indicates operation using a single device or devices in a

serially

expanded

application.

The

parallel

expansion

scheme is described by the last three entries in the truth

table.

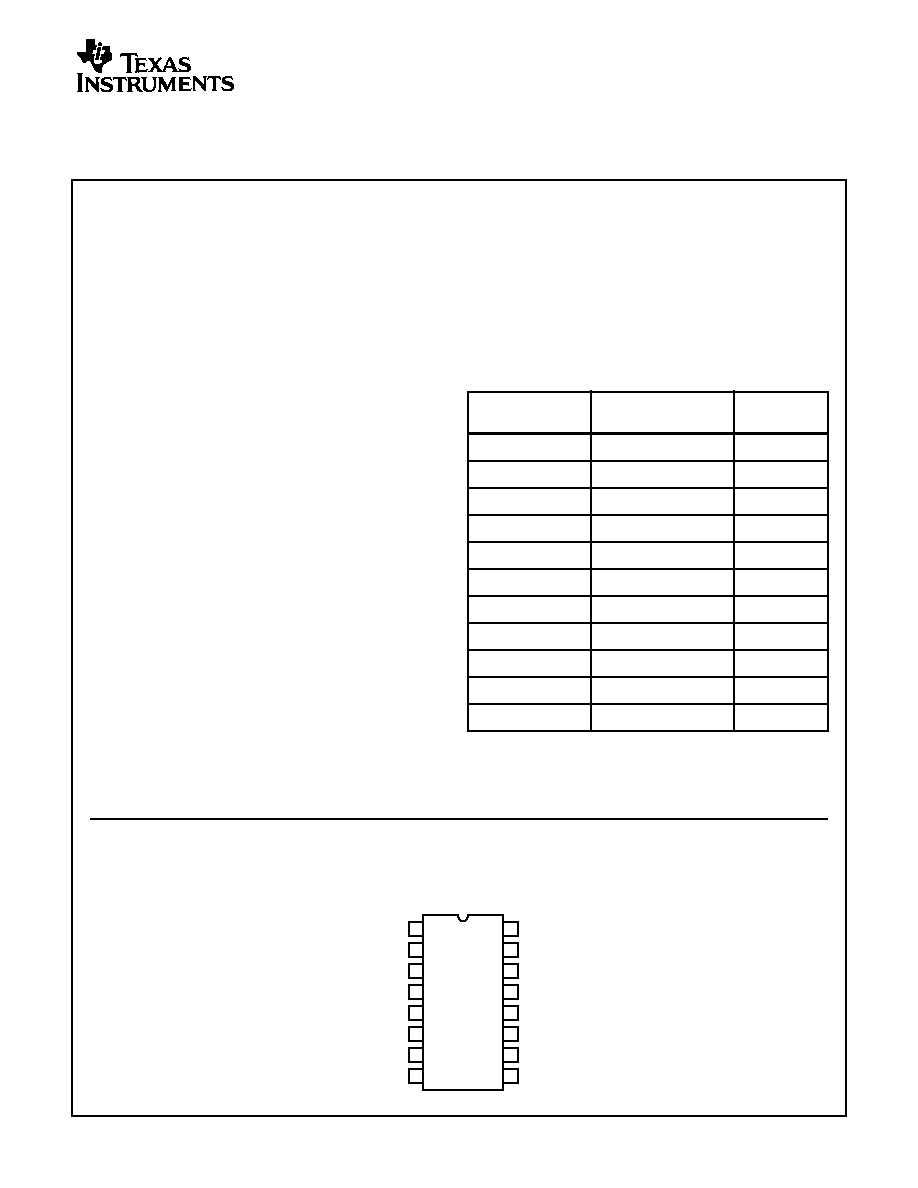

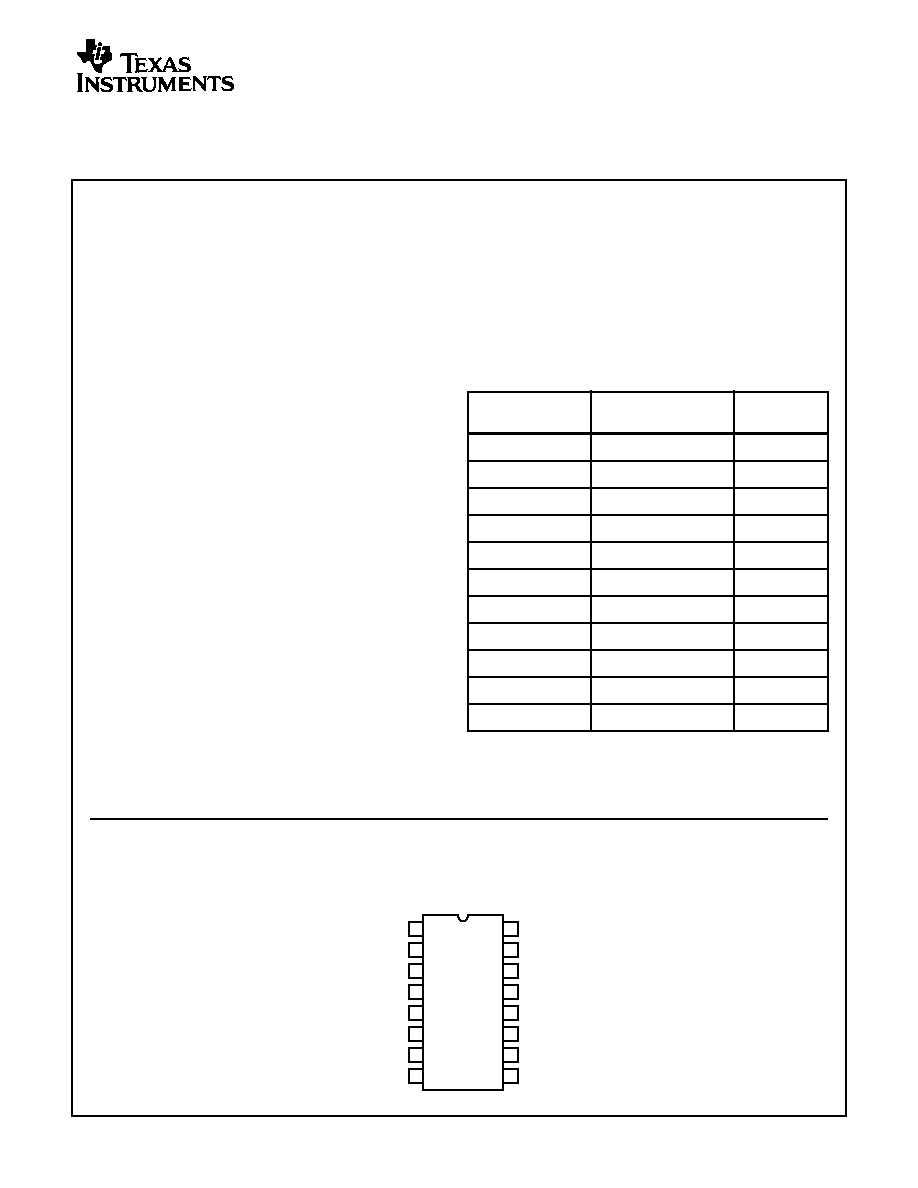

Pinout

CD54HC85, CD54HCT85 (CERDIP)

CD74HC85 (PDIP, SOIC, SOP, TSSOP)

CD74HCT85 (PDIP, SOIC)

TOP VIEW

Ordering Information

PART NUMBER

TEMP. RANGE

(

o

C)

PACKAGE

CD54HC85F3A

-55 to 125

16 Ld CERDIP

CD54HCT85F3A

-55 to 125

16 Ld CERDIP

CD74HC85E

-55 to 125

16 Ld PDIP

CD74HC85M

-55 to 125

16 Ld SOIC

CD74HC85M96

-55 to 125

16 Ld SOIC

CD74HC85NSR

-55 to 125

16 Ld SOP

CD74HC85PW

-55 to 125

16 Ld TSSOP

CD74HC85PWR

-55 to 125

16 Ld TSSOP

CD74HCT85E

-55 to 125

16 Ld PDIP

CD74HCT85M

-55 to 125

16 Ld SOIC

CD74HCT85M96

-55 to 125

16 Ld SOIC

NOTE:

1. When ordering, use the entire part number. The suffixes 96 and

R denote tape and reel.

14

15

16

9

13

12

11

10

1

2

3

4

5

7

6

8

B3

(A < B) IN

(A = B) IN

(A > B) IN

(A > B) OUT

(A = B) OUT

GND

(A < B) OUT

V

CC

B2

A2

A1

B1

A0

B0

A3

August 1997 - Revised February 2003

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

Copyright

©

2003, Texas Instruments Incorporated

CD54/74HC85,

CD54/74HCT85

High Speed CMOS Logic

4-Bit Magnitude Comparator

[ /Title

(CD74

HC85,

CD74

HCT85

)

/Sub-

ject

(High

Speed

CMOS

Logic

4-Bit

Magni-

tude

Com-

para-

2

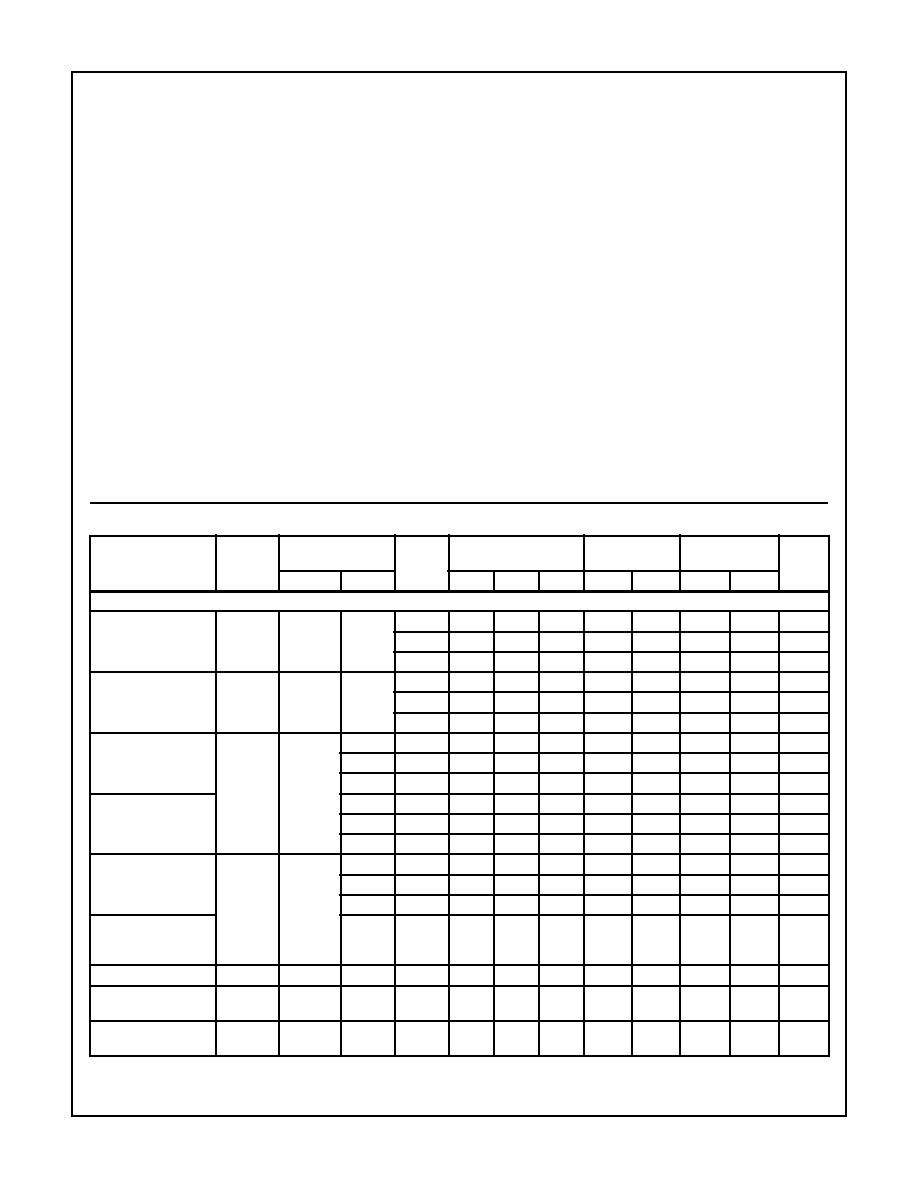

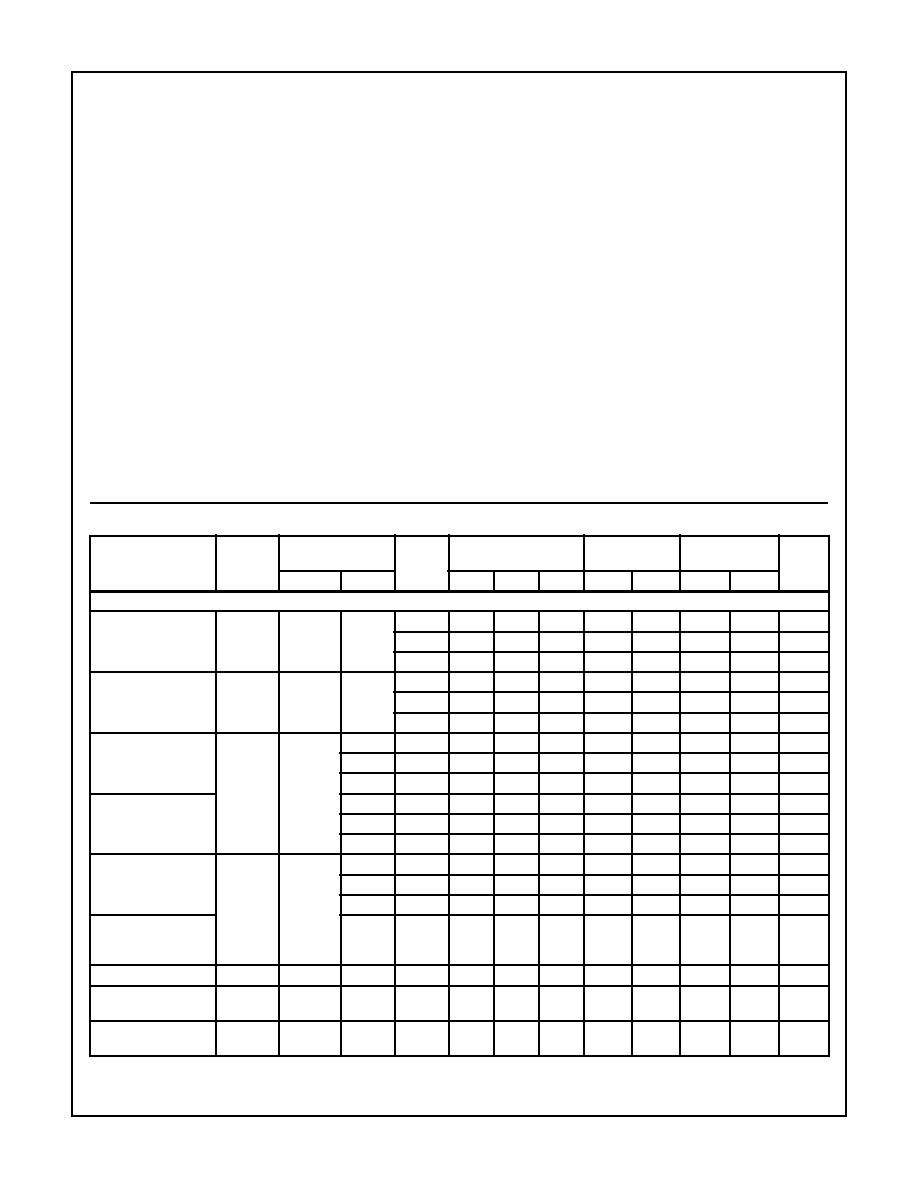

Functional Diagram

TRUTH TABLE

COMPARING INPUTS

CASCADING INPUTS

OUTPUTS

A3, B3

A2, B2

A1, B1

A0, B0

A > B

A < B

A = B

A > B

A < B

A = B

SINGLE DEVICE OR SERIES CASCADING

A3 > B3

X

X

X

X

X

X

H

L

L

A3 < B3

X

X

X

X

X

X

L

H

L

A3 = B3

A2 >B2

X

X

X

X

X

H

L

L

A3 = B3

A2 < B2

X

X

X

X

X

L

H

L

A3 = B3

A2 = B2

A1 > B1

X

X

X

X

H

L

L

A3 = B3

A2 = B2

A1 < B1

X

X

X

X

L

H

L

A3 = B3

A2 = B2

A1 = B1

A0 > B0

X

X

X

H

L

L

A3 = B3

A2 = B2

A1 = B1

A0 < B0

X

X

X

L

H

L

A3 = B3

A2 = B2

A1 = B1

A0 = B0

H

L

L

H

L

L

A3 = B3

A2 = B2

A1 = B1

A0 = B0

L

H

L

L

H

L

A3 = B3

A2 = B2

A1 = B1

A0 = B0

L

L

H

L

L

H

PARALLEL CASCADING

A3 = B3

A2 = B2

A1 = B1

A0 = B0

X

X

H

L

L

H

A3 = B3

A2 = B2

A1 = B1

A0 = B0

H

H

L

L

L

L

A3 = B3

A2 = B2S

A1 = B1

A0 = B0

L

L

L

H

H

L

NOTE: H = High Voltage Level, L = Low Voltage, Level, X = Don't Care

6

5

(A > B) OUT

15

13

12

10

3

1

4

2

A3

B3

(A > B) IN

(A = B) IN

(A < B) IN

A0

A1

A2

14

B2

11

B1

9

B0

7

(A = B) OUT

(A < B) OUT

CD54/74HC85, CD54/74HCT85

3

Absolute Maximum Ratings

Thermal Information

DC Supply Voltage, V

CC

. . . . . . . . . . . . . . . . . . . . . . . . -0.5V to 7V

DC Input Diode Current, I

IK

For V

I

< -0.5V or V

I

> V

CC

+ 0.5V

. . . . . . . . . . . . . . . . . . . . . .±

20mA

DC Output Diode Current, I

OK

For V

O

< -0.5V or V

O

> V

CC

+ 0.5V

. . . . . . . . . . . . . . . . . . . .±

20mA

DC Output Source or Sink Current per Output Pin, I

O

For V

O

> -0.5V or V

O

< V

CC

+ 0.5V

. . . . . . . . . . . . . . . . . . . .±

25mA

DC V

CC

or Ground Current, I

CC or

I

GND

. . . . . . . . . . . . . . . . . .±

50mA

Operating Conditions

Temperature Range (T

A

) . . . . . . . . . . . . . . . . . . . . . -55

o

C to 125

o

C

Supply Voltage Range, V

CC

HC Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2V to 6V

HCT Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4.5V to 5.5V

DC Input or Output Voltage, V

I

, V

O

. . . . . . . . . . . . . . . . . 0V to V

CC

Input Rise and Fall Time

2V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1000ns (Max)

4.5V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500ns (Max)

6V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 400ns (Max)

Package Thermal Impedance,

JA

(see Note 2):

E Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

o

C/W

M Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

o

C/W

NS Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

o

C/W

PW Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

o

C/W

Maximum Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . 150

o

C

Maximum Storage Temperature Range . . . . . . . . . .-65

o

C to 150

o

C

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . . 300

o

C

(SOIC - Lead Tips Only)

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

2. The package thermal impedance is calculated in accordance with JESD 51-7.

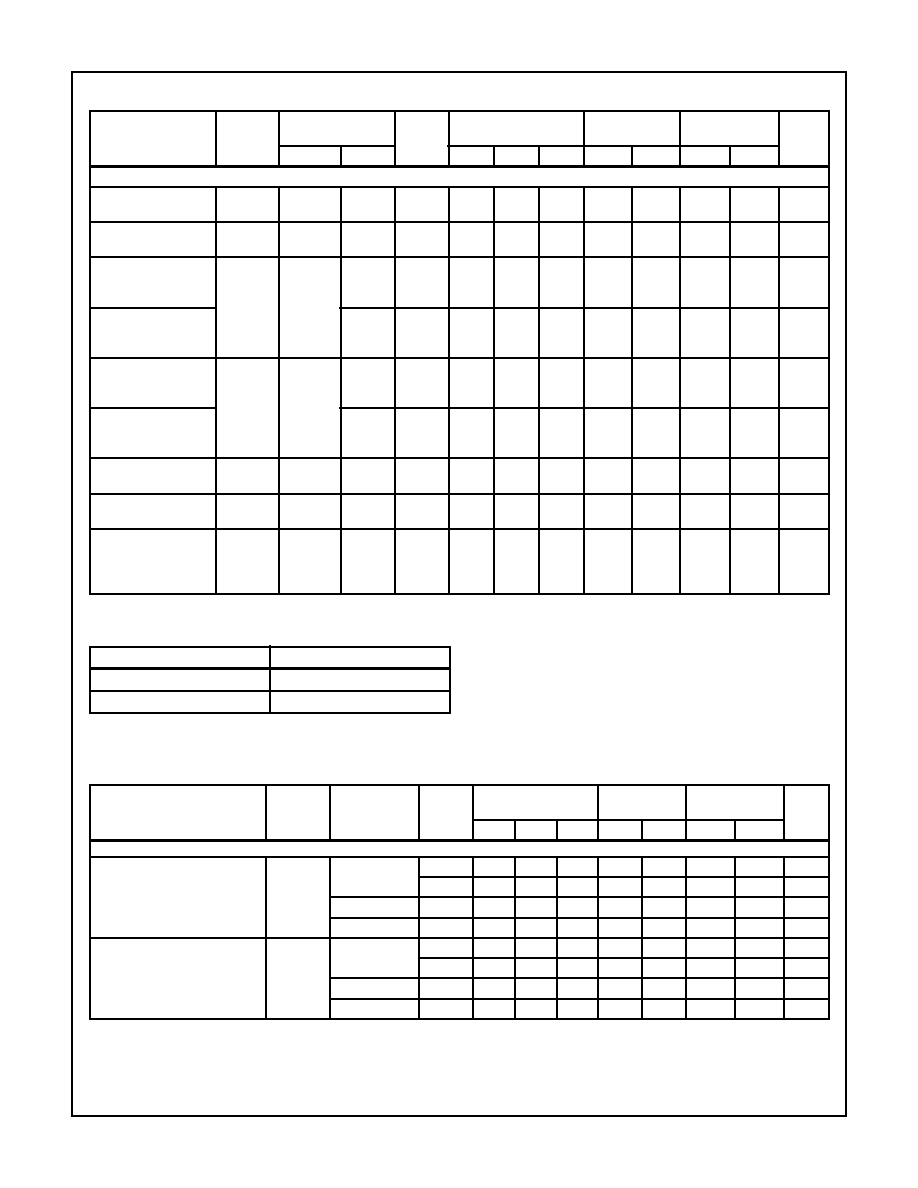

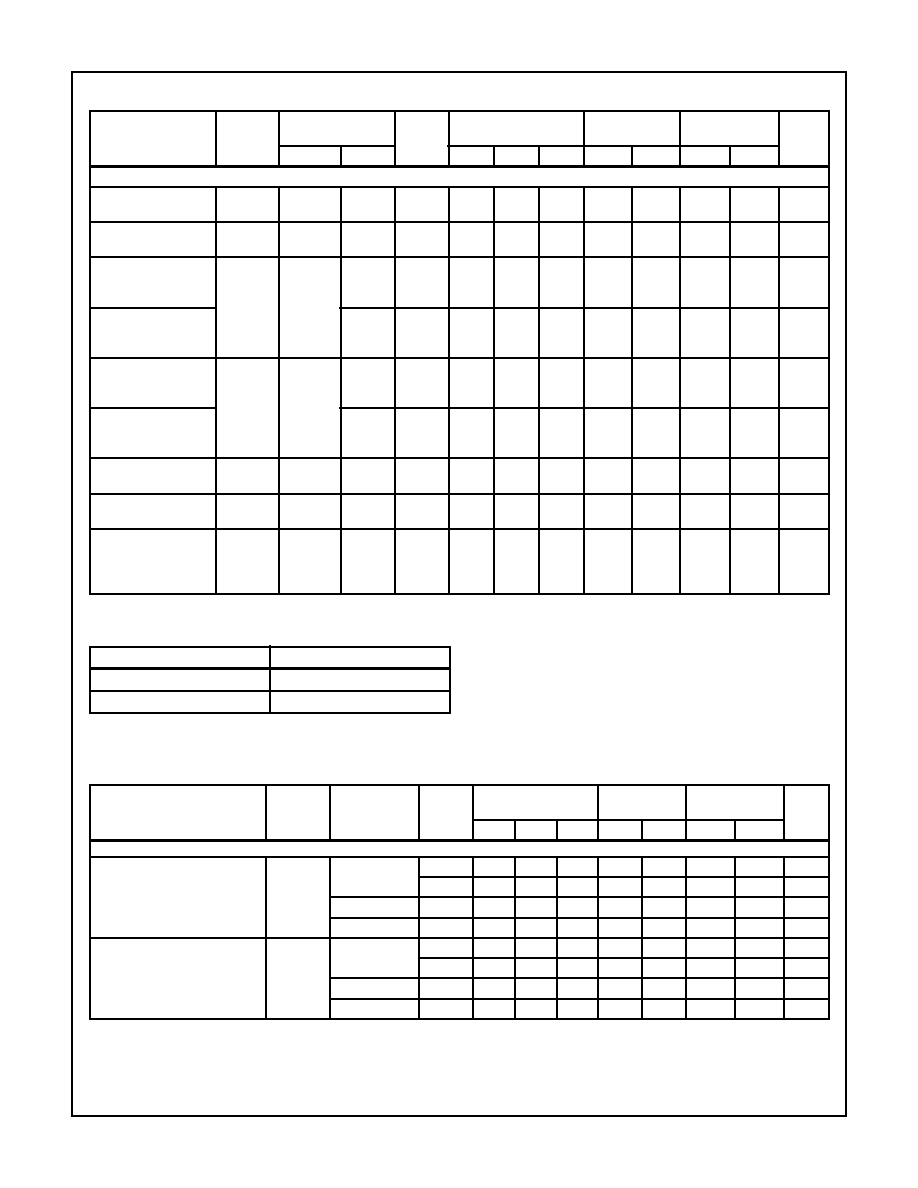

DC Electrical Specifications

PARAMETER

SYMBOL

TEST

CONDITIONS

V

CC

(V)

25

o

C

-40

o

C TO 85

o

C -55

o

C TO 125

o

C

UNITS

V

I

(V)

I

O

(mA)

MIN

TYP

MAX

MIN

MAX

MIN

MAX

HC TYPES

High Level Input

Voltage

V

IH

-

-

2

1.5

-

-

1.5

-

1.5

-

V

4.5

3.15

-

-

3.15

-

3.15

-

V

6

4.2

-

-

4.2

-

4.2

-

V

Low Level Input

Voltage

V

IL

-

-

2

-

-

0.5

-

0.5

-

0.5

V

4.5

-

-

1.35

-

1.35

-

1.35

V

6

-

-

1.8

-

1.8

-

1.8

V

High Level Output

Voltage

CMOS Loads

V

OH

V

IH

or V

IL

-0.02

2

1.9

-

-

1.9

-

1.9

-

V

-0.02

4.5

4.4

-

-

4.4

-

4.4

-

V

-0.02

6

5.9

-

-

5.9

-

5.9

-

V

High Level Output

Voltage

TTL Loads

-

-

-

-

-

-

-

-

-

V

-4

4.5

3.98

-

-

3.84

-

3.7

-

V

-5.2

6

5.48

-

-

5.34

-

5.2

-

V

Low Level Output

Voltage

CMOS Loads

V

OL

V

IH

or V

IL

0.02

2

-

-

0.1

-

0.1

-

0.1

V

0.02

4.5

-

-

0.1

-

0.1

-

0.1

V

0.02

6

-

-

0.1

-

0.1

-

0.1

V

Low Level Output

Voltage

TTL Loads

4

4.5

-

-

0.26

-

0.33

-

0.4

V

5.2

6

-

-

0.26

-

0.33

-

0.4

V

Input Leakage

Current

I

I

V

CC

or

GND

-

6

-

-

±

0.1

-

±

1

-

±

1

µ

A

Quiescent Device

Current

I

CC

V

CC

or

GND

0

6

-

-

8

-

80

-

160

µ

A

CD54/74HC85, CD54/74HCT85

4

HCT TYPES

High Level Input

Voltage

V

IH

-

-

4.5 to

5.5

2

-

-

2

-

2

-

V

Low Level Input

Voltage

V

IL

-

-

4.5 to

5.5

-

-

0.8

-

0.8

-

0.8

V

High Level Output

Voltage

CMOS Loads

V

OH

V

IH

or V

IL

-0.02

4.5

4.4

-

-

4.4

-

4.4

-

V

High Level Output

Voltage

TTL Loads

-4

4.5

3.98

-

-

3.84

-

3.7

-

V

Low Level Output

Voltage

CMOS Loads

V

OL

V

IH

or V

IL

0.02

4.5

-

-

0.1

-

0.1

-

0.1

V

Low Level Output

Voltage

TTL Loads

4

4.5

-

-

0.26

-

0.33

-

0.4

V

Input Leakage

Current

I

I

V

CC

and

GND

0

5.5

-

±

0.1

-

±

1

-

±

1

µ

A

Quiescent Device

Current

I

CC

V

CC

or

GND

0

5.5

-

-

8

-

80

-

160

µ

A

Additional Quiescent

Device Current Per

Input Pin: 1 Unit Load

(Note)

I

CC

V

CC

-2.1

-

4.5 to

5.5

-

100

360

-

450

-

490

µ

A

NOTE: For dual-supply systems theoretical worst case (V

I

= 2.4V, V

CC

= 5.5V) specification is 1.8mA.

DC Electrical Specifications

(Continued)

PARAMETER

SYMBOL

TEST

CONDITIONS

V

CC

(V)

25

o

C

-40

o

C TO 85

o

C -55

o

C TO 125

o

C

UNITS

V

I

(V)

I

O

(mA)

MIN

TYP

MAX

MIN

MAX

MIN

MAX

HCT Input Loading Table

INPUT

UNIT LOADS

A0-A3, B0-B3 and (A = B) IN

1.5

(A > B) IN, (A < B) IN

1

NOTE: Unit Load is

I

CC

limit specified in DC Electrical Table, e.g.

360

µ

A max at 25

o

C.

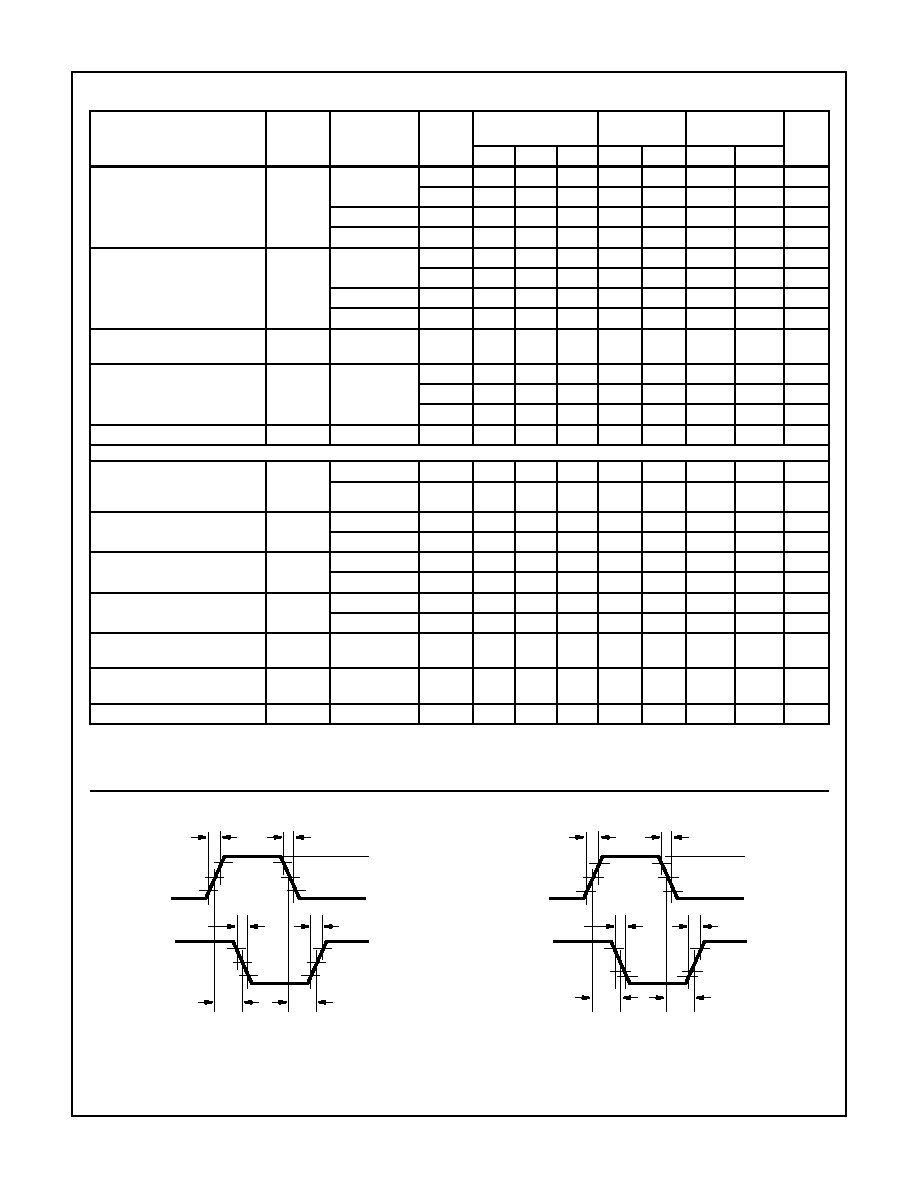

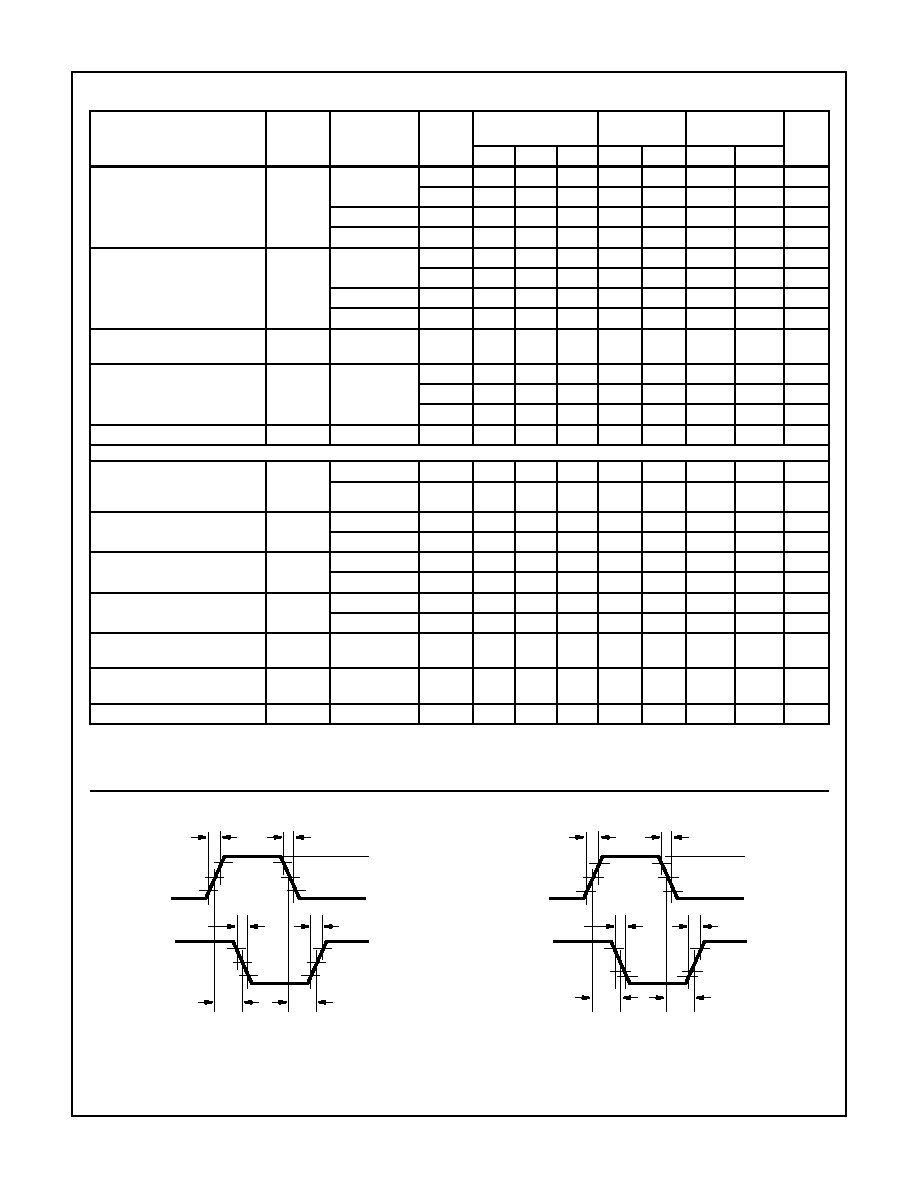

Switching Specifications

Input t

r

, t

f

= 6ns

PARAMETER

SYMBOL

TEST

CONDITIONS

V

CC

(V)

25

o

C

-40

o

C TO

85

o

C

-55

o

C TO

125

o

C

UNITS

MIN

TYP

MAX

MIN

MAX

MIN

MAX

HC TYPES

Propagation Delay,

A

n

, B

n

to (A > B) OUT,

(A < B) OUT

t

PLH,

t

PHL

C

L

= 50pF

2

-

-

195

-

245

-

295

ns

4.5

-

-

39

-

47

-

59

ns

C

L

= 15pF

5

-

16

-

-

-

-

-

ns

C

L

= 50pF

6

-

-

33

-

42

-

50

ns

A

n

, B

n

to (A = B) OUT

t

PLH,

t

PHL

C

L

= 50pF

2

-

-

175

-

240

-

265

ns

4.5

-

-

35

-

44

-

53

ns

C

L

= 15pF

5

-

14

-

-

-

-

-

ns

C

L

= 50pF

6

-

-

30

-

37

-

45

ns

CD54/74HC85, CD54/74HCT85

5

(A > B) IN, (A < B) IN, (A = B) IN

to (A > B) OUT, (A < B) OUT

t

PLH,

t

PHL

C

L

= 50pF

2

-

-

140

-

175

-

210

ns

4.5

-

-

28

-

35

-

42

ns

C

L

= 15pF

5

-

11

-

-

-

-

-

ns

C

L

= 50pF

6

-

-

24

-

30

-

36

ns

(A > B) IN to (A = B) OUT

t

PLH,

t

PHL

C

L

= 50pF

2

-

-

120

-

150

-

180

ns

4.5

-

-

24

-

30

-

36

ns

C

L

= 15pF

5

-

9

-

-

-

-

-

ns

C

L

= 50pF

6

-

-

20

-

26

-

31

ns

Power Dissipation Capacitance

(Notes 3, 4)

C

PD

-

5

-

24

-

-

-

-

-

pF

Output Transition Times

(Figure 1)

t

TLH

, t

THL

C

L

= 50pF

2

-

-

75

-

95

-

110

ns

4.5

-

-

15

-

19

-

22

ns

6

-

-

13

-

16

-

19

ns

Input Capacitance

C

IN

-

-

-

-

10

-

10

-

10

pF

HCT TYPES

Propagation Delay,

An, Bn to (A > B) OUT,

(A < B) OUT

t

PLH,

t

PHL

C

L

= 50pF

4.5

-

-

37

-

46

-

56

ns

C

L

= 15pF

5

-

15

-

-

-

-

-

ns

An, Bn to (A = B) OUT

t

PLH,

t

PHL

C

L

= 50pF

4.5

-

-

40

-

50

-

60

ns

C

L

= 15pF

5

-

17

-

-

-

-

-

ns

(A > B) IN, (A < B) IN, (A = B) IN

to (A > B) OUT, (A < B) OUT

t

PLH,

t

PHL

C

L

= 50pF

4.5

-

-

30

-

38

-

45

ns

C

L

= 15pF

5

-

12

-

-

-

-

-

ns

(A > B) IN to (A = B) OUT

t

PLH,

t

PHL

C

L

= 50pF

4.5

-

-

31

-

39

-

47

ns

C

L

= 15pF

5

-

13

-

-

-

-

-

ns

Output Transition Times

(Figure 1)

t

TLH

, t

THL

C

L

= 50pF

4.5

-

-

15

-

19

-

22

ns

Power Dissipation Capacitance

(Notes 3, 4)

C

PD

-

5

-

26

-

-

-

-

-

pF

Input Capacitance

C

IN

-

-

-

-

10

-

10

-

10

pF

NOTES:

3. C

PD

is used to determine the dynamic power consumption, per gate/package.

4. P

D

= V

CC

2

f

i

(C

PD

+ C

L

) where f

i

= Input Frequency, C

L

= Output Load Capacitance, V

CC

= Supply Voltage.

Switching Specifications

Input t

r

, t

f

= 6ns (Continued)

PARAMETER

SYMBOL

TEST

CONDITIONS

V

CC

(V)

25

o

C

-40

o

C TO

85

o

C

-55

o

C TO

125

o

C

UNITS

MIN

TYP

MAX

MIN

MAX

MIN

MAX

Test Circuits and Waveforms

FIGURE 1. HC AND HCU TRANSITION TIMES AND PROPAGA-

TION DELAY TIMES, COMBINATION LOGIC

FIGURE 2. HCT TRANSITION TIMES AND PROPAGATION

DELAY TIMES, COMBINATION LOGIC

t

PHL

t

PLH

t

THL

t

TLH

90%

50%

10%

50%

10%

INVERTING

OUTPUT

INPUT

GND

V

CC

t

r

= 6ns

t

f

= 6ns

90%

t

PHL

t

PLH

t

THL

t

TLH

2.7V

1.3V

0.3V

1.3V

10%

INVERTING

OUTPUT

INPUT

GND

3V

t

r

= 6ns

t

f

= 6ns

90%

CD54/74HC85, CD54/74HCT85