Document Outline

- IMPORTANT NOTICE

- REVISION HISTORY

- Contents

- List of Figures

- List of Tables

- TMS320VC5410A Features

- Introduction

- Description

- Pin Assignments

- Terminal Assignments for the GGU Package

- Pin Assignments for the PGE Package

- Signal Descriptions

- Functional Overview

- Memory

- Data Memory

- Program Memory

- Extended Program Memory

- On-Chip ROM With Bootloader

- On-Chip RAM

- On-Chip Memory Security

- Memory Map

- Relocatable Interrupt Vector Table

- On-Chip Peripherals

- Software-Programmable Wait-State Generator

- Programmable Bank-Switching

- Bus Holders

- Parallel I/O Ports

- Enhanced 8-/16-Bit Host-Port Interface (HPI8/16)

- HPI Nonmultiplexed Mode

- Multichannel Buffered Serial Ports (McBSPs)

- Hardware Timer

- Clock Generator

- Enhanced External Parallel Interface (XIO2)

- DMA Controller

- Features

- DMA External Access

- DMPREC Issue

- DMA Memory Map

- DMA Priority Level

- DMA Source/Destination Address Modification

- DMA in Autoinitialization Mode

- DMA Transfer Counting

- DMA Transfer in Doubleword Mode

- DMA Channel Index Registers

- DMA Interrupts

- DMA Controller Synchronization Events

- General-Purpose I/O Pins

- McBSP Pins as General-Purpose I/O

- HPI Data Pins as General-Purpose I/O

- Device ID Register

- Memory-Mapped Registers

- McBSP Control Registers and Subaddresses

- DMA Subbank Addressed Registers

- Interrupts

- Documentation Support

- Electrical Specifications

- Absolute Maximum Ratings

- Recommended Operating Conditions

- Electrical Characteristics Over Recommended Operating Case Temperature R\

ange (Unless Otherwise Noted)

- Test Load Circuit

- Package Thermal Resistance Characteristics

- Timing Parameter Symbology

- Internal Oscillator With External Crystal

- Clock Options

- Divide-By-Two and Divide-By-Four Clock Options

- Multiply-By-N Clock Option (PLL Enabled)

- Memory and Parallel I/O Interface Timing

- Memory Read

- Memory Write

- I/O Read

- I/O Write

- Ready Timing for Externally Generated Wait States

- HOLD\ and HOLDA\ Timings

- Reset, BIO\, Interrupt, and MP/MC\ Timings

- Instruction Acquisition (IAQ)\ and Interrupt Acknowledge (IACK)\ T\

imings

- External Flag (XF) and TOUT Timings

- Multichannel Buffered Serial Port (McBSP) Timing

- McBSP Transmit and Receive Timings

- McBSP General-Purpose I/O Timing

- McBSP as SPI Master or Slave Timing

- Host-Port Interface Timing

- Mechanical Data

- Ball Grid Array Mechanical Data

- Low-Profile Quad Flatpack Mechanical Data

TMS320VC5410A Fixed-Point

Digital Signal Processor

Data Manual

Literature Number: SPRS139D

November 2000 � Revised July 2002

Printed on Recycled Paper

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications,

enhancements, improvements, and other changes to its products and services at any time and to discontinue

any product or service without notice. Customers should obtain the latest relevant information before placing

orders and should verify that such information is current and complete. All products are sold subject to TI's terms

and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in

accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI

deems necessary to support this warranty. Except where mandated by government requirements, testing of all

parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for

their products and applications using TI components. To minimize the risks associated with customer products

and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right,

copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process

in which TI products or services are used. Information published by TI regarding third�party products or services

does not constitute a license from TI to use such products or services or a warranty or endorsement thereof.

Use of such information may require a license from a third party under the patents or other intellectual property

of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without

alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction

of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for

such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that

product or service voids all express and any implied warranties for the associated TI product or service and

is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments

Post Office Box 655303

Dallas, Texas 75265

Copyright

2002, Texas Instruments Incorporated

iii

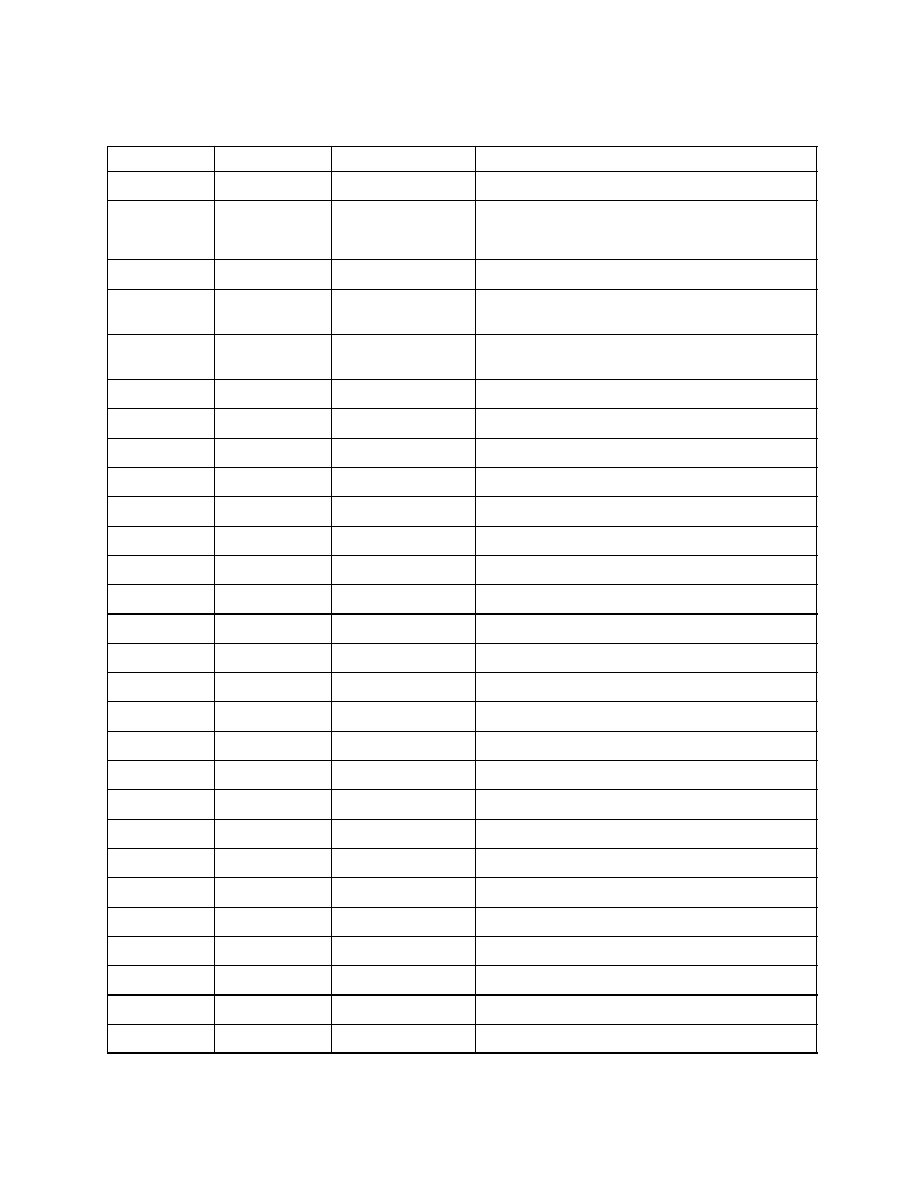

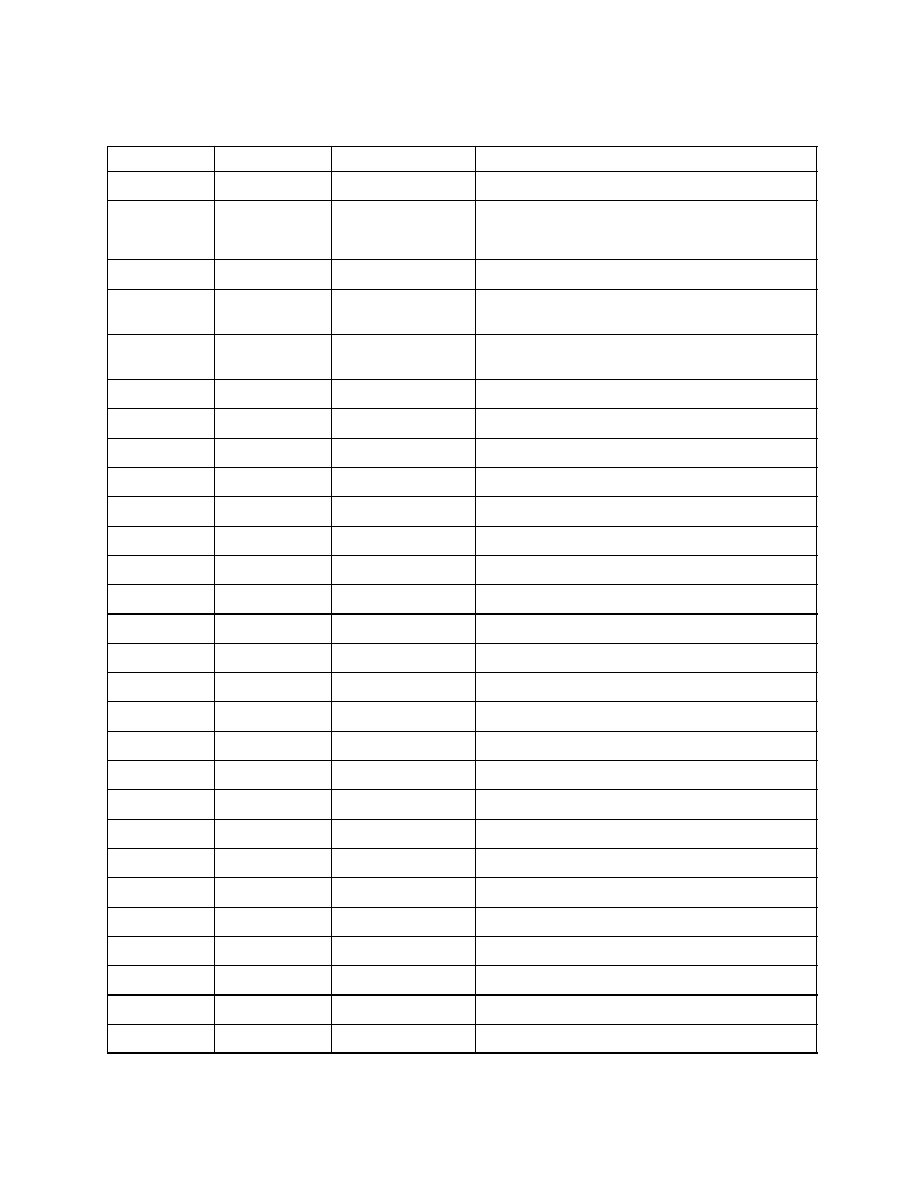

REVISION HISTORY

REVISION

DATE

PRODUCT STATUS

HIGHLIGHTS

*

November 2000

Product Preview

Original

A

February 2001

Product Preview

Updated electrical characteristic data and removed

references to internal oscillator functionality that is not

currently supported.

B

June 2001

Product Preview

Updated electrical characteristic data.

C

October 2001

Production Data

Corrected to reflect production data status. Added description

of internal oscillator functionality.

D

July 2002

Production Data

Added references to the silicon errata for additional

information concerning internal oscillator functionality.

Contents

v

November 2000 � Revised July 2002

SPRS139D

Contents

Section

Page

1

TMS320VC5410A Features

1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2

Introduction

2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1

Description

2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2

Pin Assignments

2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.1

Terminal Assignments for the GGU Package

2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.2

Pin Assignments for the PGE Package

4

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3

Signal Descriptions

5

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3

Functional Overview

10

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1

Memory

10

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.1

Data Memory

10

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.2

Program Memory

11

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.3

Extended Program Memory

11

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2

On-Chip ROM With Bootloader

11

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3

On-Chip RAM

12

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4

On-Chip Memory Security

12

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5

Memory Map

13

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.1

Relocatable Interrupt Vector Table

14

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6

On-Chip Peripherals

15

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.1

Software-Programmable Wait-State Generator

16

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.2

Programmable Bank-Switching

17

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.3

Bus Holders

19

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7

Parallel I/O Ports

19

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7.1

Enhanced 8-/16-Bit Host-Port Interface (HPI8/16)

19

. . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7.2

HPI Nonmultiplexed Mode

20

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8

Multichannel Buffered Serial Ports (McBSPs)

22

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.9

Hardware Timer

25

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.10

Clock Generator

25

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.11

Enhanced External Parallel Interface (XIO2)

26

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.12

DMA Controller

29

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.12.1

Features

30

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.12.2

DMA External Access

30

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.12.3

DMPREC Issue

31

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.12.4

DMA Memory Map

32

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.12.5

DMA Priority Level

33

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.12.6

DMA Source/Destination Address Modification

33

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.12.7

DMA in Autoinitialization Mode

33

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.12.8

DMA Transfer Counting

34

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.12.9

DMA Transfer in Doubleword Mode

34

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.12.10

DMA Channel Index Registers

34

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.12.11

DMA Interrupts

35

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.12.12

DMA Controller Synchronization Events

35

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.13

General-Purpose I/O Pins

36

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.13.1

McBSP Pins as General-Purpose I/O

36

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.13.2

HPI Data Pins as General-Purpose I/O

36

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contents

vi

November 2000 � Revised July 2002

SPRS139D

Section

Page

3.14

Device ID Register

36

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.15

Memory-Mapped Registers

37

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.16

McBSP Control Registers and Subaddresses

39

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.17

DMA Subbank Addressed Registers

40

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.18

Interrupts

42

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4

Documentation Support

43

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5

Electrical Specifications

44

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1

Absolute Maximum Ratings

44

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2

Recommended Operating Conditions

44

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3

Electrical Characteristics Over Recommended Operating Case Temperature

Range (Unless Otherwise Noted)

45

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4

Test Load Circuit

45

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.5

Package Thermal Resistance Characteristics

46

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6

Timing Parameter Symbology

46

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.7

Internal Oscillator With External Crystal

46

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.8

Clock Options

47

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.8.1

Divide-By-Two and Divide-By-Four Clock Options

47

. . . . . . . . . . . . . . . . . . . . . . . . . . .

5.8.2

Multiply-By-N Clock Option (PLL Enabled)

49

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.9

Memory and Parallel I/O Interface Timing

50

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.9.1

Memory Read

50

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.9.2

Memory Write

53

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.9.3

I/O Read

55

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.9.4

I/O Write

57

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.10

Ready Timing for Externally Generated Wait States

58

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.11

HOLD and HOLDA Timings

61

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.12

Reset, BIO, Interrupt, and MP/MC Timings

63

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.13

Instruction Acquisition (IAQ) and Interrupt Acknowledge (IACK) Timings

65

. . . . . . . . . . . . . . . . .

5.14

External Flag (XF) and TOUT Timings

66

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.15

Multichannel Buffered Serial Port (McBSP) Timing

67

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.15.1

McBSP Transmit and Receive Timings

67

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.15.2

McBSP General-Purpose I/O Timing

70

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.15.3

McBSP as SPI Master or Slave Timing

71

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.16

Host-Port Interface Timing

75

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.16.1

HPI8 Mode

75

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.16.2

HPI16 Mode

79

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6

Mechanical Data

83

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.1

Ball Grid Array Mechanical Data

83

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2

Low-Profile Quad Flatpack Mechanical Data

84

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .