TNETX3270

ThunderSWITCH

TM

24/3 ETHERNET

TM

SWITCH

WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS

SPWS043B ≠ NOVEMBER 1997 ≠ REVISED APRIL 1999

1

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

D

Port Configurations:

Twenty-Four 10-Mbit/s Ports

≠ Ports Arranged in Three Groups of Eight

Ports in a Multiplexed Interface

≠ Direct Multiplexer Interface to

TNETE2008

≠ Full and Half Duplex

≠ Half-Duplex Collision-Based Flow

Control

≠ Full-Duplex IEEE Std 802.3x Flow Control

≠ Interoperable Support for IEEE

Std 802.1Q VLAN

≠ Speed, Duplex, and Pause

Autonegotiation With Physical Layer

(PHY)

Three 10-/100-Mbit/s Ports

≠ Direct Interface to TNETE2101

≠ Full and Half Duplex

≠ Half-Duplex Collision-Based Flow

Control

≠ Full-Duplex IEEE Std 802.3x Flow Control

≠ Interoperable Support for IEEE

Std 802.1Q VLAN

≠ Pretagging Support

D

Port Trunking and Load Sharing

D

LED Indication of Port Status

D

SDRAM Interface

≠ Direct Interface to 8-Bit/Word and

16-Bit/Word, 16-Mbit, and 64-Mbit

SDRAMs

≠ 32-Bit-Wide Data Bus

≠ Up to 32 Mbytes Supported

≠ 83.33-MHz SDRAM Clock

≠ 12-ns (≠12) SDRAMs Required

D

Remote Monitoring (RMON) Support ≠

Groups 1, 2, 3, and 9

D

Direct I/O (DIO) Management Interface

≠ Eight Bits Wide

≠ CPU Access to Statistics, Registers, and

Management Information Bases (MIBs)

≠ Internal Network Management Port

≠ Forwards Spanning-Tree Packets to CPU

≠ Serial Media-Independent Interface (MII)

for PHY Control

D

EEPROM Interface for Autoconfiguration

(No CPU Required for Nonmanaged Switch)

D

Internal Address-Lookup/Frame-Routing

Engine

≠ Interoperable Support for IEEE

Std 802.1Q VLAN

≠ Supports IEEE Std 802.1D Spanning Tree

≠ Thirty-Two Assignable Virtual LANs

(VLANs)

≠ Multiple Forwarding Modes

≠ 2K Total Addresses Supported

≠ Port Mirroring

D

IEEE Std 1149.1 (JTAG) Interface (3.3-V

Signals)

D

2.5-V Process With 3.3-V-Drive I/O

D

Packaged in 240-Terminal Plastic Quad

Flatpack

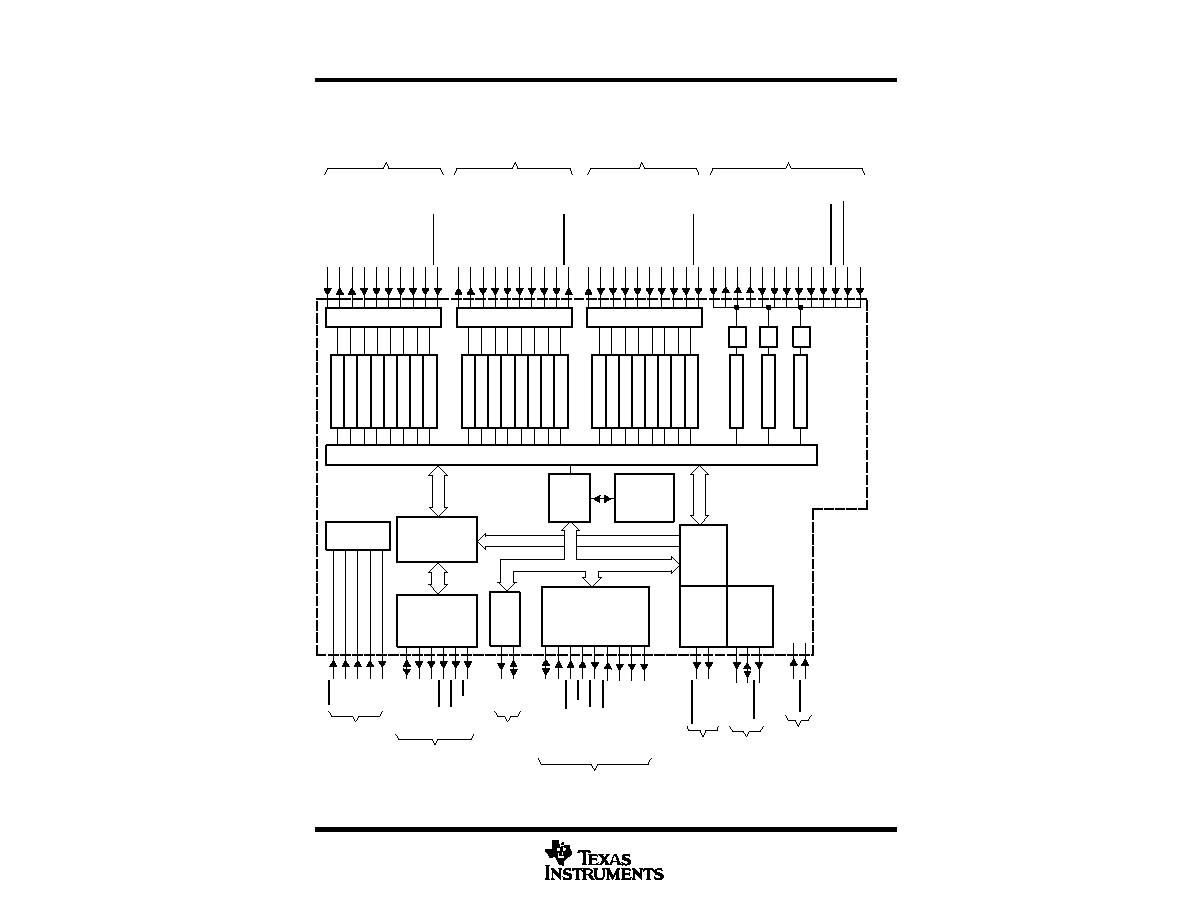

Eight Ports

(16≠23)

10 Mbit/s

Controller (MAC)

Controller (MAC)

Controller (MAC)

TAP

(JTAG)

Address

Compare

Statistics

Storage

MIB

Three Ports

(24≠26)

10/100 Mbit/s

Network

Statistics

Logic

Data Path

LED

Interface

CPU

Interface

SDRAM

Controller

Controller (MAC)

Controller (MAC)

Controller (MAC)

Controller (MAC)

MUX

Controller (MAC)

Controller (MAC)

MII

MII

MII

Eight Ports

(08≠15)

10 Mbit/s

Eight Ports

(00≠07)

10 Mbit/s

Queue

Manager

EEPROM

Interface

Controller (MAC)

Controller (MAC)

Controller (MAC)

Controller (MAC)

MUX

Controller (MAC)

Controller (MAC)

MUX

Copyright

©

1999, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

TI and ThunderSWITCH are trademarks of Texas Instruments Incorporated.

Ethernet is a trademark of Xerox Corporation.

Secure Fast Switching is a trademark of Cabletron Systems, Inc.

Port-trunking and load-sharing algorithms were contributed by Cabletron Systems, Inc. and are derived from, and compatible with, Secure Fast

Switching

TM

.

TNETX3270

ThunderSWITCH

TM

24/3 ETHERNET

TM

SWITCH

WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS

SPWS043B ≠ NOVEMBER 1997 ≠ REVISED APRIL 1999

3

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

SDRAM Interface

36

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SDRAM-Type and Quantity Indication

38

. . . . . . . . . . . . . . . . .

Initialization

38

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Refresh

38

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Frame Routing

39

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

VLAN Support

39

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

IEEE Std 802.1Q Headers ≠ Reception

40

. . . . . . . . . . . . . . . .

IEEE Std 802.1Q Headers ≠ Transmission

40

. . . . . . . . . . . . .

Address Maintenance

40

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Spanning-Tree Support

41

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Aging Algorithms

41

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Frame-Routing Determination

41

. . . . . . . . . . . . . . . . . . . . . . . .

Port Mirroring

44

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Port Trunking/Load Sharing

45

. . . . . . . . . . . . . . . . . . . . . . . . . .

Flow Control

45

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Collision-Based Flow Control

46

. . . . . . . . . . . . . . . . . . . . . . . . .

IEEE Std 802.3 Flow Control

46

. . . . . . . . . . . . . . . . . . . . . . . . .

Internal Wrap Test

48

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Duplex Wrap Test

49

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Port Mirroring

50

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Copy to Uplink

50

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Absolute Maximum Ratings

51

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Recommended Operating Conditions

51

. . . . . . . . . . . . . . . . . . . . .

Electrical Characteristics

51

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Parameter Measurement Information

52

. . . . . . . . . . . . . . . . . . . . . .

Test Measurement

52

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10-Mbit/s Interface (Ports 00≠23)

53

. . . . . . . . . . . . . . . . . . . . . . . . . .

10-/100-Mbit/s MAC Interface

54

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SDRAM Interface

56

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DIO/DMA Interface

58

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Serial MII Management Interface

60

. . . . . . . . . . . . . . . . . . . . . . . . . .

EEPROM Interface

61

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

LED Interface

62

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power-Up OSCIN and RESET

63

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Mechanical Data

64

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Description

2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PGV Package Terminal Layout

4

. . . . . . . . . . . . . . . . . . . . . . . . . .

TNETX3270 Interface Block Diagram

5

. . . . . . . . . . . . . . . . . . . .

Terminal Functions

6

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DIO Register Groups

13

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Interface Description

18

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DIO Interface

18

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Receiving/Transmitting Management Frames

18

. . . . . . . .

State of DIO Signals During Hardware Reset

18

. . . . . . . .

Network Management Port

19

. . . . . . . . . . . . . . . . . . . . . . . .

MII Serial Management Interface (PHY Management)

22

. . .

10-Mbit/s and 10-/100-Mbit/s MAC Interface

22

. . . . . . . . . . . .

Receive Control

22

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Giant (Long) Frames

22

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Short Frames

22

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Receive Filtering of Frames

23

. . . . . . . . . . . . . . . . . . . . . . .

Data Transmission

23

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Transmit Control

23

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Adaptive Performance Optimization

(APO) (Transmit Pacing)

23

. . . . . . . . . . . . . . . . . . . . . . . . .

Interframe Gap Enforcement

23

. . . . . . . . . . . . . . . . . . . . . .

Backoff

23

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Receive Versus Transmit Priority

24

. . . . . . . . . . . . . . . . . .

Uplink Pretagging

24

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

EEPROM Interface

27

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Interaction of EEPROM Load With the SIO Register

28

. .

Summary of EEPROM Load Outcomes

28

. . . . . . . . . . . . .

Compatibility With Future Device Revisions

28

. . . . . . . . .

JTAG Interface

29

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

HIGHZ instruction

29

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

LED Interface

29

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Lamp Test

30

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Multi-LED Display

30

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Hardware Configurations

30

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10-Mbit/s MAC Interfaces (Ports 00≠23)

30

. . . . . . . . . . . . . . .

10-/100-Mbit/s MAC Interfaces (Ports 24≠26)

34

. . . . . . . . . . .

10-/100-Mbit/s Port Configuration

34

. . . . . . . . . . . . . . . . . .

10-/100-Mbit/s Port Configuration

in a Nonmanaged Switch

35

. . . . . . . . . . . . . . . . . . . . . . . . .

10-/100-Mbit/s Port Configuration

in a Managed Switch

36

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contents