Description

The TMPR3904F is a 32-bit RISC micro

controller of the TX39 family. The TMPR3904F

uses the TX39/H Processor Core as the CPU, which

is a RISC CPU core Toshiba developed based on

the MIPS

ģ

R3000A architecture. The TMPR3904F

has built-in peripheral circuits such as DRAM and

ROM Memory Controllers, DMA Controllers,

Serial and Parallel Communication Ports, and

Timer/Counter implementations.

The TX39/H core and added Direct Memory

Access Controller (DMAC) features of this chip

allow the transfer of data to and from system

memory with high performance.

Microprocessor Features

∑

Built≠in TX3900 Processor Core

-

Developed based on the R3000A architecture

-

Instruction cache 4KB and Data cache 1KB

-

Built-in Debug Support Unit (DSU)

-

Five-stage pipeline: Fetch, Decode, Execute,

Memory access, and Register write

-

Incorporates single cycle 32-bit DSP function

Multiply-Accumulate (MAC) instruction

∑

Power Supply: V

DD

= 3.3V

Ī

0.3V

∑

Maximum Operating Frequency: 50MHz

∑

Package: 208 pin plastic QFP

Peripheral Features

∑

DRAM Controller

-

Supports 2 channels of DRAM memories

-

Each channel supports up to four banks of

memory

-

Independent memory size and timing set-up

for each channel

-

Support of 32/ 16-bit static bus sizing

-

Supports both fast and hyper page EDO

modes

∑

ROM Controller

-

Supports 2 channels of ROM controller

-

Supports page mode ROM support

-

Supports various memory size of

1M/2M/4M/8M/16M/32M byte per channel

-

Supports 32/16-bit static bus sizing

-

Supports Mask ROM, EPROM, E

2

PROM,

SRAM, and Flash Memory

∑

Timer/Counter

- 3-channel 24-bit up-counter

-

Interval, Watchdog, and Pulse Generator timer

modes

∑

Serial I/O Ports

-

Two-channel UART

-

Baud rate generator and modem flow control

∑

Interrupt Controller

-

Priority process of 17 interrupt sources: nine

internals, eight externals

-

Non-maskable Interrupt (NMI)

∑

Direct Memory Access Controller (DMAC)

-

Independent 2-channel DMA

-

Supports both with and without snoop bus

ownership requests

-

Supports memory-to-memory, memory-to-

I/O, and I/O-to-memory transfer devices

-

Supports Internal/External transfer requests

-

Supports both Dual Address and Single

Address transfer modes

-

Supports device sizes of: 32-bit memory; 8,

16, or 32-bit I/O

∑

Parallel I/O (PIO) Ports

-

Three 8-bit ports (one exclusive, two shared)

TOSHIBA

TMPR3904F 32-bit MIPS

RISC Microprocessor

Product Brief

TOSHIBA AMERICA ELECTRONIC COMPONENTS, INC.

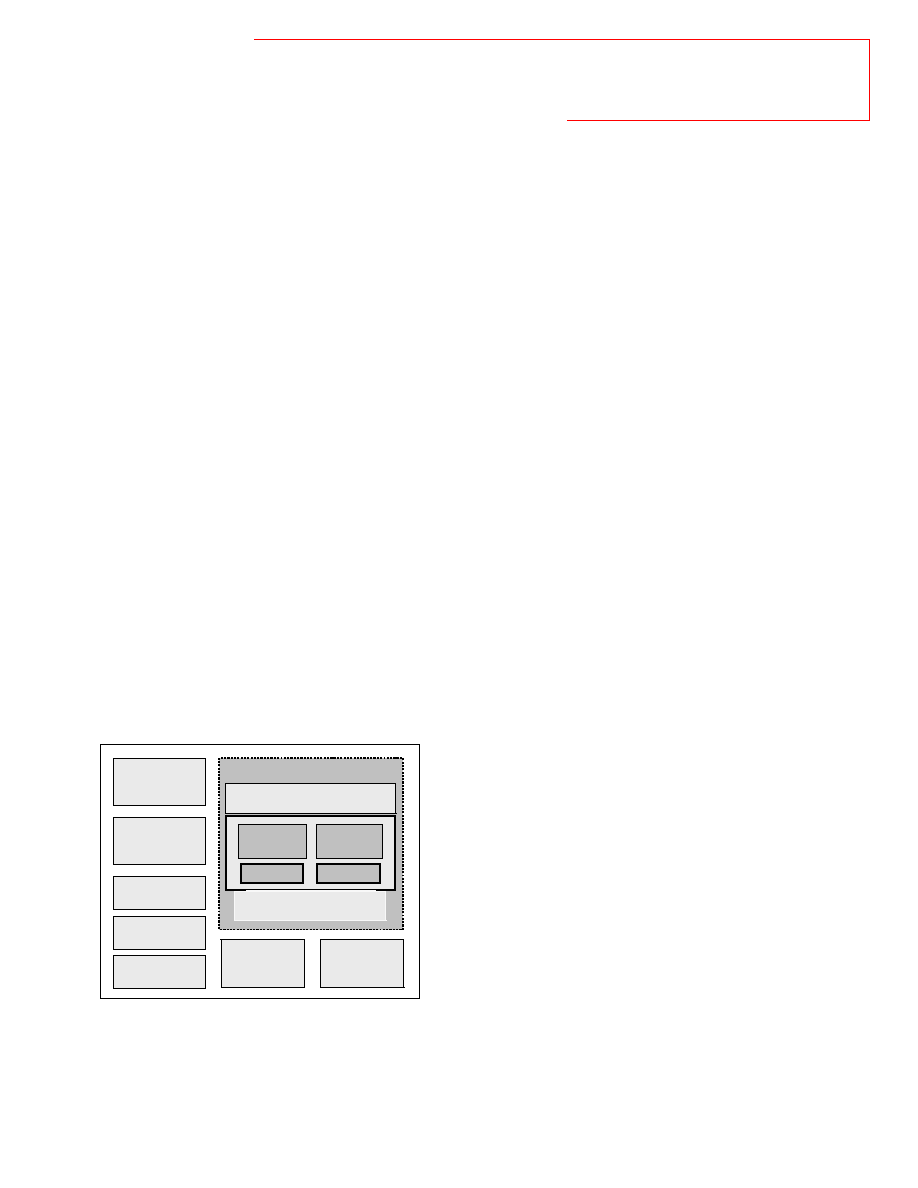

Instruction

cache

Data

cache

WBU

DSU

G-Bus Interface

R3900 Processor Core

CPU

DMAC

2 ch

DMAC

2 ch

DRAM

controller

ROM

controller

Timer 3 ch

IRC

UART 2 ch

Figure 1. TMPR3904F Simplified Block Diagram

TOSHIBA AMERICA ELECTRONIC COMPONENTS, INC.

Regional Sales Offices

TOSHIBA

Irvine, CA

Atlanta, GA

Boston, MA

Portland, OR

TEL:(714)453-0224

TEL:(770)931-3363

TEL:(617)224-0074

TEL:(503)629-0818

FAX:(714)453-0125

FAX:(770)931-7602

FAX:(617)224-1096

FAX:(503)629-0827

San Jose, CA

Chicago, IL

Edison, NJ

Dallas, TX

TEL:(408)456-8900

TEL:(708)945-1500

TEL:(908)248-8070

TEL:(972)480-0470

FAX:(408)456-8910

FAX:(708)945-1044

FAX:(908)248-8030

FAX:(972)235-4114

TMPR3904F 32-bit MIPS RISC Microprocessor

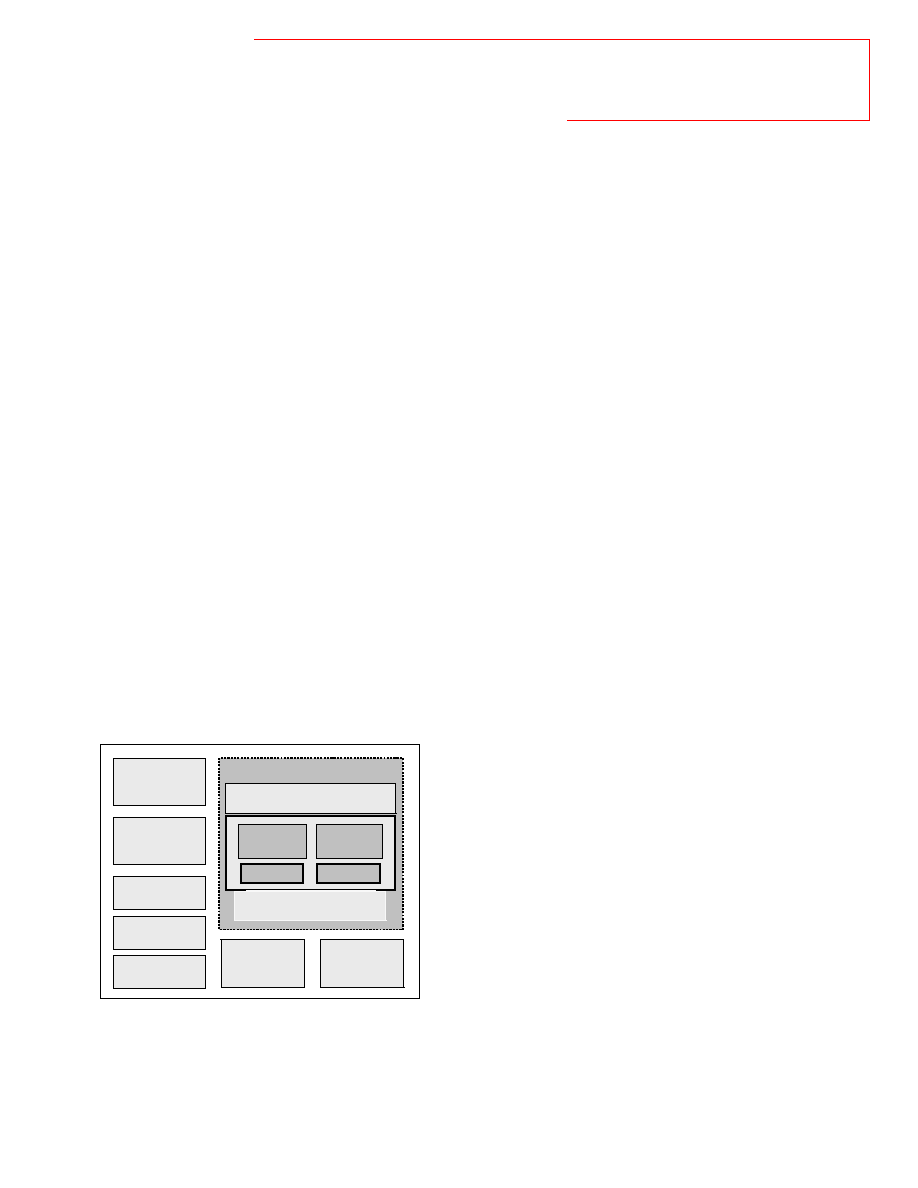

Instruction

cache

Data

cache

WBU

DSU

G-Bus Interface

DRAMC

ROMC

IRC

G to IM Bridge

CG

PIO

Timer0

Timer1

Timer2

DMAC1

2channel

DMAC0

2channel

SIO0

SIO1

EBIF

Debug[7:0]

DREQ[1:0]D

ACK[1:0]

DONE*

DREQ[8:2]

DACK[8:2]

RAS1,0[3:0]*

CAS[3:0]*

WE*

OE[1:0]*

CE1, 0[1:0]

SWE*[1:0]

INT[7:0]

XIN

XOUT

SIN0

SOUT0

SCNT0[1:0]

SCLKIN

SIN1

SOUT1

SCNT1[1:0]

G Bus

IM Bus

SYSCLK

A[31:1]

BE[3:0]*

D[31:0]

R/W*

BSTART

ACK*

BUSERR*

RESET*

BUSREQ*

BUSGNT*

BUSREL*

HAVEIT*

NMI*

ENDIAN

HALF*

SCS[3:0]

BOOT16

TEST*

CLKEN

PLLOFF*

PIO0[7:0]

TIMOUT1

TIMIN1

TIMOUT2

TIMIN2

R3900 Core

www.toshiba.com/taec

MIPS

ģ

is a registered trademark R3000A is a trademark of UPS Technologies, Inc.

Figure 2. TMPR3904F Internal Block Diagram

1.

This technical data may be controlled under U.S. Export Administration Regulations and may be subject to the approval of the U.S. Department of Commerce prior to export. Any re-

export, directly or indirectly, in contravention of the U.AS. Export Administration Regulations is strictly prohibited.

2. The information in this document has been checked and is believed to be reliable; however, no responsibility can be assumed for inaccuracies that may not have been caught. All

information in this document is subject to change without prior notice. Furthermore, Toshiba cannot assume responsibility for the use of any license under the patent rights of Toshiba

or any third parties.