| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: TA2020 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

T r i p a t h T e c h n o l o g y, I n c . - T e c h n i c a l I n f o r m a t i o n

1

TA2020 ≠ CS/6.1/04-03

TA2020-020

STEREO 20W (4

) CLASS-TTM DIGITAL AUDIO AMPLIFIER DRIVER

USING DIGITAL POWER PROCESSING (DPPTM) TECHNOLOGY

T e c h n i c a l I n f o r m a t i o n R e v i s i o n 6 . 1 ≠ A p r i l 2 0 0 3

G E N E R A L D E S C R I P T I O N

The TA2020-020 is a 20W (4

) continuous average per channel Class-T Digital Audio Power Amplifier IC

using Tripath's proprietary Digital Power Processing (DPP

TM

) technology. Class-T amplifiers offer both the

audio fidelity of Class-AB and the power efficiency of Class-D amplifiers.

A P P L I C A T I O N S

DVD Players

Mini/Micro Component Systems

Computer / PC Multimedia

Cable Set-Top Products

Televisions

Battery Powered Systems

B E N E F I T S

Fully integrated solution with internal FETs

Easier to design-in than Class-D

Reduced system cost with minimal heat sink

requirement

Dramatically improves efficiency versus Class-AB

amplifiers

Signal fidelity equal to high quality linear

amplifiers

High dynamic range compatible with digital media

such as CD and DVD, and internet audio

F E A T U R E S

Class-T architecture

Single Supply Operation

"Audiophile" Quality Sound

0.03% THD+N @ 10W 4

0.1% THD+N @12W 4

0.18% IHF-IM @ 1W 4

High Power

25W @ 4

, 10% THD+N, V

DD

=14.6V

22W @ 4

, 10% THD+N, V

DD

=13.5V

13W @ 8

, 10% THD+N, V

DD

=13.5V

High Efficiency

88% @ 12W 8

81% @ 20W 4

Dynamic Range = 99dB

Mute and Sleep inputs

Turn-on & turn-off pop suppression

Over-current protection

Over-temperature protection

Bridged outputs

32-pin SSIP package

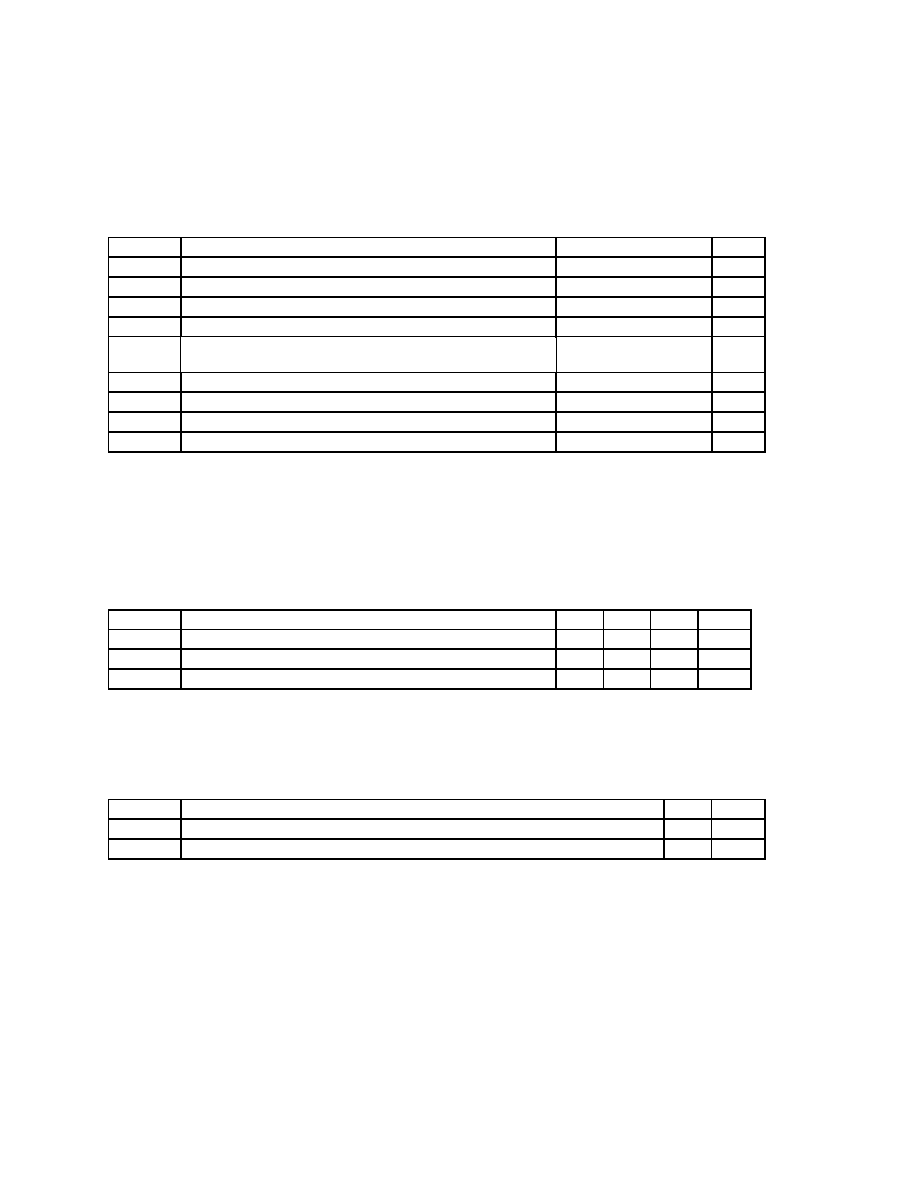

T Y P I C A L P E R F O R M A N C E

THD+N (%)

Output Power (W)

THD+N versus Output Power

VDD = 13.5V

Av = 12V/V

f = 1kHz

BW = 22Hz - 22kHz

1

2

3

4

5 6 7 8 9 10

20

500m

R

L

= 8

R

L

= 4

1

2

5

0.02

0.01

0.05

0.1

0.2

0.5

10

T r i p a t h T e c h n o l o g y, I n c . - T e c h n i c a l I n f o r m a t i o n

2

TA2020 ≠ CS/6.1/04-03

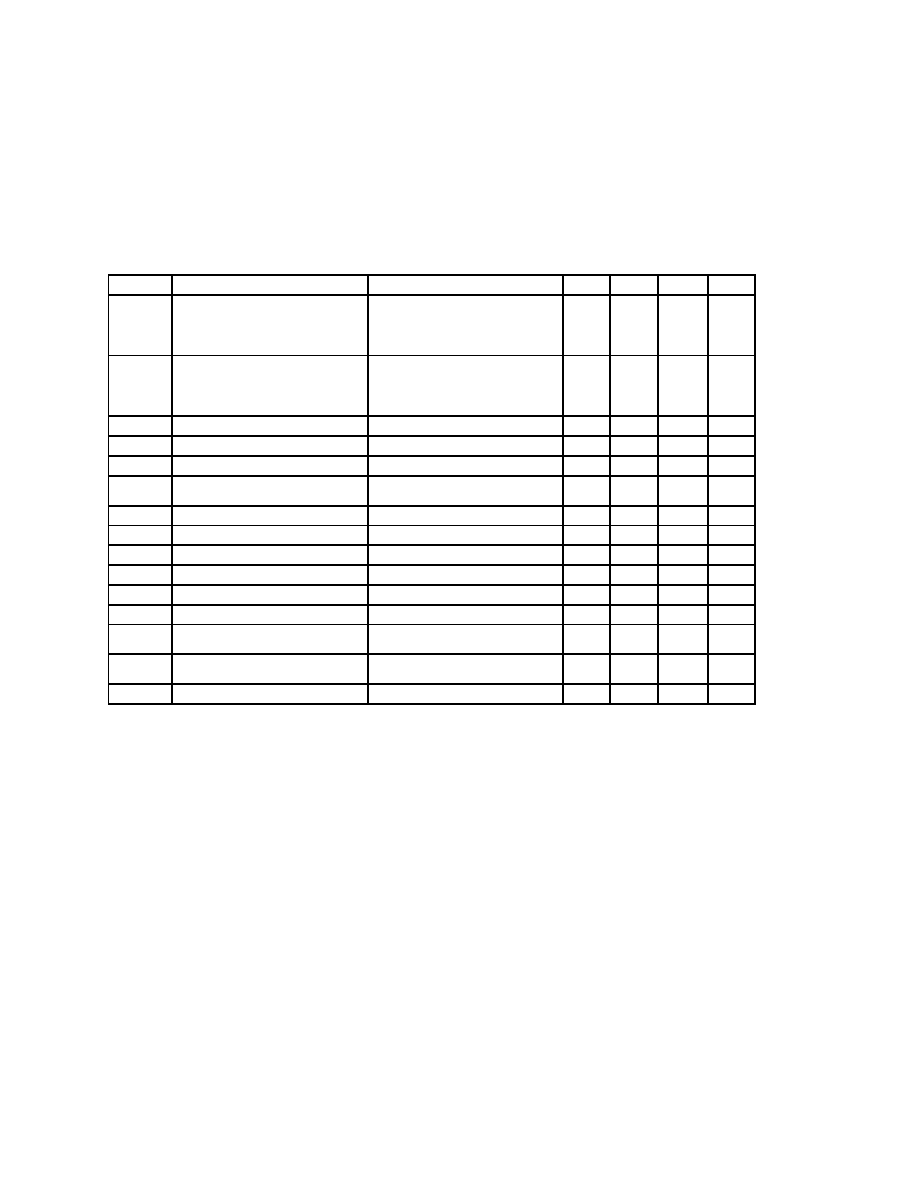

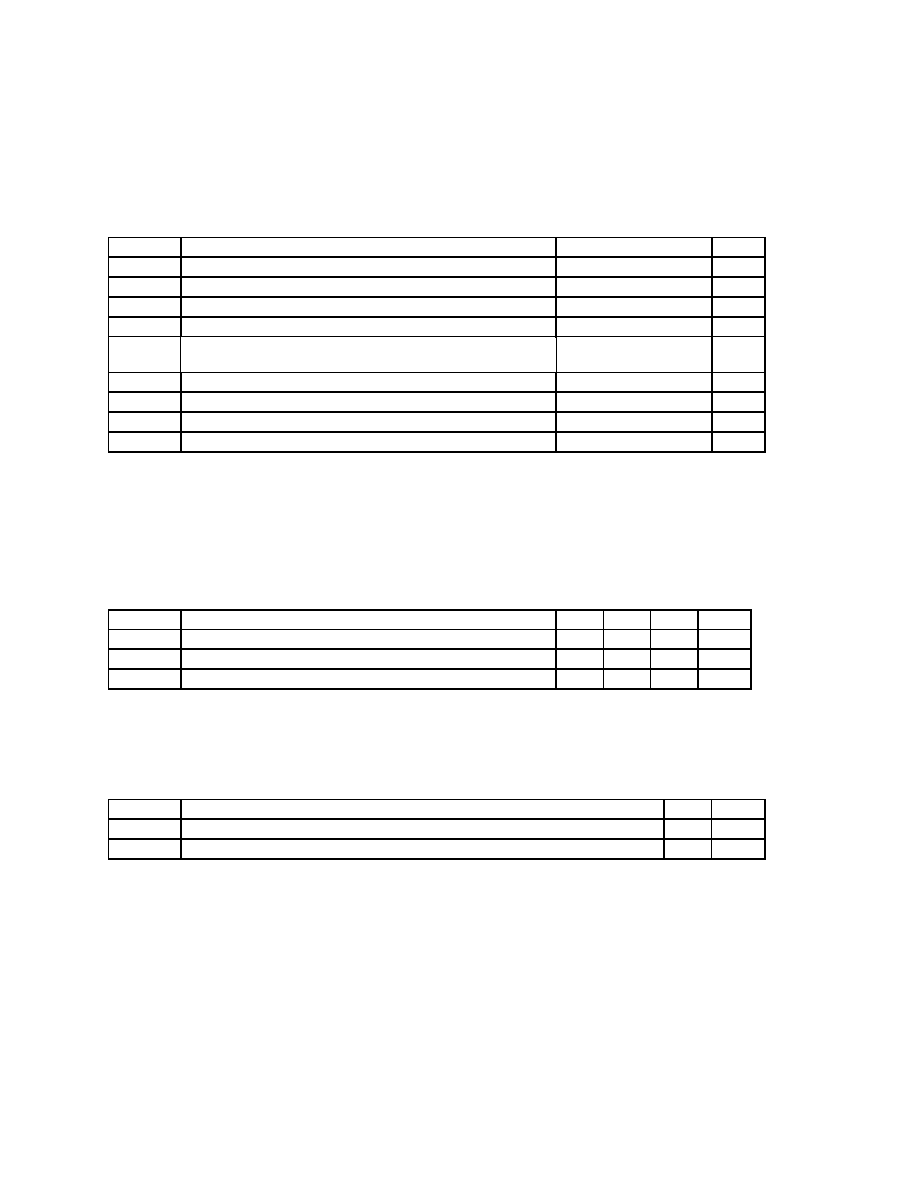

A B S O L U T E M A X I M U M R A T I N G S

(Note 1)

SYMBOL PARAMETER

Value

UNITS

V

DD

Supply Voltage

16

V

V5

Input Section Supply Voltage

6.0

V

SLEEP

SLEEP Input Voltage

-0.3 to 6.0

V

MUTE

MUTE Input Voltage

-0.3 to V5+0.3

V

ESD

HBM

ESD Susceptibility, All pins except 2, 30

Human Body Model (Note2) Pins 2, 30

2000

1000

V

V

ESD

MM

ESD Susceptibility, Machine Model (Note 3)

200

V

T

STORE

Storage Temperature Range

-40

to 150

∞C

T

A

Operating Free-air Temperature Range

-40 to 85

∞C

T

J

Junction Temperature

150

∞C

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.

See the table below for Operating Conditions.

Note 2: Human body model, 100pF discharged through a 1.5K

resistor.

Note 3: Machine model, 220pF discharged through all pins.

O P E R A T I N G C O N D I T I O N S

(Note 4)

SYMBOL PARAMETER MIN.

TYP.

MAX.

UNITS

V

DD

Supply Voltage

8.5

13.5

14.6

V

V

IH

High-level Input Voltage (MUTE, SLEEP)

3.5

V

V

IL

Low-level Input Voltage (MUTE, SLEEP)

1

V

Note 4: Recommended Operating Conditions indicate conditions for which the device is functional.

See Electrical Characteristics for guaranteed specific performance limits.

T H E R M A L C H A R A C T E R I S T I C S

SYMBOL PARAMETER

VALUE

UNITS

JC

Junction-to-case Thermal Resistance

3.5∞ C/W

JA

Junction-to-ambient

Thermal

Resistance

15∞ C/W

T r i p a t h T e c h n o l o g y, I n c . - T e c h n i c a l I n f o r m a t i o n

3

TA2020 ≠ CS/6.1/04-03

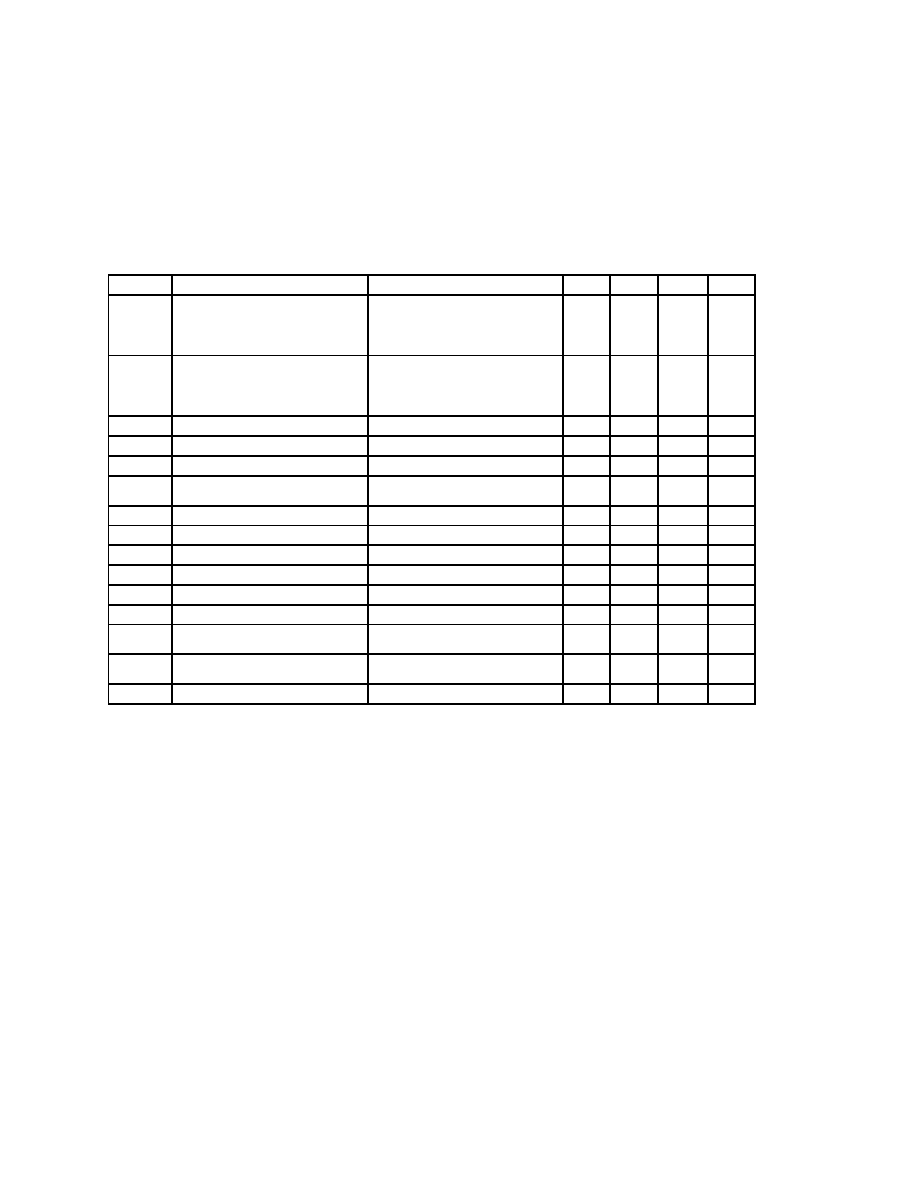

E L E C T R I C A L C H A R A C T E R I S T I C S

(Notes 6, 7)

See Test/Application Circuit. Unless otherwise specified, V

DD

= 13.5V, f = 1kHz,

Measurement Bandwidth = 22kHz, R

L

= 4

, T

A

= 25

∞C.

SYMBOL PARAMETER

CONDITIONS MIN.

TYP.

MAX.

UNITS

P

O

Output Power

(Continuous Average/Channel)

THD+N = 0.1%

R

L

= 4

R

L

= 8

THD+N = 10%

R

L

= 4

R

L

= 8

11

7

18

10

W

W

W

W

P

O

Output Power (V

DD

=14.6V)

(Continuous Average/Channel)

THD+N = 0.1%

R

L

= 4

R

L

= 8

THD+N = 10%

R

L

= 4

R

L

= 8

16.5

9.5

25

14.8

W

W

W

W

I

DD,MUTE

Mute Supply Current

MUTE = V

IH

5.5

7

mA

I

DD, SLEEP

Sleep Supply Current

SLEEP = V

IH

0.25

2

mA

I

q

Quiescent Current

V

IN

= 0 V

64

75

mA

THD + N Total Harmonic Distortion Plus

Noise

P

O

= 10W/Channel

0.03

%

IHF-IM

IHF Intermodulation Distortion

19kHz, 20kHz, 1:1 (IHF)

0.1

0.5

%

SNR

Signal-to-Noise Ratio

A-Weighted, P

OUT

= 20W, R

L

= 4

99 dB

CS

Channel Separation

0dBr = 1W, R

L

= 4, f = 1 kHz

74

80

dB

PSRR

Power Supply Rejection Ratio

Vripple = 100mV

60

80

dB

Power Efficiency

P

OUT

= 12W/Channel, R

L

= 8

88

%

V

OFFSET

Output Offset Voltage

No Load, MUTE = Logic low

50

150

mV

V

OH

High-level output voltage

(FAULT & OVERLOADB)

3.5

V

V

OL

Low-level output voltage

(FAULT & OVERLOADB)

1

V

e

OUT

Output Noise Voltage

A-Weighted, input AC grounded

100

µV

Note 6: Minimum and maximum limits are guaranteed but may not be 100% tested.

Note 7: For operation in ambient temperatures greater than 25

∞C, the device must be derated based on the

maximum junction temperature and the thermal resistance determined by the mounting technique.

T r i p a t h T e c h n o l o g y, I n c . - T e c h n i c a l I n f o r m a t i o n

4

TA2020 ≠ CS/6.1/04-03

P I N D E S C R I P T I O N

T A 2 0 2 0 P I N O U T

Pin

Function

Description

2, 8

V5D, V5A

Digital 5VDC, Analog 5VDC

3, 7,

16

AGND1, AGND2,

AGND3

Analog Ground

4

REF

Internal reference voltage; approximately 1.0VDC

6

OVERLOADB

A logic low output indicates the input signal has overloaded the amplifier.

9, 12

OAOUT1, OAOUT2

Input stage output pins

10, 13

INV1, INV2

Single-ended inputs. Inputs are a "virtual" ground of an inverting opamp with

approximately 2.4VDC bias.

11

MUTE

When set to logic high, both amplifiers are muted and in idle mode. When low

(grounded), both amplifiers are fully operational. If left floating, the device stays in

the mute mode. Ground if not used.

14

BIASCAP

Input stage bias voltage (approximately 2.4VDC).

17

SLEEP

When set to logic high, device goes into low power mode. If not used this pin

should be grounded. Can be pulled-up to V

DD

with a 1M resistor (100K

minimum).

18

FAULT

A logic high output indicates thermal overload, or an output is shorted to ground,

or another output.

19, 28

PGND2, PGND1

Power Ground (high current)

20

DGND

Digital Ground. Should be connected to AGND locally at TA2020-020.

21, 23,

26, 24

OUTP2 & OUTM2;

OUTP1 & OUTM1

Bridged output pairs

22, 25

VDD2, VDD1

Supply pin for high current H-bridges, nominally 13.5VDC.

1, 5, 15

NC

Not connected

27 VDDA

Analog

13.5VDC

29

CPUMP

Charge pump output (nominally 10V above VDDA)

30

5VGEN

Regulated 5VDC source used to supply power to the input section (pins 2 & 8).

31, 32

DCAP2, DCAP1

Charge pump switching pins. DCAP1 (pin 32) is a free running 300kHz square

wave between VDDA and DGND (13.5Vpp nominal). DCAP2 (pin 31) is level

shifted 10 volts above DCAP1 (pin 32) with the same amplitude (13.5Vpp

nominal), frequency, and phase as DCAP1.

5VGEN

NC

FAULT

PGND2

DGND

OUTP2

VDD2

OUTM2

OUTM1

VDD1

OUTP1

NC

VDDA

PGND1

CPUMP

DCAP2

AGND3

BIASCAP

INV2

OAOUT2

MUTE

INV1

OAOUT1

V5A

AGND2

OVERLOADB

REF

AGND1

V5D

DCAP1

30

16

17

18

19

20

21

22

23

24

25

26

27

28

29

1

15

14

13

11

10

12

9

8

7

6

5

4

3

2

32-pin SSIP Package

(Front View)

32

31

SLEEP

NC

T r i p a t h T e c h n o l o g y, I n c . - T e c h n i c a l I n f o r m a t i o n

5

TA2020 ≠ CS/6.1/04-03

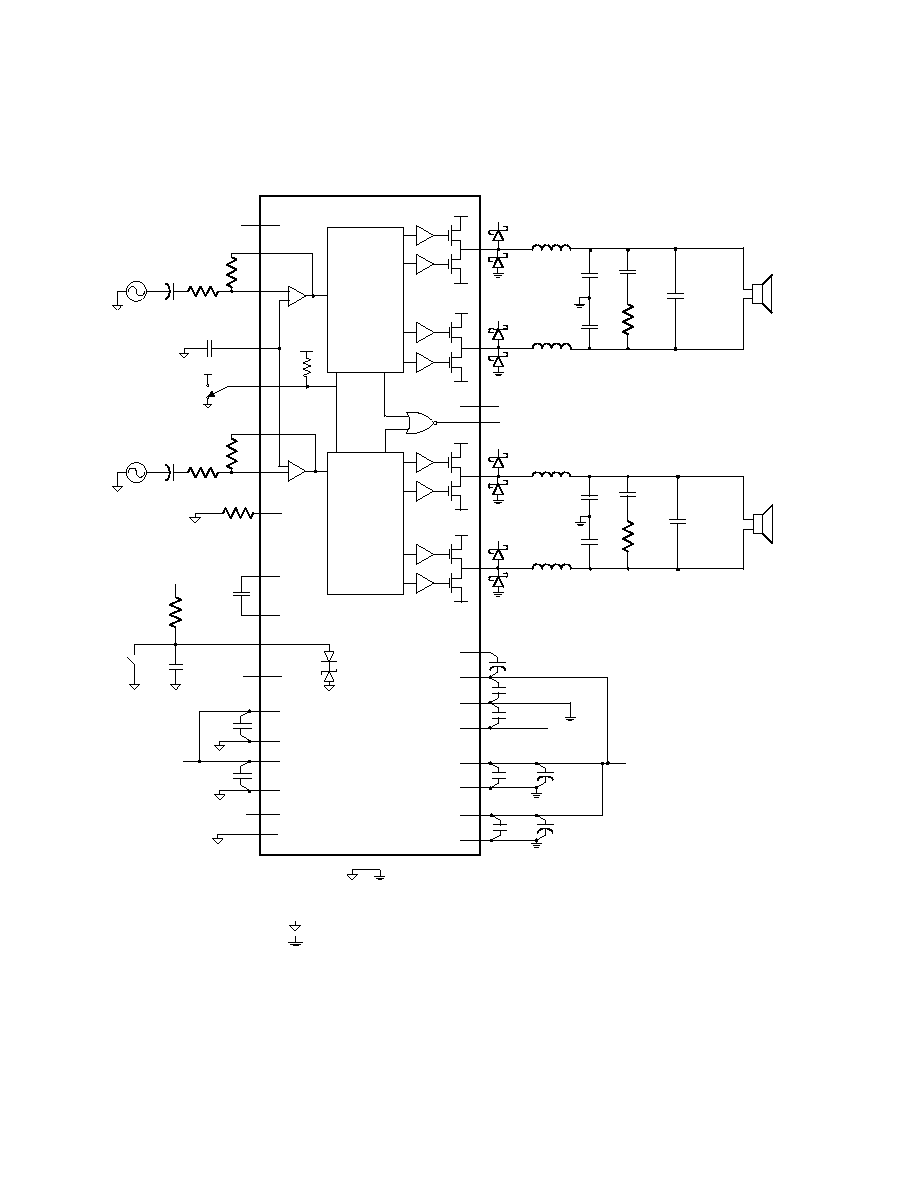

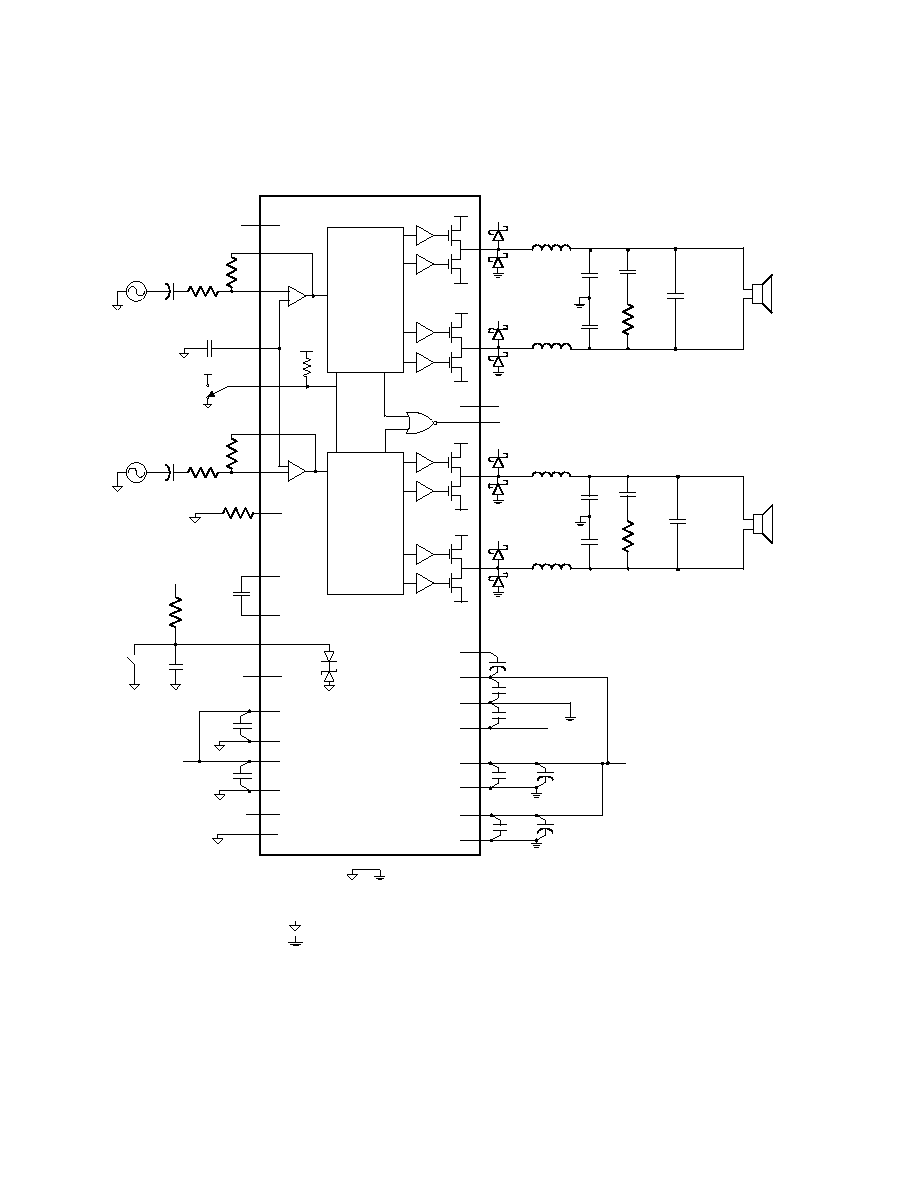

A P P L I C A T I O N / T E S T C I R C U I T

TA2020-020

R

L

4

or *8

MUTE

FAULT

OVERLOAD

B

(+13.5V)

C

I

2.2uF

OAOUT1

OAOUT2

INV1

INV2

OUTP1

OUTM1

OUTP2

OUTM2

VDDA

5VGEN

BIASCAP

DCAP2

DCAP1

C

I

2.2uF

C

A

0.1uF

C

D

0.1uF

CPUMP

9

10

19

30

27

25

22

6

18

26

24

21

23

29

31

32

13

12

11

14

R

F

20K

17

R

Z

10

, 1/2W

C

Z

0.47uF

C

P

1uF

+

+

5V

SLEEP

5V

5V

+12V

0.1uF

REF

R

REF

8.25K

, 1%

4

5

NC

1M

* Use C

o

= 0.22

µF and Cz=0.22uF for 8 Ohm loads

VDD1

PGND1

VDD1

PGND1

VDD2

VDD2

PGND2

PGND2

Note: Analog and Digital/Power Grounds must

be connected locally at the TA2020-020

C

S

0.1uF

C

S

0.1uF

To Pin 30

2

3

V5D

7

15

AGND2

V5A

20

C

S

0.1uF

DGND

VDD1

PGND2

28

PGND1

180uF, 16V

VDD2

VDD

+

+

+

Processing

&

Modulation

Processing

&

Modulation

*C

o

0.47uF

L

o

10uH, 3A

8

(Pin 7)

Analog Ground

Digital/Power Ground

(Pin 28)

(Pin 28)

(Pin 19)

(Pin 19)

To Pin 2,8

R

I

20K

(Pin 3)

R

F

20K

R

I

20K

1

NC

NC

AGND3

16

180uF, 16V

C

SW

C

SW

*C

o

0.47uF

L

o

10uH, 3A

R

L

4

or *8

L

o

10uH, 3A

L

o

10uH, 3A

*C

o

0.47uF

*C

o

0.47uF

C

Z

0.47uF

C

SW

0.1uF

C

SW

0.1uF

C

S

0.1uF

D

O

D

O

D

O

D

O

R

Z

10

, 1/2W

(Pin 28)

(Pin 19)

AGND1

VDD2 (pin 22)

VDD1 (pin 25)

D

H

D

H

D

H

D

H

VDD1 (pin 25)

VDD2 (pin 22)

Diodes (D

O

and D

H

) are Motorola MBRS130T3 (the D

H

diodes are required for V

DD

>13.5V)

C

DO

0.1uF

C

DO

0.1uF