| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: TQ8025 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

PRELIMINARY DATA SHEET

SWITCHING

PRODUCTS

1

For additional information and latest specifications, see our website: www.triquint.com

T

R

I Q

U

I

N

T

S E M I C O N D U C T O R , I N C .

TQ8025

2.5 Gigabit/sec

16x16 Digital

Crosspoint Switch

The TQ8025 is a non-blocking 16 x 16 digital crosspoint switch capable of

data rates greater than 2.5 gigabits per second per port. With a fully

differential internal data path and PECL/CML I/O, the TQ8025 offers an

extremely high data rate with exceptional signal fidelity. The use of fully

differential logic results in low crosstalk, jitter, and signal skew. The

TQ8025 is ideally suited for digital video, data communications,

telecommunication switching, and cross-connect applications.

The non-blocking architecture uses 16 fully independent 16:1 multiplexers

which allow each output port to be independently programmed to any input

port. The TQ8025 offers two programming options: a flexible port-by-port

option, and a fast configuration option.

Using the fast configuration option, all 16 switch ports are programmed

within 80ns by serially loading four 16-bit input port selection words. Two

output pins (RADD0,1) are provided to drive an external RAM

(n x 4 x 16 bits) used to store the switch configuration. An Autoconfigure

option automatically transfers the new configurations into the switch core.

Autoconfiguration occurs after the last input selection word is clocked into

the programming registers.

Data integrity is maintained on all unchanged data paths for both the port-

by-port and fast configuration options.

Features

∑ 16 PECL/CML fully differential

(back-terminated) outputs

∑ >2.5 Gb/s data bandwidth

per channel

∑ >40 Gb/s aggregate bandwidth

∑ Non-blocking architecture

∑ 80 ns configuration time

∑ Autonomous control of external

RAM for configuration data

∑ Low jitter and signal skew

∑

±

100 ps delay match (one input

to all outputs)

∑ Fully differential data path

∑ 132-pin MLC package with

heat spreader

Applications

∑ SONET OC-48 data path

∑ Double-speed Fibre Channel

∑ Hubs and routers

∑ High-definition video switching

∑ Parallel processing

CONFIG

RESET≠

CLOCK

ADD15

AUTOCONFIG

ADDREN

Address Generator

and Control

16 x 16

Crosspoint

Switch Matrix

Configuration

Latches

PECL/CML

Input

Buffers

PECL/CML

Output

Buffers

DOÿ≠15

32

DIÿ≠15

32

TQ8025

16 x 4

LOAD

LDMODE

RADD1

ADDÿ

4-Bit Shift

Register

4-Bit Shift

Register

READY

+5V

GND

(differential)

(differential)

RADDÿ

TQ8025

PRELIMINARY DATA SHEET

For additional information and latest specifications, see our website: www.triquint.com

2

Specifications

Table 1. Absolute Maximum Ratings

4

Storage temperature

T

STORE

≠65

∞

C to +150

∞

C

Junction temperature

T

CH

150

∞

C

Case temperature with bias

1

T

C

T

J

= 150

∞

C

Supply voltage

2

V

CC

0 V to +7.0 V

Voltage to any input

2

V

IN

≠0.5 V to V

CC

+ 0.5 V

Voltage to any output

2

V

OUT

≠0.5 V to V

CC

+ 0.5 V

Current to any input

2

I

IN

≠1.0 mA to +1.0 mA

Current from any output

2

I

OUT

40 mA

Power dissipation of output

3

P

OUT

50 mW

Notes: 1. T

C

is measured at the case top.

2. All voltages are measeured with respect to GND 0V and are continuous.

3. P

OUT

= (V

CC

≠ V

OUT

) x I

OUT

.

4. Absolute maximum ratings in this table are those beyond which the device's performance may be impaired

and/or permanent damage may occur.

Table 2. Recommended Operating Conditions

4

Symbol

Parameter

Min

Typ

Max

Units

Notes

T

C

Case Operating Temperature

0

--

85

∞

C

1, 3

V

CC

Supply Voltage

4.75

--

5.25

V

V

TT

Load Termination Supply Voltage

V

CC

≠ 2.0

V

2

I

CC

Current Positive Supply

--

--

2.1

A

R

LOAD

Output Termination Load Resistance

50

2

JC

Thermal Resistance Channel to Case

4.5

∞

C/W

Notes: 1. T

C

measured at case top. Use of adequate heatsink is required.

2. The V

TT

and R

LOAD

combination is subject to maximum output current and power restrictions.

3. Contact the Factory for extended temperature range applications.

4. Functionality and/or adherence to electrical specifications is not implied when

the device is subjected to conditions that exceed, singularly or

in combination, the operating range specified.

TQ8025

PRELIMINARY DATA SHEET

SWITCHING

PRODUCTS

3

For additional information and latest specifications, see our website: www.triquint.com

Table 3. DC Characteristics -- CML I/O

5

Symbol

Description

Test Conditions

Min

Nom

Max

Unit

V

COM

Common mode voltage

(Note 1)

V

CC

≠ 600

--

V

CC

mV

V

DIFF

Differential voltage

(Note 1)

400

--

1200

mV

V

IH

Input HIGH voltage

(Note 2)

--

V

CC

mV

V

IL

Input LOW voltage

V

CC

≠ 1100

--

mV

V

OH

Output HIGH voltage

(Note 3)

V

CC

≠ 100

--

V

CC

mV

V

OL

Output LOW voltage

(Note 3)

V

CC

≠ 1100

--

V

CC

≠ 600

mV

I

OH

Output HIGH current

(Note 3, 4)

20

23

30

mA

I

OL

Output LOW current

(Note 3, 4)

0

5

8

mA

Notes (Tables 3, 4, and 5):

1. Differential inputs.

2. V

REF

= 1300 mV.

3. R

LOAD

= 50 ohms to V

TT

= V

CC

≠ 2.0 V.

4. Not tested; consistent with V

OH

and V

OL

tests.

5. Specifications apply over recommended operating ranges.

Table 5. DC Characteristics -- TTL I/O

5

Symbol

Description

Test Conditions

Min

Nom

Max

Unit

V

IH

Input HIGH voltage

2.0

--

V

CC

V

V

IL

Input LOW voltage

0

--

0.8

V

I

IH

Input HIGH current

V

(IHMAX)

--

--

200

uA

I

IL

Input LOW current

V

(ILMIN)

≠400

≠200

--

uA

V

OH

Output HIGH voltage

I

OH

= 50 mA

2.4

--

V

CC

V

V

OL

Output LOW voltage

I

OH

= ≠20 mA

0

--

0.4

V

C

IN

Input capacitance

--

--

TBD

pF

C

OUT

Output capacitance

--

--

TBD

pF

VESD

ESD breakdown rating

(Note 5)

Class I

--

--

Table 4. DC Characteristics -- PECL I/O

5

Symbol

Description

Test Conditions

Min

Nom

Max

Unit

V

COM

Common mode voltage

(Note 1)

V

CC

≠ 1500

--

V

CC

≠ 1100

mV

V

DIFF

Differential voltage

(Note 1)

400

--

1200

mV

V

IH

Input HIGH voltage

(Note 2)

--

V

CC

≠ 500

mV

V

IL

Input LOW voltage

V

CC

≠ 2100

--

mV

V

OH

Output HIGH voltage

(Note 3)

V

CC

≠ 1100

--

V

CC

≠ 600

mV

V

OL

Output LOW voltage

(Note 3)

V

CC

≠ 2100

--

V

CC

≠ 1600

mV

I

OH

Output HIGH current

(Note 4)

20

23

30

mA

I

OL

Output LOW current

(Note 4)

0

5

8

mA

C

IN

Input capacitance

--

--

TBD

pF

C

OUT

Output capacitance

--

--

TBD

pF

VESD

ESD breakdown rating

(Note 5)

Class I

--

--

TQ8025

PRELIMINARY DATA SHEET

For additional information and latest specifications, see our website: www.triquint.com

4

Table 6. AC Characteristics

Symbol

Description

Test Conditions

Min

Typ

Max

Unit

T

PW

D(0:15) minimum pulse width (Note 1)

360

--

--

ps

T

R/F

O(0:15) rise/fall time 20-80%

(Note 1)

--

--

150

ps

T

PD

D(0:15), O(0:15) delay time

(Note 1)

--

--

2.5

ns

T

SKEW

Path delay matching

(Note 1)

300

ps

T

JITTER

Jitter

(Note 2)

--

50

--

ps pk≠pk

Notes: 1. Minimum V

OH

to maximum V

OL

levels.

2. Crossing of (On)--(NOn) measured with 2

23

≠ 1 PRBS, measured over extended time.

T6

T1

T1

T2

T4

T3

T5

SRCE ADDR 1

SRCE ADDR 2

LDMODE=0; AUTOCONFIG = Don't Care, RESET≠ = 1, CLOCK = Don't Care.

OLD CONFIGURATION

NEW CONFIGURATION

DEST ADDR 1

DEST ADDR 2

DAD0:3

SAD0:3

LOAD

CONFIGURE

SIGNAL PATHS

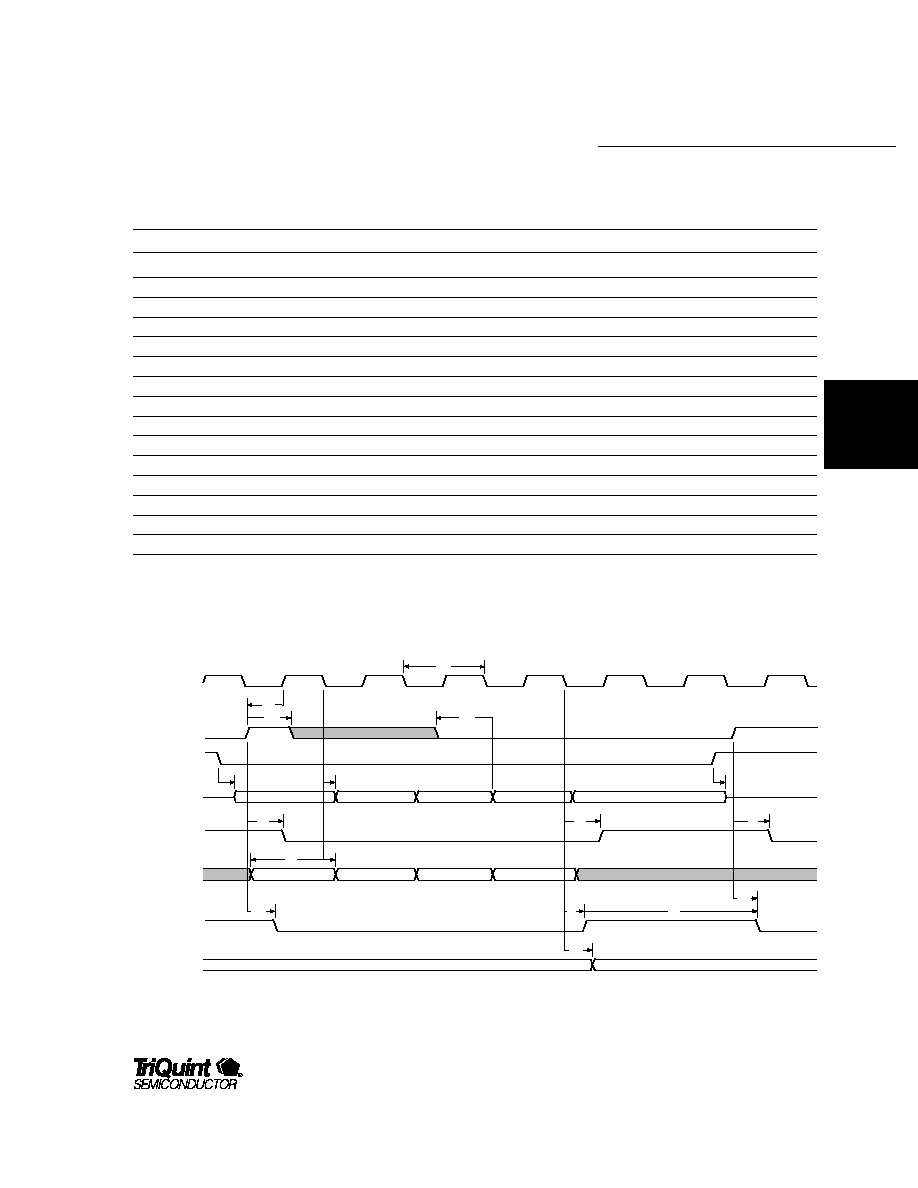

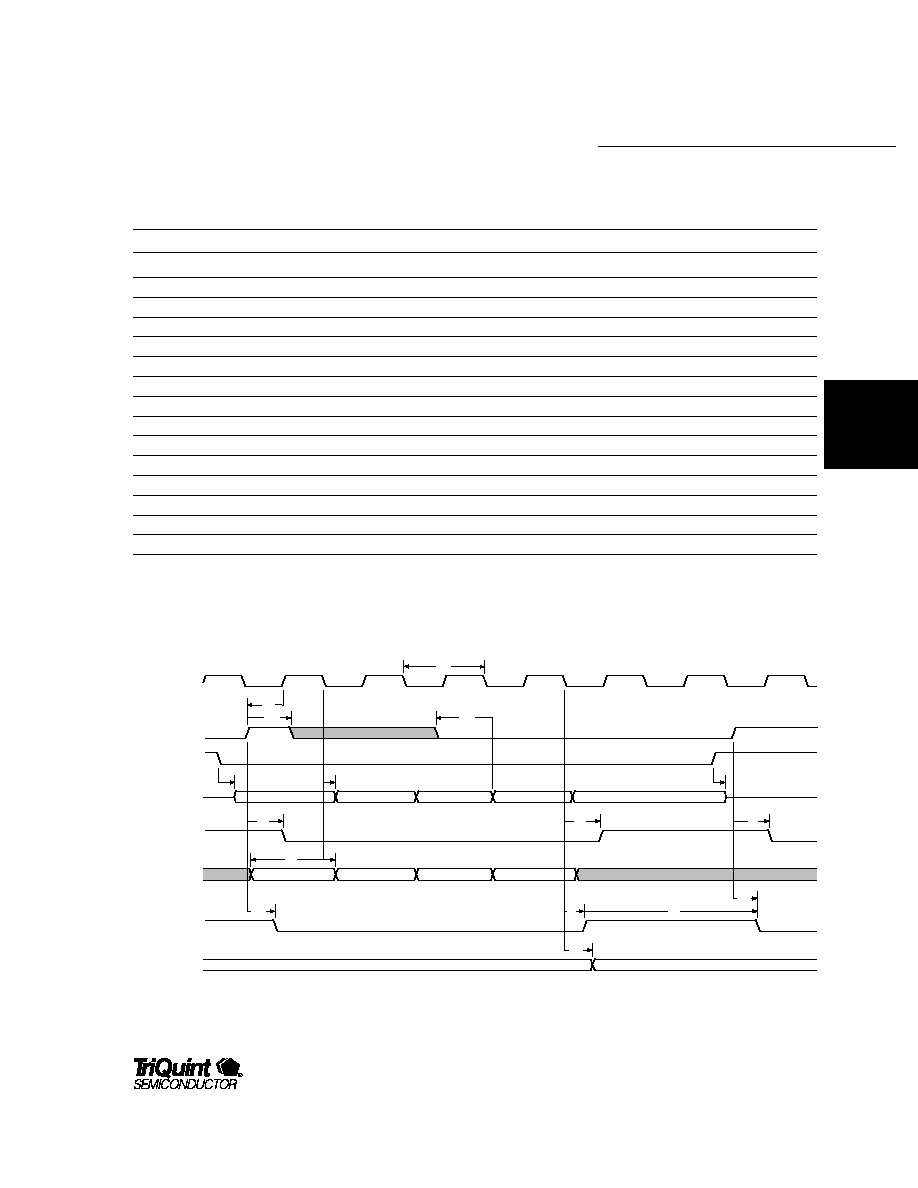

Table 7. TQ8025 Timing -- Normal Configure Mode

1

Symbol

Parameter

Min.

Max.

Units

T1

Hold LOAD low to SAD0:3, DAD0:3

2

ns

T2

Setup DAD0:3 to LOAD high

0

ns

T3

CONFIGURE pulse low time

10

ns

T4

Setup LOAD low to CONFIGURE low

3

ns

T5

CONFIGURE low to SIGNAL PATHS updated

4

ns

T6

LOAD pulse width high

TBD

ns

Notes: 1. LDMODE = 0; AUTOCONFIG = Don't Care, RESET≠ = 1, CLOCK = Don't Care.

Figure 1. TQ8025 Timing -- Normal Configure Mode

TQ8025

PRELIMINARY DATA SHEET

SWITCHING

PRODUCTS

5

For additional information and latest specifications, see our website: www.triquint.com

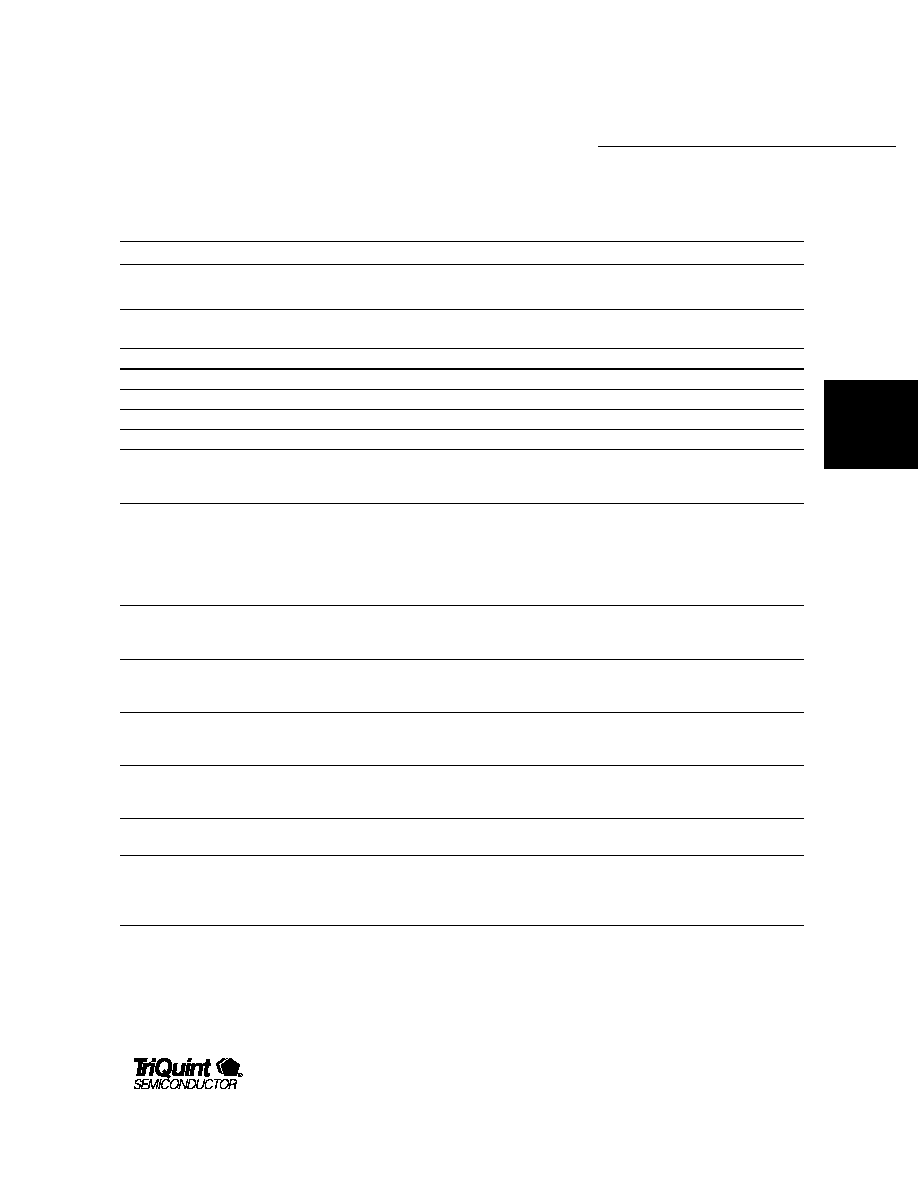

Table 8. TQ8025 Timing -- RAM Loading, Auto-Configure Mode

1

Symbol

Parameter

Min.

Max.

Units

T1

LOAD high to READY low

3

ns

T2

CLOCK low to READY high

3

ns

T3

ADDREN low to RADD enabled

3

ns

T4

Setup LOAD high to CLOCK high

4

ns

T5

CLOCK low to RADD increment

2

ns

T6

AD0:15 setup before CLOCK low

0

ns

T7

AD0:15 hold time after CLOCK low

2

ns

T8

CLOCK low to INT CONFIGURE high

2

ns

T9

CONFIGURE low pulse width

10

ns

T10

ADDREN high to RADD tristate

3

ns

T11

LOAD low prior to 3rd CLOCK low

4

ns

T12

LOAD high pulse

TBD

ns

T13

CLOCK low to SIGNAL PATHS updated

4

ns

T14

CLOCK period

20

ns

T15

LOAD high to INT CONFIGURE low

TBD

ns

Notes: 1. LDMODE = 1; AUTOCONFIG = 1, RESET≠ = 1, CONFIG = 1.

Figure 2. TQ8025 Timing -- RAM Loading, Auto-Configure Mode

T14

T4

T12

T11

T3

T5

T10

T1

T2

T1

T6

T7

T15

T8

T9

T15

T13

0

1

2

3

0

D0

D1

D2

D3

OLD CONFIGURATION

NEW CONFIGURATION

CLOCK

LOAD

ADDREN

RADD0:1

READY

AD0:15

INT CONFIGURE

SIGNAL PATHS

LDMODE = 1; AUTOCONFIG = 0, RESET≠ = 1.

Note: INT CONFIGURE is an internal signal shown for clarity of operation.

TQ8025

PRELIMINARY DATA SHEET

For additional information and latest specifications, see our website: www.triquint.com

6

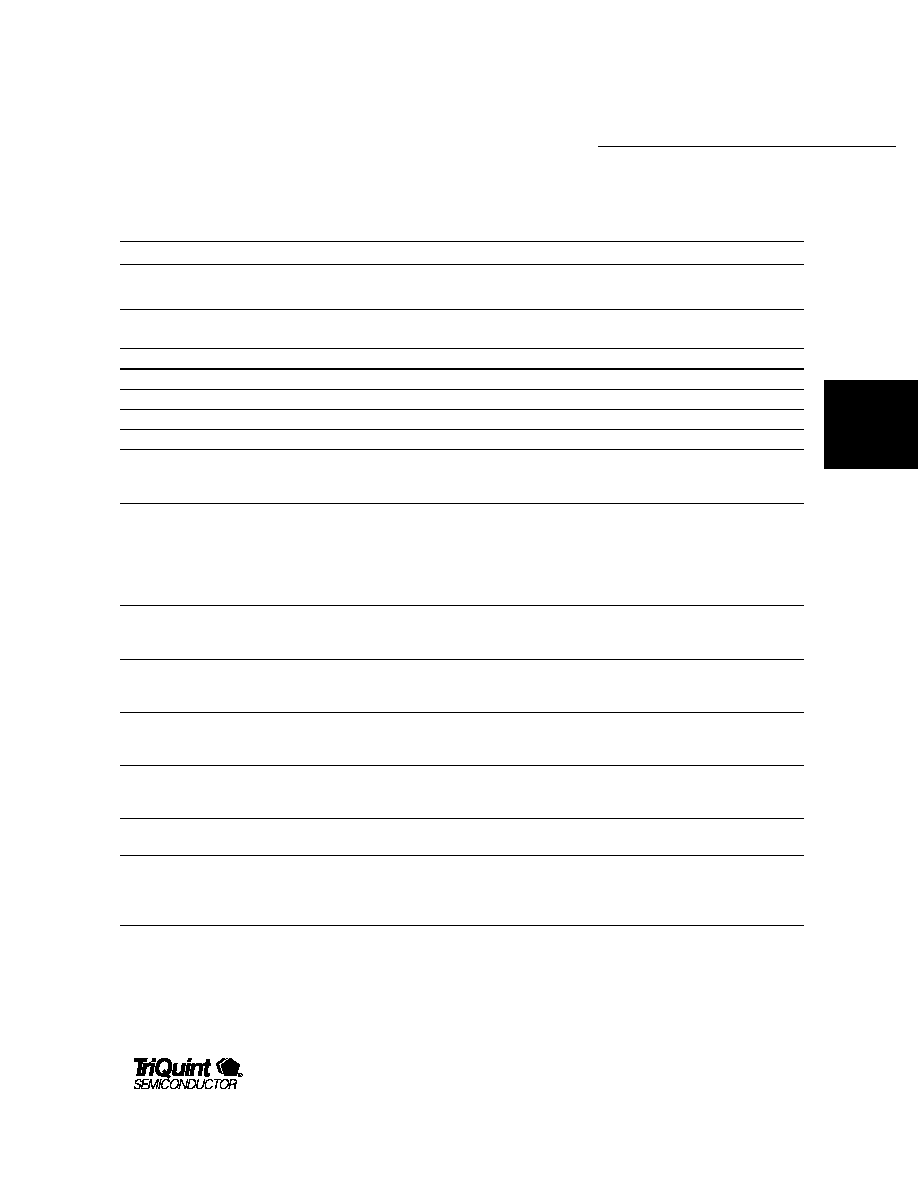

Table 9. TQ8025 Timing -- RAM Loading, External Configure Pulse Mode

1

Symbol

Parameter

Min.

Max.

Units

T1

LOAD high to READY low

3

ns

T2

CLOCK low to READY high

3

ns

T3

ADDREN low to RADD enabled

3

ns

T4

Setup LOAD high to CLOCK high

4

ns

T5

CLOCK low to RADD increment

2

ns

T6

AD0:15 setup before CLOCK low

0

ns

T7

AD0:15 hold time after CLOCK low

2

ns

T8

Setup last CLOCK before CONFIGURE low

2

ns

T9

CONFIGURE low pulse width

10

ns

T10

ADDREN high to RADD tristate

3

ns

T11

LOAD low prior to 3rd CLOCK low

4

ns

T12

LOAD high pulse

TBD

ns

T13

CONFIGURE low to READY low

TBD

ns

T14

CONFIGURE low to SIGNAL PATHS updated

4

ns

T15

CLOCK period

20

ns

Notes: 1. LDMODE = 1; AUTOCONFIG = 0, RESET≠ = 1.

Figure 3. TQ8025 Timing -- RAM Loading, External Configure Pulse Mode

T15

T4

T12

T11

T3

T5

T10

T1

T2

T13

T6

T7

T8

T9

T14

0

1

2

3

0

D0

D1

D2

D3

OLD CONFIGURATION

NEW CONFIGURATION

CLOCK

LOAD

ADDREN

RADD0:1

READY

AD0:15

CONFIGURE

SIGNAL PATHS

LDMODE = 1; AUTOCONFIG = 1, RESET≠ = 1, CONFIG = 1.

TQ8025

PRELIMINARY DATA SHEET

SWITCHING

PRODUCTS

7

For additional information and latest specifications, see our website: www.triquint.com

Typical Performance

Data Rate: 2.5Gb/s

Data Pattern: 2^7 PRBS

Rise and Fall

Data Rate: 2.5Gb/s

Rise Time: 115ps

Fall Time: 109ps

Note:

Measured jitter is 68ps pk-pk.

Signal source jitter is 32ps pk-pk.

TQ8025

PRELIMINARY DATA SHEET

For additional information and latest specifications, see our website: www.triquint.com

8

32 31 30 29 2827 26 25 24 23 22 21 20 19 18 17 16 15 14 1312 11 10 9 8 7 6 5 4 3 2 1

67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 8788 89 90 91 9293 94 95 9697 98 99

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

Vcc Vcc N.C. N.C. V

TT

V

TT

Vcc DI08P DI08N DI09P DI09N Vcc DI10P DI10N DI11P DI11N Vcc DI12P DI12N DI13P DI13N Vcc DI14P DI14N DI15P DI15N Vcc DO15N DO15P DO14N DO14P Vcc GND

Vcc

DO12N

DO12P

Vcc

DO11N

DO11P

DO10N

DO10P

DO09N

DO09P

DO08N

DO08P

Vcc

DO07N

DO07P

Vcc

DO06N

DO06P

Vcc

DO05N

DO05P

DO04N

DO04P

Vcc

DO03N

DO03P

DO02N

DO02P

Vcc

GND

GND

Vcc

AD15

AD14

AD13

AD12

Vcc

AD10

AD09

AD08

Vcc

AD07/DAD3

AD06/DAD2

AD05/DAD1

AD04/DAD0

Vcc

AD03/SAD3

AD02/SAD2

AD01/SAD1

AD00/SAD0

Vcc

RADD0

RADD1

LOAD

RESET-

Vcc

AUTOCONFIG

CLOCK

CONFIG

READY-

Vcc

Vcc

AD11

GND Vcc

LDMODE ADDREN

V

TT

V

TT

Vcc

DI00P

DI00N DI01P DI01N

Vcc

DI02P DI02N DI03P DI03N

Vcc

DI04P DI04N DI05P DI05N

Vcc

DI06P DI06N DI07P DI07N

Vcc

DO00P DO00N DO01P DO01N

Vcc Vcc

33

TQ8025

132-pin Heat Spreader

Cavity Down

Top View

DO13N

DO13P

Vcc

Figure 4. TQ8025 pinout -- top view

TQ8025

PRELIMINARY DATA SHEET

SWITCHING

PRODUCTS

9

For additional information and latest specifications, see our website: www.triquint.com

Signal

Name/Level

Description

DI00P-DI15P

Data input true and complement

Differential data input ports. VH = 0 V, VL = ≠300 mV max.

DI0N-DI15N

Differential CML/PECL input

Internal 50-ohm terminations to VTT (CML = 0 V;ECL = ≠2.0 V).

DO0P-DO15P,

Data output true and complement

Differential data output ports. 600 mV min. differential swing.

DO0N-DO15N

Differential CML/PECL output

AD00:15

Input address; TTL input

Serial input address, LSB first in time; ADn programs output port n.

RADD0:1

RAM address; TTL output, tristate

Used to generate address 0-3 during configure load from RAM.

ADDREN

Enable RADD0:2; TTL input

When low, enables RADD0:1; when high, forces RADD0:1 tristate.

CLOCK

Clock; TTL input

Controls cycle time of address generator and AUTOCONFIG.

AUTOCONFIG

Configure mode; TTL input

When high, internal CONFIGURE is automatically generated.

READY

READY; open-drain output

Indicates end of AUTOCONFIG or end of address LOAD cycle

when high. Reset low by RESET-, CONFIG low, or LOAD rising.

Requires external pullup to V

CC

.

LOAD

LOAD; TTL input

For LDMODE=1, ADDREN=0: AUTOCONFIG=0, rising LOAD causes

ADDR0:1 to generate RAM addresses, then READY is asserted

after four clock ticks. For AUTOCONFIG=1, LOAD rising causes

ADDR0:1 to generate addresses, causing an internal CONFIG

to be generated, after which READY is asserted. For LDMODE=0,

see SAD0:3 and DAD0:3.

CONFIGURE

CONFIGURE; TTL input

Used to load address contents of internal address registers.

Active LOW. Crosspoint will be configured within 4 ns

(objective) of CONFIG falling low.

LDMODE

Load Mode; TTL input

When floated high, AD0-15 are used for configuration.

When tied low, SAD0-3 and DAD0-3 are used for configuration.

When AUTOCONFIG is disabled, and AD08-15 are ignored.

SAD0:3

Source Address; TTL inputs

When LDMODE is low, specifies input address to be connected

to output port specified by DAD0:3. Latched by falling LOAD

(LDMODE=0).

DAD0:3

Destination Address; TTL input

When LDMODE is low, specifies output address to be connected

to input port specified by SAD0:3. Latched by falling LOAD

(LDMODE=0).

VCC, GND, VTT

+5V, Ground;

Power and ground pins.

Termination Voltage

V

TT

= GND for CML inputs; V

TT

= V

CC

≠ 2V for PECL inputs.

RESET≠

Reset; TTL Input

While low, programs all output ports to connect to input port 0.

Strobing CONFIG after reset restores user port programming

if device power was stable since last user programming and

during RESET≠. Active low, Schmitt triggered.

Table 10. TQ8025 Pin Descriptions

TQ8025

PRELIMINARY DATA SHEET

For additional information and latest specifications, see our website: www.triquint.com

10

Ordering Information

TQ8025

2.5 Gb/s 16x16 Crosspoint Switch

Additional Information

For latest specifications, additional product information,

worldwide sales and distribution locations, and information about TriQuint:

Web: www.triquint.com

Tel: (503) 615-9000

Email: sales@tqs.com

Fax: (503) 615-8900

For technical questions and additional information on specific applications:

Email: applications@tqs.com

The information provided herein is believed to be reliable; TriQuint assumes no liability for inaccuracies or

ommisions. TriQuint assumes no responsibility for the use of this information, and all such information

shall be entirely at the user's own risk. Prices and specifications are subject to change without notice.

No patent rights or licenses to any of the circuits described herein are implied or granted to any third party.

TriQuint does not authorize or warrant any TriQuint product for use in life-support devices and/or systems.

Copyright © 1998 TriQuint Semiconductor, Inc. All rights reserved.

Revision 0.3.A

August 1998

Figure 5. Mechanical Dimensions

.010 +.0015

BSC

1.170 +.006

PIN 1

INDEX

.950 +.006

.800

132

1

A

A

.025

0.325

±

.005

1. Part is symmetrical about the center axes.

2. Centerline bisects center pin in both directions.

3. See pad detail below.

0.015

0.010

0.105

0.525

0.025

centers

C

L

C

L

PAD LAYOUT DETAIL

Top view

Bottom view

Section A-A

CERAMIC OR

METAL LID

CHIP CAPACITOR, 4 PLACES

DEVICE

.125

SEATING PLANE

.064

.060

HEAT SPREADER