# **Contents**

| Features                                    | 1  |

|---------------------------------------------|----|

| Block Diagram                               | 2  |

| Pin Description                             | 3  |

| Pad Assignment                              | 5  |

| Pad Coordinates                             | 6  |

| Function Explanation                        | 7  |

| Instruction Explanation                     | 17 |

| Instruction List                            | 27 |

| Operation Description                       | 29 |

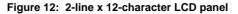

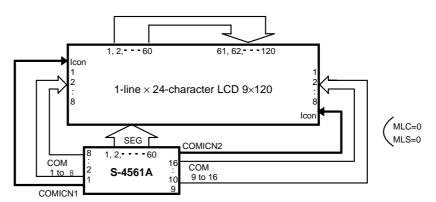

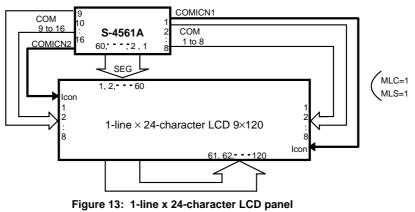

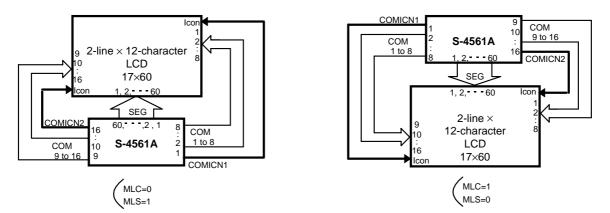

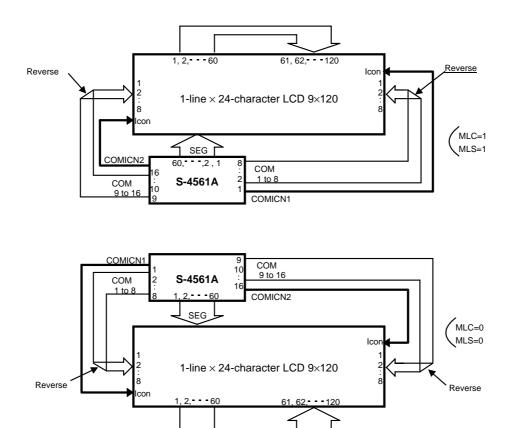

| Examples of Connection to LCD Panel         | 35 |

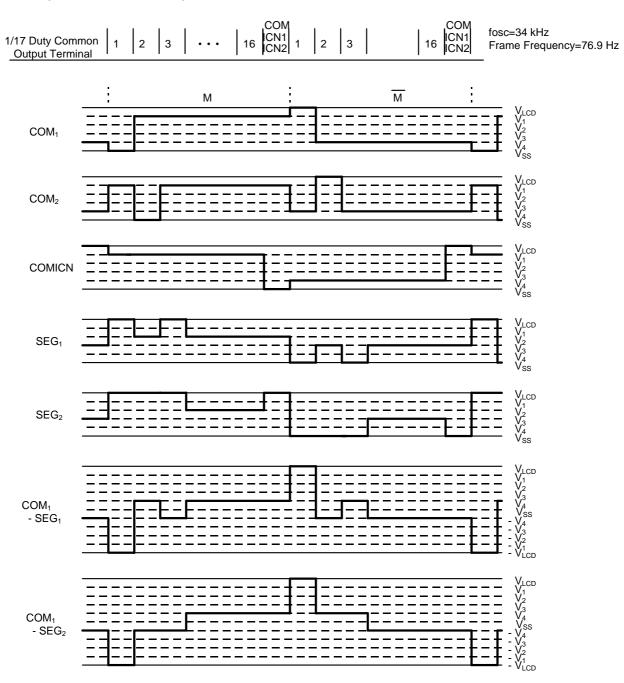

| Examples of LCD Drive Output Waveform       | 37 |

| External BiasResistor vs LCD Drive Waveform | 38 |

| Absolute Maximum Ratings                    | 39 |

| DC Characteristics                          | 39 |

| Current Consumption Measurement Examples    | 43 |

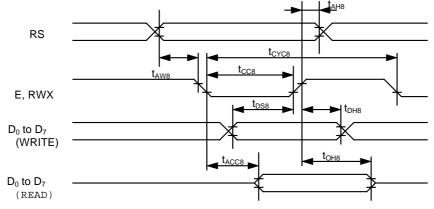

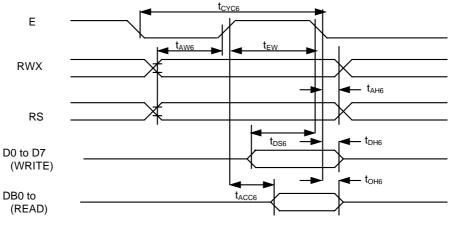

| Timing Characteristics                      | 44 |

| Examples Application Circuit                | 47 |

# **LCD Controller-Driver**

# S-4561A

The S-4561A is a 17-common x 60-segment output character LCD controller-driver with built-in serial and parallel interfaces. The S-4561A incorporates CGROM, making character display possible. Independently of the CPU, display on the LCD panel is executed via the internal oscillating circuit or clock input. The S-4561A has a wide variety of command instructions which minimize the load of the CPU. It also features a wide voltage range, low power consumption, and it is provided with a power save function, making the S-4561A a suitable display device for applications in portable electronics.

# Features

- Display Area

- 5-dot font

- 12-column x 2-line (+4 columns)

- 24-column x 1-line (+8 columns)

6-dot font

- 10-column x 2-line (+6 columns)

- 20-column x 1-line (+12 columns)

- Values in parentheses indicate the number of columns outside the display area.

- Icon Display

- 60 icons (max.)

- Icons can be displayed on the upper and lower panel.

- Fonts: 5-dot display mode and 6-dot display mode

- Interface

- 4-bit, 8-bit high-speed parallel interface (80-/68-Family CPU) Serial interface

- Driver Output

- 60 segments

- 16 commons+ Icon common :

- Character Generator ROM (CGROM)

- 9600 bits, 5×8 bits character font, 240 characters

- Character Generator RAM (CGRAM)

- 8 character x 5 x 8=320 bits

- Display Data RAM (DDRAM)

- 2 lines x 16 characters=2 x 16 x 8=256 bits

- (4 characters are displayed outside the display area)

- Display Clock

- Either internal CR oscillating circuit or external clock input : CR oscillation: 34 kHz

- (Frame Frequency=76.9 Hz)

- Duty Cycle: 1/17

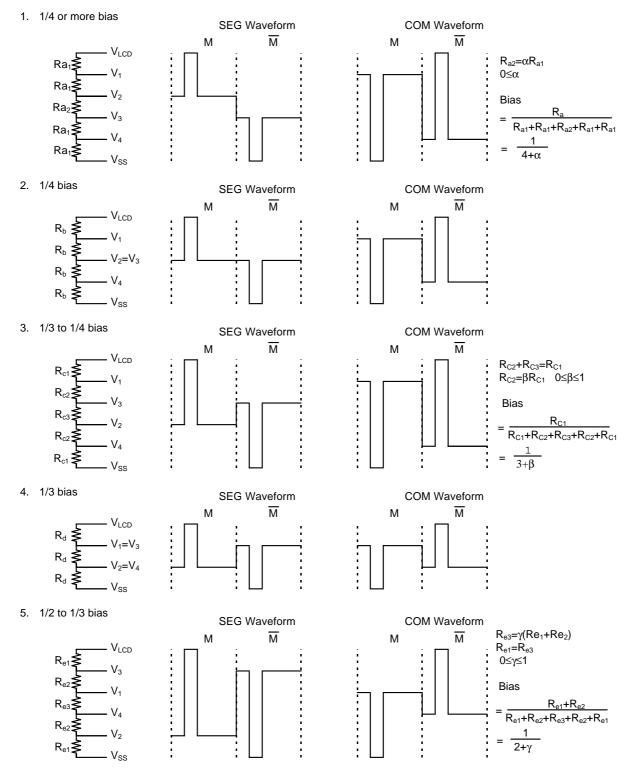

- Internal LCD Drive Bias Voltage Generator

Internal Bias Resistor :

Command selection 1/5 or 1/4 bias External Bias Resistor :

Free setting of 1/2 bias or more

Normal Instructions

Display Clear, Cursor Home, Display ON/OFF, Display Character Blink, Cursor Shift, Display Shift, Cursor ON/OFF

- Extended Instructions

- Contrast Adjustment, Smooth Scroll Control, Icon Control, Icon Blink, Bias Resistor Select, Change of Number of Display Columns, Power Save, Icon Only Display, Booster Drive Frequency Select

- Reset Circuit : Hardware Reset

- Internal Booster : Dual Booster

- Power Supply Voltage Range

- Logic Power: 2.4 V to 5.5 V

- LCD Drive Power: 2.7 V to 6.5 V

Low Current Consumption : Approx. 0 µA (during power save operation)

- Delivered on gold bump bare chips,

- Notice that isolation of the IC from light exposure is not taken into account for this IC design.

Be sure to take measures not to expose light to the surface, back, or side of the IC in order to prevent this IC from malfunctioning.

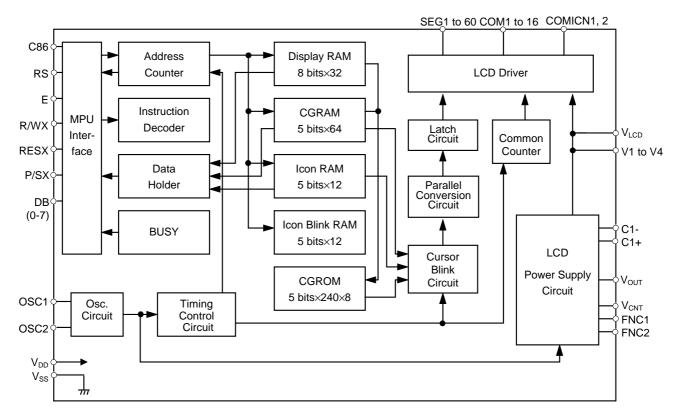

# Block Diagram

1. Block Overview

Figure 1 Block Diagram

- V<sub>OUT</sub>  $V_{\text{CNT}}$ С  $\mathsf{V}_{\mathsf{D}\mathsf{D}}$ Ô  $V_{LCD}$ C1+ LCD Bias  $V_1$ Voltage Regulator/ Resistor/ C1- $V_2$ Booster LCD Voltage Voltage Follower  $V_3$ Command ጎ  $V_4$ Standard Voltage Circuit FNC1 FNC2  $V_{\text{SS}}$ CR Oscillating MPU Interface Circuit OSC1 OSC2

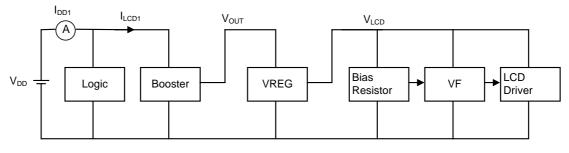

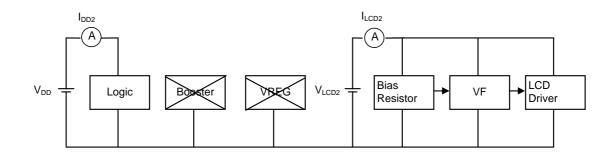

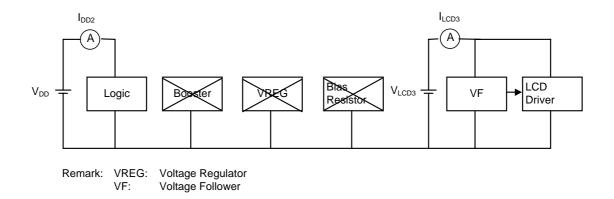

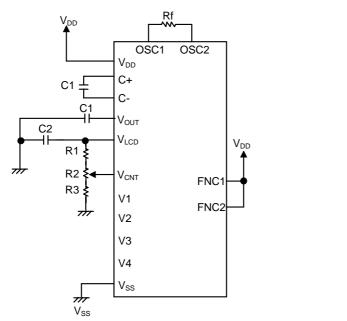

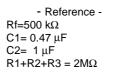

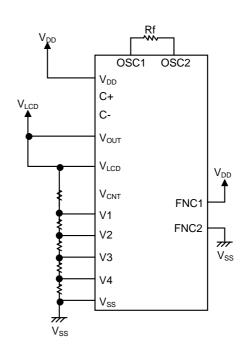

- 2. LCD Power Supply Circuit

Figure 2 LCD Power Supply Circuit

Seiko Instruments Inc.

# Pin Description

1. Logic Power Supply Pins

| Table 1 Logic Power Supply Pins |                 |                                                    |  |  |  |

|---------------------------------|-----------------|----------------------------------------------------|--|--|--|

| Pin No.                         | Pin Name        | Description                                        |  |  |  |

| 47                              | V <sub>SS</sub> | Negative Power Pin: Usually connected to 0 V (GND) |  |  |  |

| 33                              | V <sub>DD</sub> | Positive Power Pin: Usually connected to+3 V       |  |  |  |

# 2. Control Pins

|                                    | Table 2 Control Pins |                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin No.                            | Pin Name             | Description                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 7, 9<br>11, 13<br>15, 17<br>19, 21 | DB0 to DB7           | <ul> <li>When an 8-bit parallel interface is selected:<br/>8-Bit Parallel Data Bus 3-State Input/Output Pin</li> <li>When a 4-bit parallel interface is selected:<br/>DB0 to DB3 : Open<br/>DB4 to DB7 : 4-Bit Parallel Data Bus 3-State Input/Output Pins</li> <li>When a serial interface is selected:<br/>DB0 : Serial Data Input Pin<br/>DB1 : Clock Input Pin<br/>DB2 to DB7 : Open</li> </ul> |  |  |  |  |

| 25                                 | R/WX                 | <ul> <li>When a 4-bit/8-bit parallel interface is selected:<br/>68-Family MPU Read/Write Signal Input Pin<br/>R/WX="H": Read<br/>R/WX="L": Write<br/>80-Family MPU: Write Signal Input Pin<br/>Active "L" Data Bus Input State</li> <li>When a serial interface is selected:<br/>High Impedance</li> </ul>                                                                                          |  |  |  |  |

| 27                                 | P/SX                 | Parallel/Serial Interface Changeover Pin<br>P/SX="H" : 4-Bit/8-Bit Parallel Interface<br>P/SX="L" : Serial Interface                                                                                                                                                                                                                                                                                |  |  |  |  |

| 29                                 | RS                   | <ul> <li>When 4-bit/8-bit parallel interface is selected:<br/>Register Select Signal Input Pin<br/>RS="0" : Instruction Register Write<br/>Each Address Counter Read<br/>BUSY Flag Read</li> <li>RS="1" : Data Register Write/Read</li> <li>When a serial interface is selected:<br/>RS="0" : Instruction Register Write<br/>RS="1" : Data Register Write</li> </ul>                                |  |  |  |  |

| 31                                 | E                    | <ul> <li>When a 4-bit/8-it parallel interface is selected:<br/>68-Family MPU Enable Clock Signal Input Pin<br/>Active "H"<br/>80-Family MPU Read Signal Input Pin<br/>Active "L" Data Bus Output State</li> <li>When a serial interface is selected:<br/>Chip-Select Input Pin<br/>E= "L": Active</li> </ul>                                                                                        |  |  |  |  |

| 23                                 | RESX                 | Reset Input Pin     Active "L"     Internal Pullup Register                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 39                                 | C86                  | <ul> <li>When 4-bit/8-bit parallel interface is selected:<br/>C86="H"</li></ul>                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

# 3. CR Oscillating Circuit Input/Output Pins

|         | Table 3 CR Oscillating Circuit Input/Output Pins |                                                                                                                     |  |  |  |  |  |

|---------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin No. | Pin Name                                         | Description                                                                                                         |  |  |  |  |  |

| 5       | OSC2                                             | CR Oscillating Circuit Output Pin: Connects oscillating resistor Rf; while an external clock is being used, "Open." |  |  |  |  |  |

| 3       | OSC1                                             | CR Oscillating Circuit Input Pin: Connects oscillating resistor Rf; An external clock can be input.                 |  |  |  |  |  |

# 4. LCD Drive Voltage Pins

| Table 4 | LCD | Drive | Voltage | Pins |

|---------|-----|-------|---------|------|

|---------|-----|-------|---------|------|

| Pin No. | Pin Name         | Description                                                                                                                                                                                                                      |  |  |  |  |  |

|---------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 35      | FNC2             | LCD Power Circuit Operation Control Pin 2                                                                                                                                                                                        |  |  |  |  |  |

| 37      | FNC1             | LCD Power Circuit Operation Control Pin 1                                                                                                                                                                                        |  |  |  |  |  |

| 49      | VOUT             | Booster Drive Voltage Output Pin                                                                                                                                                                                                 |  |  |  |  |  |

| 51      | C1-              | 1st Boosting Negative Side Connection Pin                                                                                                                                                                                        |  |  |  |  |  |

| 53      | C1+              | 1st Boosting Positive Side Connection Pin                                                                                                                                                                                        |  |  |  |  |  |

| 59      | VCNT             | LCD Power Supply Voltage Control Pin                                                                                                                                                                                             |  |  |  |  |  |

| 65      | V <sub>LCD</sub> | LCD Drive Voltage Input/Output Pin                                                                                                                                                                                               |  |  |  |  |  |

| 67      | V1               | LCD Drive Bias Voltage Pin<br>While an internal LCD power supply circuit is being used, outputs the LCD<br>drive bias voltage.                                                                                                   |  |  |  |  |  |

| 69      | V2               | $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                           |  |  |  |  |  |

| 71      | V3               | $\begin{array}{ccc} V3 & 2/4 \times V_{LCD} & 2/5 \times V_{LCD} \\ V4 & 1/4 \times V_{LCD} & 1/5 \times V_{LCD} \\ While an external LCD power supply circuit is being used, inputs the LCD drive bias voltage. \\ \end{array}$ |  |  |  |  |  |

| 73      | V4               | $V_{LCD} \ge V1$ , V2, V3, V4 $\ge VSS$<br>$V_{LCD} \ge V_{DD}$                                                                                                                                                                  |  |  |  |  |  |

# 5. Driver Output Pins

# Table 5 Driver Output Pins

| Pin No.                | Pin Name            | Description                                   |

|------------------------|---------------------|-----------------------------------------------|

| 91 to 150              | SEG1<br>to<br>SEG60 | Segment Drive Output Pins                     |

| 76 to 83<br>159 to 166 | COM1 to<br>COM16    | Common Drive Output Pins                      |

| 75                     | COMICN1             | Common Drive Output Pins for Icon             |

| 158                    | COMICN2             | COMICN1 and 2 output the same phase waveform. |

## 6. Other Pins

# Table 6 Logic Power Supply Pins

| Pin No. | Pin Name | Description                                       |  |  |  |

|---------|----------|---------------------------------------------------|--|--|--|

| —       | Dummy    | Dummy Pin<br>Insulated from the inside of the IC. |  |  |  |

| 45      | TEST0    | Pins for IC delivery inspection:                  |  |  |  |

| 43      | TEST1    | Cannot be wired to the outside.                   |  |  |  |

| 41      | TEST2    | When in actual use, "Open."                       |  |  |  |

| 57      | TEST3    |                                                   |  |  |  |

| 63      | TEST4    |                                                   |  |  |  |

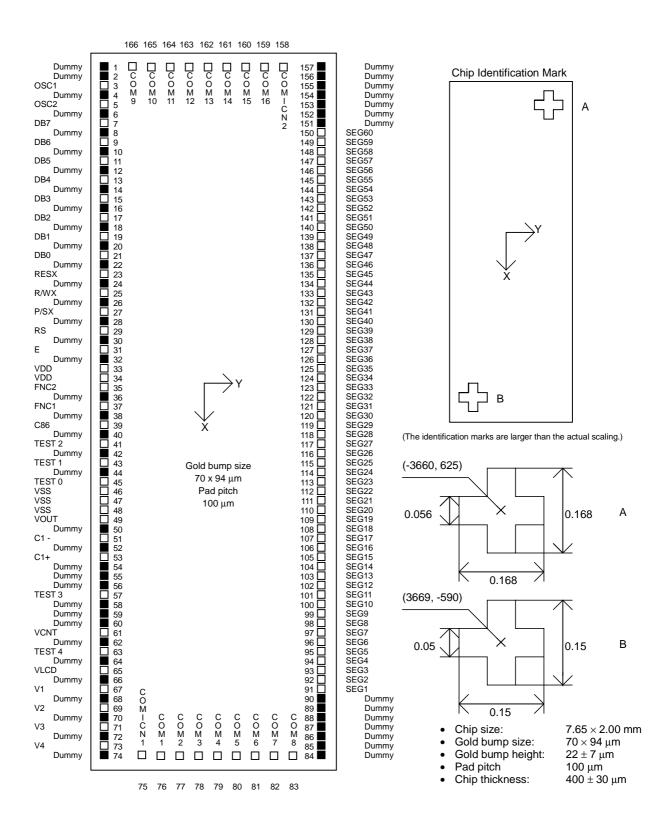

# Pad Assignment

# Pad Coordinates

| No. | Symbol | Х       | Y      | No. | Symbol  | Х      | Y      | No. | Symbol  | Х       | Y     |

|-----|--------|---------|--------|-----|---------|--------|--------|-----|---------|---------|-------|

| 1   | Dummy  | -3700.5 | -863.5 | 57  | TEST3   | 1950   | -863.5 | 113 | SEG23   | 750     | 863.5 |

| 2   | Dummy  | -3550   | -863.5 | 58  | Dummy   | 2050   | -863.5 | 114 | SEG24   | 650     | 863.5 |

| 3   | OSC1   | -3450   | -863.5 | 59  | Dummy   | 2150   | -863.5 | 115 | SEG25   | 550     | 863.5 |

| 4   | Dummy  | -3350   | -863.5 | 60  | Dummy   | 2250   | -863.5 | 116 | SEG26   | 450     | 863.5 |

| 5   | OSC2   | -3250   | -863.5 | 61  | VCNT    | 2350   | -863.5 | 117 | SEG27   | 350     | 863.5 |

| 6   | Dummy  | -3150   | -863.5 | 62  | Dummy   | 2450   | -863.5 | 118 | SEG28   | 250     | 863.5 |

| 7   | DB7    | -3050   | -863.5 | 63  | TEST4   | 2550   | -863.5 | 119 | SEG29   | 150     | 863.5 |

| 8   | Dummy  | -2950   | -863.5 | 64  | Dummy   | 2650   | -863.5 | 120 | SEG30   | 50      | 863.5 |

| 9   | DB6    | -2850   | -863.5 | 65  | VLCD    | 2750   | -863.5 | 121 | SEG31   | -50     | 863.5 |

| 10  | Dummy  | -2750   | -863.5 | 66  | Dummy   | 2850   | -863.5 | 122 | SEG32   | -150    | 863.5 |

| 11  | DB5    | -2650   | -863.5 | 67  | V1      | 2950   | -863.5 | 123 | SEG33   | -250    | 863.5 |

| 12  | Dummy  | -2550   | -863.5 | 68  | Dummy   | 3050   | -863.5 | 124 | SEG34   | -350    | 863.5 |

| 13  | DB4    | -2450   | -863.5 | 69  | V2      | 3150   | -863.5 | 125 | SEG35   | -450    | 863.5 |

| 14  | Dummy  | -2350   | -863.5 | 70  | Dummy   | 3250   | -863.5 | 126 | SEG36   | -550    | 863.5 |

| 15  | DB3    | -2250   | -863.5 | 71  | V3      | 3350   | -863.5 | 127 | SEG37   | -650    | 863.5 |

| 16  | Dummy  | -2150   | -863.5 | 72  | Dummy   | 3450   | -863.5 | 128 | SEG38   | -750    | 863.5 |

| 17  | DB2    | -2050   | -863.5 | 73  | V4      | 3550   | -863.5 | 129 | SEG39   | -850    | 863.5 |

| 18  | Dummy  | -1950   | -863.5 | 74  | Dummy   | 3700.5 | -863.5 | 130 | SEG40   | -950    | 863.5 |

| 19  | DB1    | -1850   | -863.5 | 75  | COMICN1 | 3688.5 | -400   | 131 | SEG41   | -1050   | 863.5 |

| 20  | Dummy  | -1750   | -863.5 | 76  | COM1    | 3688.5 | -300   | 132 | SEG42   | -1150   | 863.5 |

| 21  | DB0    | -1650   | -863.5 | 77  | COM2    | 3688.5 | -200   | 133 | SEG43   | -1250   | 863.5 |

| 22  | Dummy  | -1550   | -863.5 | 78  | COM3    | 3688.5 | -100   | 134 | SEG44   | -1350   | 863.5 |

| 23  | RESX   | -1450   | -863.5 | 79  | COM4    | 3688.5 | 0      | 135 | SEG45   | -1450   | 863.5 |

| 24  | Dummy  | -1350   | -863.5 | 80  | COM5    | 3688.5 | 100    | 136 | SEG46   | -1550   | 863.5 |

| 25  | R/WX   | -1250   | -863.5 | 81  | COM6    | 3688.5 | 200    | 137 | SEG47   | -1650   | 863.5 |

| 26  | Dummy  | -1150   | -863.5 | 82  | COM7    | 3688.5 | 300    | 138 | SEG48   | -1750   | 863.5 |

| 27  | P/SX   | -1050   | -863.5 | 83  | COM8    | 3688.5 | 400    | 139 | SEG49   | -1850   | 863.5 |

| 28  | Dummy  | -950    | -863.5 | 84  | Dummy   | 3700.5 | 863.5  | 140 | SEG50   | -1950   | 863.5 |

| 29  | RS     | -850    | -863.5 | 85  | Dummy   | 3550   | 863.5  | 141 | SEG51   | -2050   | 863.5 |

| 30  | Dummy  | -750    | -863.5 | 86  | Dummy   | 3450   | 863.5  | 142 | SEG52   | -2150   | 863.5 |

| 31  | E      | -650    | -863.5 | 87  | Dummy   | 3350   | 863.5  | 143 | SEG53   | -2250   | 863.5 |

| 32  | Dummy  | -550    | -863.5 | 88  | Dummy   | 3250   | 863.5  | 144 | SEG54   | -2350   | 863.5 |

| 33  | VDD    | -450    | -863.5 | 89  | Dummy   | 3150   | 863.5  | 145 | SEG55   | -2450   | 863.5 |

| 34  | VDD    | -350    | -863.5 | 90  | Dummy   | 3050   | 863.5  | 146 | SEG56   | -2550   | 863.5 |

| 35  | FNC2   | -250    | -863.5 | 91  | SEG1    | 2950   | 863.5  | 147 | SEG57   | -2650   | 863.5 |

| 36  | Dummy  | -150    | -863.5 | 92  | SEG2    | 2850   | 863.5  | 148 | SEG58   | -2750   | 863.5 |

| 37  | FNC1   | -50     | -863.5 | 93  | SEG3    | 2750   | 863.5  | 149 | SEG59   | -2850   | 863.5 |

| 38  | Dummy  | 50      | -863.5 | 94  | SEG4    | 2650   | 863.5  | 150 | SEG60   | -2950   | 863.5 |

| 39  | C86    | 150     | -863.5 | 95  | SEG5    | 2550   | 863.5  | 151 | Dummy   | -3050   | 863.5 |

| 40  | Dummy  | 250     | -863.5 | 96  | SEG6    | 2450   | 863.5  | 152 | Dummy   | -3150   | 863.5 |

| 41  | TEST2  | 350     | -863.5 | 97  | SEG7    | 2350   | 863.5  | 153 | Dummy   | -3250   | 863.5 |

| 42  | Dummy  | 450     | -863.5 | 98  | SEG8    | 2250   | 863.5  | 154 | Dummy   | -3350   | 863.5 |

| 43  | TEST1  | 550     | -863.5 | 99  | SEG9    | 2150   | 863.5  | 155 | Dummy   | -3450   | 863.5 |

| 44  | Dummy  | 650     | -863.5 | 100 | SEG10   | 2050   | 863.5  | 156 | Dummy   | -3550   | 863.5 |

| 45  | TEST0  | 750     | -863.5 | 101 | SEG11   | 1950   | 863.5  | 157 | Dummy   | -3700.5 | 863.5 |

| 46  | VSS    | 850     | -863.5 | 102 | SEG12   | 1850   | 863.5  | 158 | COMICN2 | -3688.5 | 400   |

| 47  | VSS    | 950     | -863.5 | 103 | SEG13   | 1750   | 863.5  | 159 | COM16   | -3688.5 | 300   |

| 48  | VSS    | 1050    | -863.5 | 104 | SEG14   | 1650   | 863.5  | 160 | COM15   | -3688.5 | 200   |

| 49  | VOUT   | 1150    | -863.5 | 105 | SEG15   | 1550   | 863.5  | 161 | COM14   | -3688.5 | 100   |

| 50  | Dummy  | 1250    | -863.5 | 106 | SEG16   | 1450   | 863.5  | 162 | COM13   | -3688.5 | 0     |

| 51  | C1-    | 1350    | -863.5 | 107 | SEG17   | 1350   | 863.5  | 163 | COM12   | -3688.5 | -100  |

| 52  | Dummy  | 1450    | -863.5 | 108 | SEG18   | 1250   | 863.5  | 164 | COM11   | -3688.5 | -200  |

| 53  | C1+    | 1550    | -863.5 | 109 | SEG19   | 1150   | 863.5  | 165 | COM10   | -3688.5 | -300  |

| 54  | Dummy  | 1650    | -863.5 | 110 | SEG20   | 1050   | 863.5  | 166 | COM9    | -3688.5 | -400  |

| 55  | Dummy  | 1750    | -863.5 | 111 | SEG21   | 950    | 863.5  |     |         |         |       |

| 56  | Dummy  | 1850    | -863.5 | 112 | SEG22   | 850    | 863.5  |     |         |         |       |

|                     | Tuble of only identification mark ocordinates |               |  |  |  |  |  |

|---------------------|-----------------------------------------------|---------------|--|--|--|--|--|

| Chip Identification | X-Coordinates                                 | Y-Coordinates |  |  |  |  |  |

| Mark                |                                               |               |  |  |  |  |  |

| А                   | - 3660                                        | 625           |  |  |  |  |  |

| В                   | 3669                                          | - 590         |  |  |  |  |  |

# Table 8 Chip Identification Mark Coordinates

# ■ Function Explanation

#### 1. Interface

Serial and parallel interfaces are built in. Either one can be selected by changing over the P/SX terminal. The parallel interface can respond to both 4- and 8-bit parallel data transmission. Namely, data is transmitted once in the 8-bit interface or twice in the 4-bit interface. The CPU interfaces with respective instruction codes and several kinds of data via the instruction decoder and the data holder.

Data is read from each memory via the data holder. Through the ADDRESS SETTING Command, the contents of the memory are read once into the data holder, and are output through the next READ command. Then, the next data is read into the data holder.

Parallel and serial interfaces execute and finish all instructions within the Enable or Clock cycle specified in accordance with timing characteristics. Because the "BUSY" state is cleared within the cycle time, instructions can be executed in succession without confirming the "BUSY."

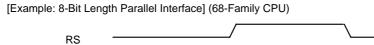

#### **1.1 Parallel Interface**

The parallel interface is engaged when the P/SX terminal is "H." Connect and fix the P/SX terminal to VDD.

| Pin Name | C86=0: 80-Family MPU | C86=1: 68-Family MPU |

|----------|----------------------|----------------------|

| RS       | RS                   | RS                   |

| E        | RD                   | E                    |

| R/WX     | WR                   | R/WX                 |

| DB(7:0)  | DB(7:0)              | DB(7:0)              |

**Table 9 Interface**

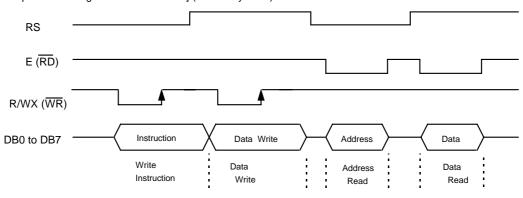

Figure 3 8-Bit Length Parallel Interface (68-Family CPU)

[Example: 8-Bit Length Parallel Interface] (80-Family CPU)

Figure 4 8-Bit Length Parallel Interface (80-Family CPU) Seiko Instruments Inc.

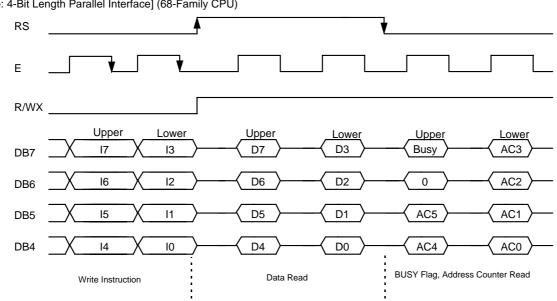

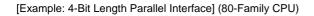

[Example: 4-Bit Length Parallel Interface] (68-Family CPU)

Figure 5 4-Bit Length Parallel Interface (68-Family CPU)

- Remarks: In case of a 4-bit length interface, data is transmitted through the four buses DB4 to DB7 (buses DB0 to DB3 are not used. Set DB0 to DB3 "Open").

- The data transmission to the CPU is completed by transmitting 4-bit data twice. The data transmission is executed in the order from upper 4 bits to lower 4 bits. The upper 4 bits of data immediately after the output level of the RS pin changes are transmitted. Leave the RS pin unchanged until lower bits finish the data transmission.

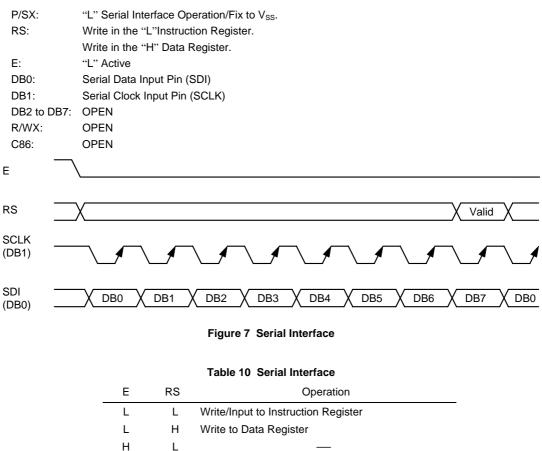

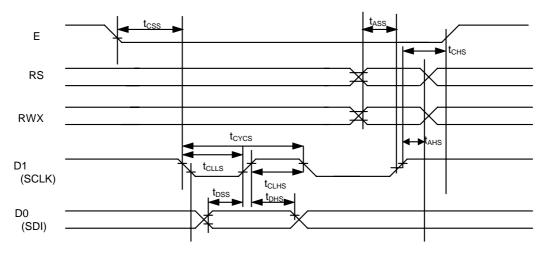

# **1.2 Serial Interface**

Serial interface is engaged when the P/SX terminal is "L." The instruction code is read at the rising edge of the serial clock (SCLK). Serial data is input in numerical order from DB0 to DB7. The instruction code is the same as that for the parallel data. Connect and fix the P/SX terminal to VSS. Connect pins DB2 through DB7, R/WX, and C86 to "OPEN."

Taking into consideration external or reflective noises, optimize the serial clock wiring. Always check operations after mounting the IC on your device.

#### 2. Busy

When the BUSY flag points "1," it shows that an instruction is being executed. The BUSY flag is read to DB7 by the ADDRESS READ command. In case of commands other than the RESET or the DISPLAY CLEAR, there is no need for confirming the BUSY flag. This is because that the instruction is completed within the cycle time specified in accordance with the timing characteristics. After confirming that BUSY flag points "0" during RESET or DISPLAY CLEAR operation or after the specified wait time, write the next command. When the BUSY flag points "1," any command other than the ADDRESS READ cannot be accepted.

When a serial interface is selected, the BUSY READ is not available.

Н

Н

# 3. Address Counter

The Address Counter (AC) gives respective addresses for DDRAM, CGRAM, ICONRAM or ICON BLINK RAM according to the contents of the AC. Only one RAM among the four kinds of RAMs is selected by the RAM ADDRESS SETTING command. After the ADDRESS SETTING command is executed, the display data can be read and written in the selected RAM. The contents of the RAM AC, where the ADDRESS READ command, is also selected are read. Increment and decrement of the AC are automatically executed after the READ or WRITE command is executed. Once an address is set, READ and WRITE commands can be input in succession.

#### 4. Display Data RAM (DDRAM)

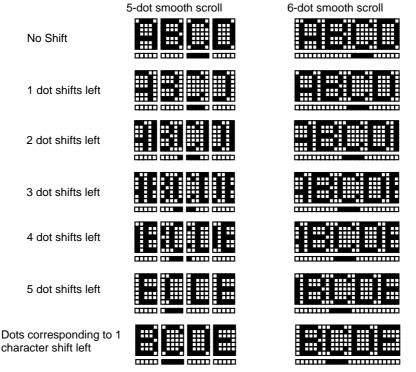

The display data RAM (DDRAM) holds the display data as an 8-bit character code. The DDRAM responds to 32 characters 00H to 1EH and has a capacity of 32×8=256 bits. When any character code is written in the DDRAM, a character which corresponds to the character code appears on the LCD panel. As the figure shows, the DDRAM is provided with a non-displayed character area as well as a normally-displayed character area. The non-displayed character area is shifted to the display area by the DISPLAY SHIFT or SMOOTH SCROLL command.

Addresses in the DDRAM are assigned to 5 bits DB0 to DB4 by the DDRAM ADDRESS SETTING command. The 8-bit character code corresponds to characters stored in the CGROM.

|                  | DB4 | DB3 | DB2 | DB1 | DB0 |

|------------------|-----|-----|-----|-----|-----|

| Address Counter  | AC4 | AC3 | AC2 | AC1 | AC0 |

| Example of (1D)H | 1   | 1   | 1   | 0   | 1   |

| Table 11 | Display | Data |

|----------|---------|------|

|----------|---------|------|

#### 5. Character Generator ROM (CGROM)

The character generator ROM (CGROM) generates 5 x 8-dot character patterns from the 8-bit character code. The CGROM holds 9600 bits which correspond to 240 character character patterns. Character codes of the Character Code List are assigned from "0001 0000" to "1111 1111."

#### 6. Character Generator RAM (CGRAM)

The character generator RAM (CGRAM) holds character patterns of 5×8 dots per character, in which users can freely write. The CGRAM holds 8 characters×5×8 dots=320 bits.

The character patterns are written for every 5 bits DB0 to DB4 by setting the address by the CGRAM ADDRESS SETTING command. The CGRAM address consists of upper 3 bits and lower 3 bits.

The written character patterns are assigned as the 8-bit character code from "0000 \*000" to "0000 \*111" (\* : don't care) of the CGRAM. The upper 3 bits of the CGRAM address corresponds to the lower 3 bits of the character code, and also corresponds to the far-left character code in the "Character Code List." The contents written in the CGRAM are displayed when the respective character codes are written in the DDRAM.

#### 7. Icon Display RAM (ICONRAM)

The icon display RAM (ICONRAM) stores data being lit on the icon display. The ICONRAM holds 60 bits corresponding to 60 marks. Data is output to SEG1 to 60 in accordance with LCD drive outputs COMICN1 and 2. To light the icon, write "1" in the ICONRAM. With data being lit on the icon display, write it using 5 bits DB0 to DB4 after executing the ICONRAM ADDRESS SETTING command. For example, to light the icon at SEG31, input icon lighting data "\*\*\*1 0000" after setting the ICONRAM address to "0110."

#### 8. Icon Display Blink RAM (ICON BLINK RAM)

The icon display blink RAM (ICON BLINK RAM) stores individual icons with respect to their necessity of blinking. The ICON BLINK RAM holds 60 bits the same as the ICON RAM, and its bit map corresponding to the segment drive output is in accordance with the ICONRAM. For example, to blink the icon corresponding to SEG31, input the icon blink data "\*\*\*1 0000" after setting the ICON BLINK RAM address to "0110." However, it is necessary to write "1" in the ICONRAM in advance.

[1-line x 24-character display]

Set to the 1-line x 24-character display mode.

| <ul> <li>Without Display Shift<br/>Display Locations<br/>1 st line</li> </ul> | COM1 to COM8                                                      | COM9 to COM16<br>13 14 15 16 17 18 19 20 21 22 23 24<br>CCDD0E 0F 10 11 12 13 14 15 16 17 | Non-Displayed Character<br>18191A1B1C1D1E1F | DDRAM<br>Address |

|-------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------|------------------|

| <ul> <li>Display Left Shift<br/>Display Locations<br/>1 st line</li> </ul>    | 1 2 3 4 5 6 7 8 9 10 11 12<br>01 02 03 04 05 06 07 08 09 0A 0B 0C | 13 14 15 16 17 18 19 20 21 22 23 24<br>0D0E0F101112131415161718                           | Non-Displayed Character                     | DDRAM<br>Address |

| <ul> <li>Display Right Shift<br/>Display Locations<br/>1 st line</li> </ul>   | 1 2 3 4 5 6 7 8 9 10 11 12<br>1F000102030405060708090A            | 13 14 15 16 17 18 19 20 21 22 23 24<br>08 0C 00 0E 0F 10 11 12 13 14 15 16                | Non-Displayed Character                     | DDRAM<br>Address |

#### Figure 8 DDRAM Addresses and Display Locations (1-line x 24-character display)

#### [2-line x 12-character display]

| <ul> <li>Without Display Shift</li> </ul>                            | COM1 to COM16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Display Locations<br>1 st line<br>2 nd line<br>• Display Left Shift  | 1         2         3         4         5         6         7         8         9         10         11         12         Non-Displayed Character           000102030405060708090A0B         0C0D0E0F         DDRAM           10         11         12         13         14         15         16         17         18         19         1A         1B         1C         1D         1E         IF         Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Display Locations<br>1 st line<br>2 nd line<br>• Display Right Shift | 1         2         3         4         5         6         7         8         9         10         11         12         Non-Displayed Character           01         02         03         04         05         06         07         08         09         0A         0B         0C         0D         0D         0D         0A         0A         0A         0B         0C         0D         0D |

| Display Locations<br>1 st line<br>2 nd line                          | 1         2         3         4         5         6         7         8         9         10         11         12         Non-Displayed Character           0F000102030405060708090A         0B0C0D0E         0B0C0D0E         DDRAM           1F101112131415161718191A         1B1C1D1E         Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Figure 9 DDRAM Addresses and Display Locations (2-line x 12-character display)

| Character Code List<br>Address | CGRAM<br>Address           | Write Character Patterns                                                                      |  |  |  |  |

|--------------------------------|----------------------------|-----------------------------------------------------------------------------------------------|--|--|--|--|

| Upper Lower                    | $A_5 A_4 A_3 A_2 A_1 A_0$  | $D_7 \ D_6 \ D_5 \ D_4 \ D_3 \ D_2 \ D_1 \ D_0$                                               |  |  |  |  |

|                                |                            | *     *     *     0     1     1     1     0       *     *     *     1     0     0     0     1 |  |  |  |  |

|                                |                            | * * * 1 0 0 0 1<br>* * * 1 0 0 0 0                                                            |  |  |  |  |

| 0 0 0 0 0 0 0 0                | 0 0 0 0 1 1                | * * * 0 1 1 1 0                                                                               |  |  |  |  |

| ۲ <u>––––</u> ۲                | 0 0 0 1 0 0                | * * * 0 0 0 1                                                                                 |  |  |  |  |

|                                | 0 0 0 1 0 1                | * * * 1 0 0 0 1                                                                               |  |  |  |  |

|                                | 0 0 0 1 1 0                | * * * 0 1 1 1 0                                                                               |  |  |  |  |

|                                | <u>0000</u> 111            | * * * 0 0 0 0 0                                                                               |  |  |  |  |

|                                | 0 0 1 0 0 0                | * * * 0 1 1 1 0                                                                               |  |  |  |  |

|                                | 0 0 1 0 0 1                | * * * 0 0 1 0 0                                                                               |  |  |  |  |

|                                | 0 0 1 0 1 0                | * * * 0 0 1 0 0                                                                               |  |  |  |  |

|                                | 0 0 1 0 1 1<br>0 0 1 1 0 0 | * * * 0 0 1 0 0<br>* * * 0 0 1 0 0                                                            |  |  |  |  |

|                                | 0 0 1 1 0 0                | * * * 0 0 1 0 0<br>* * * 0 0 1 0 0                                                            |  |  |  |  |

|                                |                            | * * * 0 1 1 1 0                                                                               |  |  |  |  |

|                                |                            | * * * 0 0 0 0 0                                                                               |  |  |  |  |

|                                |                            |                                                                                               |  |  |  |  |

| •                              | •                          | •                                                                                             |  |  |  |  |

| •                              | •                          | •                                                                                             |  |  |  |  |

|                                |                            | * * * 0 1 1 0                                                                                 |  |  |  |  |

|                                | 1 1 1 0 0 1                | * * * 0 0 1 0 0                                                                               |  |  |  |  |

|                                | 1 1 1 0 1 0                | * * * 0 0 1 0 0                                                                               |  |  |  |  |

|                                | 1 1 1 0 1 1                | * * * 0 0 1 0 0                                                                               |  |  |  |  |

|                                | 1 1 1 1 0 0                | * * * 0 0 1 0 0                                                                               |  |  |  |  |

|                                | 1 1 1 1 0 1                | * * * 0 0 1 0 0                                                                               |  |  |  |  |

|                                |                            | * * * 0 1 1 1 0<br>* 0 0 0 0 0 0                                                              |  |  |  |  |

|                                |                            | * * * 0 0 0 0 0                                                                               |  |  |  |  |

# Table 11 Relationship between CGRAM Addresses/Character Codes and Character Patterns

Remarks • The lower 3 bits of the Character Code List correspond to the upper 3 bits (A5 A4 A3) of the CGRAM.

- The lower 3 bits (A2 A1 A0) of the CGRAM correspond to the respective lines of the character patterns.

- The 8th line of the character pattern is the cursor position. By turning the cursor display ON, thelogic sum of the cursor and the character pattern is displayed. The upper 3 bits (D7 D6 D5) are ignored.

|       | ICOI  | NRA   | M     | Icon Display Data and |            |       |       |                |       |       |       |  |  |

|-------|-------|-------|-------|-----------------------|------------|-------|-------|----------------|-------|-------|-------|--|--|

|       | Ad    | dres  | s     |                       | SEG Output |       |       |                |       |       |       |  |  |

| $A_3$ | $A_2$ | $A_1$ | $A_0$ | D <sub>7</sub>        | $D_6$      | $D_5$ | $D_4$ | D <sub>3</sub> | $D_2$ | $D_1$ | $D_0$ |  |  |

| 0     | 0     | 0     | 0     | *                     | *          | *     | S1    | S2             | S3    | S4    | S5    |  |  |

| 0     | 0     | 0     | 1     | *                     | *          | *     | S6    | S7             | S8    | S9    | S10   |  |  |

| 0     | 0     | 1     | 0     | *                     | *          | *     | S11   | S12            | S13   | S14   | S15   |  |  |

| 0     | 0     | 1     | 1     | *                     | *          | *     | S16   | S17            | S18   | S19   | S20   |  |  |

| 0     | 1     | 0     | 0     | *                     | *          | *     | S21   | S22            | S23   | S24   | S25   |  |  |

| 0     | 1     | 0     | 1     | *                     | *          | *     | S26   | S27            | S28   | S29   | S30   |  |  |

| 0     | 1     | 1     | 0     | *                     | *          | *     | S31   | S32            | S33   | S34   | S35   |  |  |

| 0     | 1     | 1     | 1     | *                     | *          | *     | S36   | S37            | S38   | S39   | S40   |  |  |

| 1     | 0     | 0     | 0     | *                     | *          | *     | S41   | S42            | S43   | S44   | S45   |  |  |

| 1     | 0     | 0     | 1     | *                     | *          | *     | S46   | S47            | S48   | S49   | S50   |  |  |

| 1     | 0     | 1     | 0     | *                     | *          | *     | S51   | S52            | S53   | S54   | S55   |  |  |

| 1     | 0     | 1     | 1     | *                     | *          | *     | S56   | S57            | S58   | S59   | S60   |  |  |

| 1     | 1     | 0     | 0     | *                     | *          | *     | *     | *              | *     | *     | *     |  |  |

| 1     | 1     | 0     | 1     | *                     | *          | *     | *     | *              | *     | *     | *     |  |  |

| 1     | 1     | 1     | 0     | *                     | *          | *     | *     | *              | *     | *     | *     |  |  |

| 1     | 1     | 1     | 1     | *                     | *          | *     | *     | *              | *     | *     | *     |  |  |

Table 12 ICONRAM Address and Segment Drive Output Drive Bit Map

| ICON             | Blin | k RA | ١M |    | ICO   | ON B  | link D | isplay | / Data | and   |       |  |

|------------------|------|------|----|----|-------|-------|--------|--------|--------|-------|-------|--|

| A                | ddre | SS   |    |    |       |       | SEG    | Outp   | ut     |       |       |  |

| A <sub>3</sub> A | 2 A  |      | C  | D7 | $D_6$ | $D_5$ | $D_4$  | $D_3$  | $D_2$  | $D_1$ | $D_0$ |  |

| 0                | 0    | 0    | 0  | *  | *     | *     | S1     | S2     | S3     | S4    | S5    |  |

| 0                | 0    | 0    | 1  | *  | *     | *     | S6     | S7     | S8     | S9    | S10   |  |

| 0                | 0    | 1    | 0  | *  | *     | *     | S11    | S12    | S13    | S14   | S15   |  |

| 0                | 0    | 1    | 1  | *  | *     | *     | S16    | S17    | S18    | S19   | S20   |  |

| 0                | 1    | 0    | 0  | *  | *     | *     | S21    | S22    | S23    | S24   | S25   |  |

| 0                | 1    | 0    | 1  | *  | *     | *     | S26    | S27    | S28    | S29   | S30   |  |

| 0                | 1    | 1    | 0  | *  | *     | *     | S31    | S32    | S33    | S34   | S35   |  |

| 0                | 1    | 1    | 1  | *  | *     | *     | S36    | S37    | S38    | S39   | S40   |  |

| 1                | 0    | 0    | 0  | *  | *     | *     | S41    | S42    | S43    | S44   | S45   |  |

| 1                | 0    | 0    | 1  | *  | *     | *     | S46    | S47    | S48    | S49   | S50   |  |

| 1                | 0    | 1    | 0  | *  | *     | *     | S51    | S52    | S53    | S54   | S55   |  |

| 1                | 0    | 1    | 1  | *  | *     | *     | S56    | S57    | S58    | S59   | S60   |  |

| 1                | 1    | 0    | 0  | *  | *     | *     | *      | *      | *      | *     | *     |  |

| 1                | 1    | 0    | 1  | *  | *     | *     | *      | *      | *      | *     | *     |  |

| 1                | 1    | 1    | 0  | *  | *     | *     | *      | *      | *      | *     | *     |  |

| 1                | 1    | 1    | 1  | *  | *     | *     | *      | *      | *      | *     | *     |  |

Table 13 ICON BLINK RAM Address and Segment Drive Output Drive Bit Map

Remark: S1 to S60 correspond to segment drive output pins SEG1 to SEG60.

# 9. Cursor Blink Controller

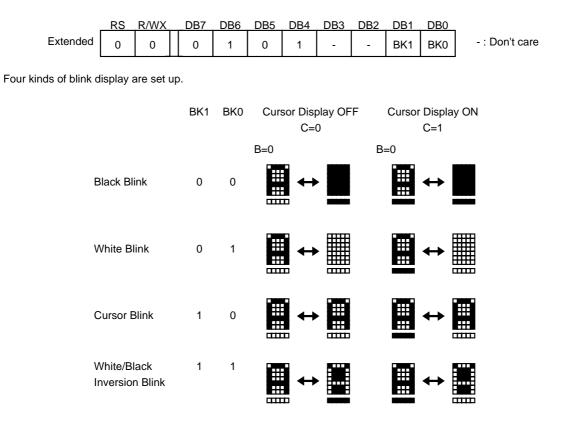

Controls the cursor display as well as the blink display (Character Blink Display). Displays and blinks the character indicated by the DDRAM address counter. To change the cursor or blink display position, execute the DDRAM SETTING ADDRESS command or the DATA WRITE command. The cursor display and the blink display positions are not changed by executing the CGRAM, ICONRAM or ICON BLINK RAM ADDRESS command or executing data write. The cursor is displayed on the 8th line of the character font of a 5-bit length, and with the logic sum of the CGROM character patterns. The blink display comes in four types and can be set by the BLINK SELECT command. Refer to "Instruction Description" (page 25 of this specification).

# **10.CR Oscillating Circuit**

Generates a basic clock that serves as display timing.

The oscillating frequency can be reduced to fosc=approx. 34 kHz via an oscillating resistor (Rf=500 k $\Omega$ ). By inputting the external clock in OSC1, operation through the external clock is possible. In this case, set OSC2 to "Open."

| Duty      | Rf     | fosc   | Frame Frequency | Frame Frequency | fosc<br>——— [Hz] |

|-----------|--------|--------|-----------------|-----------------|------------------|

| 1/17 Duty | 500 kΩ | 34 kHz | 76.9 Hz         |                 | 2×13×17          |

# 11.LCD Driver

Has 16 common output pins, two ICON common output pins, and 60 segment output pins for driving the LCD, and generates 2-frame AC drive waveform (type B). Two ICON common output pins, each of which is configured orgthogonally to the chip, generate the drive waveform at the same timing. The ICON display can be configured over and under the top and the bottom of the LCD panel. When the ICON display is in no use, set the icon common output pin to "Open."

# **12. LCD Power Supply Circuit**

Consists of a doubler, an LCD voltage controller, an LCD bias resistor, and a voltage follower. The LCD voltage controller consists of a voltage regulator and an LCD voltage command fine adjustment circuit. The LCD power supply circuit can be controlled by pins FNC1 and 2 and BIAS SELECT command. For power supply, an internal type for the booster, voltage regulator and LCD voltage adjustment circuit or any external type can be switched by setting pins FNC1 or 2. All of internal LCD power supplies will be automatically turned OFF by setting FNC1 to "H", and FNC2 to "L." Because of this, the LCD bias voltage produced via the externally-divided resistor can be supplied to pins VLCD, and V1 to V4.

| FI | NC<br>1 | FNC<br>2 | Doubler | LCD Voltage<br>Adjustment<br>Circuit | LCD Bias<br>Resistor | Voltage<br>Follower                             | Remarks                               | O: Valid<br>× : Invalid |  |

|----|---------|----------|---------|--------------------------------------|----------------------|-------------------------------------------------|---------------------------------------|-------------------------|--|

|    | Н       | Н        | 0       | 0                                    | 0                    | O O Use all internal LCD power supply circuits. |                                       |                         |  |

|    | Н       | L        | ×       | ×                                    | ×                    | $\times$ × Use an external bias resistance.     |                                       |                         |  |

|    | L       | н        | ×       | ×                                    | ×                    | < × Setting is not needed.                      |                                       |                         |  |

|    | L       | L        | ×       | ×                                    | 0                    | 0                                               | Externally generates and inputs VLCD. |                         |  |

#### Table 14 LCD Power Supply Circuit

Remarks • Always connect FNC1 and 2 to VDD or VSS.

- Externally-connected pins VOUT, VLCD and V1 through V4 cannot be used as a drive power supply of other circuits.

- Connecting the power supply externally with the internal LCD power supply circuit ON may lead to a breakdown of the IC.

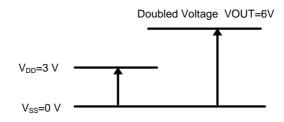

#### 12.1 Doubler

Doubles the voltage through oscillating frequency of the CR Oscillating Circuit. The voltage is boosted from the  $V_{SS}$  level and output to  $V_{OUT}$ . Capacitors between C1+ and C1- as well as between  $V_{SS}$  and  $V_{OUT}$  are connected. Use the doubler in the range of  $V_{DD} \leq 3.6 \text{ V}$ .

Figure 10 Example of Booster Output

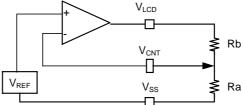

#### 12.2 LCD Voltage Adjustment Circuit

LCD drive voltage V can be adjusted by the following two voltage controllers:

Voltage Regulator

Adjusts voltage regulator output VLCD by externally- divided resistors Ra and Rb.

VLCD can be calculated as the division ratio of the internal reference voltage VREF. VREF has temperature characteristics of approx. 0.01%/ C and -0.13%/ C and the LCD temperature gradient can be compensated. VREF differs depending upon the temperature characteristics of the reference voltage to select a command.

$$V_{LCD} = \frac{Ra + Rb}{Ra} V_{REF}$$

(V)

Figure 11 Example of LCD Voltage Adjustment Circuit

VLCD can be used as a "variable" by using the volume resistor as the divided resistor. Feedback voltage noises occurring at VCNT pin directly affect VLCD. Take appropriate measures against noises.

# 12.3 LCD Bias Resistor

The internally-divided resistor creates a bias potential for the LCD drive. Either 1/5 or 1/4 bias potential can be selected by executing a command. Because the bias potential is supplied from bias resistor via the voltage follower to the LCD driver, the bias current consumption is significantly reduced.

When setting FNC1 to "H" and FNC2 to "L," the externally-attached bias resistor can be connected directly to pins V1 through V4. The bias resistor of a 1/2 or more bias ratio can be freely supplied to the LCD driver as an LCD drive voltage. Regardless of its level, the voltage can be input to pins V1 through V4. Select an appropriate resistance value of the divided resistor in accordance with the size and the capacity of of the LCD panel. A deflection may occur in the LCD drive waveform depending upon the size and the capacity of the LCD panel. If so, adjust the value of the bias resistor or the capacitor. When the external bias is selected, the bias voltage is also supplied via the voltage follower to the LCD driver. The internal booster or the LCD voltage adjustment circuit cannot be used.

Supply VLCD via the externally-attached LCD power supply circuit.

#### 12.4 Voltage Follower

Buffers the bias potential via the internal bias resistor and supplies it to the LCD driver.

#### 12.5 Reference Voltage Circuit

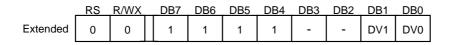

Generates reference voltage VREF. The VREF has the following three values:

#### Table 15 $V_{REF}$

|     |     | V <sub>F</sub>  | REF              |  |  |

|-----|-----|-----------------|------------------|--|--|

| DV1 | DV0 | Temperature     | Reference        |  |  |

|     |     | Characteristics | Voltage          |  |  |

| 0   | 0   | -0.13%/°C       | 1.7 V (Standard) |  |  |

| 0   | 1   | 0.01%/°C        | 1.7 V (Standard) |  |  |

| 1   | *   | —               | V <sub>DD</sub>  |  |  |

# Instruction Explanation

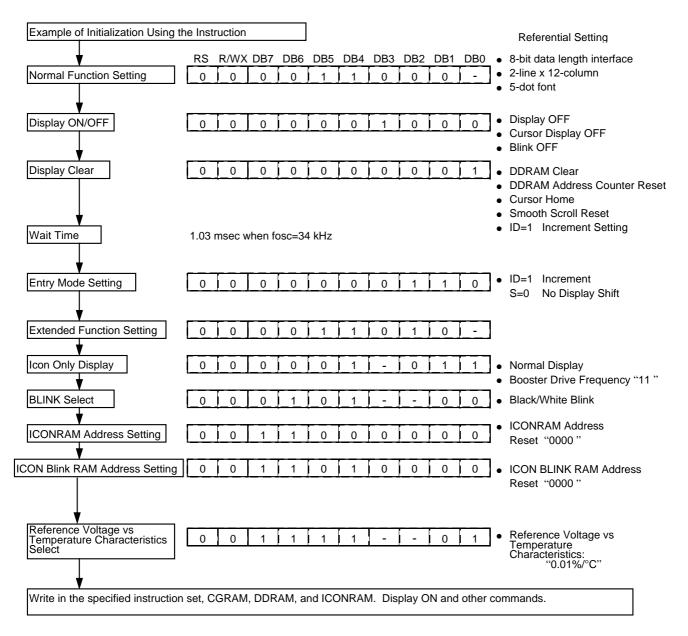

The instruction comes in two types - - namely, normal instructions and extended instructions. All instructions excluding the DISPLAY CLEAR are completed within the instruction command cycle time. Because of this, the CPU does not need for checking the BUSY flag, and instructions can be input in succession.

#### 1. Normal Instructions

# 1.1 DISPLAY CLEAR

|        | RS | R/WX | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|--------|----|------|-----|-----|-----|-----|-----|-----|-----|-----|

| Normal | 0  | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

Clears the display and initializes the state. The display of marks remains unchanged.

| DDRAM                   | : | Writes 20H in hexadecimal scale.                                                      |

|-------------------------|---|---------------------------------------------------------------------------------------|

| DDRAM Address Counter   | : | Sets address 0. Clears the DISPLAY SHIFT and returns to the default.                  |

| Entry Mode              | : | Sets to ID=1 [increment]. "S" remains unchanged.                                      |

| Cursor                  | : | The CURSOR DISPLAY position moves to the 1st line, left end. "C" remains unchanged.   |

| Blink                   | : | The BLINK DISPLAY position moves to the 1st line, left end. "B" remains<br>unchanged. |

| Amount of smooth scroll | : | Resets the amount of scroll.                                                          |

The DISPLAY CLEAR needs the time for writing space codes in succession in all of DDRAMs. Confirm the completion of the DISPLAY CLEAR command by checking the BUSY flag. When you wait for the time expressed by equation (1) after executing the DISPLAY CLEAR command, the BUSY flag does not need to be checked (the value twice as many as the value expressed in equation (1) is recommended as the wait time).

The contents of the CGRAM, ICONRAM, and ICON BLINK RAM remain unchanged.

The DISPLAY CLEAR command is ignored during the POWER SAVE.

Remark: Always set all space codes in "20" (hexadecimal scale).

Time until DISPLAY CLEAR is completed=  $\frac{35}{\text{fosc}(\text{kHz})}$  msec +++ Equation (1)

#### 1.2 CURSOR HOME

|        | RS | R/WX | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|--------|----|------|-----|-----|-----|-----|-----|-----|-----|-----|

| Normal | 0  | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 1   | СН  |

Initializes the cursor position and the blink position. The contents of the CHARACTER DISPLAY and the ICON DISPLAY remain unchanged. After this instruction is executed, data is read from the CPU and written in the DDRAM.

• CH=1 (Cursor Home)

| DDRAM Address Counter   | : Sets the address to 0.                                                             |

|-------------------------|--------------------------------------------------------------------------------------|

| DISPLAY SHIFT           | : Clears the amount of the DISPLAY SHIFT and returns to the initial display screen.  |

| CURSOR                  | : The CURSOR DISPLAY position moves to the 1st line, left end. "C" remains           |

|                         | unchanged.                                                                           |

| BLINK                   | : The BLINK DISPLAY position moves to the 1st line, left end. "B" remains unchanged. |

| Amount of SMOOTH SCROLI | .: Resets the amount of the SCROLL and returns to the initial display screen.        |

| CH=0 (Cursor Return)    |                                                                                      |

| DDRAM Address Counter  | : Sets the 1st address on the CURSOR DISPLAY line.                                   |

|------------------------|--------------------------------------------------------------------------------------|

| DISPLAY SHIFT          | : Clears the amount of the DISPLAY SHIFT and returns to the initial display screen.  |

| CURSOR                 | : The CURSOR DISPLAY position moves to the same line, left end. "C" remains          |

|                        | unchanged.                                                                           |

| BLINK                  | : The BLINK DISPLAY position moves to the 1st line, left end. "B" remains unchanged. |

| Amount of SMOOTH SCROL | L: Resets the amount of the SCROLL and returns to the initial display screen.        |

# **1.3 ENTRY MODE SETTING**

|        | RS | R/WX | _DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|--------|----|------|------|-----|-----|-----|-----|-----|-----|-----|

| Normal | 0  | 0    | 0    | 0   | 0   | 0   | 0   | 1   | ID  | S   |

When data is written in and read from the DDRAM, CGRAM, ICONRAM, or the ICON BLINK RAM in accordance with the ID, set ID=1 [increment] or ID=0 [decrement] of the selected RAM address counter.

"S" determines whether or not the whole display shifts during the write in the DDRAM. The display shifts left when ID=1, and shifts right when ID=0.

Table 16 Operations of Address Counter

| ID | Access from/to RAM                                                   | Operations of Address Counter                                                                          |  |  |  |

|----|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|--|--|

| 0  | DDRAM<br>CGRAM: After write<br>ICONRAM: After read<br>ICON BLINK RAM | Decrements the address counter of the RAM (-1) after executing write and read.                         |  |  |  |

| 1  | DDRAM<br>CGRAM: After write<br>ICONRAM: After read<br>ICON BLINK RAM | <ul> <li>Increments the address counter of the RAM (+1)<br/>after executing write and read.</li> </ul> |  |  |  |

#### Table 17 Display Shift

| Access from/to RAM                                    | ID | S | Display Shift                                                                                          |

|-------------------------------------------------------|----|---|--------------------------------------------------------------------------------------------------------|

|                                                       | 1  | 1 | <ul><li>Shifts the whole display left.</li><li>CURSOR and BLINK positions remain unchanged.*</li></ul> |

| Write in DDRAM                                        |    | 0 | <ul><li>The display does not shift.</li><li>CURSOR and BLINK positions shift right.</li></ul>          |

|                                                       | 0  | 1 | <ul><li>Shifts the whole display right.</li><li>CURSOR and BLINK positions remain unchanged.</li></ul> |

|                                                       |    | 0 | <ul><li>The display does not shift.</li><li>CURSOR and BLINK positions shift left.</li></ul>           |

| Read from DDRAM                                       | 1  | - | <ul><li>The display does not shift.</li><li>CURSOR and BLINK positions shift right.</li></ul>          |

|                                                       | 0  | - | <ul><li>The display does not shift.</li><li>CURSOR and BLINK positions shift left.</li></ul>           |

| CGRAM<br>Write in ICONRAM<br>Read from ICON BLINK RAM | -  | - | <ul><li>The display does not shift.</li><li>CURSOR and BLINK positions do not shift.</li></ul>         |

Notes: -- : Don't care.

\* : The display shifts. CURSOR and BLINK positions seem to be standstill on the display screen. CURSOR and BLINK displays are valid only when "1" is set to DISPLAY ON/OFF command C or B.

# 1.4 DISPLAY ON/OFF

|        | RS | R/WX | _DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 | _ |

|--------|----|------|------|-----|-----|-----|-----|-----|-----|-----|---|

| Normal | 0  | 0    | 0    | 0   | 0   | 0   | 1   | D   | С   | В   |   |

"D", "C" and "B"set the DISPLAY ON/OFF, CURSOR DISPLAY ON/OFF and BLINK DISPLAY ON/OFF.

Table 18 D

| D | Functions                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 1 | urns ON the display (display start).                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| 0 | <ul> <li>Turns OFF the CHARACTER DISPLAY, MARK DISPLAY, CURSOR DISPLAY, and BLINK DISPLAY.</li> <li>Data of the DDRAM, CGRAM, ICONRAM, and ICON BLINK RAM remain unchanged.</li> <li>Displays again when turning ON the display.</li> <li>Remark: There is no change in the current consumption when turning OFF the display.</li> </ul> |  |  |  |  |  |  |  |  |

# Table 19 C

| С | Functions                                                                         |  |  |  |  |  |  |  |

|---|-----------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 1 | Displays the cursor at the position of the DDRAM address counter.                 |  |  |  |  |  |  |  |

| 0 | Turns OFF the CURSOR DISPLAY.<br>There is no change in setting values such as ID. |  |  |  |  |  |  |  |

# Table 20 B

| В | Functions                                                                                                                                                                              |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | Continues blinking the characters at the position of the DDRAM address counter.<br>Can set the CURSOR and BLINK at the same time.<br>Blink Frequency= $\frac{\text{fosc}}{32768}$ [Hz] |

| 0 | Aborts the blink.                                                                                                                                                                      |

# 1.5 CURSOR/DISPLAY SHIFT

|                | RS | R/WX | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 | _ |

|----------------|----|------|-----|-----|-----|-----|-----|-----|-----|-----|---|

| Normal         | 0  | 0    | 0   | 0   | 0   | 1   | SC  | RL  | -   | -   |   |

| - : Don't care |    |      |     |     |     |     |     |     |     |     |   |

Shifts CURSOR and BLINK positions without writing in and reading from the display data. Used for character correction and retrieval.

Data is written in and read from the CPU to the DDRAM after executing this command.

# Table 21 Cursor/Display Shift

| SC | RL | Functions                                                                                    |

|----|----|----------------------------------------------------------------------------------------------|

|    | _  | Shifts CURSOR and BLINK positions left.                                                      |

| 0  | 0  | Decrements the DDRAM address counter (-1).                                                   |

|    |    | Repetitious operations of the CURSOR SHIFT move the cursor to other line.                    |

|    |    | Shifts CURSOR and BLINK positions right.                                                     |

| 0  | 1  | Increments the DDRAM address counter (+1).                                                   |

|    |    | Repetitious operations of the CURSOR SHIFT move the cursor to other line.                    |

|    |    | Shifts the whole display left.                                                               |

| 1  | 0  | Shifts CURSOR and BLINK positions left, together with characters.                            |

| '  | 0  | There is no change in the DDRAM address counter.                                             |

|    |    | Characters do not shift to other line even when the DISPLAY SHIFT is executed in succession. |

|    |    | Shifts the whole display right.                                                              |

| 1  | 1  | Shifts CURSOR and BLINK positions right, together with characters.                           |

| '  |    | There is no change in the DDRAM address counter.                                             |

|    |    | Characters do not shift to other line even when the DISPLAY SHIFT is executed in succession. |

#### **1.6 FUNCTION SET**

|        | RS | R/WX | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|--------|----|------|-----|-----|-----|-----|-----|-----|-----|-----|

| Normal | 0  | 0    | 0   | 0   | 1   | DL  | Ν   | MS  | DT  | -   |

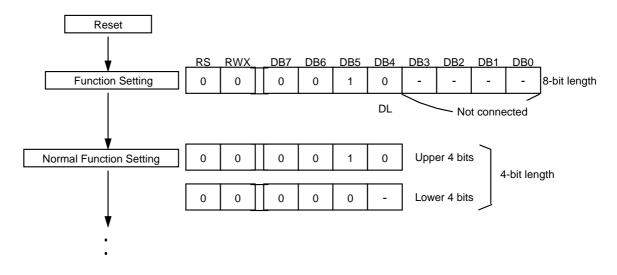

#### 1.6.1 DL

Sets the length of data for parallel interface.

0: 4-bit data length interface

1: 8-bit data length interface

# 1.6.2 N

Sets the display screen.

N:0 Selects a 2-line x 12 column display.

N:1 Selects a 1-line x 24 column display.

#### 1.6.3 MS

Selects the instruction table.

#### Table 22 MS

| MS | Functions                                                   |

|----|-------------------------------------------------------------|

| 0  | Selects the Normal Instruction Table.                       |

|    | Sets "0" when changing from the Extended Instruction Table. |

| 1  | Selects the Extended Instruction Table.                     |

|    | Sets "1" when changing from the Normal Instruction Table.   |

# 1.6.4 DT

# Table 22 DT

| DT | Γ | Functions          |

|----|---|--------------------|

| 0  |   | 5-dot display mode |

| 1  |   | 6-dot display mode |

#### **1.7 CGRAM ADDRESS SETTING**

|        | RS | R/WX | DB7 | DB6 | DB5            | DB4            | DB3            | DB2            | DB1            | DB0            | _ |

|--------|----|------|-----|-----|----------------|----------------|----------------|----------------|----------------|----------------|---|

| Normal | 0  | 0    | 0   | 1   | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |   |

Sets binary "A5A4A3A2A1A0" to the CGRAM Address Counter.

After executing this command, data is written from the CPU and read in the CGRAM.

#### **1.8 DDRAM ADDRESS SETTING**

|        | RS | R/WX | DB7 | DB6 | DB5 | DB4            | DB3            | DB2            | DB1            | DB0            |

|--------|----|------|-----|-----|-----|----------------|----------------|----------------|----------------|----------------|

| Normal | 0  | 0    | 1   | -   | -   | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |

|        |    |      |     |     |     |                |                |                |                |                |

-: Don't care

Sets binary "A4A3A2A1A0" to the DDRAM Address Counter.

After executing this command, data is written from the CPU and read in the DDRAM.

# 1.9 BUSY FLAG/ADDRESS READ

|        | RS | R/WX | DB7 | DB6 | DB5            | DB4            | DB3            | DB2            | DB1            | DB0            | _ |

|--------|----|------|-----|-----|----------------|----------------|----------------|----------------|----------------|----------------|---|

| Normal | 0  | 1    | BF  | 0   | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |   |

Reads the BUSY flag and the content of "A5A4A3A2A1A0" of the Address Counter. Outputs BUSY flag BF"1" to DB7 during execution of a command. Execution of any command excluding the DISPLAY CLEAR is completed within the command cycle time. Therefore, confirmation of the BUSY flag is not needed.

The Read Address Counter reads the contents of the RAM address counter accessed just before executing this command among DDRAM, CGRAM, ICONRAM, and ICON BLINK RAM.

#### 1.10 DATA WRITE

|        | RS | R/WX | _DB7           | DB6            | DB5            | DB4            | DB3            | DB2   | DB1            | DB0            | _ |

|--------|----|------|----------------|----------------|----------------|----------------|----------------|-------|----------------|----------------|---|

| Normal | 1  | 0    | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | $D_2$ | D <sub>1</sub> | D <sub>0</sub> |   |

Writes binary data "D7D6D5D4D3D2D1D0" in CGRAM, DDRAM, ICONRAM, and ICON BLINK RAM. Prior to data write, execute the desired RAM ADDRESS SETTING command to select an appropriate RAM. Addresses after write are incremented or decremented depending upon the ID value in the entry mode.

| Table 24 Length of Data of Each Memory | Table 24 | Length | of Data o | f Each | Memory |

|----------------------------------------|----------|--------|-----------|--------|--------|

|----------------------------------------|----------|--------|-----------|--------|--------|

|                | DB7            | DB6   | DB5            | DB4   | DB3   | DB2            | DB1            | DB0            |

|----------------|----------------|-------|----------------|-------|-------|----------------|----------------|----------------|

| DDRAM          | D <sub>7</sub> | $D_6$ | D <sub>5</sub> | $D_4$ | $D_3$ | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |

| CGRAM          | *              | *     | *              | $D_4$ | $D_3$ | $D_2$          | D <sub>1</sub> | D <sub>0</sub> |

| ICONRAM        | *              | *     | *              | $D_4$ | $D_3$ | $D_2$          | D <sub>1</sub> | D <sub>0</sub> |

| ICON BLINK RAM | *              | *     | *              | $D_4$ | $D_3$ | $D_2$          | D <sub>1</sub> | D <sub>0</sub> |

#### 1.11 DATA READ

|        | RS | R/WX | _DB7           | DB6            | DB5            | DB4            | DB3            | DB2   | DB1            | DB0            |

|--------|----|------|----------------|----------------|----------------|----------------|----------------|-------|----------------|----------------|

| Normal | 1  | 1    | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | $D_2$ | D <sub>1</sub> | D <sub>0</sub> |

Reads binary "D7D6D5D4D3D2D1D0" from CGRAM, DDRAM, ICONRAM, ICON BLINK RAM. Prior to data write, execute the desired RAM ADDRESS SETTING command to select an appropriate RAM. Addresses after write are incremented or decremented depending upon the ID value in the entry mode.

# 2. Extended Instructions

# 2.1 POWER SAVE SETTING

|          | RS | R/WX | _DB | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |                |

|----------|----|------|-----|-----|-----|-----|-----|-----|-----|-----|----------------|

| Extended | 0  | 0    | 0   | 0   | 0   | 0   | -   | -   | -   | PS  | - : Don't care |

#### PS : 1 Power Save

- Aborts the oscillating circuit and the LCD power supply circuit.

- Aborts the LCD driver. Segment, and common LCD drive outputs are fixed to VSS.

- Aborts the LCD.

- Leaves the setting of individual data, common and address in the DDRAM, CGRAM, ICONRAM, ICON BLINK RAM unchanged.

PS : 0 Cancels Power Save

In the Power Save mode, the current consumption is minimized to approximate the value during standstill. When the external power supply is used, it is necessary to stop it and go to the floating or the VSS level. Also, a switching transistor and other circuit which cut the current flowing through the external bias resistor are needed.

#### 2.2 SELECTING ICON ONLY DISPLAY, BOOSTER DRIVE FREQUENCY

|          | RS | R/WX | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |                |

|----------|----|------|-----|-----|-----|-----|-----|-----|-----|-----|----------------|

| Extended | 0  | 0    | 0   | 0   | 0   | 1   | -   | MD  | DC1 | DC0 | - : Don't care |

MD : 0 Normal Display

MD : 1 Icon Only Display

DC : Booster Drive Frequency Setting

| DC1 | DC0 |         | Booster Drive Frequency [kHz] |

|-----|-----|---------|-------------------------------|

|     |     |         | 1/17 Duty fosc=34 kHz         |

| 0   | 0   |         | 4.25 (1/8 osc)                |

| 0   | 1   | Default | 2.13 (1/16 osc)               |

| 1   | 0   |         | 1.06 (1/32 osc)               |

| 1   | 1   |         | 0.53 (1/64 osc)               |

Regardless of the contents of the DDRAM, the icon only is displayed and display screens excluding marks go out when MD=1. When setting the booster drive frequency, it is possible to minimize the current consumption by reducing the booster drive frequency in accordance with the boosting control data.

When the booster drive frequency is reduced, the contrast of the display icon differs depending upon the display panel size and the value of the capacitor for the booster. Determine the ability of the booster by experimentally optimizing the contrast of the LCD panel. In addition, take into careful consideration noises which may affect the system due to the booster drive frequency.

After resetting, the booster drive frequency is the default value.

# 2.3 SELECT COM/SEG OUTPUT MODE, SELECT BIAS

|          | RS | R/WX | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----------|----|------|-----|-----|-----|-----|-----|-----|-----|-----|

| Extended | 0  | 0    | 0   | 1   | 0   | 0   | MLC | MLS |     | BS5 |

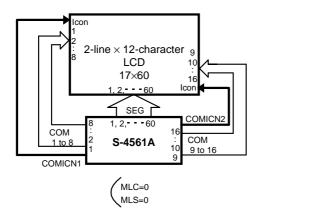

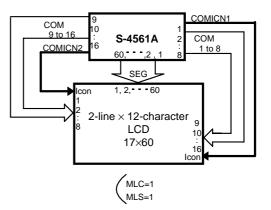

The MLC determines how the common output waveform is output to COM (1-16) terminals.

MLC=0: The common output waveform is output in the order of COM1, COM2, ..., COM15, COM16.

MLC=1: The common output waveform is output in the order of COM16, COM15, ..., COM2, COM1.

The MLS determines how the segment output waveform is output to SEG (1-60) terminals.

The output form also varies depending upon N=0 or N=1.

[N=0 (2-line x 12-column) display]

- MLS=0: The segment output waveform to be displayed on the DDRAM addresses from 00 to 0B is output to terminals from SEG1 to SEG60.

The segment output waveform to be displayed on the DDRAM addresses from 10 to 1B is output to terminals from SEG1 to SEG60.

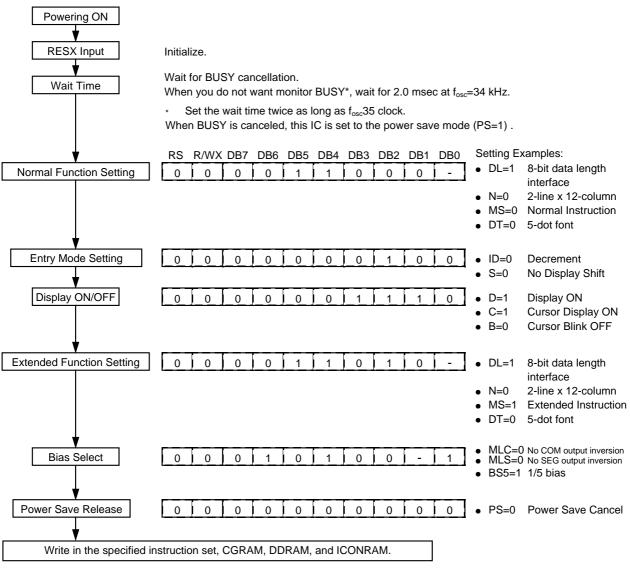

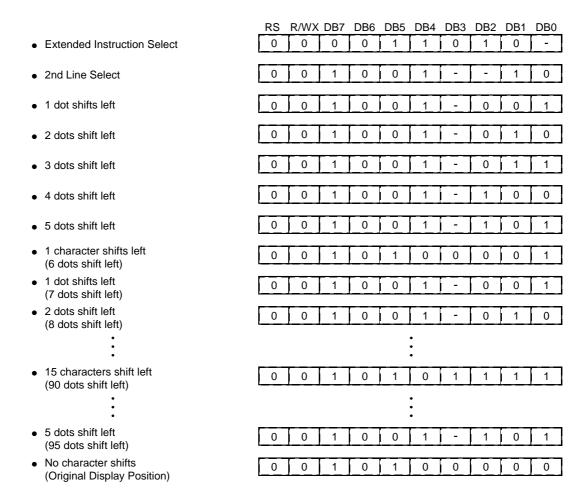

- MLS=1: The segment output waveform to be displayed on the DDRAM addresses from 00 to 0B is output to terminals from SEG60 to SEG1. The segment output waveform to be displayed on the DDRAM addresses from 10 to 1B is output to